1

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств высокого быстродействия.

Известно запоминающее устройство, содержащее полноточный накопитель на ферритдиодных запоминающих элементах, сердечники которых прошиты обмотками возбуждения и выходными обмотками, а диоды подключены своими анодами через соответствующие адресные шины записи к адресным ключам записи, а катодами - через обмотки возбуждения сердечников к разрядным шинам накопителя, усилители воспроизведения, соединенные с разрядными выходными обмотками накопителя, дешифратор адреса, выходы которого подключены к соответствующим адресным ключам записи, и регистр числа.

Для записи информации в таком запоминающем устройстве необходимо два такта: такт обнуления выбранной ячейки памяти и такт записи.

Целью изобретения является упрощение устройства и повышение его быстродействия, что достигается за счет сокращения количества обмоток, прошивающих сердечник запоминающего элемента и за счет сокращения цикла записи информации.

От известного предложенное устройство отличается тем, что оно содержит двуполярные разрядные формирователи тока, адресные ключи считывания и дополнительные диоды, причем выходы двухполярных разрядных формирователей тока соединены с разрядными шинами накопителя, а конец обмотки возбуждения каждого сердечника, подключенный к катоду диода, соединен с анодом дополнительного диода, катод которого соединен адресной шиной считывания с выходом адресного ключа считывания, подключенного своим входом к соответствующему выходу дешифратора адреса.

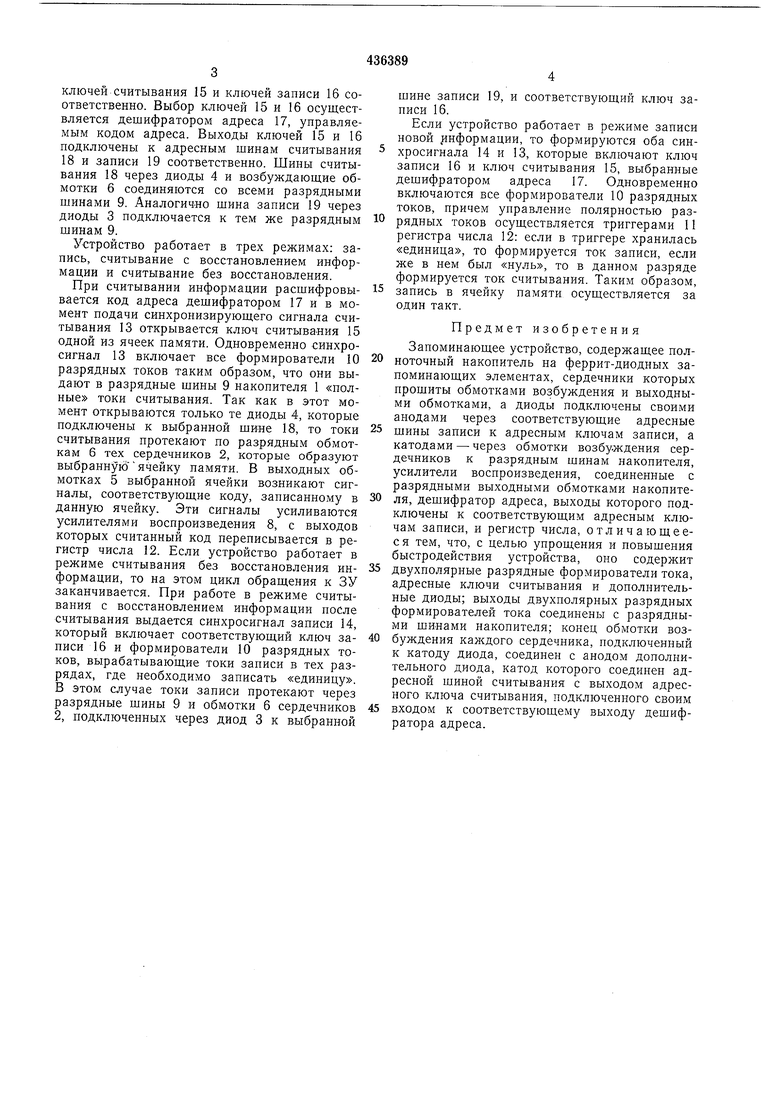

На чертеже приведена структурная схема запоминающего устройства.

Устройство состоит из накопителя 1, каждый запоминающий элемент которого содержит ферритовый сердечник 2 и два селектирующих диода 3 и 4. Через каждый ферритовый сердечник проходят две обмотки: выходная 5 и возбуждающая 6. Выходные обмотки 5 сердечников одного разряда соединены последовательно и образуют разрядную выходную обмотку 7, которая подключается к усилителю воспроизведения 8. Возбуждающие

обмотки 6 с одной стороны подключены к разрядным шинам 9, подключенным к формирователям 10 разрядных токов. Формирователи 10 управляются триггерами 11 регистра числа 12 и синхросигналами 13 и 14. Одновременно

синхросигналы 13 и 14 подаются на входы

ключей считывания 15 и ключей записи 16 соответственно. Выбор ключей 15 и 16 осуществляется дешифратором адреса 17, управляемым кодом адреса. Выходы ключей 15 и 16 подключены к адресным шинам считывания 18 и записи 19 соответственно. Шины считывания 18 через диоды 4 и возбуждаюш,ие обмотки б соединяются со всеми разрядными шинами 9. Аналогично шина записи 19 через диоды 3 подключается к тем же разрядным шинам 9.

Устройство работает в трех режимах: запись, считывание с восстановлением информации и считывание без восстановления.

При считывании информации расшифровывается код адреса дешифратором 17 и в момент подачи синхронизирующего сигнала считывания 13 открывается ключ считывания 15 одной из ячеек памяти. Одновременно синхросигнал 13 включает все формирователи 10 разрядных токов таким образом, что они выдают в разрядные шины 9 накопителя 1 «полные токи считывания. Так как в этот момент открываются только те диоды 4, которые подключены к выбранной шине 18, то токи считывания протекают по разрядным обмоткам 6 тех сердечников 2, которые образуют выбраннук) ячейку памяти. В выходных обмотках 5 выбранной ячейки возникают сигналы, соответствующие коду, записанному в данную ячейку. Эти сигналы усиливаются усилителями воспроизведения 8, с выходов которых считанный код переписывается в регистр числа 12. Если устройство работает в режиме считывания без восстановления информации, то на этом цикл обращения к ЗУ заканчивается. При работе в режиме считывания с восстановлением информации после считывания выдается синхросигнал записи 14, который включает соответствующий ключ записи 16 и формирователи 10 разрядных токов, вырабатывающие токи записи в тех разрядах, где необходимо записать «единицу. В этом случае токи записи протекают через разрядные шины 9 и обмотки 6 сердечников 2, подключенных через диод 3 к выбранной

шине записи 19, и соответствующий ключ записи 16.

Если устройство работает в режиме записи новой нфopмaции, то формируются оба синхросигнала 14 и 13, которые включают ключ записи 16 и ключ считывания 15, выбранные дешифратором адреса 17. Одновременно включаются все формирователи 10 разрядных токов, причем управление полярностью разрядных токов осуществляется триггерами 11 регистра числа 12: если в триггере хранилась «единица, то формируется ток записи, если же в нем был «нуль, то в данном разряде формируется ток считывания. Таким образом,

запись в ячейку памяти осуществляется за один такт.

Предмет изобретения

Запоминающее устройство, содержащее полноточный накопитель на феррит-диодных запоминающих элементах, сердечники которых прошиты обмотками возбуждения и выходными обмотками, а диоды подключены своими анодами через соответствующие адресные

шины записи к адресным ключам записи, а катодами - через обмотки возбуждения сердечников к разрядным шинам накопителя, усилители воспроизведения, соединенные с разрядными выходными обмотками накопителя, дешифратор адреса, выходы которого подключены к соответствующим адресным ключам записи, и регистр числа, отличающееся тем, что, с целью упрощения и повышения быстродействия устройства, оно содержит

двухполярные разрядные формирователи тока, адресные ключи считывания и дополнительные диоды; выходы двухполярных разрядных формирователей тока соединены с разрядными шинами накопителя; конец обмотки возбуждения каждого сердечника, подключенный к катоду диода, соединен с анодом дополнительного диода, катод которого соединен адресной шиной считывания с выходом адресного ключа считывания, подключенного своим

входом к соответствующему выходу дешифратора адреса.

ft iVi

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА ПОЛНОТОЧНОМНАКОПИТЕЛЕ | 1971 |

|

SU289514A1 |

| Цифровое устройство числового программного управления | 1971 |

|

SU441858A1 |

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| Оперативное запоминающее устройство | 1980 |

|

SU942140A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| Логическое запоминающее устройство | 1971 |

|

SU443411A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Запоминающее устройство типа 2,5 д | 1981 |

|

SU999105A1 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

Даты

1974-07-15—Публикация

1972-07-11—Подача