(5) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1972 |

|

SU517935A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОСЙ1Ч '^ | 1972 |

|

SU436389A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Ассоциативное логическое запоминающее устройство | 1972 |

|

SU485501A1 |

| Запоминающее устройство | 1973 |

|

SU446107A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| Запоминающее устройство | 1978 |

|

SU696542A1 |

| Запоминающее устройство с сохранением информации при аварийном отключении питания | 1977 |

|

SU693441A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ТИПА ЗД | 1971 |

|

SU427380A1 |

| Магнитное запоминающее устройство | 1975 |

|

SU568971A2 |

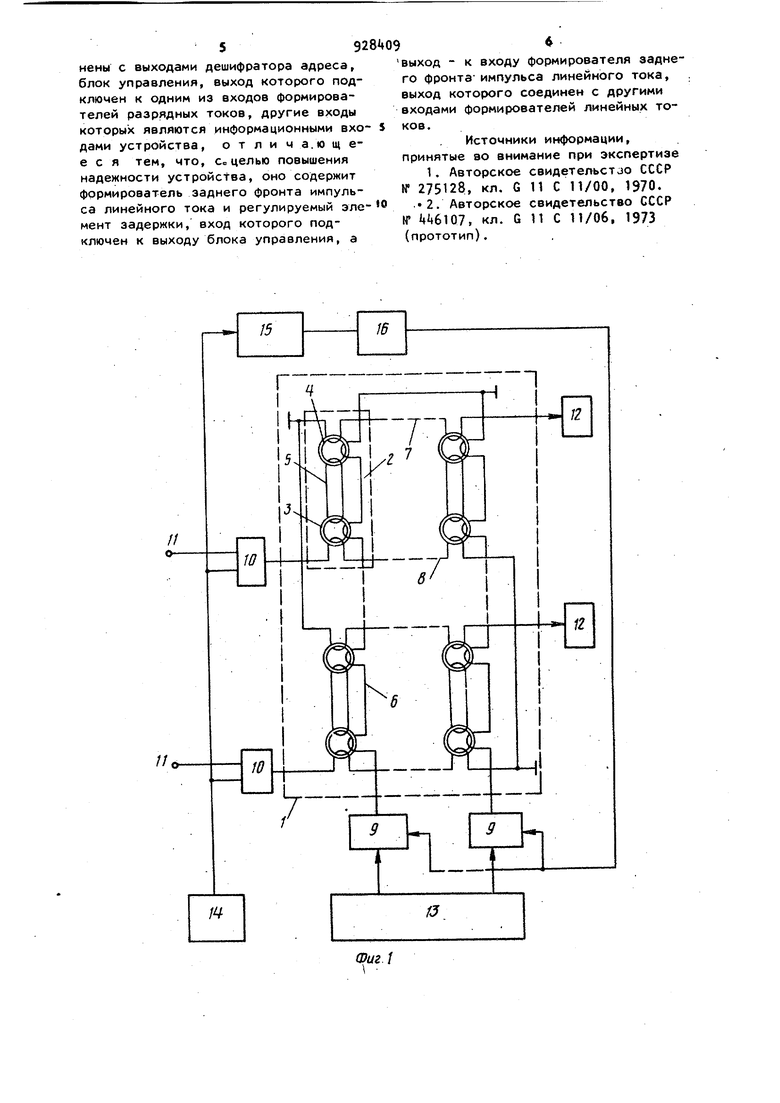

Изобретение относится к запоминающим устройствам. Известно запоминающее устройство (ЗУ) , содержащее накопитель с элементами памяти., шины записи и считывания, формирователи линейных токов, разрядные ((юрмирователи и дешифратор Ц. „ Недостатком этого устройства является невысокое быстродействие. Наиболее близким техническим решением к данному изобретению яаля.ется ЗУ, содержащее накопитель с чи ловыми ячейками, выполненными на фе ритовых сердечниках с прямоугольной петлей гистерезиса, объединенны попарно витками.связи и прошитых адресными шинами считывания, рдзряд ными шинами записи, разрядными шина ми чтения, соединенными соответственно с блоком адресной выборки, ра рядными формирователями тока записи м усилителями воспроизведения, и ши ной смещения, а также блок управления, вентиль и разрядные вентили 21. Недостатком этого устройства является то, что вследствие индуктивного характера сопротивления разрядной шины наблюдается завал переднего фронта разрядного тока. Это приводит к уменьшению тока в витке связи элеMeHta памяти в такте, записи и к не-i полному перемагнимиванию запоминающего сердечника при записи 1, а это в свою очередь приводит к уменьшению амплитуды считываемого сигнала с элемента памяти и к снижению отношения сигнал/помеха. Устойчивая работа такого ЗУ становится невозможной . без деления накопителя на секции и введения дополнительных разрядных (1юрмирователей для каждой секции. Указанные обстоятельства снижают надежностьустройства. Целью изобретения является повышение надежности запоминающего устройства. Поставленная цель достигается тем, что в запоминающее устройство, содержащее накопитель i элементы памя ти которого выполнены на двух сердечниках, объединенных резистивным витком связи и прошитых разрядными шинами записи и считывания и линейными шинами, подключенйыми соответственно к выходам формирователей разрядных токов, входам усилителей считывания и выходам формирователей линейных токов, одни из входов которых соединены с выходами дешифратора адреса, блок управления, выход ко торого подключен к одним из входов формирователей разрядных токов, другие входы которых являются информаци онными входами устройства, введены формирователь заднего фронта импульса линейного тока и регулируемый эл мент задержки, вход которого подклю чен к выходу блока управления, а выход - к входу формирователя заднего фронта импульса линейного тока , выход которого соединен с други входами формирователей линейных токов. На фиг. 1 изображена схема предложенного ЗУ; на фиг. 2 - временная диаграмма его работы. Запоминающее устройство содержит накопитель 1 с элементами памяти 2, каждый из которых состоит из селект рующего 3 и запоминающего -Ц сердечников, объединенных резистивным вит ком связи 5- Элементы памяти 2 прош ты линейными шинами 6, Разрядными ши нами 7 считывания и разрядными шинами 8 записи, которые подключены соответственно к формирователям 9 линейных токов, формирователям 10 разрядных токов со входами 11 и усилителям 12 считывания. Кроме того, ЗУ содержит дешифратор 13 адреса, выходы которого подключены к формирователям 9 линейных токов, и блок 14 управления, выходы которого подключены к формирователям 10 и через регулируемый элемент 15 задержки к формирователю 16 заднего фронта импульса линейного тока. Выход формирователя 16 подключен к формирователям 9 линейных токов. Работа ЗУ осуществляется в три такта - считывание, запись и дозапись (см. фиг. 2) В такте считывания дешифратор 13 запускает один из формирователей 9, который выдает в подсоединенную 9 4 к нему линейную шину импульс ЧИС лового тока 1 , В разрядных шинах 7считывания наводятся импульсы напряжения, соответствующие коду хранимой информации. Эти импульсы усиливаются усилителем 12. Импульс числового тока 1 в избранной линейной шине 6 продолжается также в такте записи и частично в такте дозаписи. Число, подлежащее записи в ЗУ, подается на входы М формирователей 10 в течение тактов записи и дозаписи. 8такте записи запускаются те формирователи 10, на входы которых подан код О, а в такте дозаписи те, на входы которых подан код 1. В момент начала такта дозаписи на вход элемента 15 задержки с блока 1 управления поступает управляющий сигнал i который задерживается элементом 15 задержки на время t и запускает формирователь 16 заднего фронта импульса линейного тока. По сигналу с этого формирователя прег кращает работу избранный формирователь 9 линейного тока. Линейный ток прекращается достаточно быстро, и селектирующий сердечник 3 элементов памяти 2 под действием суммарных токов Ц и IP быстро перемагничивается. Величина задержки элемента 15 ус танавливается по максимальной величине считываемых сигналов. Форсировка перемагничивания селектирующего сердечника в такте дозаписи приводит к увеличению тока в витке связи 5, к более полному перемагничиванию запоминающего сердечника 4 и увеличению амплитуды и стабильности сигнала считанной единицы в последующем такте считывания. Предлагаемое устройство более надежно а эксплуатации. Формула изобретения Запоминающее устройство, содержащее накопитель, элементы памяти которого выполнены на двух сердечниках, объединенных резистивным витком связи и прошитых разрядными шинами записи и считывания и линейными шинами, подключенными соответственно к выходам формирователей разрядных токов, входам усилителей считывания и выходам формирователей линейных токов, одни из входов которых соедийены с выходами дешифратора адреса, блок управления, выход которого подключен к одним из входов формирова телей разрядных токов, другие входы которых являются информационными вхо дами устройства, о т л и ч а.ю щ ее с я тем, что, с«целью повышения надежности ycтpoйctвa, оно содержит формирователь заднего фронта импульса линейного тока и регулируемый эле мент задержки, вход которого подключен к выходу блока управления, а выход - к входу формирователя заднего фронта- импульса линейного тока, выход которого соединен с другими входами формирователей линейных токов. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 275128, кл. G П С П/ОО, 1970. . 2. Авторское свидетельство СССР W kk6}Q7, кл. G П С П/06, 1973 (прототип).

Запись

Авторы

Даты

1982-05-15—Публикация

1980-04-14—Подача