входом седьмого элемента И, вход четвертого элемента запрета соединен с первым входом восьмого элемента И, выходы третьего элемента запрета и восьмого элемента И соединены соответственно с первым и вторым входами двенадцатого элемента ИЛИ, выходы четвертого элемента запрета и седьмого элемента И соединены соответственно с первым и вторым входами тринадцатого элемента ИЛИ, выходы двенадцатого и тринадцатого элементов ИЛИ соединены соответственно с первыми нулевым и единичным входами сумматора по модулю два и первыми входами девятого и десятого элементов И. вторые входы которых соединены с вторым единичным входом сумматора по модулю два, выходы девятого и десятого элементов И соединены соответственно с первым и вторым входами девятого элемента ИЛИ, единичный и нулевой выходы сумматора по модулю два соединены соответственно с первыми входами одиннадцатого и двенадцатого элементов И, вторые входы которых

соединены с выходами четырнадид ого элемента ИЛИ, первый выход ко- его соединен с вторыми входами седы-юго и восьмого элементов И и yпpaвляюIп ми входами третьего и четвертого элементов запрета, вьпходы одиннадцатого и двенадцатого элементов И и вход Умножение устройства соединены соответственно с вторыми входами элементов И групп с первой по шестую, отличающееся тем, что, с целью упрощения, в нем выходы десятого и одиннадцатого элементов ИЛИ соединены соответственно с нулевым (р+1) / /2-1-| и единичным (р+1)/2+2 йходами третьего регистра, первый и второй входы четырнадцатого элемента ИЛИ соединены соответственно с входами Вычитание и Сложение устройства, выходы элементов ИЛИ с первого по четвертый соединены соответственно с нулевым вторым входом сумматора по модулю два, первым входом седьмого элемента И, вторым входом девятого элемента И, первым входом восьмого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для умножения элементов поля Галуа GF(2 @ ) при образующем полиноме F(х)=х @ +Х @ +х @ +х @ +1 | 1989 |

|

SU1716504A1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1983 |

|

SU1121670A1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1999 |

|

RU2173877C2 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1999 |

|

RU2165099C2 |

| Устройство для умножения в системе остаточных классов | 1978 |

|

SU922731A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

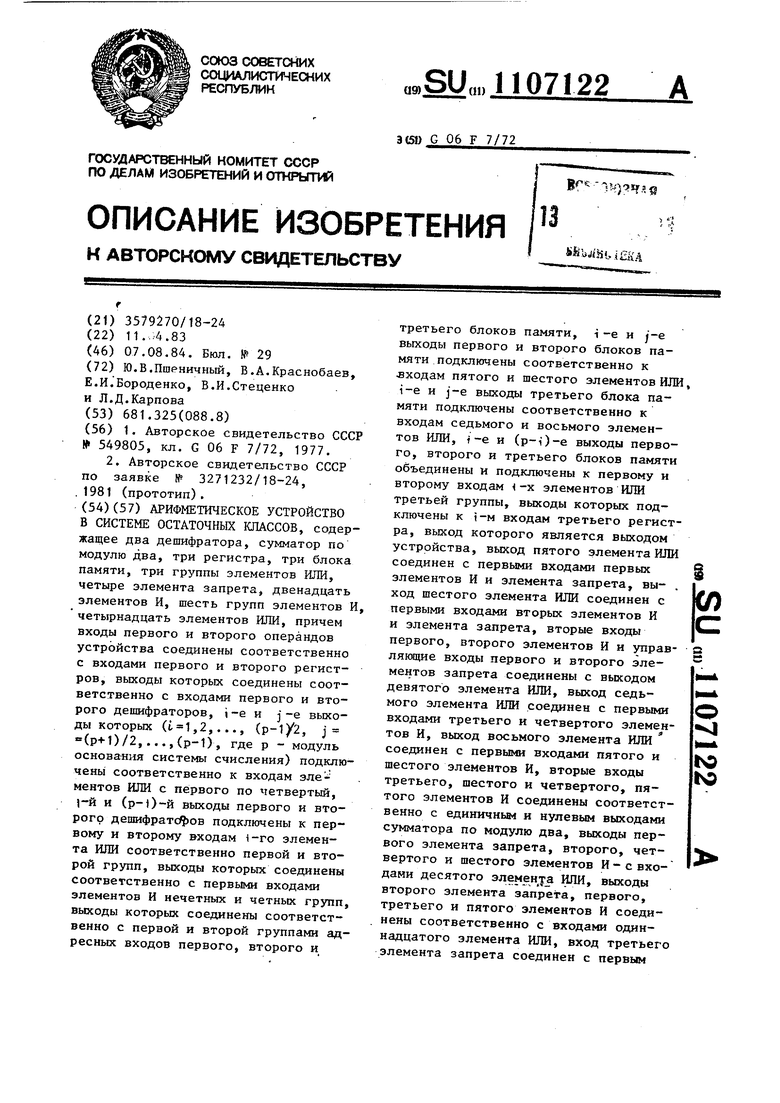

АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ, содержащее два дешифратора, сумматор по модулю два, три регистра, три блока памяти, три группы элементов ИЛИ, четыре элемента запрета, двенадцать элементов И, шесть групп элементов И, четырнадцать элементов ИЛИ, причем входы первого и второго операндов устройства соединены соответственно с входами первого и второго регистров, выходы которых соединены соответственно с входами первого и второго дешифраторов, i-е и j-е выходы которых (i. 1,2,..., (р-1/2, j (р+1)/2,...,(р-1), где р - модуль основания системьг счисления) подключены соответственно к входам ментов ИЛИ с первого по четвертый, 1-й и (р-)-й выходы первого и второго дешифратсфов подключены к первому и второму входам 1-го элемента ИЛИ соответственно первой и второй групп, выходы которых соединены соответственно с первыми входами элементов И нечетных и четных групп, выходы которых соединены соответственно с первой и второй группами адресных входов первого, второго и третьего блоков памяти, i-е и у-е выходы первого и второго блоков памяти подключены соответственно к входам пятого и шестого элементов ИЛИ, i-e и j-e выходы третьего блока памяти подключены соответственно к входам седьмого и восьмого элементов ИЛИ, -е и (p-i)-e выходы первого, второго и третьего блоков памяти объединены и подключены к первому и второму входам -х элементов ИЛИ третьей группы, выходы которых подключены к i-M входам третьего регистра, выход которого является выходом устройства, выход пятого элемента ИЛИ соединен с первыми входами первых элементов И и элемента запрета, вы- . (Л ход шестого элемента ИЛИ соединен с первыми входами вторьсх элементов И и элемента запрета, вторые входы первого, второго элементов И и управлякицие входы первого и второго элементов запрета соединены с выходом девятого элемента ИЛИ, выход седьмого элемента ИЛИ соединен с первыми входами третьего и четвертого элементов И, выход восьмого элемента ИЛИ соединен с первыми входами пятого и IND ю шестого элементов И, вторые входы третьего, шестого и четвертого, пятого элементов И соединены соответственно с единичньм и нулевым выходами сумматора по модулю два, выходы первого элемента запрета, второго, четвертого и шестого элементов И-с входами десятого элемедтра ИЛИ, выходы второго элемента запрета, первого, третьего и пятого элементов И соединены соответственно с входами одиннадцатого элемента ИЛИ, вход третьего элемента запрета соединен с первым

Изобретение относится к вычислительной технике.

Известно арифметическое устройство в системе остаточных классов, содержащее дешифратор, блоки ключей, формирователи, блок определения координат, блоки кодирования 1.

Недостаток данного устройства большой объем оборудования.

Наиболее близким техническим решением к изобретению является арифметическое устройство в системе остаточных классов, содержащее три регистра, два дешифратора, сумматор по модулю два, три блока памяти, три группы элементов ИЛИ, шесть групп элементов И, шестнадцать элементов ИЛИ, шесть элементов запрета, четырнадцать элементов И, причем входы первого, и второго операндов устройства соединены соответственно с входами первого и второго регистров, выходы которых соединены соответственно с входами первого и второго деошфраторов, i-е и j-е выходы которых

(,2,...,(), p-ElL...(p-.) ,

где р - основание системы счисления) подключены соответственно к входам элементов ИЛИ с первого по четвертьш, i-и и (р-О-й выходы первого и второго дешифраторов подключены к первому и второму входам 1-го элемента ИЛИ соответственно первой и второй групп.

выходы которых соединены соответственно с первыми-входами элементов И нечетных и четных групп, выходы которых соединены соответственно с первой и второй группой адресных входов

первого, второго и третьего блоков памяти, i-e и j-е выходы первого и второго блоков памяти подключены соответственно к входам пятого и шестого, элементов ИЛИ, i-e и -е выходы третьего блока памяти подключены соответственно к входам седьмого и восьмого элементов ИЛИ,i-e и (p-i)-e выходы первого, второго и третьего блоков памяти обьединены и подключены к первому и второму входам Н-х элементов ИЛИ третьей группы. выходы которых подключены к i-м входам третьего регистра, выход которого является выходом устройства, выход пятого элемента ИЛИ соединен с первыми входами первых элементов И и с первыми входами вторых элементов И и элемента запрета, вторые входы первого и второго элементов И и управляющие входы первого и второго эле-, ментов запрета соединены с вькодом девятого элемента ИЛИ, выход седь;iioro элемента ИЛИ соединен с первыми входами третьего и четвертого элементов И,выход восьмого элемента ИЛИ соединен с первыми входами пятого и шес того элементов И, вторые входы третьего, шестого и четвертого, пятого элементов И соединены соответственно с единичным и нулевым выходами сумматора по модулю два выходы первого элемента запрета, второго, четвертого и шестого элементов И соединены с,оответственно с входами десятого элемента ИЛИ, выходы второго элемента запрета, первого, третьего и пятого элементов И соединены соответственно с входами одиннадцатого элемента ИЛИ, вход третьего элемента запрета соединен с первым входом седьмого элемента И,, вход четвертого элемента, запрета соединен с первым входом восьмого элемента И, выходы третьего элемента запрета и восьмого элемента И соединены соответственно с первым и вторым входами двенадцатого элемента ИЛИ, выходы четвертого элемента запрета и седьмого элемента И соединены соответственно с первым и вторым входами тринадцатого элемента ИЛИ, выходы двенадцатого и тринадцатого элементов ИЛИ соединены соответственно с первыми нулевьи и единичным входами сумматора по

модулю и первыми входами девятого и десятого элементов И, вторые входы которых соединены с вторым единичным входом сумматора по модулю два, выходы девятого и десятого элементов И соединены соответственно с первым и вторым входами девятого элемента ИЛИ, единичный и нулевой вькоды сумматора по модулю два соединены соответственно с первыми входами одиннадцатого и двенадцатого элементов И, вторые входы которых соединены с выходом четырнадцатого элемента ИЛИ, первый вход которого соединен с вторыми входами седьмого и восьмого элементов И и управляющими входами третьего и четвертого элементов запрета, вход Ум Цель изобретения - упрощение устройства.

45 Поставленная цель достигается Тем, что в арифметическом устройстве в системе остаточных классов, содержащем три регистра, два дешифратора, сумматор по модулю два, три блока

50 памяти, три группы элементов ИЛИ, шесть групп элементов И, четырнадцат элементов ИЛИ, четыре элемента запрета, двенадцать элементов И, причем входы первого и второго операндов

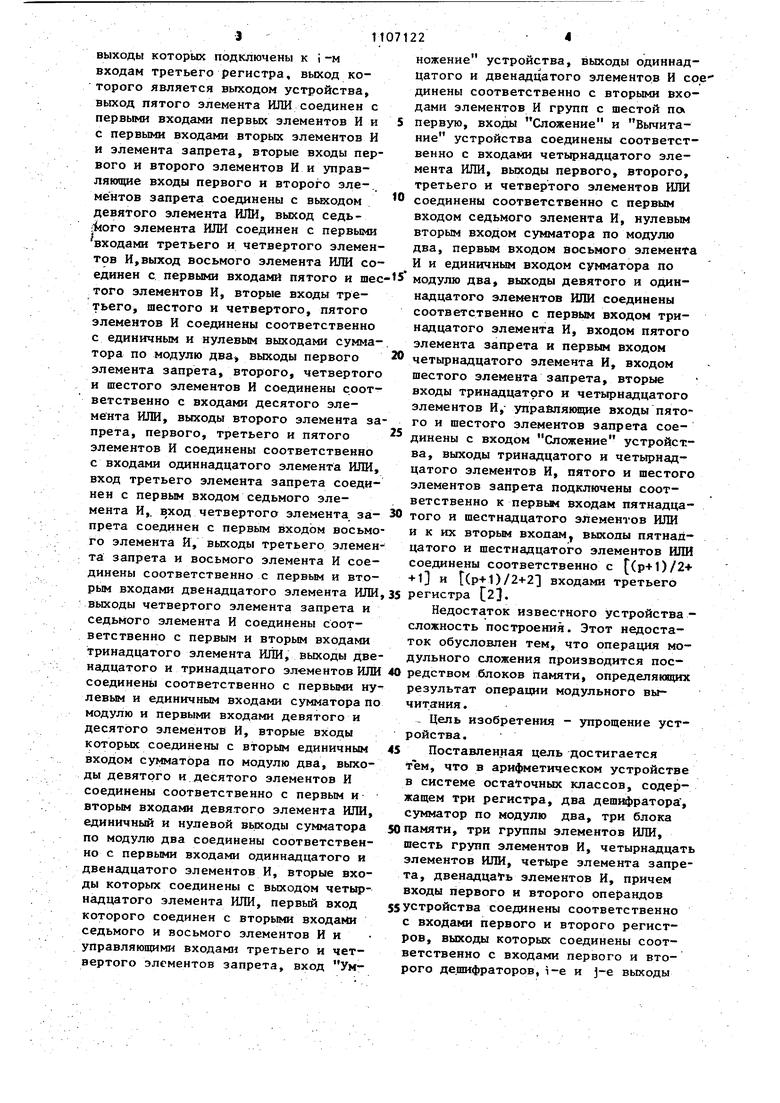

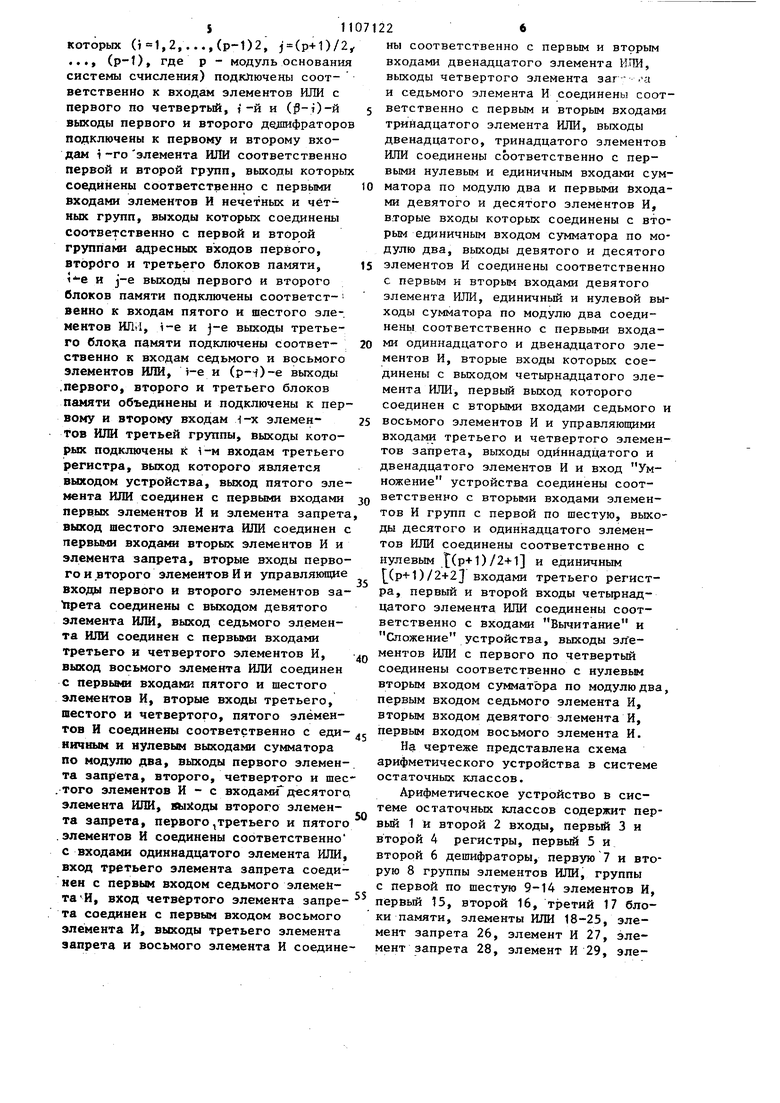

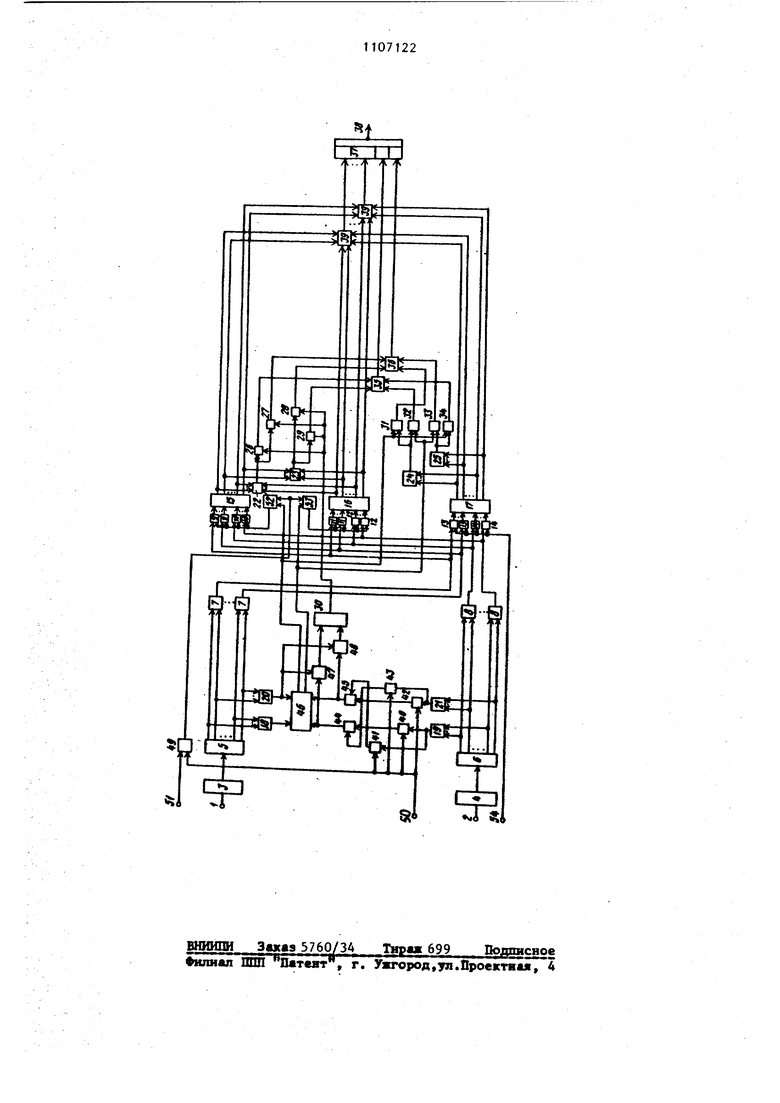

55устройства соединены соответственно с входами первого и второго регистров, выходы которых соединены соответственно с входами первого и второго де.шифраторов, i-e и j-e вькоды ножение устройства, выходы одиннадцатого и двенадцатого элементов И сое динены соответственно с вторыми входами элементов И групп с шестой п первую, входы Сложение и Вычитание устройства соединены соответственно с входами четырнадцатого элемента ИЛИ, выходы первого, второго, третьего к четвертого элементов ИЛИ соединены соответственно с первым входом седьмого элемента И, нулевым вторым входом сумматора по модулю два, первым входом восьмого элемента И и единичным входом сумматора по модулю два, выходы девятого и одиннадцатого элементов ИЛИ соединены соответственно с первьш входом тринадцатого элемента И, входом пятого элемента запрета и первым входом четырнадцатого элемента И, входом шестого элемента запрета, вторые входы тринадцатого и четырнадцатого элементов И,- управляющие входы пятого и шестого элементов запрета соединены с входом Сложение устройства, выходы тринадцатого и четырнад- цатого элементов И, пятого и шестого элементов запрета подключены соответственно к первым входам пятнадцатого и шестнадцатого элементов ИЛИ и к их вторым входам выходы пятнадцатого и шестнадцатого элементов ИЛИ соединены соответственно с (р+1)/2+ + 1} и (p+D/Z+Z входами третьего регистра 21. Недостаток известного устройства сложность построения. Этот недостаток обусловлен тем, что операция мо- дульного сложения производится посредством блоков памяти, определяющих результат операции модульного вьгчитания. которых (,2,. ..,(p-1)2, (рц-1)/2 (), где p - модуль основания системы счисления) подключены соответственно к входам элементов ИЛИ с первого по четвертый, j-и и ( выходы первого и второго дешифраторов подключены к первому и второму входам i-гоэлемента ИЛИ соответственно первой и второй групп, выходы которых соединены соответственно с первыми входами элементов И нечетных и четных групп, выходы которых соединены соответственно с первой и второй группами адресных входов первого, второго и третьего блоков памяти, и j-e выходы первого и второго блоков памяти подключены соответст- веяно к входам пятого и шестого элементов ИП(1, i-e и j-e выходы третьего блока памяти подключены соответственно к входам седьмого и восьмого элементов ИЛИ, i-e и (р-О-е выходы .первого, второго и третьего блоков памяти объединены и подключены к первому и второму входам 1-х элемен тов ИЛИ третьей группы, выходы которых подключены к V-M входам третьего регистра, выход которого является выходом устройства, выход пятого элемента ИЛИ соединен с первыми входами первых элементов И и элемента запрета выход шестого элемента ИЛИ соединен с первыми входавш вторых элементов И и элемента запрета, вторые входы первого и второго элементов И и управляющие входы первого и второго элементов заtipeTa соединены с выходом девятого элемента ШШ, выход седьмого элемента ИЛИ соединен с первыми входами третьего и четвертого элементов И, выход восьмого элемента ИЛИ соединен с первюш входами пятого и шестого элементов И, вторые входы третьего, шестого и четвертого, пятого элементов И соединены соответственно с единичным и нулевым выходами сумматора по модулю два, выходы первого элемента запрета, второго, четвертого и шес . того элементов И - с входами десятого элемента ШШ, выходы второго элемента запрета, первого,третьего и пятого .элементов И соединены соответственно с входами одиннадцатого элемента ШШ вход третьего элемента запрета соеди нен с первым входом седьмого элемента И, вход четвертого элемента запре та соединен с первым входом восьмого элемента И, выходы третьего элемента запрета и восьмого элемента И соедин ны соответственно с первым и вторым входами двенадцатого элемента ИЛИ, выходы четвертого элемента заг .а и седьмого элемента И соединены соответственно с первым и вторым входами тринадцатого элемента ИЛИ, выходы двенадцатого, тринадцатого элементов ИЛИ соединены соответственно с первыми нулевым и единичным входами сумматора по модулю два и первыми Входами девятого и десятого элементов И, вторые входы которых соединены с вторым е.циничным входом сумматора по модулю два, выходы девятого и десятого элементов И соединены соответственно с первым и вторым входами девятого элемента ИЛИ, единичный и нулевой выходы сумматора по модулю два соединены соответственно с первыми входами одиннадцатого и двенадцатого элементов И, вторые входы которых соединены с выходом четырнадцатого элемента ИЛИ, первый выход которого соединен с вторыми входами седьмого и восьмого элементов И и управляющими входаъш третьего и четвертого элементов запрета, выходы одиннадцатого и двенадцатого элементов И и вход Умножение устройства соединены соответственно с вторыми входами элементов И групп с первой по шестую, выходы десятого и одиннадцатого элементов ИЛИ соединены соответственно с нулевым |(р+1)/2+1 и единичным (p+1)/2+2j входами третьего регистра, первый и второй входы четьфнадцатого элемента ИЛИ соединены соответственно с входами Вычитание и Сложение устройства, выходы элементов ИЛИ с первого по четвертый соединены соответственно с нулевьм вторым входом сумматора по модулю два, первым входом седьмого элемента И, вторым входом девятого элемента И, первым входом восьмого элемента И. На чертеже представлена схема арифметического устройства в системе остаточных классов. Арифметическое устройство в системе остаточных классов содержит первый 1 и второй 2 входы, первый 3 и второй 4 регистры, первый 5 и второй 6 дешифраторы, первую 7 и вторую 8 группы элементов ШШ, группы с первой по шестую 9-14 элементов И, первый 15, второй 16, третий 17 блоки памяти, элементы ШШ 18-25, элемент запрета 26, элемент И 27, элемент запрета 28, элемент И 29, эле7110712мент ИЛИ 30,элементы И 31-34, элеменгты ИЛИ 35 и 36, третий 37 регистр, выход 38, третью группу 39 элементов ИЛИ, элемент запрета 40, элемент И 41, элемент запрета 42, элемент И 43, j элементы ИЛИ 44 и 45, сумматор 46 по модулю два, элементы.И 47 и 48, элемент ИЛИ 49, входы50и51 соответственно Вычитание и Сложение, элементы И 52,53, вход 54 Умноже- ю ние. Арифметическое устройство в системе остаточных классов выполняет операции над числами А(Ур,,а) и (fg,6j заданными в коде табличного умноже- 5 ния табл.1 (для ). Таблица 1 ЗГа индексу а- цифра. В качестве таблицы блока 15 памяти, реализующего опедацию модульного сложения при -у Ув используется табл.2 (для ). Таблица 2 567 478 389 2 9 10 л 1 10 О 34 .28 В качестве таблищ) второго блока 16 памяти, реализующего операцию модульного Ьложения для Та Тв используется табл.3 (для ). ТаблицаЗ Результат операции модульного вычи ания определяется посредством блоков 15 и 16 памяти и йредварительного инвертирования второго слагаемого. В качестве таблицы третьего блока памяти, реализующегооперацию модульного з ножения, используется табл.4 (для ). Таблица 4 Наличие выходного сигнала () элемента ИЛИ 30 указывает на необходимость инвертирования индекса при модульном сложении или вычитании.

Работу арифметического устройства целесообразно рассмотреть в трех режимах.

Первый режим - определение резуль тата операции модульного умножения (совпадает с известным устройством).

Первый и второй операнды А и В поступают по входным шинам 1 и 2 на регистры 3 и 4, далее поступают на дешифраторы 5 и 6, с выхода которых они в десятичном коде поступают через группы 7 и 8 злемен ов ИЛИ и группы 13 и 14 элементов И при наличии управляющего сигнала на входе 54 на ; первые и вторые входы блока 17 памяти; выбранная цифра через элемент ты ИЛИ третьей группы 39 поступает в регистр 37. Кроме того, сигналы с выходов депшфратороВ 5 и 6 через элементы ИЛИ 18, 19 или 20, 21 поступают на соответствующие входы сумматора 46 по модулю два. Выходной сигнал с блока 17 памяти поступает на входы элементов ИЛИ 24 или 25 и в зависимости от результата сложения в сумматоре 46 по модулю два индекс поступает через элементы ШМ 35 или 36 на соответствующий вход регистра 37.

Второй режим - определение результата операции модельного сложения.

Первый А и второй В операнды в двоичном коде по входным шинам 1 и 2 заносятся соответственно во входные регистры 3 и 4 и далее поступают на соответствующие дешифраторы 5 и 6, с выходов которых операнды et и в десятичном коде через соответствующие элементы ИПИ 7 и 8 поступают на соответствукицие элементы И групп 9-12

Пусть-г -jTn , тогда сигнал нулевого выхода сумматора 46 открывает элемент И 53, выходной сигнал которого открывает элементы И 11 и 12. Ьыходной сигнал блока 16 памяти, соответствующий результату операции, через соответствукядий элемент ИЛИ 39 поступает на соответствующий вход регистра 37, одновременно этот сигнал поступает на вход элемента ИЛИ 22 или 23. При наличии выходного сигнала элемента ИЛИ 30 сигнал, соответствующий результату операции, через элементы И 27 или 29, элементы ИЛИ 35 или 36 поступает на нулевой или единичньй вход регистра 37. сигнал, соответствующий результату операции, через элементы запрета 26 или 28, элементы ИЛИ 35 и 36 поступает на нулевой или единичный вход регист ра 3 7.

Пусть jv 4 y/jf тогда сигнал единичного выхода сумматора 46 открывает элемент И 52, выходной сигнал которого открывает элементы И групп 9 и 10. В этом случае результат операции определяет блок 15 памяти.

Третий режим - определение результата операции модульного вычитания.

В этом режиме сигнал управления подается на вход 50, поступает на вход элемента ИЛИ 49 и, кроме того, инвертирует значение индекса fa второго операнда.

Далее работа арифметического устройства идентична работе устройства во втором режиме.

Техническое преимущество изобретения по сравнению с прототипом состоит в сокращении на щесть элементов количества оборудования при сохранении всех функциональных возможностей.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Арифметическое устройство в системе остаточных классов | 1973 |

|

SU549805A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3271232/18-24, .1981 (прототип). | |||

Авторы

Даты

1984-08-07—Публикация

1983-04-11—Подача