Изобретение относится к вычислительной технике, в частности к технологии изготовления полупроводниковых интегральных схем, и может быть использовано для изготовления матричного накопителя для электрически пе репраммируемого постоянного запоминающего устройства, сохраняющего информацию при отключении источника питания, на лавинно-ннжекционных транзисторах с плавающими и управляющими затворами, перепрограммииуе- мых импульсами напряжения.

Цель изобретения - увеличение количества циклов перепрограммирования элемента памяти.

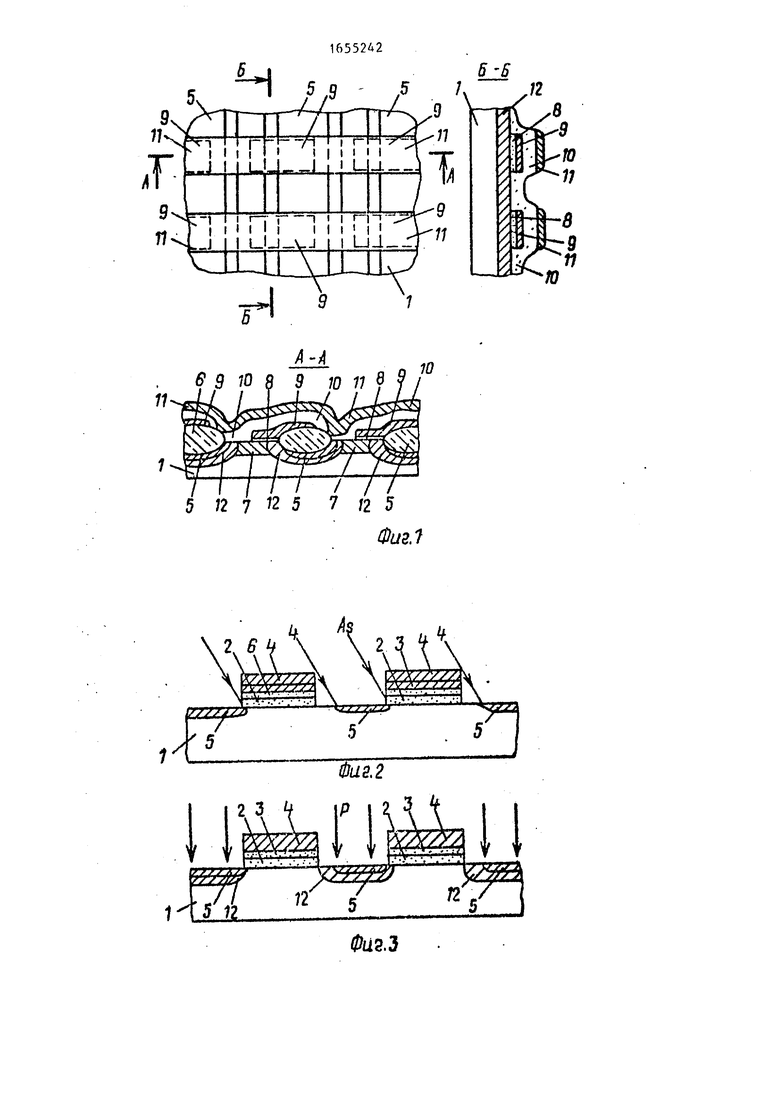

На фиг. 1 представлены топология и разрезы структуры элемента памяти на фиг.2-5 - разрезы структуры элемента памяти на различных стадиях его изготовления.

Элемент памяти содержит полупро- тзодннковую подложку 1, слой 2 из двуокиси кремния маски, слой 3 из нитрида кремния маски, слой 4 фоторезиста маски, первую и вторую диффузионные области 5 второго типа проводимости с высокой концентрацией примеси (разрядные диффузионные шины), первый диэлектрический слой 6 из двуокиси кремния, третью диффузионную область 7 первого типа

& ел

СП N9

4ь

to

проводимости с низкой концентрацией примеси, второй диэлектрический слой 8 из двуокиси кремния, проводящую область 9 из легированного поликрем- ния, третий диэлектрический слой 10 из двуокиси кремния, проводящей слой It нз легированного полнкремния, четвертую и пятую диффузионные области 12 второго типа проводимости с низкой концентрацией примеси.

Элемент памяти состоит из лавин- но-инжекционного электрически программируемого запоминающего транзистора с плавающим и управляющим затво- рани, включенного последовательно с адресным МДП-транзнстором, с электрически программируемым конденсатором, включенным между плавающим затвором и стоком запоминающего тран- зистора.

Поликремнневые области 9 являются плавающими затворами запоминающих транзисторов, поликремниепые слон 1 I - их управляющими затворами, разрядные диффузионные шины - их стоками . Адресные поликремниевые шины также являются затворами адресных ТЩП-тран- зистороп, разрядные диффузионные шины - их истоками и обкладками электрически программируемых конденсаторов .

Работа матричного накопителя на элементах памяти заключается в следующем. Для одновременного (разрядного) стнрания информации на все выбранные разрядные шицы подают вы- сокое положительное импульсное напряжение (12 В, 1 с). На адресные поликремниевые шины или невыбранные разрядные шины подают нулевое напряжение относительно полупроводниковой подложки 1.

Под действием высокой напряженности электрического поля во втором диэлектрическом слое 8 электроны инжектируются с нижней поверхности полнкремниевых областей 9, туннеян- руют через второй диэлектрический слой 8 и удаляются через разрядные диффузионные шипы. В результате этого пороговые напряжения запоминающих транзисторов становятся отрицтельными, что эквивалентно единичному проводящему, состоянию в режиме считывания информации

В режиме программирования иифор- нации на выбранную адресную поликрем

, o

5 0

5 о

Q

45 JQ

5

ниевую гаину и выбранные разрядные диффузионные шины подают высокое положительное импульсное напряжение (12 В, 1 мс), на соседние разрядные диффузионные шины, остальные адресные шины подают нулепое напряжение, на остальные разрядные диффуэионные шины- низкое положительное напряжение.

При протекании тока через открытые выбранные запоминающие транзисторы и адресные МДП-транзисторы за счет высокой напряженности стокового электрического поля выбранных запоминающих транзисторов горячие электроны инжектируются из каналов этих транзисторов, чахпатываются поликремнн- евымн областями, что приводит к повышению их пороговых напряжений. Это эквивалентно нулевому непроводящему состоянию в режиме считывания информации.

Состояния остальных невыбранных запоминающих транзисторов сохраняются неизменными из-за нулевого напряжения на адресных иоликремниевых шинах или низкого напряжения на разрядных диффузионных шинах, в результате чего отсутствует ннжекция горячих электронов в их каналах.

В режиме считывания информации па адресные поликремниевые шины и разрядные диффузионные шины подают более низкое (5 В) напряжение относительно полупроводниковой подложки 1г чем при программировании информации.

Через выбранные запоминающие транзисторы ток не протекает (протекает) , если они находятся в нулевом (единичном) состоянии. Через невыбранные запоминающие транзисторы Ток не протекает.

ь

При изготовлении элемента памяти на поверхность полупроводниковой подложки 1 первого типа проводимо- стн наносят маску нз диэлектрического слоя 2 из двуокиси кремния, диэлектрического .слоя 3 из нитрида крем-; ния, слоя 4 фоторезиста.

Легируют примесью с высокой кои-., цевтрацпей под углом к поверхности нолупроводнтсовой подложки и п плоскости, перпендикулярной продольным , отверстиям в маске, до образования первой и второй диффузионных обла- стей 5 второго типа проводимости, разрядных диффузионных шин,удаленных от первых краев маски (фиг.2). После

1

этого легируют примесью о низкой ои центрацнеП через отверстия маски ло обраэовапил четвертой и пятой диффузионных областей 12 второго типа проводимости (фнг. О.

После удаления слол 4 фоторезиста маски наносят первый диэлектрический слой 6 из двуокиси кремния локальным окислением кремниевой полупроводниковой подложки 1, удаляют маску. Проводят легирование примесью с низкой концентрацией до образования третьей диффузионной области 7 первого типа проводимости (фиг.4).

На поверхность полупроводниковой подложки 1 наносят второй диэлектрический слой 8 из двуокиси кремния малой толщины. На поверхности первого и второго диэлектрических слоев 6, 8 наносят первый поликремниевый легированный слой 9, формируют в нем поликремниевые шины (фиг.5).

На поверхности поликремниевых шин полупроводниковой подложки 1 наносят третий диэлектрический слой 10 из двуокиси кремния, на поверхность которого наносят второй легированный слой 11 из поликремння, формируют в Нем адресные полнкремниевые шипы, торцы в диэлектрическом слое 8 и из поликремниевых шин - поликремниевые электроды, совмещенные с краями адресных поликремииевых шин (фиг.1).

Формула изобретения

1. Элемент памяти для постоянного запоминающего устройства, содержащий полупроводниковую подложку первого типа проводимости, первую и вторую диффузионные области второго типа проводимости, расположенные в приповерхностном слое подложки, первый диэлектрический слой, расположенный на поверхности подложки над первой и второй диффузионными областями, третью диффузионную область первого типа проводимости, расположенную в приповерхностном слое подложки между первой и второй диффузионными областями, второй диэлектрический слой, расположенный на поверхности подлож.S242 6

ки над третьей диффузионной облястью, проводящую область, расположенную на поверхности первого и второго дн- , электрических слоев, третий диэлектрический слой, расположенный на поверхности подложки над третьей диффузионной областью и на поверхности проводящей области, проводящий слой,

10 расположенный на поверхности третьего диэлектрического слоя, отличающийся тем, что, с целью увеличения количества циклов перепрограммирования элемента памяти,

15 ол содержит четвертую и пятую диффузионные области второго типа проводимости, расположенные п приповерхностном слое полупроводниковой подложки между первой и третьей и между вто рои и третьей диффузионными областями соответственно с примыканием к их краям, второй диэлектрический слой расположен на поверхности четвертой и пятой диффузионных областей, первый

25 диэлектричесюгй слой расположен с

перекрытием краев первой и второй диффузионных областей.

2. Способ изготовления элемента памяти для постоянного запоминающего

30 устройства, включающий последовательное нанесение на поверхность полупроводниковой подложки слоев двуокиси кремния, нитрида кремния, фоторезиста, образующих маску, формирование

35 первой и второй диффузионных областей селективным легированием по маске, удаление слоя фоторезиста маски, формирование первого диэлектрического слояселективным окислением по маске,

40 последовательное удаление слоев нитрида кремния и двуокиси кремния маски, формирование третьей диффузионной области, нанесение второго диэлектрического слоя, формирование

5 проводящей области из легированного полнкремния, отличающийся тем, 4Tos что при формировании первой и второй диффузионных областей легирование проводят под углом к поверх0 ности полупроводниковой подложки, а затем формируют четвертую и пятую диффузионные области селективым легированием по маске.

7И5

Qs T

Ю

сл

4

Т

,05

ш т

Ю

0}

/

B K- °

fu

:з

cv

3

tr

5 П 7

Изобретение относится к вычислительной технике, в частности к технологии изготовления полупроводниковых интегральных схем, и может быть использовано для изготовления матриц - кого накопителя длл электрически перепрограммируемого ПЗУ, сохраняющего информацию при отключении источника питания, на лавинно-ннжекционных транзисторах с плавающими и управляю-- щими затворами, перепрограммируемых импульсными напряжениями. Целью изобретения является увеличение количества циклов перепрограммирования элемента памяти. Поставленная цель достигается легированием примесью с высокой концентрацией до образования первой и второй диффузионных областей второго типа проводимости под углом к поверхности полупроводниковой подложки и в плоскости, перпендикуляр- . пой продольным отверстиям в маске, после чего проводят легирование примесью с низкой концентрацией через отверстия маски до образования чет- . вертой и пятой диффузионных областей второго типа проводимости. 5 ил. (Л С

| СПОСОБ ВЫТАПЛИВАНИЯ ЖИРОВ | 0 |

|

SU286121A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР # 1535231, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

Авторы

Даты

1992-09-23—Публикация

1989-08-30—Подача