1

Изобретение относится к вычисли- , тельной технике и цифровой автомати- ке и может использоваться в ЭВМ, вычислительных устройствах, например, контроллерах периферийных устройств, и приборах цифровой автоматики для приема, хранения, выдачи, стирания и сжатия информации при обработке.данных. Обычно стековая память используется при организации обращений к стандартным подпрограммам, при обработке прерываний и для временного хранения информации (в качестве буфера данных)

Известна информгщионная магазинная память, содержащая сдвиговой регистр из N запоминающих каскадов, гщресный счетчик по модулю N, схемы ввода и вывода. В режиме записи информационные единицы, хранимые в сдвиговом регистре, сдвигаются на один каскад/ а адресный счетчик изменяет свое состояние на одну единицу. Таким образом, реализуется запоминёнощее устройство по принципу первый вошелпервый запел iD.

Недостатком известного устройства является то, что отсутствует возможность внести изменения в заданную последовательность информационных слов, хранящихся в нем.

Наиболее близкой по технической сущности к Изобретению вляется стековая память, содержащая блок регистров, группу элементов ИЛИ, первую группу элементов И, регистр управления, инверсные выходы разрядов которого соединены соответственно с первыми входами элементов И первой группы, инверсный выход первого разряда

10 этого регистра, кроме того, соединен с первым выходом стековой памяти, прямые выходы разрядов регистра, начиная с первого и кончая предпоследним, соединены соответственно со вто15рыми входами элементов И первой группы, начиная со второго и кончая последним, прямой выход последнего разряда регистра управления соединен со вторым выходом стековой памяти, вто20рой вход первого элемента И первой группы соединен с первым входом стековой памяти, а выходы элементов И первой группы соединены с первыми входами соответствующих разрядов ре25гистра управления и с первыми входами соответствующих регистров блока регистров, вторые входы каждого регистра начиная со второго и кончая последним соединены с прямыми выходами

30 предыдущего регистра, а вторые входы

первого регистра блока регистров соединены со второй шиной входов стековой памяти, прямые выходы последнего регистра соединены с соответствующими выходами третьей шины, выходы элементов И первой группы, кроме того, начиная со второго и кончая последним, соединены соответственно с первыми входами элементов ИЛ, группы, начиная с первого и кончая предпоследним, первый вход последнего элемента ИЛИ группы соединен с третьим входом стековой памяти, выходы элементов ИЛИ группы соединены со вторыми входами соответствующих разрядов регистра управления, а вторые входы элементов ИЛИ группы соединены с четверты входом стековой памяти. Каждому регистру блока регистров соответствует определенный триггер в регистре управления, причем единичное состояние этого триггера указывает, что в соответствующем регистре блока регистров имеется достоверная информация. Если триггер управления находится в нулевом состоянии, то это означает, что в соответствующем регистре блока регистров отсутствует достоверная информация и в этот регистр может быть записана информация с регистра блока регистров, имеющего адрес на единицу меньше, или со второй шины входов стковой памяти L2.

Недостатком известного устройства являются узкие функциональные возможности. Оно не позволяет вносить каких-либо изменений в последовательность считываемых информационных слов, которая задается при записи.

Цель изобретения - расширение функциональных возможностей за счет возможности считывания и стирания информации из произвольного регистра стековой памяти.

Указанная цель достигается тем, что в стековое запоминающее, устройство, содержащее блок регистров, одни входы которого являются информационными входами устройства, элементы И первой группы, первый вход одного из которых является первым управлякицим входом устройства, а первые входы других элементов И первой группы подключены к соответствующим первым выходам регистра управления, вторые входы элементов И первой группы подключены ко вторым выходам регистра управления, первые входы которого подключены к выходам элементов И первой группы, элементы ИЛИ, первый вход одного из которых является вторым управляющим входом устройства, а первые входы других элементов ИЛИ подключены к соответствующим выходам элементов И первой группы, вторые входы элементов ИЛИ объединены и являются третьим управляющим входом устройства, в него дополнительно введены коммутатор, информационные входы которого подключены к выходам блока регистров, а выходы являются выходами устройства, управляющие входы коммутатора соединены с соответствующими выходами регистра управления, адресный дешифратор, выходы которого подключены к соответствующим управляющим входам коммутатора, а входы являются адресными входами устройства, элемент НЕ, выход которого подключен к соответствующему управляющему входу коммутатора, а его вход подключен к у: равляющему входу адресного дешифратора и является четвертым управляющим входом устройства элементы И второй группы, первые входы которых подключены к выходам элементов ИЛИ, вторые входы - к выходу элемента НЕ , а выходы - ко вторым входам регистра управления, третьи входы элементов ИЛИ являются группой управляющих входов устройства.

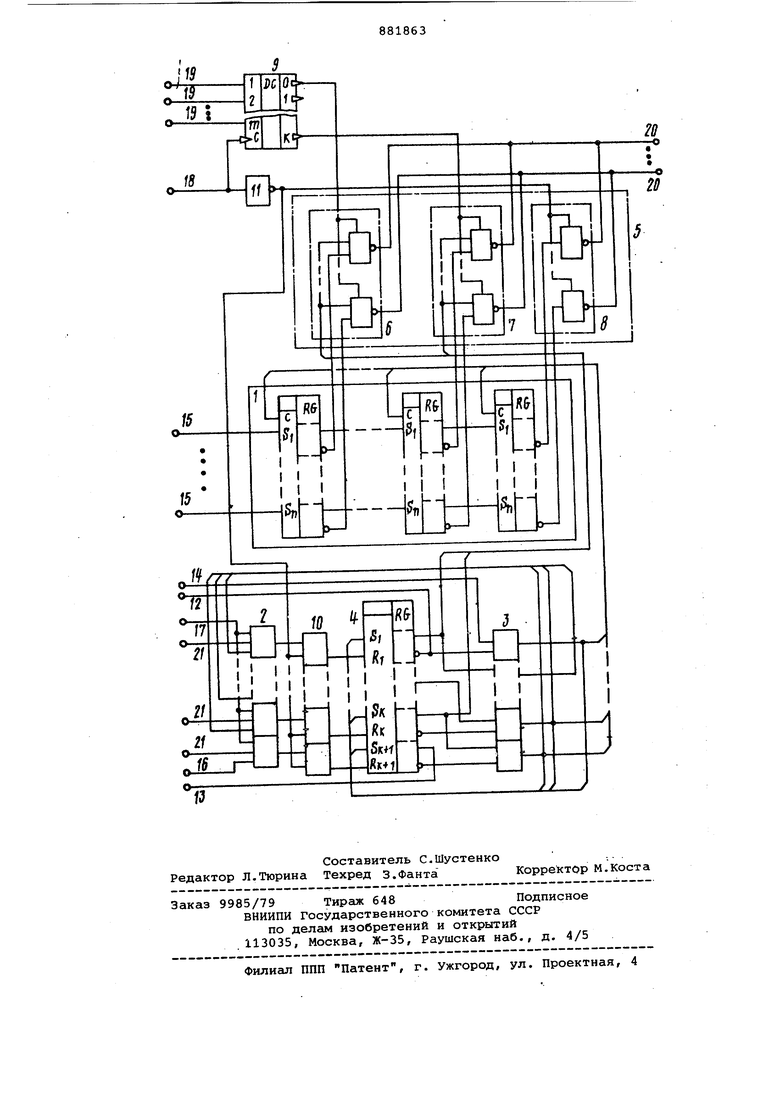

На чертеже представлена схема стекового запоминающего устройства. Стековое запоминающее устройство содержит блок 1 регистров, группу элементов ИЛИ 2, первую группу элементов И 3, регистр управления 4, коммутатор 5, включающий первую группу элементов И-НЕ 6, предпоследнюю группу элементов И-НЕ 7, последнюю группу элементов И-НЕ 8, а также адресный дешифратор 9, вторую группу элементов И 10, элемент НЕ 11, первый выход 12 (команда Готовность к приему), второй выход 13 (команда Готовность к выдаче), первый управляющий вход 14 (команда Разрешение приема), информационные входы 15, второй управляквдий вход 16 (команда Выход прочитан), третий управляющий вход 17 (команда Общий сброс), четвертый управляющий вход 18 (команда Считывание), адресные входы 19, информационные выходы 20, группу управляющих входов 21 (команда Селективный сброс).

Блок 1 регистров предназначен для приема, хранения и продвижения информации в стековой памяти. Группа элементов ИЛИ 2 предназначена для выполнения логической операции ИЛИ при установке в нулевое состояние всего регистра управления 4 или селективно отдельных его триггеров. Первая группа элементов И 3 формирует команды приема информации в соответствукицие регистры блока 1 регистров и команды установки триггеров регистра управления 4 в соответствующие состояния. Регистр управления 4 содержит столько триггеров, сколько регистров в блоке 1 регистров, и преназначен для управления приемом и продвижением информации в стековой памяти. Коммутатор 5, состоящий из групп элементов И-НЕ 6-8, количество которЬис соответствует количеству регистров в блоке 1 регистров, обеспечивает считывание информации с того регистра блока 1 регистров, адрес которого подан на вход адресного дешифратора 9, Вторая группа элементов И 10 обеспечивает блокировку цепей сброса в нулевое состояние триггеров регистра управления 4 при считывании информации из стековой памяти. Элемент НЕ 11 обеспечивает инвертирование входной команды Считывание подаваемой на четвертый управляющий вход 18, которая определяет режим работы устройства. Стековое запоминающее устройство работает следующим образом. Имеется три основных режима работы. В первом режиме устройство работает как обычная стековая память с принципом функционирования первый вошел - первый вышел. При этом на четвертый вход 18 подается низкий уровень напряжения, что соответствует отсутствию команды Считывание от внешнего источника. На выходе эле мента НЕ 11 устанавливается высокий потенциал, который подается на управ ляющие входы последней группы элементов И-НЕ 8 коммутатора 5, тем самым на информационные ВЕДХОДЫ 20 все да подаются выходы последнего регист ра блока 1 регистров. Кроме того, низкий уровень напряжения команды Считывание, подаваемый на синхрони зирующий вход адресного дешифратора 9, блокирует работу последнего, а поэтому на всех выходах дешифратора устанавливаются низкие уровни напря жения, которые подаются на соответствующие управляющие входы групп эл ментов И-НЕ 6 и 7 коммутатора 5, ус танавливая все выходы последних в третье состояние (высокоимпедансное что позволяет объединить одноименны выходы всех групп элементов И-НЕ 6 8 коммутатора 5. Входная п-разрядная информация подается от внешнего источника через информационные входы 15 на первый регистр блока 1 регистров. Продвижение информации в стековой памяти определяется состоя нием триггеров регистра управления 4. Например, если в i-том триггере регистра управления 4 записана еди ница, то информация,находящаяся в соответствующем i-том регистре блок регистров 1, является достоверной. Если информация из i-того регистра переписана в (+1)-ый регистр, то i-ый триггер в регистре управления 4 может быть установлен в нуль и информация в i-том регистре может быть заменена на информацию, находя щуюся в (i-l)-OM регистре и т.д. до первого.триггера регистра управления 4, инверсный выход которого подается на первый выход 12 как коман да Готовность к приему информации Если блок регистров 1 полностью заполнен информацией, то на первом вы ходе 12 низкий потенциал напряжения {команда Готовность к приему). Если поданная входная информация провалилась через весь блок регистров в последний регистр, то последний (К+1)-ый триггер регистра управления 4 устанавливается в единичное состояние и на второй выход 13 выдается команда Готовность к выдаче. Если с информационных выходов 20 информация принята внешним приемником, то последний в стековую память выдает по второму управляющему входу 16 команду Выход прочитан, которая подается через последний элемент группы элементов ИЛИ 2 и последний элемент И второй группы элементов И 10 на второй вход (К+1)-го триггера регистра управления 4, устанавливая последний в нулевое состояние, что разрешает запись в (К+1)-ый регистр блока регистров 1 и.нформа1;ии из Ктого регистра, з К - тый из (К-1)-го и т.д. до первого регистра блока 1 . регистров, когда инверсный выход первого триггера регистра управления 4 выдается на первый выход 12 как команда Готовность к приему, указывая источнику входной информации, что стековая память готова к приему информации. Источник входной информации, приняв команду Готовность к приему, выдает на первый управляющий вход устройства 14 команду Разрешение приема , по которой информация с информационных входов 15 принимается в первый регистр блока регистров 1 и далее асинхронно пересылается в стековой памяти до первого занятого регистра, которогчту соответствует единичное состояние триггера в регистре управления 4, Общий сброс стековой памяти производится подачей низкого потенциала (команда Общий сброс) на третий управляющий вход 17. Во втором режиме работы устройства (режим Считывание) на адресные входы 19 подается в двоичном коде адрес регистра, с которого должна быть считана информация, который поступает на входы сщресного дешифратора 9, а на четвертый управляющий вход 18 подается высокий уровень напряжения, что соответствует наличию команды Считывание, которая поступает на вход элемента НЕ 11 и синхронизирующий вход потенциально-импульсного адресного дешифратора 9. Только на одном выбранном выходе адресного дешифратора устанавливается высокий уровень напряжения, который подается на управляющие входы соответствующей группы элементов И-НЕ коммутатора 5, разрешая выдачу на информационные выходы 20 информации с выходов регистра, адрес которого был задан на входе адресного дешифратора 9. При этом на управляющие входы всех групп элементов И-НЕ, кроме выбранной, подаются низкие уровни напряжений с выхода адресного дешифратора 9, а на последнюю группу 8 - с выхода элемента НЕ 11, которые выходы всех этих групп элементов И-НЕ переводят в-третье состояние (высокоимпедансное). Кроме того, команда Считывание, подаваемая с выхода элемента НЕ 11 на первые входы второй группы элементов И 10, блокирует изменение значений триггеров регистра управления 4 на время считывания информации из устройства, т.е. блокируется прод вижение информации в блоке 1 регистров в направлении от первого регистра к последнему. После снятия команды Считывание автоматически устанавливается первый режим работы. Третий режим работы устройства (режим Сжатие) может работать тол ко совместно с первым режимом работы. При этом на любой из группы управляющих входов селективно может быть подан высокий уровень напряжения, который устанавливает соответст вукадий триггер регистра управления 4 в нулевое состояние, которое указы вает, что информация в соответствующем регистре блока 1 регистров недостоверная и может быть заменена информацией, содержащейся в регистре адрес которого на единицу меньше. Заметим, что при этом происходит сжатие информации в устройстве без изменения заданной последовательнос ти, что обеспечивает более рационгшь ноё использование объема стековой п мяти . По сравнению с известным предлагаемое устройство позволяет считывать информацию из любого регистра стековой памяти и селективно стирать информацию из любого регистра. При стирании происходит сжатие информации без нарушения последовательности, с которой она была записана. Расширение функциональных возможностей стекового запоминающего устройства позволяет эффективно использовать его при цифровой обработке сиг налов, при построении мультиплексор ных и мультиблочных систем обработки данных. Формула изобретения Стековое эапоминакадее устройство, содержащее блок регистров, одни входы которого являются информационными входами устройства, элементы И первой группы, первый вход одного из которых является первым управляющим входом устройства, а первые входы других элементов И первой группы подключены к соответствующим первым входам регистра управления, вторые входы элементов И первой группы подключены ко вторым выходам регистра управления, первые входы которого подключены к выходам элементов И первой группы, элементы ИЛИ, первый вход одного из которых является вторым управляющим входом устройства, а первые вхоДы других элементов ИЛИ подключены к соответствующим выходам элементов И первой группы, вторые входы элементов ИЛИ объединены и являются третьим управляющим входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет возможности считывания и стирания информации из произвольного регистра, в него введены коммутатор, информационные входы которого подключены к выходам блока регистров, а выходы являются выходами устройства, управляющие входы коммутатора соединены с соответствующими выходами регистра управления, адресный дешифратор, выходы которого подключены к соответствунхцим управляющим входам коммутатора, а входы являются сщресными входами устройства, элемент НЕ, выход которого подключен к соответствующему управляющему входу коммутатора, а его вход подключен к управляющему входу адресного дешифратора и является четвертым управляющим входом устройства, элементы И второй группы, первые входы которых подключены к выходгии элементов ИЛИ, вторые входы к выходу элемента НЕ, а выходыко вторым входам регистра управления, третьи входы элементов ИЛИ являются группой управляквдих входов устройства. Источники информации, принятые во внимание при экспертизе 1.Патент США 3992699, кл. G 11 С 19/00, 1976. 2.Am 3341/2841. 64 х 4 bits first - in first - out memories. Advanced Micro Devices Inc., 1974, p.p. 5.51. - 5.56 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для отладки программ | 1979 |

|

SU849218A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для обмена информацией | 1979 |

|

SU826328A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Устройство управления обращением к подпрограммам | 1984 |

|

SU1273929A1 |

Авторы

Даты

1981-11-15—Публикация

1979-12-07—Подача