«

а

Кг-эналов. Устройство солержит блок 1 микропрограммного управления, входной 2 регистр, Быходнор 1 регистр А, коммутатор 14, блок 17 управления, 6JTOK IP, приоритета запросов, группу блоков согласования 19, регистр 23 заданий, узел 24 коммутации, блок 25

приоритетных шифраторов, блок 26 регистров, узел 27 дешифраторов, две группы 15, 16 регистров, две группы 5, 2П элементов И-ИШ, два триггера 7, 11, элемент ИЛИ 12, два элемента И 6, 13, два элемента И-НЕ 8, 1П. 10 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для распределения подканалов | 1981 |

|

SU1003065A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для назначения подканалов | 1984 |

|

SU1264189A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

Изобретение относится к области вычислительной техники и может быть использовано при разработке процессоров, оборудование которых используется при передаче данных между каналами ввода-вывода и оперативной памятью или системах ввода-вывода. Целью изобретения является расширение . функциональных возможностей устройства за счет организации общего поля подканалов с целью гибкой адаптации к условиям пользователя как в части эффективного использования объемов памяти, предназначенной для хранения подканалов, так и в части возможности подключения того или иного количества периферийных устройств к каждому каналу ввода-вывода из группы

1

Изобретение относится к вычисли,тельной технике и может быть использовано при разработке процессоров, оборудование которых используется при передаче данных между каналами ввода-вывода и оперативной памятью или в системах ввода-вывода.

Цель изобретения - расширение функциональных возможностей устройства путем организации общего поля подканалов для обеспечения гибкой адаптации к условиям пользователя как в части эффективного использования объемов памяти, предназначенной для хранения подканалов, так и в части возможности подключения того или JHHoro количества периферийного устройства к каждому каналу ввода-вывода из группы каналов.

Регистр заданий содержит п-разрядный регистр и группу из п переключателей, причем выход п-разрядного регистра соединен с информационными выходом узла, первый контакт каждого переключателя из группы подключен к входу соответствующего разряда п-разрядного регистра, а вторые контакты п-переключателей соединены с землей.

Введение в устройство регистра за. даний дает возможность индивидуально для каждого пользователя выбирать и устанавливать необходимый и оптималь-ны; объем памяти для хранения подканалов.

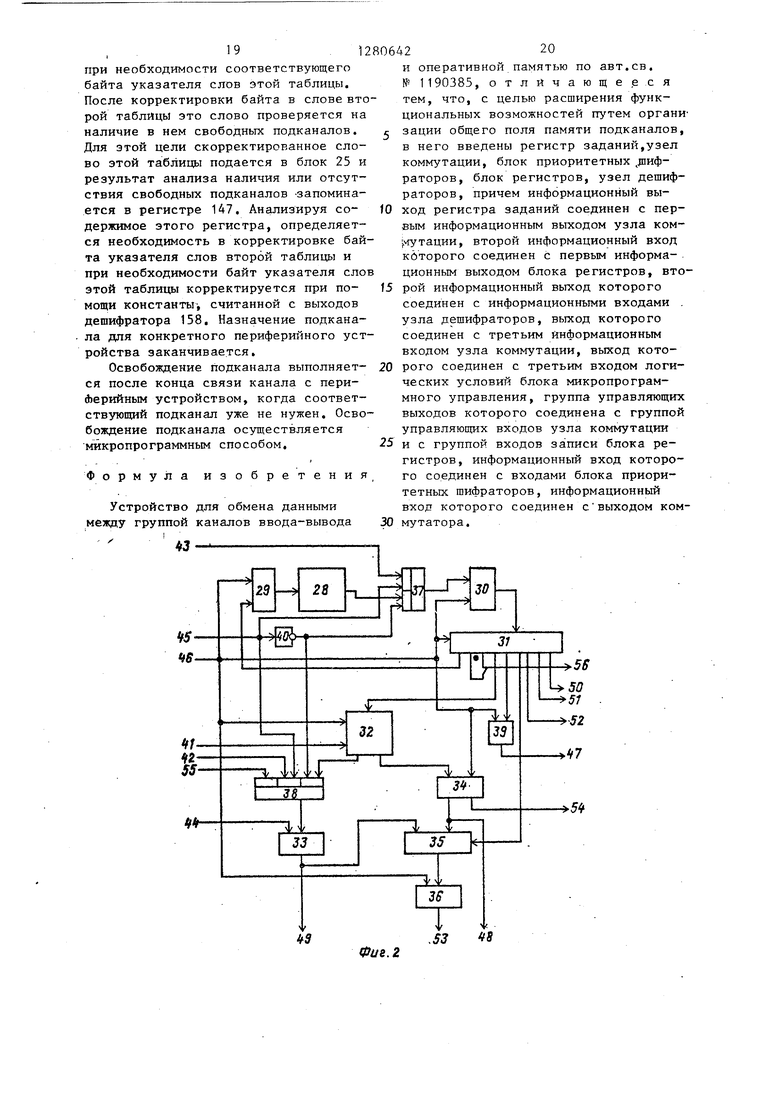

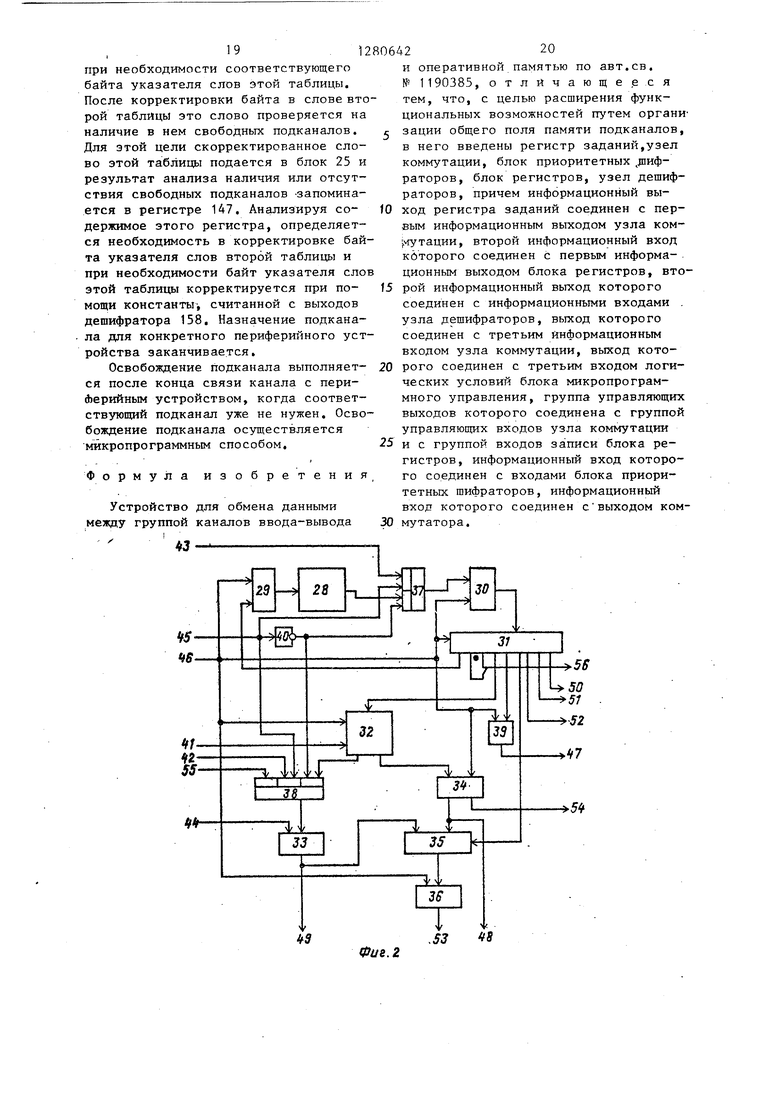

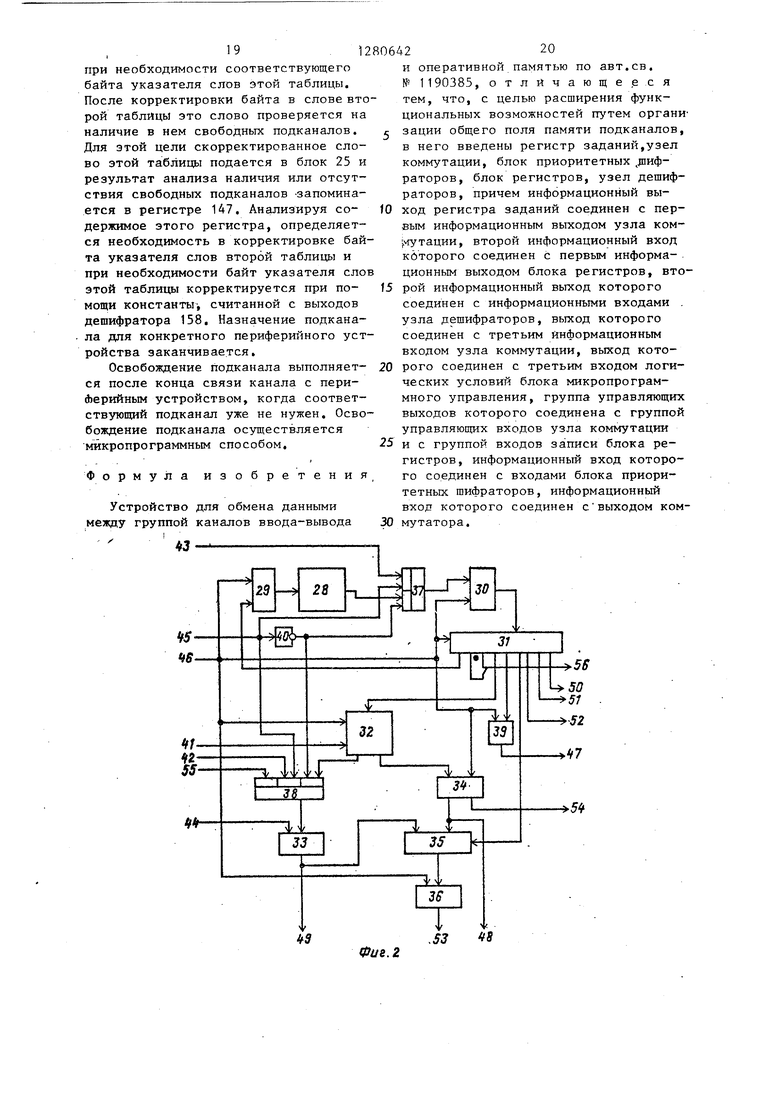

На фиг.1 изображена структурная схема устройства для обмена данными между группой каналов ввода-вывода и оперативной памятью; на фиг.2 - функциональная схема блока микропрограммного управления; на фиг.З - функциональная схема блока управления; на фиг.4 - функциональная схема блока .согласования; на фиг,5 - функциональная схема блока приоритетных шифраторов; на фиг.6 - функциональная схема блока регистров; на фиг«7 - функциональная схема узла дешифратора; на фиг.8 - временная диаграмма выполнения микрокоманды ПАМЯТЬ при обращении к ней процессора; на фиг.9 - временная диаграмма выполнения микрокоманды Память считывания из оперативной памяти в каналы; на фиг.10 - временная диаграмма выполнения микрокоманды Память записи в оперативную память из каналов.

Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью содержит блок 1 микропрограммного управления, входной регистр 2, оперативную память 3, выходной регистр 4, элемент И-ИЛИ 5 первой группы, первый элемент И 6, первый триггер 7, первый элемент И-НЕ 8, третий триггер 9, второй элемент И-НЕ 10, второй триггер 11, элемент ИЛИ 12, второй элемент И 13, коммутатор 14, регистры 15 и 16 первой и второй группы соответственно, блок 17 управления, блок 18 приоритета запросов, группу блоков 19 согласования, элемент И-ИЛИ 20 второй группы, синхровход устройства 21, групп информационных входов-выходов 22, регистр 23 заданий, узел 24 коммутации, блок 23 приоритетных шифраторов,блок 26 регистров и узел 27 дешифраторов.

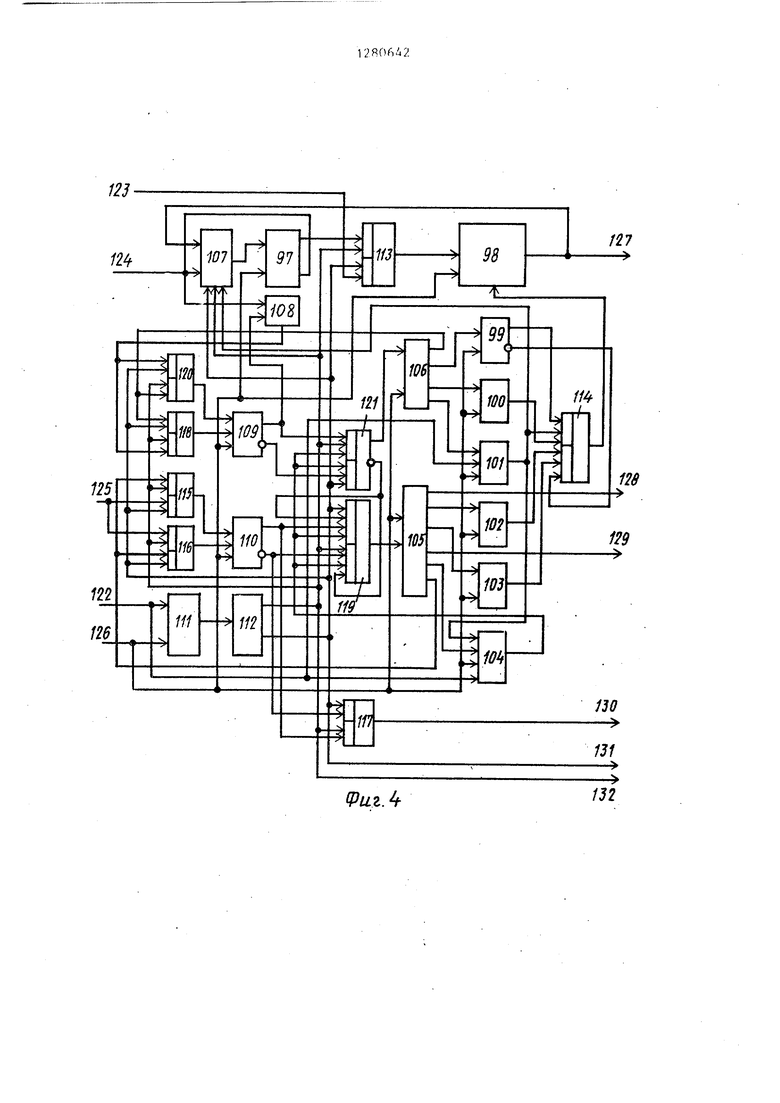

Блок 1 микропрограммного управления состоит из памяти 28 микрокоманд, регистра 29 адреса, регистра 30 микрокоманд, дешифратора 31, местной памяти 32,второго 33 и первого 34 регистров, арифметическо-логического узла 33, регистра 36 результата, первой 37 и второй 38 группы элементов И-ИЛИ, элемента И 39 и элемента И-НЕ Блок 1 имеет первый 41 и второй 42 и формационные входы, вход 43 режима, стробирующий вход 44, вход 45 разреше ния, синз ровход 46, стробирующий выход 47, адресный выход 48, с первого по пятый управляющие выходы 49-53,выход 54 выборки, третий информационный вход 55 и группу управляющих выходов 56 дешифрации блока. Блок 17 управления содержит триггер 57 передачи данных, группу триггеров 58 и 59 передачи данных каналов, элементы И 60 и 61 первой группы второй 62 и первый 63 элементы ИЛИ, первый 64 и второй 65 элементы И,элемент НЕ 66, триггер 67 запроса передачи данных, триггер 68 первого цикла передачи, триггер 69 промежуточного цикла передачи, триггер 70 второго цикла передачи, группу триггеров 71 и 72 второго цикла передачи каналов, элементы И 73 и 74 второй группы, группу элементов И-ИЛИ-НЕ 75 и 76, первый 77 и второй 78 элементы И-ИЛИ, элементы И-ИЛИ 79 и 80 первой группы и элементы И-ИЛИ 81 и 82 второй группы. Блок 17 имеет с первого по четвертьй группы входов 83-86, первьй 87 и второй 88 входы, с первого по пятый выходы 89-93 и с первой по третью группы выходов 94-96 блока соответственно. Блок 19 согласования образуют регистр 97 данных, буферная память 98 данных, триггер 99 обращения интерфейса, триггер 100 выбора буфера интерфейса, счетчик 101 адреса байтов, триггер 102 выбора буфера процессора, триггер 103 номера слова, счетчик 104 двойных слов, первьй 105 и второй 106

уэлы синхронизации, коммутатор 107, узел 108 обмена по интерфейсу, триггер 109 занятости регистра данных, триггер 110 занятости группы регистров, регистр 111 кода операции, де-. шифратор 112, элементы И-ИЛИ 113 и 114 первой и второй группы, с первого по шестой элементы И-ИЛИ 115-120 и элемент И-ИЛИ-НЕ 121, Блок 19 имее первый 122 и второй 123 информационные входы, информационньй вход-выход 124, вход 125 разрешения, синхровход 126, информационный вьпсод 127, первый 128 и второй 129 синхровыходы, выход 130 запроса, выход 131 записи и выход 132 чтения.

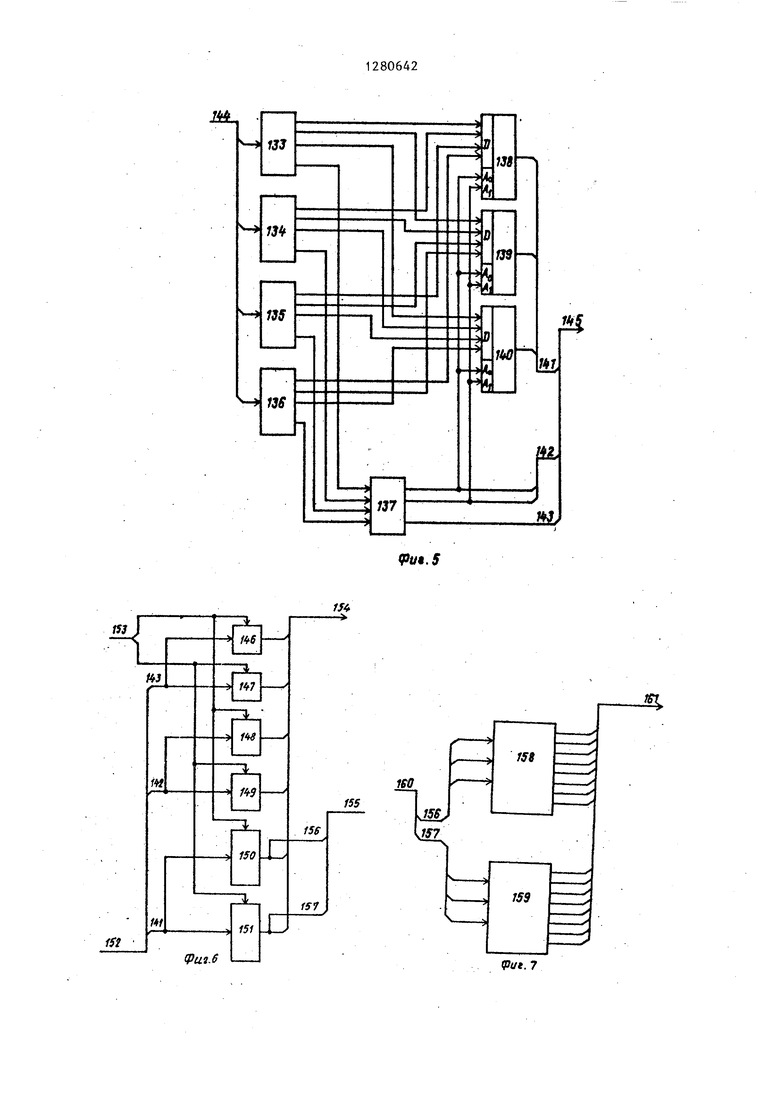

Блок 25 приоритетных шифраторов содержит (в данном случае) четыре

хода дешифратора 112 определяет, что в блоке согласования выполняется операция чтения.

При выполнении чтения данные из периферийного устройства побайтно с информационного входа-выхода блока 19 через коммутатор 107 поступают в регистр 97 данных, из которого через первую группу элементов И-ИЛИ 113 данные записываются в буферную память 98 по адресу с выхода второй группы элементов И-ИЛИ 114,

Если триггер 110 занятости группы регистров сброшен, то после накопления двойного слова в буферной памяти производится, сначала считывание первого слова из буферной памяти и передача его через информавосьмивходовых приоритетных шифратора 133-136, один четырехвходовый приоритетный шифратор 137 и три мультиплексора 138-140, а также информационный вход 141 мультиплексоров, информационные выходы 142 и 143 шифратора 137 и свои информационный вход 144 и выход 145. Блок 26 регистров состоит из двух одноразрядных регистров 146 и 147, двух двухразрядных регистров 148 и 149, двух трехразрядных регистров 150 и 151, своихИнформационного входа 152, группового входа 153 записи и первого 154 и второго 155 информационного выходов, а также выходов 156 и 157 регистров 150 и 151, Узел 27 дешифраторов содержит два дешифратора 158 и 159, информационный вход 160 и информационный выход 161, Устройство работает следующим образом. Буферная память 98 данных имеет две зоны заполнения данньми. Емкость каждой из зон соответствует разрядности оперативной памяти и в данном случае составляет двойное слово (восемь байт). Ширина разрядности буферной памяти соответствует разрядности информационного тракта процессора (в рассматриваемом случае она составляет одно слово), через тракты которого канал обменивается данными с оперативной памятью, Код операции, выполняемый блоком 19 согласования, находится в регистре 111 кода операции. Сигнал второго выхода дешифратора 112 определяет, что в блоке 19 выполняется oneрация записи. Сигнал с первого вы51Г1ИОННЫЙ выход блока 19, вторую группу элементов И-ИЛИ 20 и первую группу регистров 15 во вторую группу регистров 16, затем считывание второго слова и передача его в первую группу регистров 15.оПосле заполнения регистров триггер 110 занятости груп пы регистров устанавливается в единичное состояние. Для операции чтения в этом случае третьим элементом И-ИЛИ 117 вырабатьгаается запрос на передачу данных, который через выход запроса блока 19 поступает на вход блока 18 приоритета запросов. При опе рации записи во время второго цикла передачи данных соответствующего кана ла по сигналу, поступающему на вход разрешения блока 19, устанавливается триггер 110 занятости группы регистров, фиксирующий наличие данных, принятых из -оперативной памяти в первую и вторую группы регистров 15 и 16 соответствующего канала. Если в буферно памяти 98 данных одна из зон свободна то происходит передача сначала первого слова данных из второй группы регистров 16, а затем второго слова данных через второй информационный вход блока 19 и первую группу элементов Й-ИЛИ 113 в буферную память 98, Данные из буферной памяти 98 через второй информационный вход коммутатора 107 поступают в регистр 97 данных откуда выдаются на информационный вход-выход блока 19 под управлением узла 108 обмена по интерфейсу и триггера 109 занятости регистра данных. При операции записи запрос на передачу данных устанавливается с помощью третьего элемента И-ИЛИ 117, если триггер 110 занятости группы регистров сброшен. Сигнал операции чтения с первого выхода дешифратора 112 и сигнал операции записи с второго выхода дешифратора 112 подается соответственно через выходы чтения 132 и записи 131 блока 19 на группу элементов И-ИЛИ 20 и для управления направлением загрузки первой и второй группы регистров 15 и 16 на блок 17 управления. Для управления адресацией буфера данных используется триггер 99 обращения интерфейса. Если триггер 99 обращения интерфейса сброшен, то при выполнении обмена данными между буферной памятью данных и группой регистров адресация буферной памяти до /42 зоны двойного слова происходит с помощью триггера 102 выбора бусЬера процессора, а до зоны слова - с помощью триггера 103 номера слова. Триггер 103 номера слова во время передачи двойного слова переключается. Если триггер 99 обращения интерфейса установлен, то может выполняться обмен между буферной памятью и регистром 97. При этом адресация зоны происходит с помощью триггера 100 выбора буфера интерфейса, а слова и байта внутри слова - с помощью трехраэрядного счетчика 101 адреса байтов, Лвухразрядный счетчик 104 двойных слов указывает количество двойных слов в буферной памяти 98 данных. Во время операции записи он показывает количество незаполненных двойных слов в буферной памяти 98, во время операции чтения количество заполненных двойных слов, В начале операции записи счетчик устанавливается на 2 (два двойных слова не заполнеJ,Q) jj go время передачи двойного слова из групп регистров 15 и 16 его содержимое уменьшается. После передачи двойного слова через интерфейс содержимое счетчика 104 двойных слов увеличивается, В начале операции чтения счетчик устанавливается на О и при обмене данными соответственно модифи- цируется. Управление последовательностью работы оборудования блока 19 во время передачи данных между буферной памятью 98 и регистром 97 осуществляется с помощью узла 106, Управление передачей данных между буферной памятью 98 и группой регистров 15 и 16 производится узлом 105. Этот узел вырабатывает стробы загрузки первой и второй групп регистров 15 и 16 соответ- ствующего канала, которые поступают соответственно при передаче данных в буферную память или из буферной памяти на первый и второй синхровходы блока 19, Запуск узла 106 производится через элемент И-ИЛИ-НЕ 121, а запуск узла 105 - через пятый элемент И-ИЛИ 119, Запросы от всех блоков 19 поступают на блок 18, который по синхронизирующему сигналу принимает их, определяет наиболее приоритетный из них и передает в блок 17, в котором устанавливается триггер 57 передачи данных и один из группы триггеров 58

и 59 передачи данных каналов, которые указывают, какой блок 19 должен производить обмен данными. На вход блока 17, на вторую группу входов, из блока 19 поступает код операции, который используется для аппаратурного формирования микрокоманды обращения и оперативной памяти на первой группе элементов И 60 и 61 и втором элементе ИЛИ 62, с выхода которого микрокоманда поступает на вход режима блока 1 в регистр микрокоманд 30 через первую группу элементов И-ИЛИ 37, При этом потенциалом с триггера 57 передачи данных блока 17 блокируется прием микрокоманд из памяти 28 микрокоманд блока 1 на первую группу элементов И-ИЛИ 37 и пропускается микрокоманда из блока 17, в ходе выполнения которой должен производиться обмен данными между оперативной памятью и первой и второй группами регистров 15 и 16 через внутренние тракты процессора.

Для управления прохождением данных блок 17 вырабатывает последовательность сигналов с выходов триггера 67 запроса передачи данных,триггера 68 первого цикла передачи, триггера 69 промежуточного цикла передач триггера 70 второго цикла передачи, для управления первой и второй группами регистров 15 и 16 - с выходов первой и второй групп элементов И-ИЛИ 79-82.

Микрокоманда Память выполняется в два цикла,

В первом цикле готовится адрес данных.и при записи в память записываются данные. Чтение и запись производится в паузе между первым и вторим циклами. Длительность паузы зависит от времени обращения к памяти. Это время намного превышает первый и второй циклы памяти. Во втором цикле в случае считывания выбираются данные из памяти и пересылаются через внутренние тракты.процессора в первую и вторую группу регистров 15 и 16,Триггер 67 запроса передачи данных блока 17 использует два запуска циклов аппаратурно сформированной микрокоманды Память, Блок 18 предназначен для выбора наиболее приоритетных из каналов.

Коммутатор 14 служит для выбора данных из оперативной памяти или регистра результата 36 блока 1 и представляет собой группу элементов И-ИЛИ

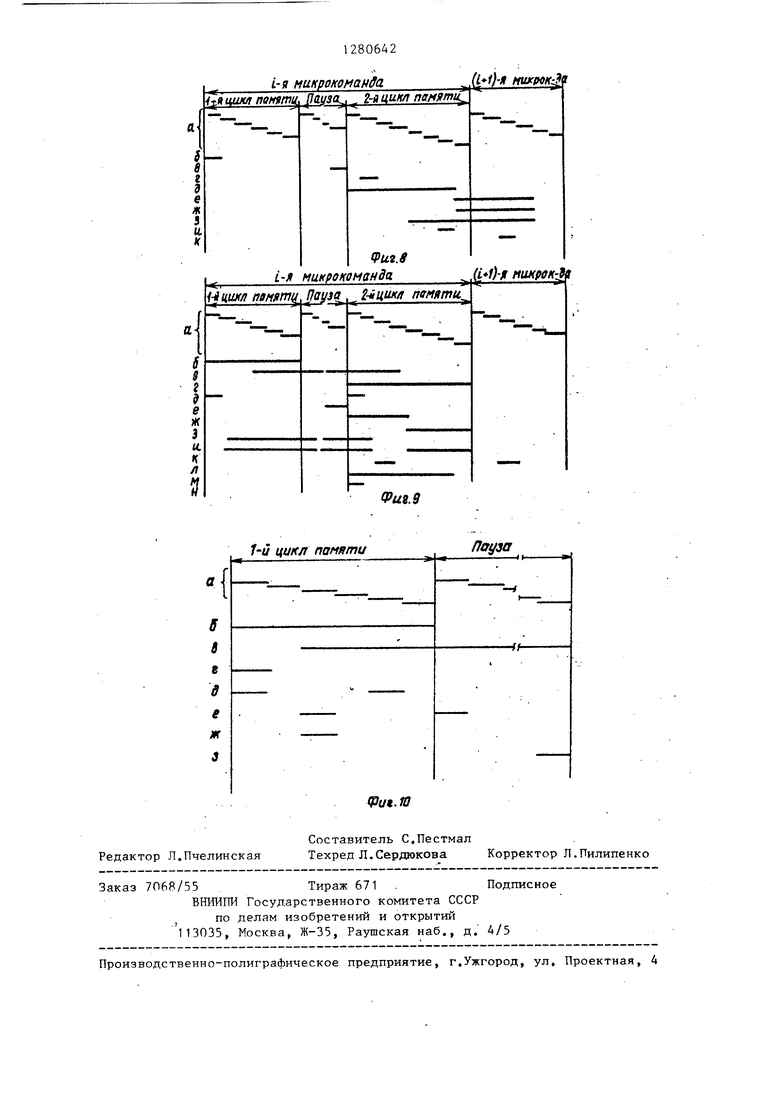

На сЬиг.В изображена временная диаграмма работы устройства для обмена данными между группой каналов вводавывода и оперативной памятью для выполнения микрокоманд Память при обращении к ней процессора. На диаграмме приняты следующие условные обозначения: а - синхронизация; S - прием в первый регистр 34 адреса оперативной памяти; 6 - прием двойного слова данных в выходной регистр 4; 2 - запись в местную память 32 модифицированного адреса оперативной памяти; а - вьщача первого слова данных с первой группы элементов И-ИЛИ 5; е - выход третьего триггера 9; ж- вЪщача второго слова данных с первой группы элементов И-ИЛИ 5; управление коммутатором 14 на выбор данных из оперативной памяти; U эапись первого слова данных; к - запись второго слова данных.

Устройство для выполнения микрокоманды Память при обращении к ней процессора работает следующим образом.

Из памяти 28 микрокоманд блока 1 по адресу из регистра 29 адреса, через первую группу элементов И-ИЛИ 37 и регистр 30 заносится микрокоманда, которая поступает на дешифратор 31, с седьмого выхода которого на местную память 32 подается адрес, по которому на первый регистр 34 считывается адрес данных оперативной памяти, который через адресный -выход 38 блока 1 подается на адресный выход устройства в оперативную память. Двойное -слово данных иэ оперативной памяти заносится в выходной регистр 4, из которого с помощью первой группы элементов И-ИЛИ 5 на коммутатор 14 подается первое слово данных. Управление выбором нового слова осуществляется первым элементом И-НЕ 8 поустановленному первому триггеру 7, который устанавливается через первый элемент И 6 по младшему байту адреса двойного слова из первого регистра 34 блока 1. Адрес данных оперативной памяти подается также на арифметико-логический узел 35, в котором он модифицируется и через регистр результата 36 и коммутатор 14 записывается в местную память 32, После этого, управление коммутатором 14 по выходу второго элемента И 13 переключается на выбор первого слова данных из оперативной памяти. После записи первого слова данных по второму выходу дешифратора 31 блока 1 устанавливается триггер 9, которьт инверсным выходом на первом элементе И.6 изменяет младший адрес оперативной памяти, который запоминается в конце выяолнения микрокоманды Память на первом триггере 7 и через первый элемент И-НЕ 8 изменяет управление первой группой элементов И-ИЛИ 5 и на выдачу второго слова Данных из выходного регистра 4 на коммутатор 14, а прямой выход третьего триггера 9 управляет передачей этого слова данных через коммутатор 14 на фоне выполнения следующей микрокоманды.

На фиг,9 изображена временная диаграмма работы устройства для выполнения аппаратурно-сформированной микрокоманды Память считывания из оперативной памяти. На ней приняты следующие обозначения: а - синхронизация; S - выход триггера 68 первого цикла передачи; Ь - выход триггера 69 промежуточного цикла передачи; 2 - выход триггера 70 второго цикла передачи; а - прием в первьй регистр 34 адреса оперативной памяти и счетчика байтов; 6 - прием двойного слова данных в выходной регистр 4; К - вьщача первого слова данных с первой группы элементов И-ИЛИ 5; выдача второго слова данных с первой группы элементов И-ИПИ 5; U - выход второго триггера 11; к управление коммутатором 14 на выбор данных из оперативной памяти; -л - запись в местную память 32 модифицированного адреса оперативной памяти и счетчика байтов; м строб первой группы регистров 15; Н - строб второй группы регистров 16, Устройство при считывании данных из оперативной памяти в первую и вторую группы регистров 15 и 16 работает следующим образом, Из блока 17 в блок 1 в регистр 30 заносится аппаратурно-сформированная микрокоманда, которая поступает на дещифратор 31, с седьмого выхода кото рого на местную память 32 подается

адрес, по которому на первьй регистр 34 в первом цикле памяти считьгеается адрес данных оперативной памяти, который подается на адресный выход устройства в оперативную память и на арифметико-логический узел 35, на котором он модифицируется. Из оперативной памяти в выходной регистр 4 считывается двойное слово данных,Младший байт адреса оперативной памяти, который адресует первое слово данных из первого регистра 34 блока 1 через первый элемент И 6 устанавливает первый триггер 7, который через первый элемент И-НЕ 8 управляет выбором на первой группе элементов И-ИЛИ 5 первого слова данных, которое поступает на коммутатор 14, С выхода триггера 55 передачи данных блока 17 на информационный вход второго триггера 11 подается сигнал, который устанавливает этот триггер в начале первого

цикла микрокоманды Память, Второй триггер 11 управляет передачей через коммутатор 14 первого слова данных из оперативной памяти, которое проходит через вторую группу элементов

И-ИЛИ 20 под управлением выхода записи блока 19 и через первую группу регистров 15, так как на синхронизирующий вход подается постоянный строб, защелкивается во второй группе регистров 16 по стробу, сформированному на первой группе элементов И-ИЛИ 79 и 80 блока 17 по сигналам с выхода группы триггеров 58 и 59 передачи данных каналов и триггера 70 второго

ных, которое через коммутатор 14 под управлением сигнала с выхода второго элемента И 13 поступает через вторую цикла передачи и синхросигнала. Из местной памяти 32 блока 1 во втором цикле памяти на первый регистр 34 считывается счетчик байтов, которые осталось передать из оперативной памяти в каналы. Счетчик байтов передается на арифметико-логический узел 35, на котором он модифицируется. После сброса второго триггера 11 управление коммутатором 14 переключается на выдачу из регистра результата 36 модифицированного адреса, который записывается в местную память 32,Затем на втором элементе И-НЕ 10 по сигналу с выхода триггера 70 второго цикла передачи блока 17 и сигналу с синхровхода устройства 21 вырабатывается сигнал, который поступает на рторой вход первого элемента И-НЕ 8 и инвертирует выходы этого элемента. Таким образом, первая группа элементов И-ИЛИ 5 выбирает второе слово дангруппу элементов И-ИЖ 20 на первую группу регистров 15 и защелкивается по стробу, сформированному на второй группе элементов И-ШТИ 81 по сигнала1 с выхода группы триггеров 58 и 59 пе11 :

редачи данных каналов, синхросигнала с выхода группы триггеров 75 и 76 второго цикла передачи каналов. Запись модифицированного счетчика из регистра 36 результата блока 1 в мес тную память 32 выполняется на фоне выполнения следующей микрокомандьг,

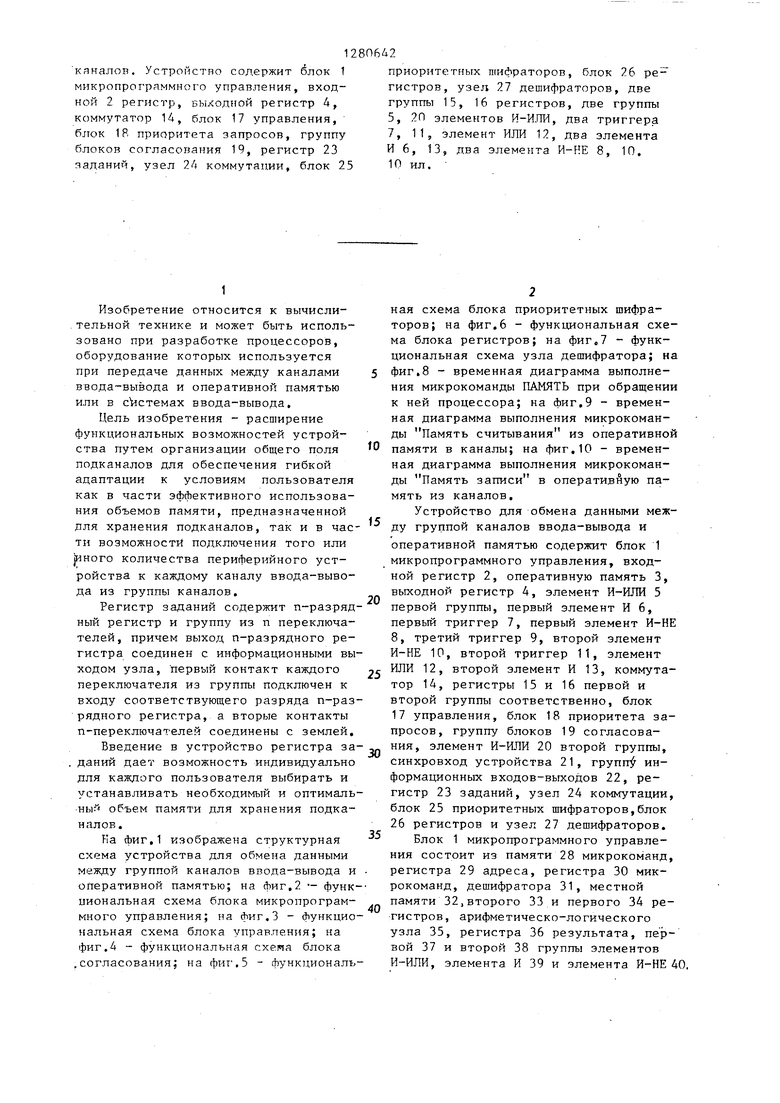

На фиг,10 изображена диаграмма работы устройства для выполнения аппаратурно-сформированной микрокоманды Память записи в оперативную память. На диаграмме приняты следующие обозначения: а - синхронизация; &выход триггера 68 первого цикла передачи; В - выход триггера 69 промежуточного цикла передачи;;2 - прием в первый регистр 34 адреса оперативной памяти; J - прием во второй регистр 33 данных из второй группы регистров 16; е - прием данных во входной регистр 2; Ж - строб второй группы регистров 16; 0 - запись в оперативную память.

Устройство для записи данных из первой и второй групп регистров 15 и 16 в оперативную память работает следующим образом.

С второго информационного выхода группы регистров 16 в блок 1 во второй регистр 33 через вторую группу элементов И-ИЛИ 38 под управлением сигнала с выхода триггера 57 передачи данных блока 17 принимается первое слово данных по стробу с выхода первого элемента И-ИЛИ 77 блока 17, который вырабатывается по синхросигналу. После приема первого слова во второй регистр 33 блока 1 данные через первый управляннций выход 51 блока 1 подаются на входной регистр 2, в котором принимаются по стробу, ° сформированному на втором элементе И-ИЛИ 78 блока 17, который вырабатывается .по синхросигналу и третьему управляющему выходу блока 1, После приема первого слова данных во- входной-регистр 2 второе слово данных из первой группы регистров 15 переписывается во вторую группу регистров 16 по стробу с выхода первой группы элементов И-ИЖ 79 и 80 блока 17, сформированного по сигналам с выхода группы триггеров 58 и 59 передачи ,данных каналов, триггера 68 первого цикла передачи и синхросигнала, С выхода второй труппы регистров 16 второе слово данных записывается во второй регистр 33 блока 1 через рторую группу элементов И-ИЛИ 38 по стробу

8064212

с выхода первого;элемента И-ИЛИ 77 блока 17, сформированного по сигналам с выхода триггера 57 передачи данных, триггера 68 первого цикла

с передачи и синхросигнала, С выхода второго регистра 33 блока 1 второе слово данных поступает на входной регистр 2, на котором оно защелкивается по стробу с выхода второго зле10 мента И-ИЛИ 78 блока 17, сформированному по сигналам с выхода тригге- ра 55 передачи данных и синхросигналу. Из местной памяти 32 блока 1 считывается адрес, который через первый f5 регистр 34 передается на адресный выход устройства в оперативную память. По пятому выходу дешифратора 31 бло ка 1 на элементе И 39 вырабатывается строб замен в оперативную память, ко20 торый подается на стробирующий выход устройства.

Организация общего поля подканала в устройстве для обмена данными между группой каналов ввода-вывода и 25 оперативной памятью выполняется аппаратно-микропрограммным способом.

Устройство в данном случае работает следующим образом,

30 Аппаратная часть реализации общего поля подканалов основана на использовании регистра 23 заданий, узла 24 коммутации, блока 25 приоритетных шифраторов, блока 26 регистров,2 узла 27 дешифрации. Микропрограммная часть реализации обобщенного поля подканалов основана на использовании йсего оборудования процессора, в сос|Тав которого входит устройство для

40 обмена данными между группой каналов ввода-вывода оперативной памятью,При этом процессор управляет работой группы каналов ввода-вывода с помощью специальных команд ввода-вывода,

45 Обращение к программе канала осуществляется с помощью адресного слова канала, расположенного в фиксированной ячейке оперативной памяти. Адресное слово канала содержит ключ защиты и

50 адрес первого управляющего слова канала, которое первоначально находится в оперативной памяти.

Программа канала состоит из последовательности управляющих слов ка55 нала. Управляющие слова канала содержат всю необходимую информацию для организации и проведения связи канала ввода-вывода с периферийным устройством, С целью обеспечения макси ально эффективного с точки зрения быстродействия анализа управляющего слова канала управляющее слово канала из оперативной памяти переписывается в определенные ячейки (подканалы) более быстродействующей местной памяти, в которой управляющие слова канала сохраняются до конца работы канала ввода-вывода с периферийным устройством.

При работе одного канала.вводавывода из группы каналов с несколькими периферийными устройствами одновременно в местной памяти необходимо хранить столько управляющих слов канала, сколько периферийных устройств одновременно запущено по всей группе каналов. Таким образом, возможное количество одновременно запущенных периферийных устройств определяется количеством подканалов, т.е. тем максимальным объемом в местной памяти, который отводится для хранения общего количества управляющих каналов. Таким образом, чтобы максимально использовать адресное поле периферийных устройств для каждого канала, которое определяет максимально возможноеКоличество периферийных устройств, которое можно подключить к одному каналу ввода-вывода (а в рассматриваемом случае 256 устройств), в местной памяти необходимо отвести объем, достаточный для хранения 256хп подканалов (где п - количество каналов ввода-вывода .в группе). Если учесть, что для хранения одного подканала необходимо в местйой памяти отвести четыре тридцатидвухразрядных слов, и то, что не для каждого пользователя необходимо такое количество подканалов, вариант предоставления максимального количества подканалов не является оптимальным.

Организация общего поля подканалов с их динамическим назначением позволяет, во-первых,оптимальным образом перераспределить подканалы между группой каналов, во-вторых, при оптимальном количестве подканалов организовать возможность подключения к каждому каналу ввода-вывода максимального количества периферийных устройств.

Выбор оптимального количества подканалов осуществляется путем коммутации в регистре 23 вручную при помощи

переключателей или каким-либо другим образом соответствующих разрядов (в данном случае тридцатидвухразрядного регистра) таким образом, чтобы на инЛормационный выход регистра 23 заданий поступал 32-разрядный код, определяющий выбранное количество подканалов. При выполнении микропрограммы сброса системы, которая выполняется

каждьш раз при загрузке системы команд или после нажатия на пульте оператора кнопки Сброс системы, этот код по микрокоманде чтения, продешифрованной на дешифраторе 31, считыва5 ется сигналом чтения с группы выходов 56 из регистра 23 через узел 24, третий информационный вход 55 блока 1, элемент И-ИПИ 38, регистр 33, арифметико-логический узел 35, регистр 36

0 результата, второй управляющий выход 53 блока 1, первый вход коммутатора 14, первый информационный вход 41 блока 1 и записывается стандартным . образом в определенную ячейку мест5 ной памяти 32 как характеристика количества подканалов, отведенных в местной памяти для группы каналов ввода-вывода. В дальнейшем эта информация используется каждый раз при вы0 полнении очередной команды ввода-вывода дЛя назначения свободного подканала. Если свободных подканалов нет, выполнение команды ввода-вывода прекращается.

При этом канальная микропрограмма формирует такой признак результата, который формировался бы, если бы при выполнении команды ввода-выво да оказалось, что нужного периферийного устройства нет. Подобный алгоритм формирования признака результата при отсутствии свободных подканалов выбран из расчета, чтобы указать пользователю, что при существующем количестве подключенных к группе каналов ввода-вывода периферийных устройств выбранного количества подканалов недостаточно. Такой вывод дол0 жен сделать пользователь, когда операционная система (или какая-либо другая система) стандартно сообщает, что конкретного периферийного устройства нет, а на самом деле оно под5 ключено и нормально функционирует. Изменяя общее количество подканалов в ту или другую сторону, пользователь индивидуально для собственных нужд выбирает, оптимальное количество подканалов. Организация подключения максимального количества периферийных устройств к каждому каналу ввода-вывода из группы каналов выполняется путем произвольного назначения подканалов, т.е. путем возможности назначения любого подканала любому периферийному устройству с дальнейшим освобождением этого подканала после конца связи с периферийным устройством. Произвольное назначение подка налов в рассматриваемом случае выполняется аппаратно-микропрограммным способом. При Этом используется апларатура узла 24, блоков 25, 26 и (узла 27. Кроме того, используются таблицы, расположенные в местной памяти, и несколько ячеек местной памя ти, необходимые для оперативной обработки управляющей информации. Первая таблица содержит 256 последовательно адресованных ячеек местной памяти, каждая из которых предназна чена для хранения адреса назначенного подканала для конкретного периферийного устройства. Адресация ячеек этой таблицы соответствует адресации. максимального количества периферийных устройств, которые могут быть подключены к одному каналу ввода-вывода. Количество первых таблиц определяется количеством каналов ввода-вывода в группе. Первая таблица предназначена также для хранения признака, который говорит о том, назначен для периферийного устройства подканал или нет. При назначении подканала этот

признак устанавливается. После конца работы с периферийным устройством, когда подканал не нужен, этот признак сбрасывается.

Вторая таблица, содержащая В рассматриваемом случае тридцать два 32разрядных слова совместно с указателем слов второй таблицы, которьш в рассматриваемом случае состоит из одного 32-разрядного слова используется для формирования адреса свободного подканала. Вторая таблица определяет то максимальное количество подканалов, которое может быть отведено для группы каналов (в данном случае 1024), Действительное количество отведенных подканалов устанавливается путем коррекции этой табли цы и указателя слов второй таблицы

хотя бы одного свободного подканала, определяемого одним словом этой таблицы характеризуется соответствующим

второй таблицы по адресу 3 нет. Учитывая сказанное, первоначальная устанрвка соответствующего количества подканалов, которое определяется кодом, считанным из регистра 23, осу45 ществляется микропрограммно путем установки в единичное состояние соответствующего количества бит в словах второй таблицы и в указателе слов этой таблицы.

55 первой таблицы и запоминается в одной из ячеек местной памяти. Цель этой выборки - определить свободно ли адрессованное в команде ввода-вывода в соответствии С;характеристикой количества подканалов, ртведенн з1х в местной памяти для группы каналов ввода-вывода, указанной в.коде, считайном из регистра 23 заданий. Указатель слов второй таблицы используется для оперативного нахождения свободного подканала из общего количества отведенных подканалов. Формирование адреса свободного подканала выполняется путем определения пятиразрядного адреса слова второй таблицы (старшие разряды адреса подканала) и пятиразрядного адреса бита в этом слове (младшие разряды адреса подканала), Так как адрес слова второй таблицы определяется адресом бита в указателе слов второй табдицы, то адрес свободного подканала Нормируется из адреса бита в указателе слов второй таблицы и адреса бита в соответствующем слове второй таблицы. Формирование адреса свободного подканала для конкретного периферийного устройства выполняется следующим образом. Общее количество подканалов задается путем установки в нулевое.состояние общего количества бит в словах второй таблицы. Причем наличие 35 битом указателя слов второй таблицы, установленного в нулевое состояние, Например, если бит 3 указателя слов второй таблицы установлен, в 1, то свободных подканалов адресуемых слов

периферийное устройство или нет, что, выполняется путем анализа признака назначения, подканала.

Если подканал назначен, следовательно, адресованное в команде ввода-вывода периферийное устройство, занято и выполнение команды вводавывода прекращается.

Если подканал не назначен, периферийное устройство свободно, выпол- fO

нение Команды ввода-вывода продолжается.

Выполняется попытка назначения свободного подканала. Для этой цели анализируется наличие свободных под- 15 146,

каналов. Анализ выполняется с определения наличия нулевых битов в указателе слов второй таблицы. Если нулевых битов нет, т,е, свободные подканалы отсутствуют f выполнение операции ввода-вывода прекращается. Если свободные подканалы есть, формируется адрес свободного подканала следующим образом.

Указатель слов второй таблицы из местной памяти через регистр 34, арифметико-логический узел 35, регистр 36 результата, управляющий выход 53 и коммутатор 14 поступает в блок 25 приоритетных шифраторов, Через информационный вход 14 с первого по четвертый байты этого слова поступают на входы с первогоч по четвертый приоритетных шифраторов 133-136 соответственно. Таким образом, на адресных выходах приоритетных шифраторов 133-136 формируются адреса первых нулевых битов каждого байта елова. При этом, если нулевых битов в байте нет, соответствующий приоритетный шифратор возбуждает свой управляющий выход. Следовательно, если в указателе слов второй, таблицы нет ни бдного нулевого бита, возбуждается управляющий выход пятого приоритетно го шифратора 137,который по линии 14 соединен с информационным выходом 145 Если свободные подканалы есть, то двухразрядный адрес, снятый с адресного выхода приоритетного шифратора 137, указывает адрес первого байта указателя слов второй таблицы, в котором есть по крайней мере один нуле вой бит, а трехразрядный адрес, снятый с выходов мультиплексоров 138140, указывает адрес бита в соответствующем байте, Двухразрядный адрес .байта по линиям 142 и трехразрядный адрес бита по линиям 141 соединены

с информационным выходом 145 блока 25, Таким образом, при помощи блока 25 аппаратным путем выполняется анализ наличия свободных подканалов и формирование адреса слова второй таблицы, в котором есть свободные подканалы,

Информация, полученная на информационном выходе 145 блока 25 по микраторе 31 сигналом записи, снятым с группового выхода дешифрации 156 блока 1, через групповой вход 153- записи блока 26 записывается в регистры

и 141 и запоминается с целью дальнейшего анализа.

Анализируя информацию, снятую с выхода регистра 146 через первый инФормационный выход 154 блока 26, определяется наличие свободных подканалов. Если свободные подканалы есть, с выходов регистров 148 и 150 пятиразрядный код, по которому из второй

таблицы в одну из ячеек местной памяти считывается соответствующее 32разрядное слово, которое затем выдается в блок 25, и по специальной микрокоманде информация, полученная рокоманде, продешифрованной на дешиф148 и 150 по линиям 143, 142 на информационном выходе 145 блока 25, запоминаются в блоке 26 на регистрах 147, 149 и 151, Таким образом, после анализа двух 32-разрядных слов указателя слов, второй таблицы и одного из слов второй таблицы на первом информаци онном выходе 154 блока 26 формирует:ся десятиразрядный код, являющийся адресом свободного подканала. Этот адрес считывается и затем заносится в первую таблицу вместе с признаком. свидетельствующим о том, что подканал для конкретного периферийного устройства назначен. После назначения подканала кррректируется слово второй таблицы и, при необходимости, указатель слов этой таблицы. Для этой цели коды адреса бита в байте указателя слов второй таблицы и в байте соответствующего слова этой таблицы по линиям 156 и 157 соответственно подаются через второй информационный выход 155 блока 26 в узел 27 на входы дешифраторов 158 и 159, На выходах дешифраторов 158 и 159 устанавливаются соответствующие константы, которые используются для корректировки соответствующего байта слова второй таблицы и при необходимости соответствующего байта указателя слов этой таблицы. После корректировки байта в слове вто рой таблицы это слово проверяется на наличие в нем свободных подканалов. Для этой цели скорректированное слово этой таблицы подается в блок 25 и результат анализа наличия или отсутствия свободных подканалов -запоминается в регистре 147, Анализируя содержимое этого регистра, определяется необходимость в корректировке бай та указателя слов второй таблицы и при необходимости байт указателя сло этой таблицы корректируется при помощи константы-, считанной с выходов дешифратора 158, Назначение подканала для конкретного периферийного уст ройства заканчивается. Освобождение подканала выполняется после конца связи канала с периАерийным устройством, когда соответствующий подканал уже не нужен, Осво боткдение подканала осуществляется микропрограммным способом, Формула изобретения Устройство для обмена данными между группой каналов ввода-вывода

Фиг. 2 и оперативной памятью по авт,св, № 1190385, отличающееся тем, что, с целью расширения функциональных возможностей путем организации общего поля памяти подканалов, в него введены регистр заданий,узел коммутации, блок приоритетных шифраторов, блок регистров, узел дешифраторов, причем информационный выход регистра заданий соединен с первым информационным выходом узла ком;.чутации, второй информационный вход которого соединен с первым информационным выходом блока регистров, второй информационный выход которого соединен с информационными входами . узла дешифраторов, выход которого соединен с третьим Информационным входом узла коммутации, выход которого соединен с третьим входом логических условий блока микропрограммного управления, группа управляющих выходов которого соединена с группой управляющих входов узла коммутации и с группой входов записи блока регистров, информационный вход которого соединен с входами блока приоритетных шифраторов, информационный вход которого соединен свыходом коммутатора.

/52

(Риг. 4

flf«.5

wo

| Авторское свидетельство СССР 1190385, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1985-08-30—Подача