to |

1чЭ

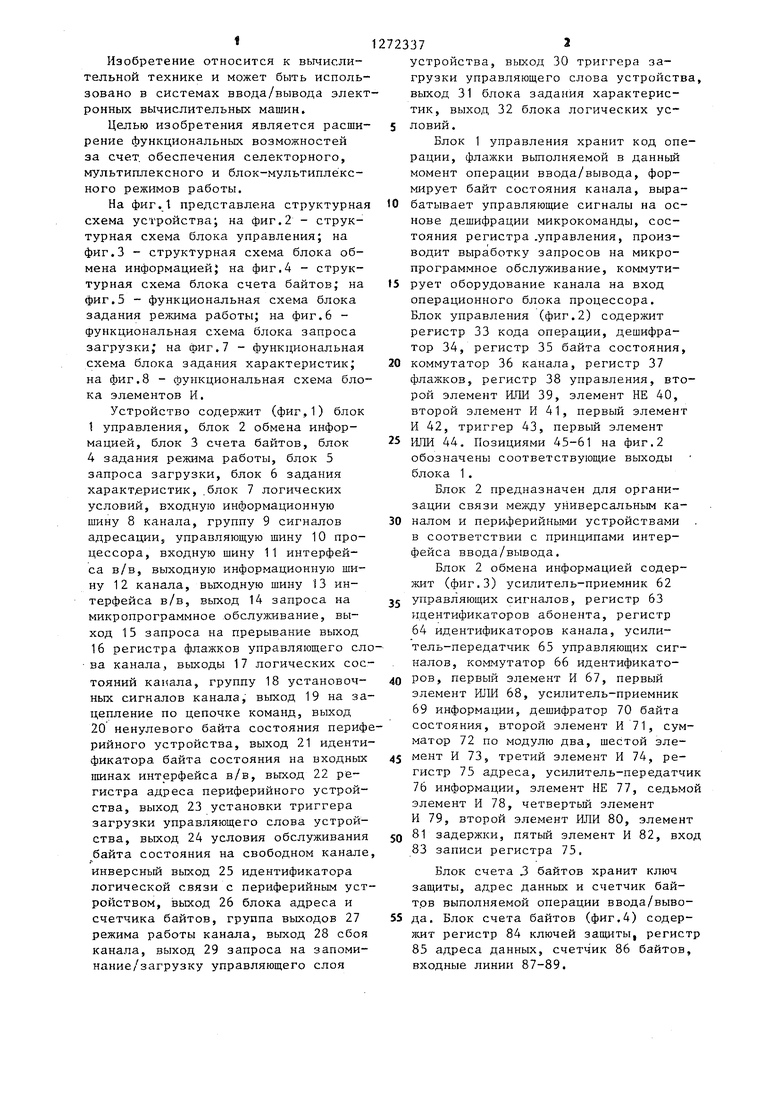

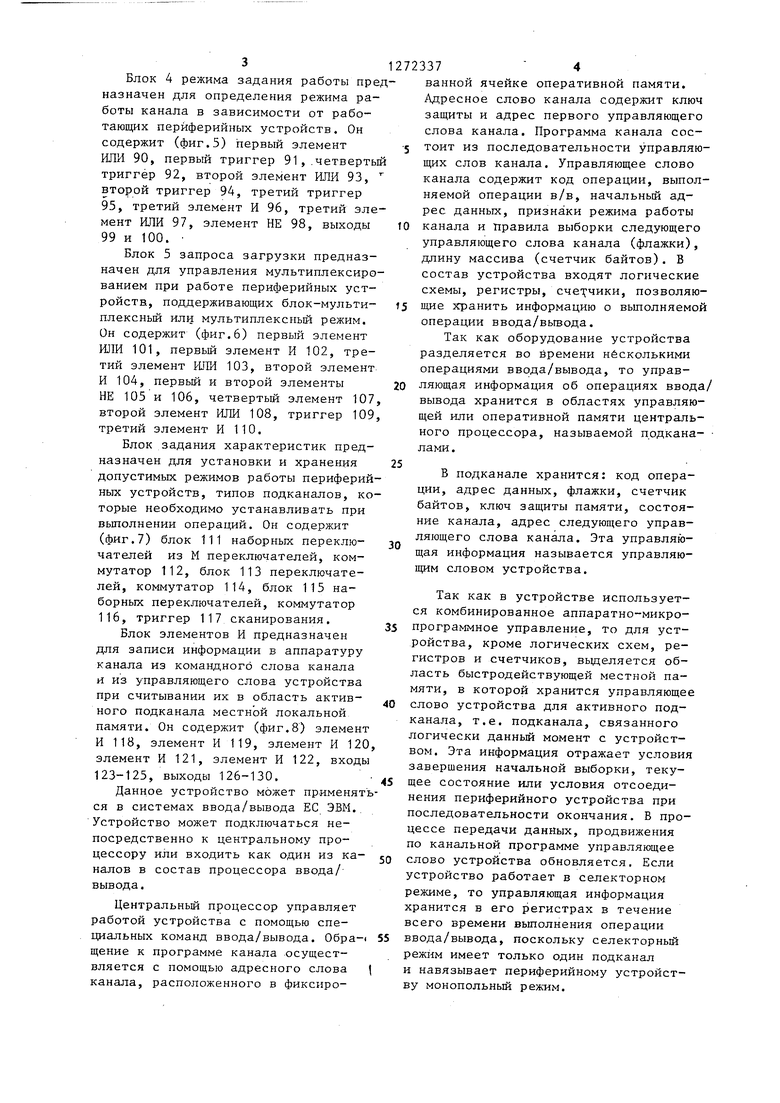

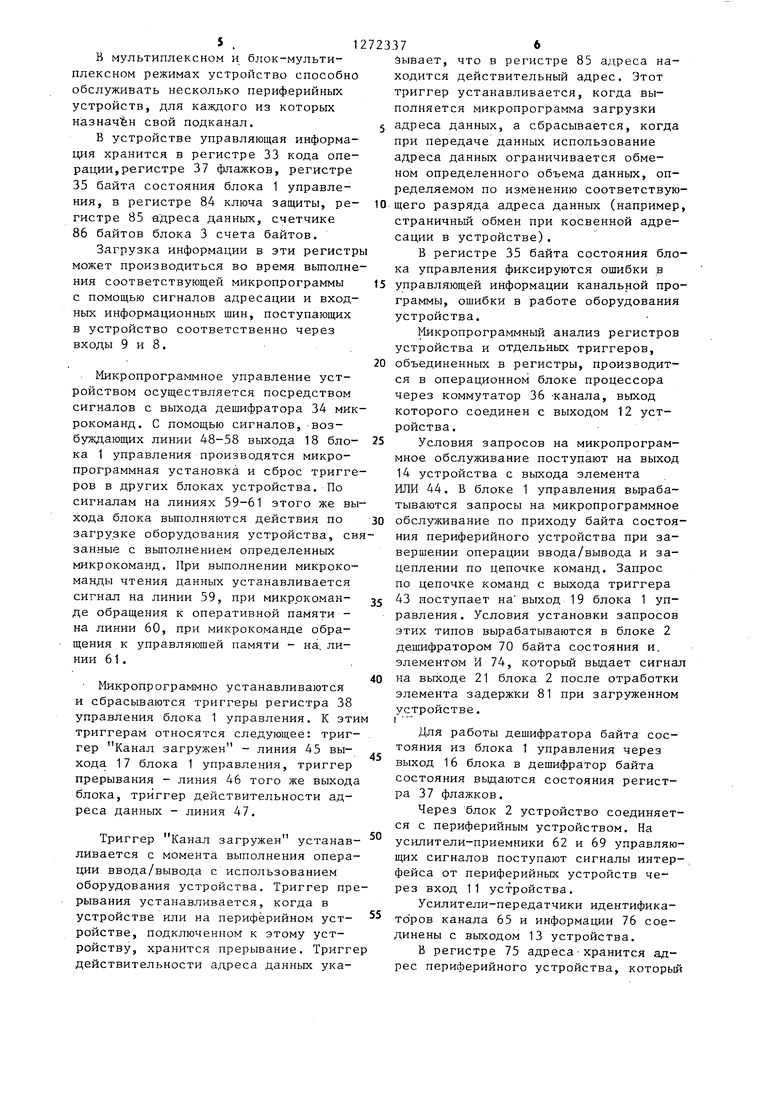

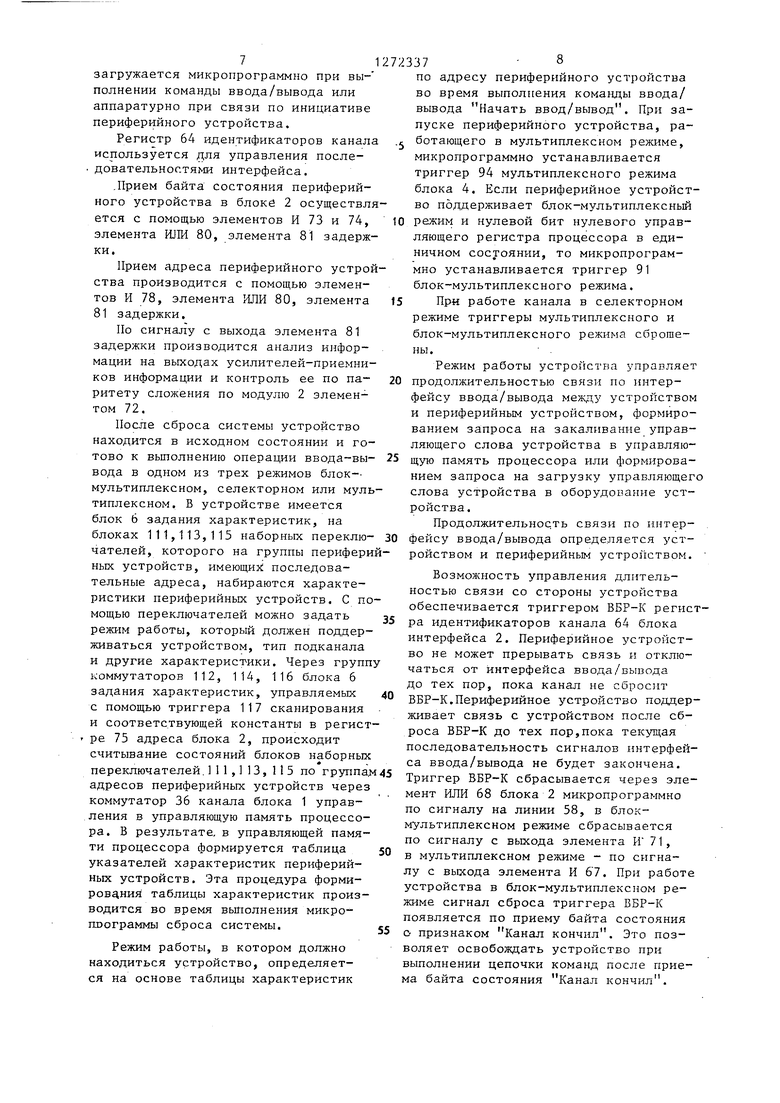

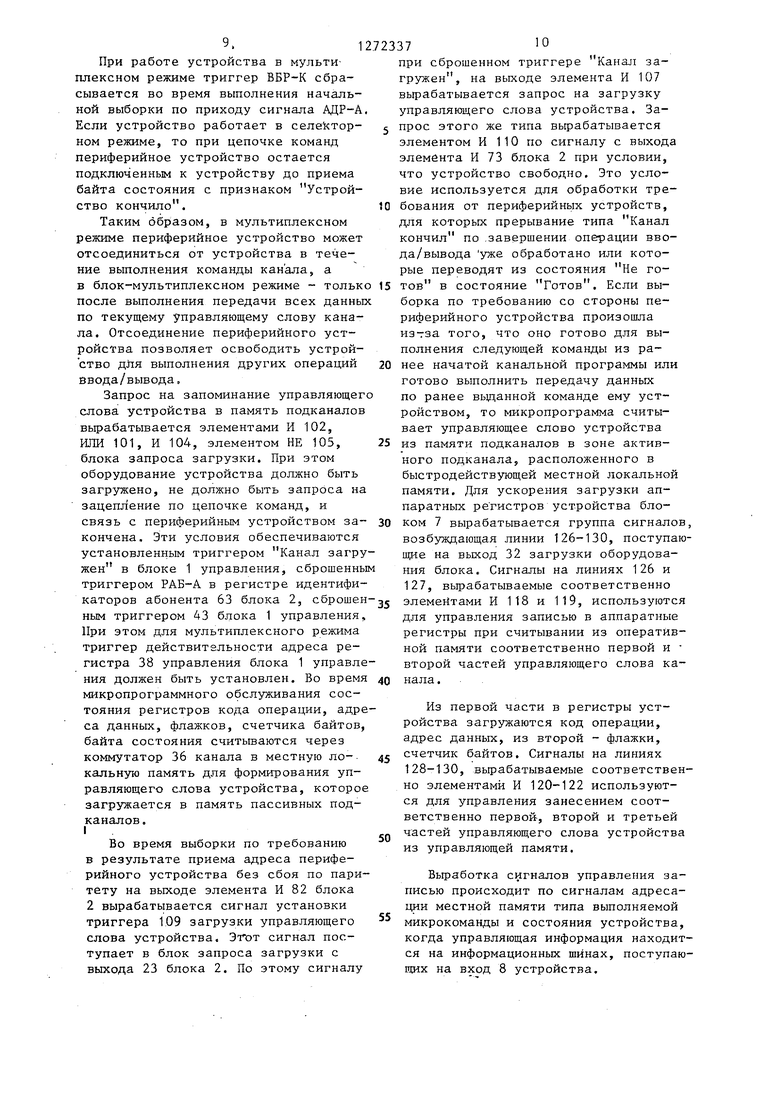

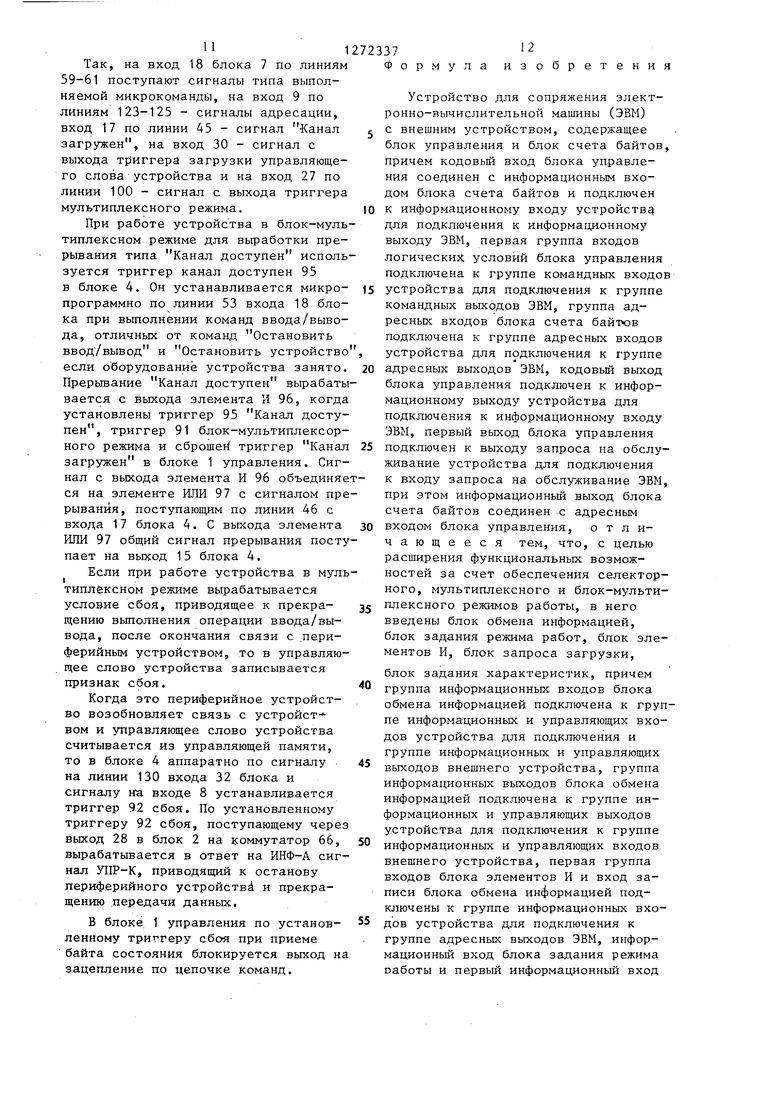

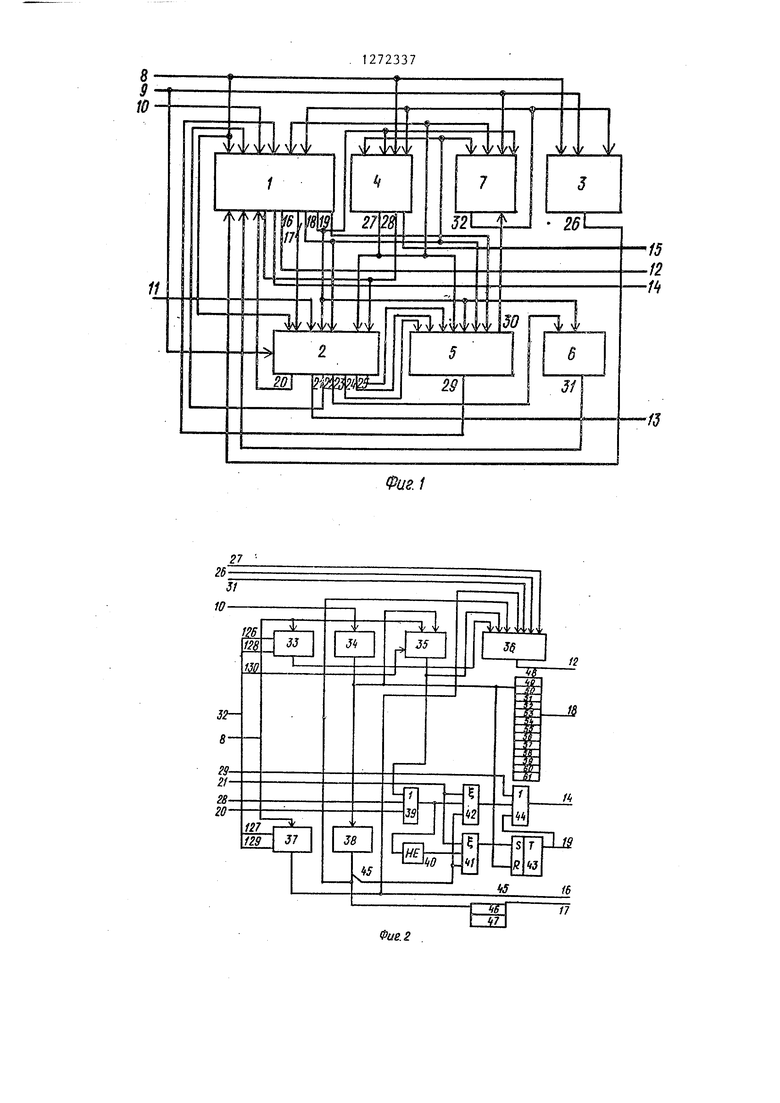

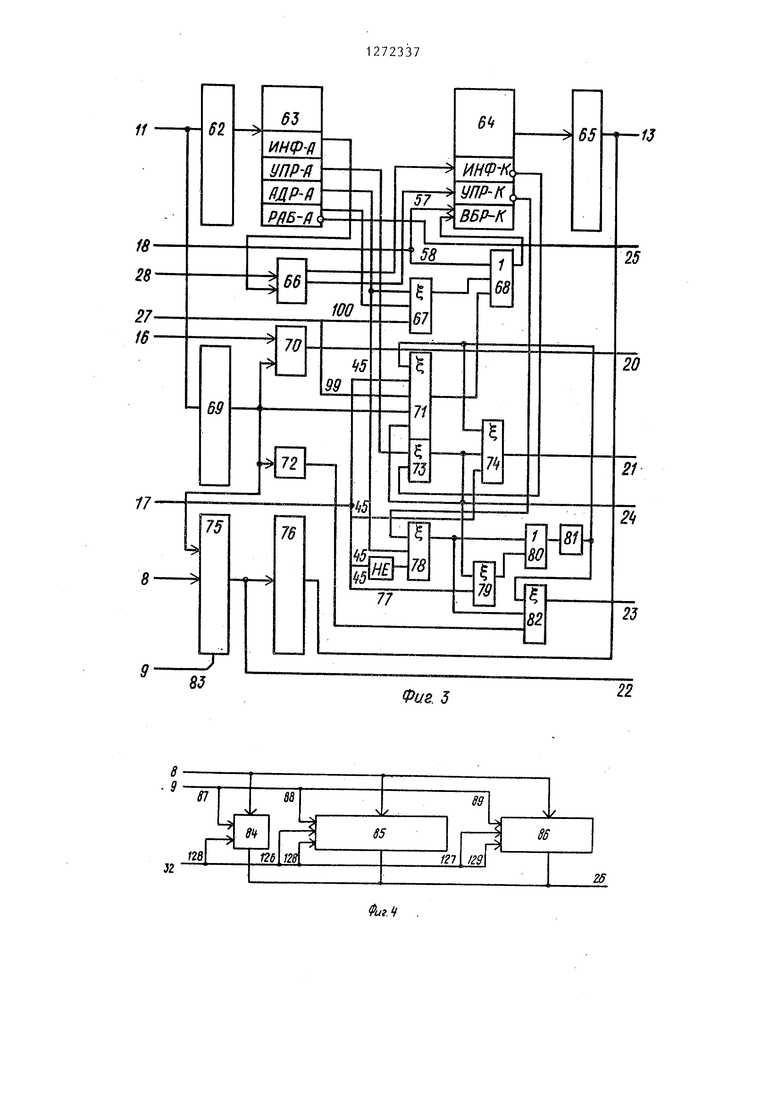

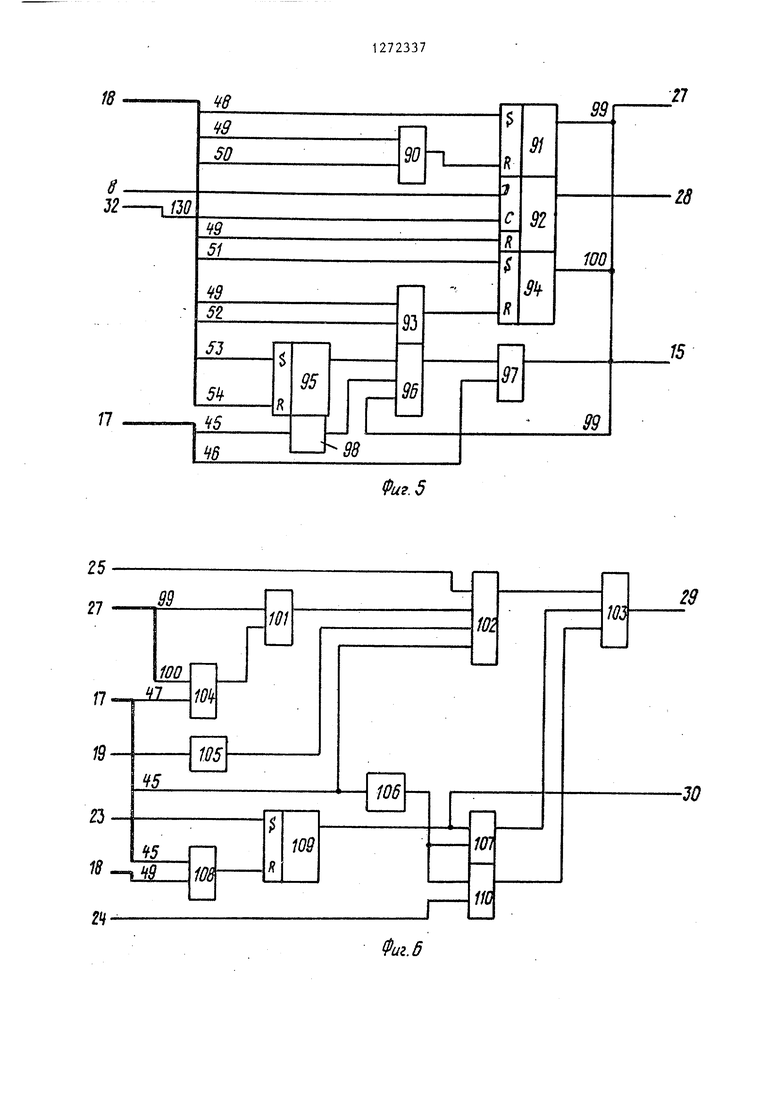

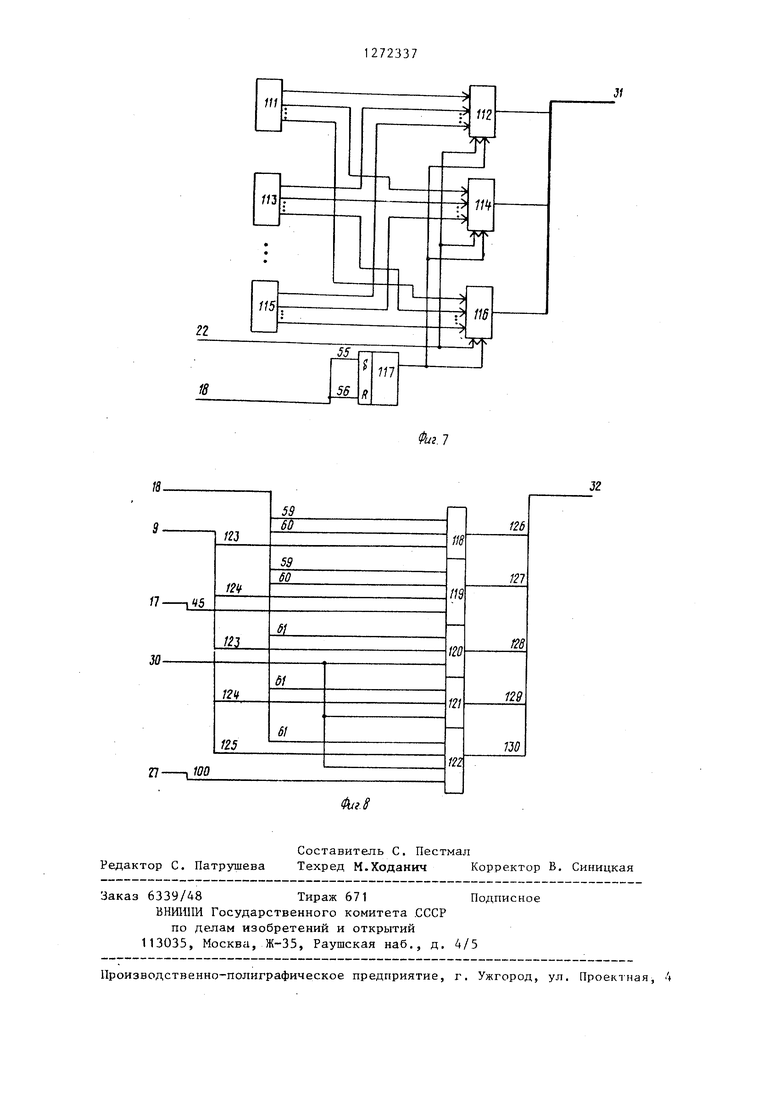

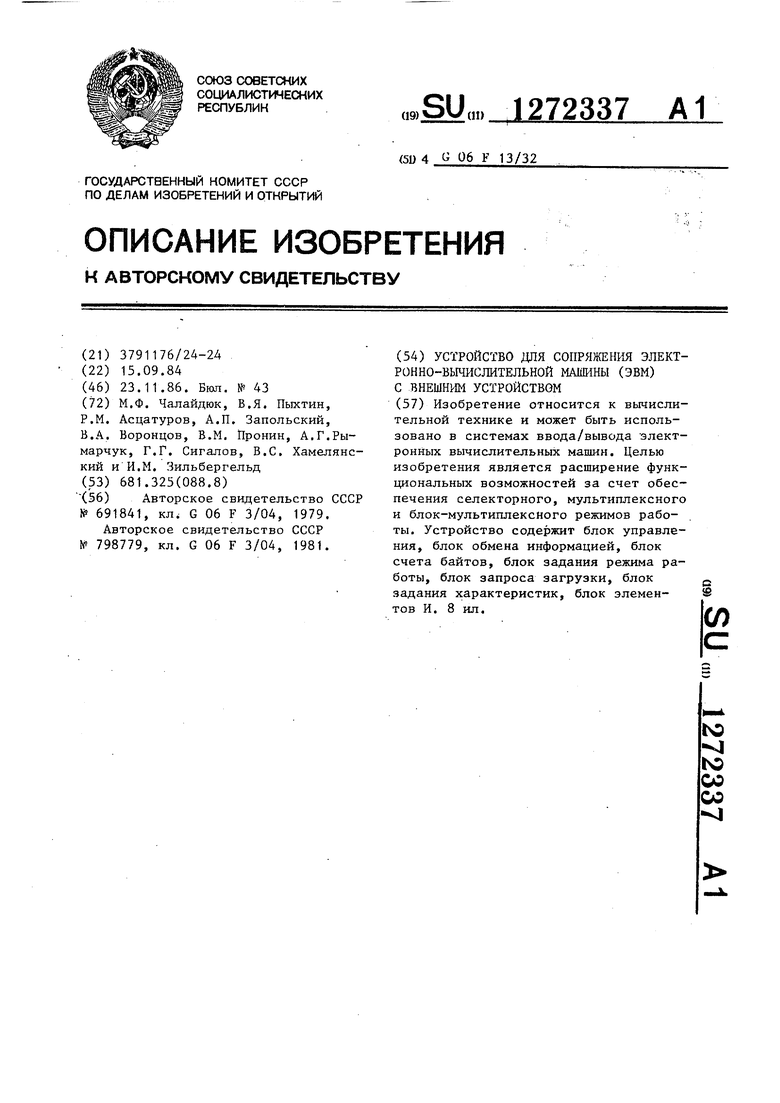

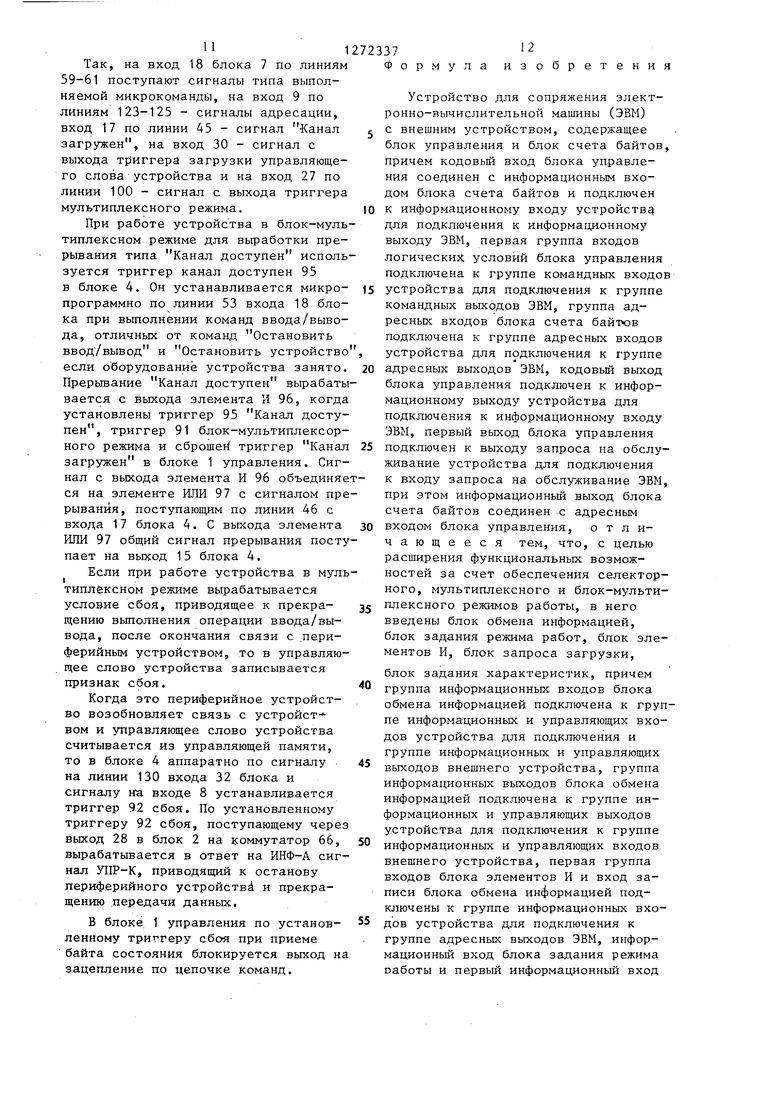

со со « Изобретение относится к вычислительной технике и может быть исполь зовано в системах ввода/вывода элек ронных вычислительных машин. Целью изобретения является расши рение функциональных возможностей за счет, обеспечения селекторного, мультиплексного и блок-мультиплексного режимов работы. На фиг. представлена структурна схема устройства; на фиг.2 - структурная схема блока управления; на фиг.З - структурная схема блока обмена информацией; на фиг,4 - структурная схема блока счета байтов; на фиг.З - функциональная схема блока задания режима работы; на фиг.6 функциональная схема блока запроса загрузки; на фиг.7 - функциональная схема блока задания характеристик; на фиг.З - функциональная схема бло ка элементов И. Устройство содержит (фиг,,1) блок 1 управления, блок 2 обмена информацией, блок 3 счета байтов, блок 4 задания режима работы, блок 5 запроса загрузки, блок 6 задания характеристик, .блок 7 логических условий, входную информационную шину 8 канала, группу 9 сигналов адресации, управляюш;ую шину 10 процессора, входную шину 11 интерфейса в/в, выходную информационную шину 12 канала, выходную шину 13 интерфейса в/в, выход 14 запроса на микропрограммное .обслуживание, выход 15 запроса на прерывание выход 16 регистра флажков управляющего сл ва канала, выходы 17 логических сос тояний канала, группу 18 установочных сигналов канала, выход 19 на за цепление по цепочке команд, выход 20 ненулевого байта состояния периф рийного устройства, выход 21 иденти фикатора байта состояния на входных пинах интерфейса в/в, выход 22 регистра адреса периферийного устройства, выход 23 установки триггера загрузки управляющего слова устройства, выход 24 условия обслуживани байта состояния на свободном канал инверсный выход 25 идентификатора логической связи с периферийным уст ройством, выход 26 блока адреса и счетчика байтов, группа выходов 27 режима работы канала, выход 28 сбо канала, выход 29 запроса на запоминание/загрузку управляющего слоя 372 устройства, выход 30 триггера загрузки управляющего слова устройства, выход 31 блока задания характеристик, выход 32 блока логических условий. Блок 1 управления хранит код операции, флажки выполняемой в данный момент операции ввода/вывода, формирует байт состояния канала, вырабатывает управляющие сигналы на основе дешифрации микрокоманды, состояния регистра .управления, производит выработку запросов на микропрограммное обслуживание, коммутирует оборудование канала на вход операционного блока процессора. Блок управления (фиг.2) содержит регистр 33 кода операции, дешифратор 34, регистр 35 байта состояния, коммутатор 36 канала, регистр 37 флажков, регистр 38 управления, второй элемент ИЛИ 39, элемент НЕ 40, второй элемент И 41, первый элемент И 42, триггер 43, первый элемент ИЛИ 44, Позициями 45-61 на фиг.2 обозначены соответствующие выходы блока 1. Блок 2 предназначен для организации связи между универсальным каналом и периферийными устройствами в соответствии с принципами интерфейса ввода/вывода. Блок 2 обмена информацией содержит (фиг.З) усилитель-приемник 62 управляющих сигналов, регистр 63 идентификаторов абонента, регистр 64 идентификаторов канала, усилитель-передатчик 65 управляющих сигналов, коммутатор 66 идентификаторов, первый элемент И 67, первый элемент ШШ 68, усилитель-приемник 69 информации, дешифратор 70 байта состояния, второй элемент И 71, сумматор 72 по модулю два, шестой элемент И 73, третий элемент И 74, регистр 75 адреса, усилитель-передатчик 76 информации, элемент НЕ 77, седьмой элемент И 78, четвертый элемент И 79, второй элемент ИЛИ 80, элемент 81 задержки, пятый элемент И 82, вход 83 записи регистра 75, Блок счета 3 байтов хранит ключ защиты, адрес данных и счетчик байт.ов выполняемой операции ввода/вывода. Блок счета байтов (фиг.4) содер кит регистр 84 ключей защиты, регистр 85 адреса данных, счетчик 86 байтов, входные линии 87-89. Блок 4 режима задания работы пр назначен для определения режима ра боты канала в зависимости от работающих периферийных устройств. Он содержит (фиг.5) первый элемент ИЛИ 90, первый триггер 91, .четверт триггер 92, второй элемент ИЛИ 93, второй триггер 94, третий триггер 95, третий элемент И 96, третий эл мент ИЛИ 97, элемент НЕ 98, выходы 99 и 100. Блок 5 запроса загрузки предназ начен для управления мультиплексир ванием при работе периферийных устройств, поддерживающих блок-мультиплексньй или мультиплексный режим. Он содержит (фиг.6) первый элемент ИЛИ 101, первьй элемент И 102, третий элемент ИЛИ 103, второй элемент И 104, первый и второй элементы НЕ 105 и 106, четвертый элемент 10 второй элемент ИЛИ 108, триггер 109 третий элемент И 110. Блок задания характеристик предназначен для установки и хранения допустимых режимов работы периферий ных устройств, типов подканалов, ко торые необходимо устанавливать при выполнении операций. Он содержит (фиг.7) блок 111 наборных переключателей из М переключателей, коммутатор 112, блок 113 переключателей, коммутатор 114, блок 115 наборных переключателей, коммутатор 116, триггер 117 сканирования. Блок элементов И предназначен для записи информации в аппаратуру канала из командного слова канала и из управляющего слова устройства при считывании их в область активного подканала местной локальной памяти. Он содержит (фиг.8) элемент И 118, элемент И 119, элемент И 120 элемент И 121, элемент И 122, входы 123-125, выходы 126-130. Данное устройство может применят ся в системах ввода/вывода ЕС ЭВМ.. Устройство может подключаться непосредственно к центральному процессору или входить как один из каналов в состав процессора ввода/ вывода. Центральный процессор управляет работой устройства с помощью специальных команд ввода/вывода. Обращение к программе канала осуществляется с помощью адресного слова канала, расположенного в фиксированной ячейке оперативной памяти. Адресное слово канала содержит ключ защиты и адрес первого управляющего слова канала. Программа канала состоит из последовательности управляющих слов канала. Управляющее слово канала содержит код операции, выполняемой операции в/в, начальный адрес данных, признаки режима работы канала и правила выборки следующего управляющего слова канала (флажки), длину массива (счетчик байтов). В состав устройства входят логические схемы, регистры, , позволяющие хранить информацию о выполняемой операции ввода/вывода. Так как оборудование устройства разделяется во времени несколькими операциями ввода/вывода, то управляющая информация об операциях ввода/ вывода хранится в областях управляющей или оперативной памяти центрального процессора, называемой п.одкана- лами. В подканале хранится: код операции, адрес данных, флажки, счетчик байтов, ключ защиты памяти, состояние канала, адрес следующего управляющего слова канала. Эта управляющая информация называется управляющим словом устройства. Так как в устройстве используется комбинированное аппаратно-микропрограммное управление, то для устройства, кроме логических схем, регистров и счетчиков, выделяется область быстродействующей местной памяти, в которой хранится управляющее слово устройства для активного подканала, т.е. подканала, связанного логически данный момент с устройством. Эта информация отражает условия завершения начальной выборки, текущее состояние или условия отсоединения периферийного устройства при последовательности окончания. В процессе передачи данных, продвижения по канальной программе управляющее лово устройства обновляется. Если стройство работает в селекторном ежиме, то управляющая информация ранится в его регистрах в течение сего времени выполнения операции вода/вывода, поскольку селекторный ежим имеет только один подканал навязывает периферийному устройсту монопольный режим. В мультиплексном и блок-мультиплексном режимах устройство способно обслуживать несколько периферийных устройств, для каждого из которых назначен свой подканал. В устройстве управляющая информация хранится в регистре 33 кода операции, регистре 37 флажков, регистре 35 байта состояния блока 1 управления, в регистре 84 ключа защиты, регистре 85 адреса данных, счетчике 86 байтов блока 3 счета байтов. Загрузка информации в эти регистр может производиться во время вьтолне ния соответствующей микропрограммы с помощью сигналов адресации и входных информационных шин, поступающих в устройство соответственно через входы 9 и 8. Микропрограммное управление устройством осуществляется посредством сигналов с выхода дешифратора 34 мик рокоманд. С цомощью сигналов, возбуждающих линии 48-58 выхода 18 блока 1 управления производятся микропрограммная установка и сброс тригге ров в других блоках устройства. По сигналам на линиях 59-61 этого же вы хода блока выполняются действия по загрузке оборудования устройства, св занные с выполнением определенных микрокоманд. При выполнении микрокоманды чтения данных устанавливается сигнал на линии 59, при микрокоманде обращения к оперативной памяти на линии 60, при микрокоманде обращения к управляюшей памяти - на, линии 61. Микропрограммно устанавливаются и сбрасываются триггеры регистра 38 управления блока 1 управления. К эт триггерам относятся следующее: триг гер Канал загружен - линия 45 выхода 17 блока 1 управления, триггер прерывания - линия 46 того же выход блока, триггер действительности адреса данных - линия 47. Триггер Канал загружен устанав ливается с момента выполнения опера ции ввода/вывода с использованием оборудования устройства. Триггер пр рывания устанавливается, когда в устройстве или на периферийном устройстве, подключенном к этому устройству, хранится прерывание. Тригг действительности адреса данных укаЭывает, что в регистре 85 адреса находится действительный адрес. Этот триггер устанавливается, когда выполняется микропрограмма загрузки адреса данных, а сбрасывается, когда при передаче данных использование адреса данных ограничивается обменом определенного объема данных, определяемом по изменению соответствующего разряда адреса данных (например, страничньш обмен при косвенной адресации в устройстве). В регистре 35 байта состояния блока управления фиксируются ошибки в управляющей информации канальной программы, ошибки в работе оборудования устройства. Микропрограммный анализ регистров устройства и отдельных триггеров, объединенных в регистры, производится в операционном блоке процессора через коммутатор 36 -канала, выход которого соединен с выходом 12 устройства. Условия запросов на микропрограммное обслуживание поступают на выход 14 устройства с выхода элемента ИЛИ 44. В блоке 1 управления вырабатываются запросы на микропрограммное обслуживание по приходу байта состояния периферийного устройства при завершении операции ввода/вывода и зацеплении по цепочке команд. Запрос по цепочке команд с выхода триггера 43 поступает на выход 19 блока 1 управления . Условия установки запросов этих типов вырабатываются в блоке 2 дешифратором 70 байта состояния и. элементом И 74, который выдает сигнал на выходе 21 блока 2 после отработки элемента задержки 81 при загруженном устройстве. Для работы дешифратора байта состояния из блока 1 управления через выход 16 блока в дешифратор байта состояния вьщаются состояния регистра 37 флажков. Через блок 2 устройство соединяется с периферийным устройством. На усилители-приемники 62 и 69 управляющих сигналов поступают сигналы интерфейса от периферийных устройств через вход 11 устройства. Усилители-передатчики идентификаторов канала 65 и информации 76 соединены с выходом 13 устройства. В регистре 75 адресахранится адрес периферийного устройства, которьц загружается микропрограммно при выполнении команды ввода/вывода или аппаратурно при связи по инициативе периферийного устройства. Регистр 64 идентификаторов канал используется для управления последовательностями интерфейса. .Прием байта состояния периферийного устройства в блоке 2 осуществл ется с помощью элементов И 73 и 74, элемента Ш1И 80, элемента 81 задерж ки. Прием адреса периферийного устро ства производится с помощью элементов И 78, элемента ИЛИ 80, элемента 81 задержки. По сигналу с выхода элемента 81 задержки производится анализ информации на выходах усилителей-приемни ков информации и контроль ее по паритету сложения по модулю 2 элементом 72. После сброса системы устройство находится в исходном состоянии и го тово к вьшолнению операции ввода-вы вода в одном из трех режимов блок-мультиплексном, селекторном или мул типлексном. В устройстве имеется блок 6 задания характеристик, на блоках 111,113,115 наборных переклю чателей, которого на группы перифери ных устройств, имеющих: последовательные адреса, набираются характеристики периферийных устройств. С п мощью переключателей можно задать режим работы, который должен поддерживаться устройством, тип подканала и другие характеристики. Через групп коммутаторов 112, 114, 116 блока б задания характеристик, управляемых с помощью триггера 117 сканирования и соответствующей константы в регист ре 75 адреса блока 2, происходит считывание состояний блоков наборных переключателей. 1 1 1 ,1 13, 115 по группа адресов периферийных устройств через коммутатор 36 капала блока 1 управления в управляющую память процессора. В результате, в управляющей памяти процессора формируется таблица указателей характеристик периферийных устройств. Эта процедура формировдния таблицы характеристик производится во время выполнения микропвограммы сброса системы. Режим работы, в котором должно находиться устройство, определяется на основе таблицы характеристик по адресу периферийного устройства во время выполнения комавды ввода/ вывода Начать ввод/вывод. При запуске периферийного устройства, работающего в мультиплексном режиме, микропрограммно устанавливается триггер 94 мультиплексного режима блока 4. Если периферийное устройство поддерживает блок-мультиплексньш режим и нулевой бит нулевого управляющего регистра процессора в единичном состоянии, то микропрограммно устанавливается триггер 91 блок-мультиплексного режима. При работе канала в селекторном режиме триггеры мультиплексного и блок-мультиплексного режима сброшены. Режим работы устройства управляет продолжительностью связи по интерфейсу ввода/вывода между устройством и периферийным устройством, формированием запроса на закаливание управляющего слова устройства в управляющую память процессора или формированием запроса на загрузку управляющего слова устройства в оборудование устройства. Продолжительность связи по интер- , фейсу ввода/вывода определяется устройством и периферийным устрозштвом. Возможность управления длительностью связи со стороны устройства обеспечивается триггером ВБР-К регистра идентификаторов канала 64 блока интерфейса 2. Периферийное устройство не может прерывать связь и отключаться от интерфейса ввода/вывода до тех пор, пока канал не сбросит ВБР-К.Периферийное устройство поддерживает связь с устройством после сброса ВБР-К до тех пор,пока текущая последовательность сигналов интерфейса ввода/вывода не будет закончена. Триггер ВБР-К сбрасывается через элемент ИЛИ 68 блока 2 микропрограммно по сигналу на линии 58, в блокмультиплексном режиме сбрасывается по сигналу с выхода элемента И 71, в мультиплексном режиме - по сигнау с выхода элемента И 67. При работе устройства в блок-мультиплексном реиме сигнал сброса триггера ВБР-К оявляется по приему байта состояния признаком Канал кончил. Это позоляет освобождать устройство при ыполнении цепочки команд после приеа байта состояния Канал кончил.

при работе устройства в мультиплексном режиме триггер ВБР-К сбрасывается во время выполнения начальной выборки по приходу сигнала АДР-А Если устройство работает в ceлekтopном режиме, то при цепочке команд периферийное устройство остается подключенным к устройству до приема байта состояния с признаком Устройство кончило.

Таким образом, в мультиплексном режиме периферийное устройство может отсоединиться от устройства в течение выполнения команды канала, а в блок-мультиплексном режиме только 15 после выполнения передачи всех данных по текущему управляющему слову канала. Отсоединение периферийного устройства позволяет освободить устройство дЛя выполнения других операций ввода/вывода. Запрос на запоминание управляющег слова устройства в память подканалов вырабатывается элементами И 102, ШШ 101, И 104, элементом НЕ 105, блока запроса загрузки. При этом оборудование устройства должно быть загру кено, не должно быть запроса на зацепление по цепочке команд, и связь с периферийным устройством закончена. Эти условия обеспечиваются установленным триггером Канал загру жен в блоке 1 управления, сброшенны триггером РАБ-А в регистре идентификаторов абонента 63 блока 2, сброшен ным триггером 43 блока 1 управления При этом для мультиплексного режима триггер действительности адреса регистра 38 управления блока 1 управл ния должен быть установлен. Во время микропрограммного обслуживания состояния регистров кода операции, адр са данных, флажков, счетчика байтов байта состояния считываются через коммутатор 36 канала в местную ло-. кальную память для формирования управляющего слова устройства, которо загружается в память пассивных подканалов, I Во время выборки по требованию в результате приема адреса периферийного устройства без сбоя по пари тету на выходе элемента И 82 блока 2 вырабатывается сигнал установки триггера 109 загрузки управляющего слова устройства. Этот сигнал поступает в блок запроса загрузки с выхода 23 блока 2. По этому сигналу

.7233710

при сброшенном триггере Канал загружен, на выходе элемента И 107 вырабатывается запрос на загрузку управляющего слова устройства, За5 прос этого же типа вьфабатывается элементом И 110 по сигналу с выхода элемента И 73 блока 2 при условии, что устройство свободно. Это условие используется для обработки треtO бования от периферийных устройств, для которых прерывание типа Канал кончил по .завершении операции ввода/вывода уже обработано или которые переводят из состояния Не готон в состояние Готов, Если выборка по требованию со стороны периферийного устройства произошла изтза того, что оно готово для выполнения следующей команды из ранее начатой канальной программы или готово выполнить передачу данных по ранее вьщанной команде ему устройством, то микропрограмма считывает управляющее слово устройства из памяти подканалов в зоне активного подканала, расположенного в быстродействующей местной локальной памяти. Для ускорения загрузки аппаратных регистров устройства блоком 7 вырабатывается группа сигналов, возбуждающая линии 126-130, поступаюшде на выход 32 загрузки оборудования блока. Сигналы на линиях 126 и 127, вырабатываемые соответственно элемейтами И 118 и 119, используются для управления записью в аппаратные регистры при считывании из оперативной памяти соответственно первой и второй частей управляющего слова канала , Из первой части в регистры устройства загружаются код операции, адрес данных, из второй - флажки, счетчик байтов. Сигналы на линиях 128-130, вьфабатываемые соответственно элементами И 120-122 используются для управления занесением соответственно первой, второй и третьей частей управляющего слова устройства из управляющей памяти. Выработка сигналов управления записью происходит по сигналам адресации местной памяти типа выполняемой микрокоманды и состояния устройства, когда управляющая информация находится на информационных шинах, поступающих на вход 8 устройства. 1 Так, на вход 18 блока 7 по линиям 59-61 поступают сигналы типа выполняемой микрокоманды, на вход 9 по линиям 123-125 - сигналы адресации, вход 17 по линии 45 - сигнал -Канал загружен, на вход 30 - сигнал с выхода TjJHrrepa загрузки управляющего слова устройства и на вход 27 по линии 100 - сигнал с выхода триггера мультиплексного режима. При работе устройства в блок-муль типлексном режиме для выработки прерывания типа Канал доступен исполь зуется триггер канал доступен 95 в блоке 4. Он устанавливается микропрограммно по линии 53 входа 18 блока при выполнении команд ввода/вывода, отличных от команд Остановить ввод/вывод и Остановить устройство если оборудование устройства занято. Прерьгоание Канал доступен вырабаты вается с выхода элемента И 96, когда установлены триггер 95 Канал доступен, триггер 91 блок-мультиплексорного режима и c6pomeri триггер Канал загружен в блоке 1 управления. Сигнал с выхода элемента И 96 объединяе ся на элементе ИЛИ 97 с сигналом пре рывания, поступающим по линии 46 с входа 17 блока 4. С выхода элемента ИЛИ 97 общий сигнал прерывания посту пает на выход 15 блока 4. Если при работе устройства в муль типлексном режиме вырабатывается условие сбоя, приводящее к прекращению вьшолнения операции ввода/вывода, после окончания связи с периферийным устройством, то в управляющее слово устройства записывается признак сбоя. Когда это периферийное устройство возобновляет связь с устройст- вом и управляющее слово устройства считывается из управляющей памяти, то в блоке 4 аппаратно по сигналу . на линии 130 входа 32 блока и сигналу на входе 8 устанавливается триггер 92 сбоя. По установленному триггеру 92 сбоя, поступающему чере выход 28 в блок 2 на коммутатор 66, вырабатывается в ответ на ИНФ-А сиг нал У11Р-К, приводящий к останову периферийного устройств и прекращению .передачи данных. В блоке 1 управления по установленному триггеру сбоя при приеме байта состояния блокируется выход н зацепление по цепочке команд. 37 бретения Формула Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством, содержащее блок управления и блок счета байтов, причем кодовьй вход блока управления соединен с информационным входом блока счета байтов и подключен к информационному входу устройству для подключения к информационному выходу ЭВМ, первая группа входов логически54 условий блока управления подключена к группе командных входов устройства для подключения к группе командных выходов ЭВМ, группа адресных входов блока счета байтюв подключена к группе адресных входов устройства для подключения к группе адресных выходов ЭВМ, кодовый выход блока управления подключен к информационному выходу устройства для подключения к информационному входу ЭВМ, первый выход блока управления подключен к выходу запроса на обслуживание устройства для подключения к входу запроса на обслуживание ЭВМ, при этом информационный выход блока счета байтов соединен с адресным входом блока управления, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения селекторного, мультиплексного и блок-мультиплексного режимов работы, в него введены блок обмена информацией, блок задания режима работ, блок элементов И, блок запроса загрузки, блок задания характеристик, причем группа информационных входов блока обмена информацией подключена к группе информационных и управляющих входов устройства для подключения и группе информационных и yпpaвляюш x выходов внешнего устройства, группа информационных выходов блока обмена информацией подключена к группе информационных и управляющих выходов устройства для подключения к группе информационных и управляющих входов внешнего устройства, первая группа входов блока элементов И и вход записи блока обмена информацией подключены к группе информационных входов устройства для подключения к группе адресных выходов ЭВМ, информационньй вход блока задания режима оаботы и первый информационный вход блока обмена информацией подключен к информационному входу устройства для подключения к информационному выходу ЭВМ, выход прерывания блока задания режима работы подключен к выходу требования прерывания устрой ства для подключения к входу прерывания ЭВМ, при этом второй выход блока управления соединен с вторым информационным входом блока обмена информацией, группа установочных входов которого, а также группа установочных входов блока задания характеристик, первый установочный вход блока запроса загрузки, группа установочных входов блока задания режима работы и вторая группа входо блока элементов И соединены с соответствующими разрядами первой групп выходов блока управления, вход логи ческих условий блока обмена информа цией, а также группа входов логичес ких условий блока запроса загрузки, первый вход блока элементов И и гру па входов логических условий блока задания режима работы соединены с соответствующими разрядами второй группы выходов блока управления, третий выход которого соединен с пе вым входом логических условий блока запроса загрузки, информационный выход которого соединен с вторым входом блока элементов И, группа выходов которого соединена с группой входов записи (считывания блока счета байтов, с второй группой входов логических условий блока управления, с тактовым входом блока задаi ля режима работы, первый вход логических условий блока управления, а также третий вход блока элементов И, вход режима работы блока запроса загрузки и группа входов режима работы блока обмена информацией соедй нены с соответствующими разрядами выходов режима работы группы блока, задания режима работы, выход сбоя .канала которого соединен с третьим информационным входом блока обмена информацией и с вторым входом логических условий блока управления, вх байта состояния которого соединен с выходом байта состояния блока обмена информацией, выход идентификатора байта состояния которого соединен с входом идентификатора байта состоя ния блока управления, вход запроса которого соединен с. выходом запроса 37 блока запроса загрузки, вход идентификатора логической связи, второй вход логических условий и второй установочный вход которого соединены с выходом идентификатора логической связи, с выходом логических условий и установочным выходом блока обмена информацией соответственно, адресный выход которого соединен с адресными входом блока задания х-арактеристик, информационный выход которого соединен с третьим входом логических условий блока управления, причем блок управления содержит коммутатор канала, регистр байта состояния, регистр кода операции, регистр флажков, регистр управления, дешифратор, триггер, два элемента ИЛИ, два элемента И, элемент НЕ, причем первый, второй и третий информационные в-ходы коммутатора канала являются первым входом логических условий, адресным входом и третьим входом логических условий блока управления соответственно, :. группа информационных входов дешифратора образует первую группу входов логических условий блока управления, входы записи и считывания регистра кода операции, вход записи, регистра байта состояния, входы записи и считьшания регистра флажков образуют вторую группу входов логических условий блока управления, информационный вход .регистра байта состояния соединен с информационными входами регистра кода операции и регистра флажков и является кодовым входом блока управления, первый вход первого элемента ИЛИ является входом запроса блока управления, первьй вход первого элемента И соединен с первым входом второго элемента И и является входом идентификатора байта состояния блока управления, первый и второй входы второго элемента ИЛИ являются вторым входом логических условий и входом байта состояния блока управления соответственно, информационный выход коммутатора канала является кодовым выходом блока управления, группа выходов дешифратора образует первую группу выходов блока управления, группа выходов регистра управления соединена с группой управляющих входов коммутатора канала и образует вторую группу выходов блока управления, выход первого элеента ИЛИ является первым выходом блока управления, информационньш выход регистра флажков соединен с четвертым информационным входом ком мутатора, каналов и является вторым выходом блока управления, выход три гера соединен с вторым входом перво элемента ИЛИ и является третьим выходом блока управления, при этом в блоке управления нулевой вход тригг ра, вход считывания регистра байта состояния и информационный вход регистра управления соединены с соответствующими разрядами группы выход дешифратора, соответствующий разряд группы .выходов регистра управления соединен с вторыми входами первого и второго элементов И, выходы котор соединены с третьим входом первого элемента И и с единичным входом три гера соответственно, третий вход вт рого элемента И соединен с--выходом элемента НЕ, вход которого соединен с третьим входом первого элемента И и с выходом второго элемента ИЛИ, третий вход которого соединен с информационным выходом регистра байта состояния и с пятым информационным входом коммутатора канала, шестой информационньм вход которого соедин с информационным выходом регистра кода операции, причем блок обмена информацией содерлсит усилитель-прие ник управляющих сигналов, усилитель приемник информации, усилитель-пере датчик управляющих сигналов,.усилитель-передатчик информации, регистр идентификаторов абонента, регис идентификаторов канала, коммута- jp идентификаторов, дешифратор байта состояния, сумматор по модулю два, регистр адреса, два элемента ИЛИ, семь элементов И, элемент НЕ, элемент задержки, при этом группы информационных входов усилителей-приемников управляющих сигналов и информации образуют группу информацион ных входов блока обмена информацией единичный вход регистра идентификаторов канала и первый вход первого элемента ИЛИ- образуют группу установочных входов блока обмена информацией, первые входы первого и второго элементов И образуют группу входов режима работы блока обмена информацией, второй вход второго эле мента И соединен с первыми входами третьего и четвертого элементов И; с входом элемента НЕ и является вхо3376дом логических условий блока обмена информацией, первый информационньй вход регистра адреса является первым информационным входом блока обмена информацией, первый информационный вход дешифратора байта состояния и информационньй вход коммутатора идентификаторов являются вторым и третьим информационными входами блока обмена информацией соответственно, вход записи регистра адреса является входом записи блока обмена информацией, выходы усилителей-передатчиков управляющих сигналов и информации являются информационными входом блока обмена информацией, выход регистра адреса соединен с входом усилителяпередатчика информации и является адресным выходом блока обмена информацией, первый выход регистра идентификаторов абонента, выход дешифратора состояния, выходы третьего и пятого элементов и являются выходами идентификатор логической связи, байта состояния, идентификатора бай-. та состояния и установочным выходом блока обмена информацией соответственно, выход шестого элемента И соединен с третьим входом второго элег1мента И, с вторыми входами третьего и четвертого элементов И и является выходом логических условий блока обмена информацией, при этом в блоке обмена информацией выход усилителяприемника управляющих сигналов соединен с информационным входом регистра идентификаторов абонента, второй выход которого соединен с управляющим входом коммутатора идентификаторов, первый и второй выходы которого соединены с первым и вторым инфор-. мационными входами регистра идентификатора канала соответственно первый выход которого соединен с входом усилителя-передатчика управляющих сигналов, выход усилителя-приемника информации соединен с вторым информациоиньгм входом дешифратора байта состояния, с четвертым входом второго элемента И, с вторым информационньв входом регистра адреса, с входом сумматора по модулю два, выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с первым входом второго элеента ИЛИ и с выходом седьмого элеента И, первый вход которого соединен с вторым входом первого элемента

Лис третьим выходом регистра идентификаторов абонента, четвертый выход которого соединен с третьим входом первого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, третий вход которого соединен с выходом второго элемента И, пятый вход которого соединен с третьими входами третьего и пятого элементов И и с выходом элемента задержки, вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, выход элемента НЕ соединен с вторым входом седьмого элемента И, третий вход которого соединен с вторым выходом регистра идентификаторов канала, третий выход которого соединен с первым входом шестого элемента И, второй вход которого соединен с пятым выходом регистра идентификаторов абонента, выход первого элемента ИЛИ соединен с нулевым входом регистра идентификаторов канала, причем блок запроса загрузки содержит триггер, три элемента ИЛИ, четыре элемента И, два, элемента НЕ, причем первый вход первого элемента И является входом идентификатора логической связи блока запроса загрузки, первые входы первого элемента.ИЛИ и второго элемента И образуют группу входов режима работы блока запроса загрузки, второй вход второго элемента И и первый вход второго элемента ИЛИ образуют группу входов логических условий блока запроса загрузки, вход . первого элемента НЕ и первькй вход третьего элемента И являются первым и вторым входами логических уйловий блока запроса загрузки соответственно, второй вход второго элемента ИЛИ и единичный вход триггера являются первым и вторьЕ установочными входами блока запроса загрузки соответственно, вь1ход третьего элемента ИЛИ является выходом запроса блока запроса загрузки, выход триггера соединен с первьм входом четвертого элемента И и является информационньм выходом блока запроса загрузки, причем в

локе запроса загрузки выход второго лемента И соединен с вторым входом ервого элемента ИЛИ, выход которого оединен с вторым первого элеента И, выход которого соединен с ервым входом третьего элемента ИЛИ, второй и третий входы которого Соединены с выходами третьего и четвертого элементов соответственно, вторые вхоы которых соединены с выходом второго элемента НЕ, вход которого соединен с первым входом второго элемента ИЛИ и третьим входом первого элемента И, четвертьй вход которого соединен с выходом первого элемента НЕ, нулевой вход триггера соединен с выходом второго элемента ИЛИ, причем блок задания режима работы содержит четыре триггера, три элемента ИЛИ, элемент И, элемент НЕ, при этом единичные входы первого, второго, и третьего триггеров, нулевые входы третьего и четвертого триггеров, первые и вторые входы первого и второго элементов ИЛИ образуют группу установочных входов блока задания режима работы, первый вход третьего элемента ИЛИ и вход элемента НЕ образуют группу входов Логических условий блока задания режима работы, информационный и тактовый входы четвертого триггера являются информационным PI тактовым входами блока задания режима работа соответственно, вьгкоды первого и второго триггеров образуют группу выходов режима работы блока задания режима работы, выходы четвертого триггера и третьего элемента ИЛИ являются выходами сбоя канала и прерывания блока задания режима работы соответственно, при этом в блоке задания режима работы выходы первого, третьего триггеров и выход элемента НЕ соединены С-первым, вторым и третьим входами элемента И соответственно, выход которого соединен с вторым входом третьего элемента ИЛИ, выходы цервого, и второго элементов ИЛИсоединены с нулевьми входами первого триггеров соответственно.

//

/J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для сопряжения процессора с периферийными устройствами | 1985 |

|

SU1359780A1 |

| Устройство для формирования сигнала подключения периферийного устройства к каналу ввода-вывода | 1985 |

|

SU1247881A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1256036A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Устройство управления для мультиплексного канала | 1984 |

|

SU1265787A1 |

| Селекторный канал | 1978 |

|

SU798779A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах ввода/вывода электронных вычислительных машин. Целью изобретения является расширение функциональных возможностей за счет обеспечения селекторного, мультиплексного и блок-мультиплексного режимов рабо- . ты. Устройство соде|5жит блок управления, блок обмена информацией, блок счета байтов, блок задания режима работы, блок запроса загрузки, блок с S задания характеристик, блок элементов И. 8 ил. (Л

18 28

27 16

SJ

22

Фаг. 5

К

/f(l

т

126

18

3227

18

Фиг. 5

Фиг. 6

| Блок-мультиплексный канал | 1977 |

|

SU691841A1 |

| Селекторный канал | 1978 |

|

SU798779A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-23—Публикация

1984-09-15—Подача