(54) УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ

1

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ для автоматической отладки программ.

Известно устройство для отладки программ, содержащее память типа ОЗУ, куда при отладке записываются адре- ; са условных и безусловных переходов 1 .

Известно устройствоj в котором на двух регистрах запоминаются адреса двух последних переходов 2.

Известно также устройство, в котором отладка программ.осуществляется путём передачи управления с уровня программы отладчика на уровень отлаживаемой программы, выполнения одной команды отлаживаемой программы, запоминания информации о. состоянии отлаживаемой программы в блоке хранения и возврата управления на уровень программы отладчика. Для этого устройство содержит триггер сбоя, триггер автоматического переключения, триггеры возврата, четыре ряда клапанов и логические схемы И, ИЛИ и НЕ 3 .

Недостатком этих устройств является то, что в них регистрируют

только один из многих возможных типов программных событий, сведения в которых нужны при отладке программ.

, Наиболее близким к изобретению по техническойсущности является устройство регистрации программных событий, позволяющее зарегистрировать, а затем сообщить управляющей прог10рамме сведения о поступлении таких событий, происшедших в ходе выполнения команды отлаживаемой программы, как выборка команды из заданной области оперативной памяти, изменение содержимого заданных ячеек оперативной пгю1яти, изменение содержимого заданныхрегистров общего, назначения и успешное выполнение команды перехода. Анализ наступления

20 первых трех типов событий njioHsaoдится перед выполнением команды, анализ успешного выполнения команды перехода производится после выполнения команды. Устройство работает

25 непосредственно с процессором ЭВМ и содержит блок управления, местную память, регистр команд, коммутатор и буферный регистр, первый вход которого соединен с первым выходом

30 коммутатора, второй вход соединен .

с первым выходом блока управления, а первый выход соединен с первьом входом местной памяти, второй вход которой соединен с вторым выходом узла управления, а выход соединен с третьим входом буферного регистра второй выход которого соединен с первым входом коммутатора, второй вход которого соединен с первым выходом регистра команд, первый вход которого соединен с третьим выходом узла управления, первый вход которого соединен с вторым выходом регистра команд, второй вхо которого соединен с вторым выходом коммутатора, третий вход которого через первую входную шину устройства соединен с выходом KOMiviyTaTopa процессора ЭВМ, вход которого через первую выходную шину устройства соединен с третьим выходом коммутатор четвертый вход которого соединен с четвертым выходом блока управления пятый выход которого через вторую выходную шину устройства соединен, с входом устройства управления процессора ЭВМ, выход которого через вторую входную шину устройства подается на второй вход блока управления.

В. этом устройстве регистрация изменения содержимого заданных ячее оперативной памяти и заданных регистров общего назначения производится как и регистрация выборки команды из заданной области оперативной памяти, перед выполнением команды путем моделирования ее выполнения 4 .

Однако анализируемые события могут происходить не в каждой команде Для исключения анализа невозможных событий используются модификаторы возможных событий для каждой команды, которые хранятся в местной памяти, .что увеличивает ее объем. Кроме того, управляющей программе в ходе выполнения отлаживаемой программы необходиь/ш сведения о наступлении изменения содержимого заданных регистров с плавающей точкой и выполнения команды с заданным кодом операции, а также некоторой предЫстории в виде последовательности команд, выполняющихся процессором ЭВМ перед текущей командой, чего же позволяет сделать известное устройСТВО. Цель изобретения - расширение функций устройства за счет обеспечения возможности фиксации событий, связанный с изменением содержания регистров и группы ячеек памяти.

Поставленная цель достигается тем, что в устройство,, содержащее блок управления, блок местной памяти, регистр команд, коммутатор и буферный регистр, причем первый, второй и третий выходы коммутатора соединены соответственно с первым входом буферного регистра, первым

выходом устройства и первым входом регистра команд, первый и второй выходы которого соединены соответственно с первым входом коммутатора и. первым входом блока местной - памяти, первый, второй, третий, четвертый и пятый выходы блока управления соединены соответственно с вторым входом буферно о регистра вторым выходом устройства, вторым

- входом коммутатора, вторым входом регистра команд, вторым входом блока местной памяти, выход которого соединен с третьим входом буферного регистра, первый и второй выходы буферного регистра соединенные соответственно с третьим входом коммутатора и третьим входом блока местной памяти, первый и второй входы устройства соединены соответственно с четвертым входом коммутатора

0 и перВЕам входом блока управления, введены дешифратор, узел регистрации и блок стековой памяти, причем третий выходрегистра.команд соединен с входом дешифратора, выход

5 которого соединен с вторым входом блока- управления, шестой и седьмой выходы блока управления соединены соответственно с первым входом : блока стековой памяти и входом узла

.. регистрации, .выход- которого соединен с третьим входом блока управления, выход блока стековой памяти соединен с четвертым входом буферного регистра, третий выход которого соединен с вторым входом блока стековой памяти.

Кроме того, блок управления содержит формирователь адреса микрокоманд, регистр адреса микрокоманд, блок памяти микрокоманд, регистр микрокоманд и дешифратор, причем выход формирователя адреса микрокоманд соединен с входом регистра микрокоманд, выход которого соединён

с входом блока памяти микрокоманд/ выход блока памяти микрокоманд соединен с входом регистра микрокоманд, первый и второй выходы которого соединены соответственно с первым входом формирователя адреса микрокоманд и первым входом дешифратора, первый выход дешифратора соединен с вторым входом формирователя адреса микрокоманд, остальные выходы

дешифратора образуют группу выходов блока, первый, второй и третий входы блока соединены с третьим, четвертым и пятым входами формирователя адреса микрокоманд, второй и

третий входы блока соединен с вторым и третьим входом дешифратора.

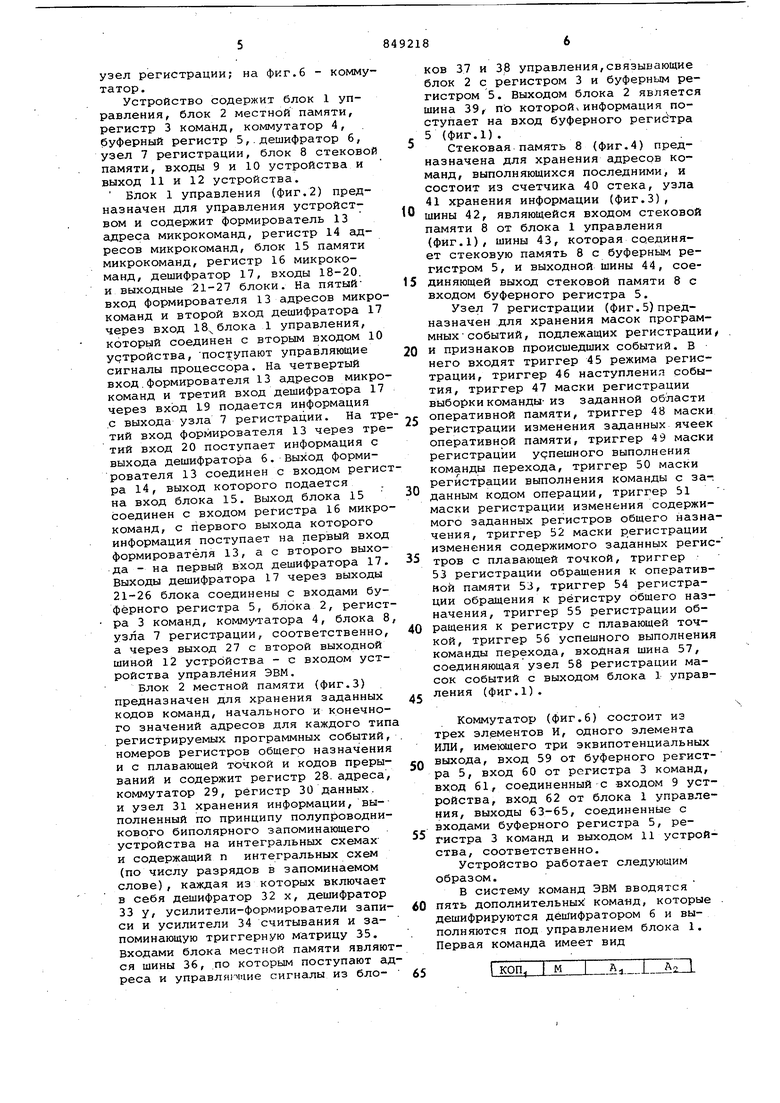

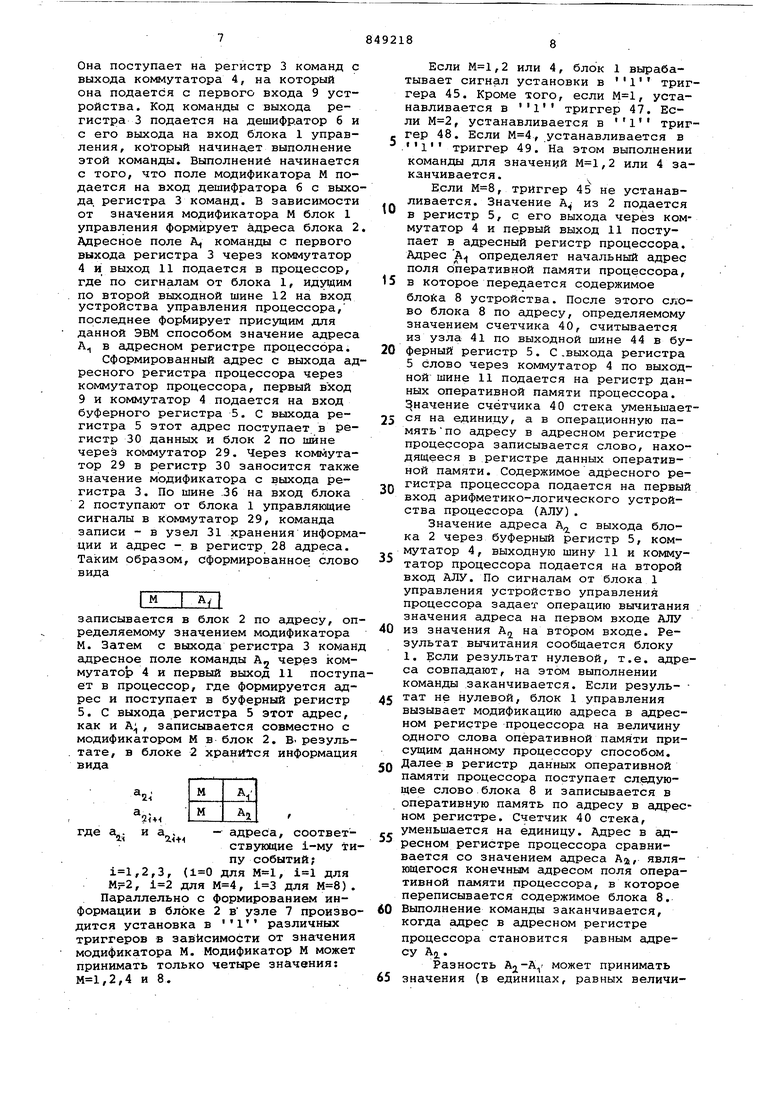

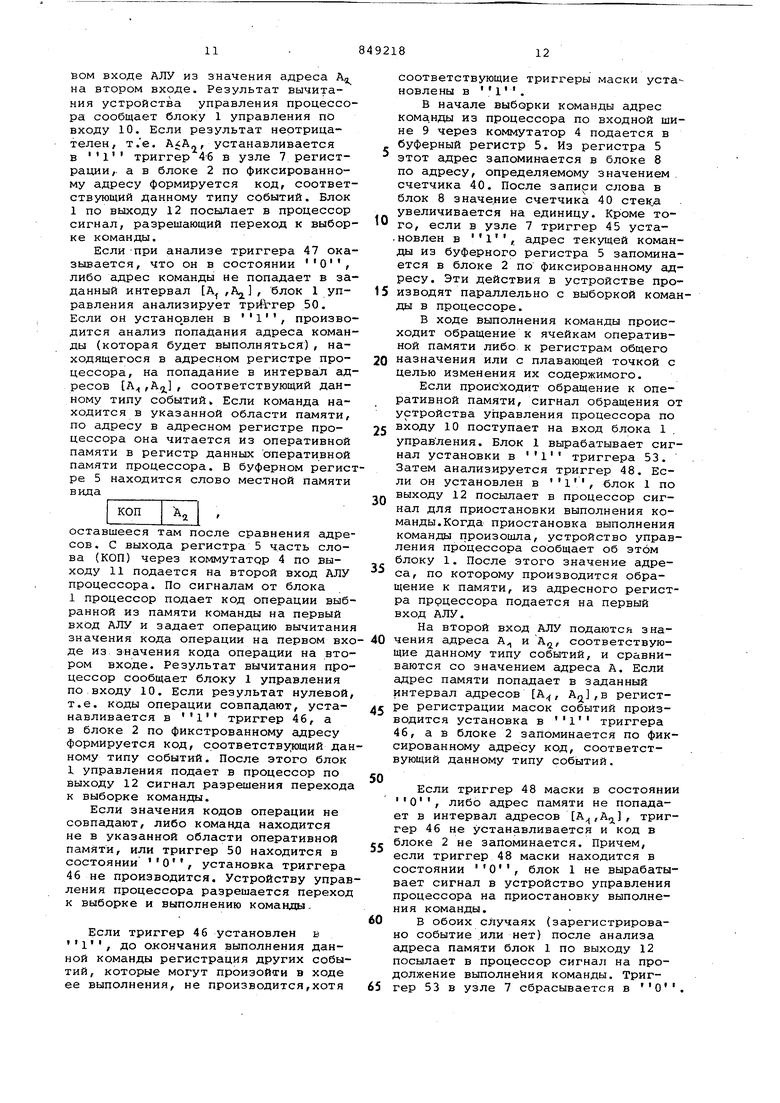

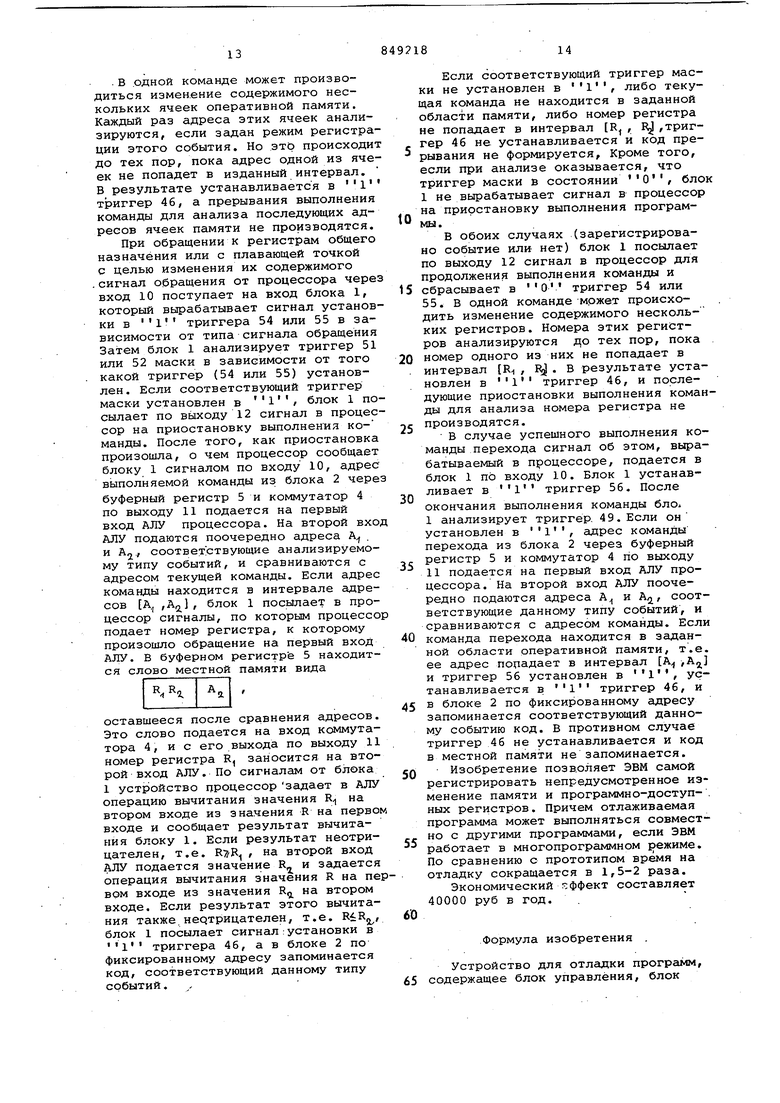

На фиг.1 представлена блок-схема устройства для отладки программы; на фиг.2 - блок управления; на фиг.З - блок местной памяти; на

фиг.4 - стековая память; на фиг.З узел регистрации; на фиг.6 - коммутатор.

Устройство содержит блок 1 управления, блок 2 местной памяти, регистр 3 команд, коммутатор 4, буферный регистр 5,.дешифратор 6, узел 7 регистрации, блок 8 стековой памяти, входы 9 и 10 устройства и выход 11 и 12 устройства.

Блок 1 управления (фиг.2) предназначен для управления устройством и содержит формирователь 13 адреса микрокоманд, регистр 14 адресов микрокоманд, блок 15 памяти микрокоманд, регистр 16 микрокоманд, дешифратор 17, входы 18-20. и выходные 21-27 блоки. На пятый вход формирователя 13 адресов микрокоманд и второй вход дешифратора 17 через вход 18 блока 1 управления, который соединен с вторым входом 10 удтройства, поступают управляющие сигналы процессора. На четвертый вход.формирователя 13 адресов микрокоманд и третий вход дешифратора 17 через вход L9 подается информация .с выхода узла 7 регистрации. На тртий вход формирователя 13 через третий вход 20 поступает информация с выхода дешифратора 6. Выход формирователя 13 соединен с входом регисра 14, выход которого подается на вход блока 15. Выход блока 15 соединен с входом регистра 16 микрокоманд, с первого выхода которого информация поступает на первый вход формирователя 13, а с второго выхода - на первый вход дешифратора 17. Выходы дешифратора 17 через выходы 21-26 блока соединены с входами буферного регистра 5, блока 2, регистра 3 команд, комму-татора 4, блока 8 узла 7 регистрации, соответственно, а через выход 27 с второй выходной шиной l2 устройства - с входом устройства управления ЭВМ.

Блок 2 местной памяти (фиг.З) предназначен для хранения заданных кодов команд, начального и конечного значений адресов для каждого тип регистрируемых программных событий, номеров регистров общего назначения и с плавающей точкой и кодов прерываний и содержит регистр 28. адреса, коммутатор 29, регистр 30 данных, и узел 31 хранения информации, выполненный по принципу полупроводникового биполярного запоминающего устройства на интегральных схемах и содержащий п интегральных схем (по числу разрядов в запоминаемом слове), каждая из которых включает в себя дешифратор 32 х, дешифратор 33 у, усилители-Формирователи записи и усилители 34 считывания и запоминающую триггерную матрицу 35. Входами блока местной памяти являются шины 36, по которым поступают адреса и управля1пиие сигналы из блоков 37 и 38 управления,связывающие блок 2 с регистром 3 и буферным регистром 5. Выходом блока 2 является шина 39, по которой ч информация поступает на вход буферного регис тра 5 (фиг.1).

Стековая память 8 (фиг.4) предназначена для хранения адресов команд, выполняющихся последними, и состоит из счетчика 40 стека, узла 41 хранения информации (фиг.З),

0 шины 42, являющейся входом стековой памяти 8 от блока 1 управления (фиг.1), шины 43, которая соединяет стековую память 8 с буферным регистром 5, и выходной шины 44, сое5диняющей выход стековой памяти 8 с входом буферного регистра 5.

Узе.л 7 регистрации (фиг. 5) предназначен для хранения масок программных событий, подлежащих регистрации

0 и признаков происшедших событий. В него входят триггер 45 режима регистрации, триггер 46 наступления, события, триггер 47 маски регистрации выборки команды-из заданной области оперативной памяти, триггер 48 маски

5 регистрации изменения заданных ячеек оперативной памяти, триггер 49 маски регистрации успешного выполнения команды перехода, триггер 50 маски регистрации выполнения команды с за-,

0 данным кодом операции, триггер 51 маски регистрации изменения содержимого заданных регистров общего назначения, триггер 52 маски регистрации изменения содержимого заданных регис5тров с плавающей точкой, триггер 53 регистрации обращения к оперативной памяти 53, триггер 54 регистрации обращения к регистру общего назначения, триггер 55 регистрации обращения к регистру с плавающей точ0кой, триггер 56 успешного выполнения команды перехода, входная шина 57, соединяющая узел 58 регистрации масок событий с выходом блока 1 управления (фиг.1).

5

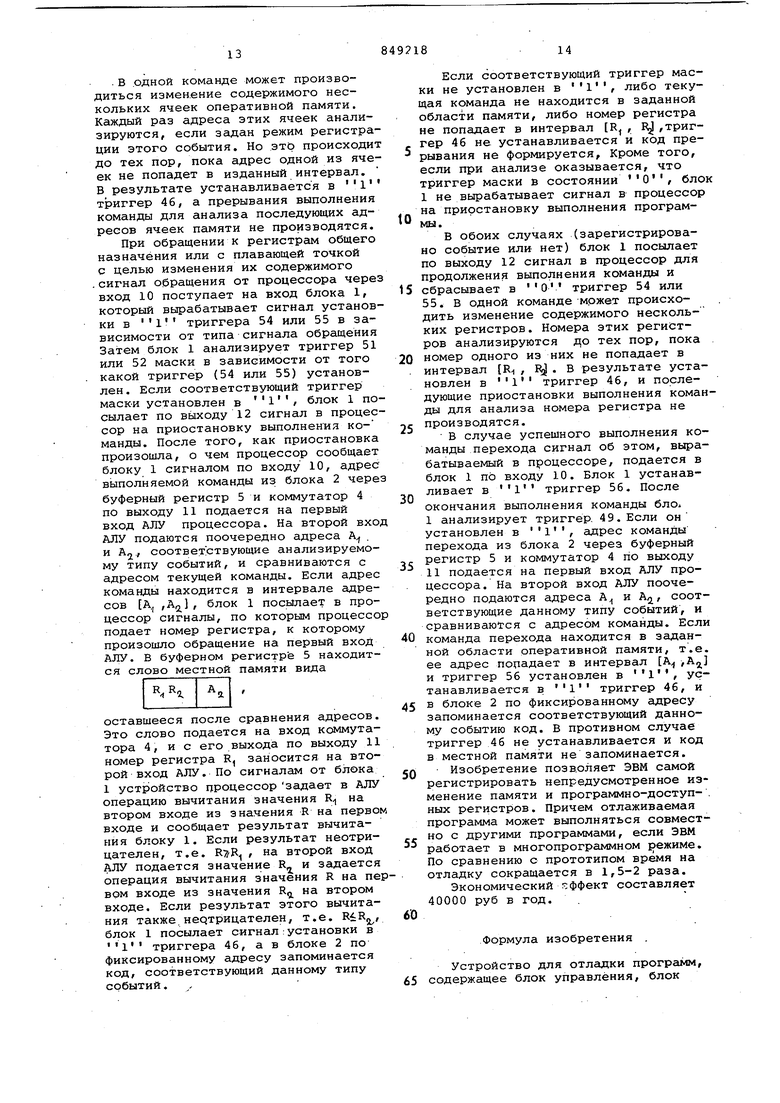

Коммутатор (фиг.6) состоит из трех элементов И, одного элемента ИЛИ, имекяцего три эквипотенциальных выхода, вход 59 от буферного регист0ра 5, вход 60 от регистра 3 команд, вх:од 61, соединенный с входом 9 устройства, вход 62 от блока 1 управления, выходы 63-65, соединенньае с входами буферного регистра 5, ре5гистра 3 команд и выходом 11 устройства, соответственно.

Устройство работает следующим образом.

В систему команд ЭВМ вводятся

0 пять дополнительных команд, которые . дешифрируются дешифратором 6 и выполняются под управлением блока 1. Первая команда имеет вид

nzimzi

м

КОП

65

Она поступает на регистр 3 команд с выхода коммутатора 4, на который она подается с первого входа 9 устройства. Код команды с выхода регистра 3 подается на дешифратор 6 и с его выхода на вход блока 1 управления, который начинает выполнение этой команды. Выполнение начинается с того, что поле модификатора М подается на вход дешифратора 6 с выхода, регистра 3 команд. В зависимости от значения модификатора М блок 1 управления формирует адреса блока 2. Адресное поле А команды с первого выхода регистра 3 через коммутатор 4 и выход 11 подается в процессор, где по сигналам от блока 1, ид5,тдим по второй выходной шине 12 на вход устройства управления процессора, последнее формирует присущим для данной ЭВМ способом значение адреса А в адресном регистре процессора.

Сформированный адрес с выхода адресного регистра процессора через коммутатор процессора, первый вход 9 и коммутатор 4 подается на вход буферного регистра 5. С выхода регистра 5 этот адрес поступает в регистр 30 данных и блок 2 по шине через коммутатор 29. Через коммутатор 29 в регистр 30 заносится также значение модификатора с выхода регистра 3. По шине -36 на вход блока 2 поступают от блока 1 управляющие сигналы в коммутатор 29, команда записи - в узел 31 хранения информации и адрес - в регистр 28 адреса. Таким образом, сформированное, слово вида

Н I А,|

записывается в блок 2 по адресу, определяемому значением модификатора М. Затем с выхода регистра 3 команд адресное поле команды Aj через коммутатор 4 и первый выход 11 поступает в процессор, где формируется адрес и поступает в буферный регистр 5. С выхода регистра 5 этот адрес, как и А, записывается совместно с модификатором М в блок 2. В результате, в блоке 2 хранится информация вида

гч

U

- адреса, соответи а.

0

где

2.-И ствующие 1-му типу событий;

,2,3, для , для , для , для ) . Параллельно с формированием информации в блоке 2 в узле 7 производится установка в 1 различных триггеров в зависимости от значения модификатора М. Модификатор М может принимать только четыре значения: ,2,4 и 8.

Если ,2 или 4, блок 1 вырабатывает сигнал установки в i триггера 45. Кроме того, если , устанавливается в триггер 47. Если , устанавливается в i триг. гер 48. Если , устанавливается в э « 1- I t триггер 49. На этом выполнении команды для значений ,2 или 4 заканчивается.

Если , триггер 45 не устанавливается. Значение А из 2 подается

в регистр 5, с его выхода через коммутатор 4 и первый выход 11 поступает в адресный регистр процессора. Адрес А определяет начальный адрес поля Оперативной памяти процессора,

5 в которое передается содержимое

блойа 8 устройства. После этого слово блока 8 по адресу, определяемому значением счетчика 40, считывается из узла 41 по выходной шине 44 в буферный регистр 5. С .выхода регистра 5 слово через коммутатор 4 по выходной шине 11 подается на регистр данных оперативной памяти процессора. Значение счётчика 40 стека уменьшается на единицу, а в операционную память по адресу в адресном регистре процессора записывается слово, находящееся в регистре данных оперативной памяти. Содержимое адресного реQ гистра процессора подается на первый вход арифметико-логического устройства процессора (АЛУ).

Значение адреса А с выхода блока 2 через буферный регистр 5, ком- мутатор 4, выходную шину 11 и коммутатор процессора подается на второй вход АЛУ. По сигналам от блока 1 управления устройство управления процессора задает операцию вычитания значения адреса на первом входе АЛУ

0 из значения AQ на втором входе. Результат вычитания сообщается блоку 1. Если результат нулевой, т.е. адреса совпадают, на этом выполнении команды заканчивается. Если резуль-

5 тат не нулевой, блок 1 управления вызывает модификацию адреса в адресном регистре процессора на величину одного слова оперативной памяти присущим данному процессору способом.

Q Далее в регистр данных оперативной памяти процессора поступает сл.едующее слово блока 8 и записывается в оперативную память по адресу в адресном регистре. Счетчик 40 стека, уменьшается на единицу. Адрес в адресном регистре процессора сравнивается со значением адреса Аа, являющегося конечным адресом поля оперативной памяти процессора, в которое переписывается содержимое блока 8.

0 Выполнение команды заканчивается, когда адрес в адресном регистре процессора становится равным адресу Ai.

Разность А-ц-А может принимать

5 значения (в единицах, равных величине слова), от О до т-1 (где m - глубина стековой памяти).

Таким образом, можно .считать в оперативную память процессора либо часть стековой памяти, либо все m слов.

Вторая команда имбет вид

где R. - номер регистров общего назначения в командах с кодами КОП ;

R. - номер регистров с плавающей точкой в- командах с кодами КОП ..

При выполнении этих команд, как и при выполнении команды с кодом КОП, в блоке 2 по адресам, соответствующим коду команд, запоминается информация

В узле -7 при выполнении обеих котригманд устанавливается в

гер 45. Кроме того, для команды с кодом КОП устанавливается в Ч триггер 51, а для команды с кодом КОП, устанавливается в 1тригге 52. Как и в команде с кодом КОП, 11 дреса, определяемые кодом команды. Для команды с кодом для команды с кодом КОП , для команды с кодом КОП, .

Пятая команда имеет вид

I KOng

М

После дешифрации кода операции дешифратором 6 на него подается модификатор Ми, В зависимости от значений битов модификатор, блок 1 управления производит следующие действия в узле 7 регистрации:

Если бит О модификатора равен

в О

О, сбрасывается гер 47.

Если бит 1 модификатора равен

О

0, сбрасывается в

триггер 48.

Если бит 2 модификатора равен О, сбрасывается в О триггер 49.

Если бит 3 модификатора равен О, Сбрасывается в О триг, гер 50.

Если бит 4 модификатора равен О , сбрасывается в О триггер 51. .

Если бит 5 модификатора равен

О

, сбрасывается в

тригo гер 52.

Если модификатор М весь нулевой или в ходе выполнения команды все триггеры 47-52 маски оказываются сброшенными в О, сбрасывается

5 в О триггер 45 режима регистра:7 ции. Больше в команде никаких действий не производится.

Перед выборкой любой команды из оперативной памяти процессораблок

0 1 управления анализирует триггер 46

в узле 7 регистрации. Если он установлен в 1 , блок 1 управления по второму выходу 12 посылает в устройство управления процессора

5 сигнал запроса на программное прерывание. Одновременно из блока 2 по фиксированному адресу считывается в буферный регистр 5 код прерыва-т : НИН. При входе в прерывание блок 1

Q посылает сигнал сброса в О триггера 46, а код прерывания с выхода регистра 5 через коммутатор 4 по первому выходу 11 подается в процессор.

c Если при анализе триггер 46 нахо- . дится в состоянии О, блок 1 управления анализирует триггер 45.

Если триггер в состоянии , т.е. режим регистрации задан, анализируется триггер 47. Если триггер

0 47 установлен в , адрес А,

соответствующий данному типу событий (это определяется блоком 1 управления, который задает соответствующий адрес из блока 2), с выхода блока 2

5 через буферный регистр 5 и коммутатор 4 по вьаходу 11 подается на второй вход АЛУ процессора. По сигналам от блока 1 процессор подает адрес команды, находящийся в адресQ ном регистре процессора, на первый вход АЛУ-и задает ь АЛУ операцию вычитания адреса А на втором входе из- адреса команды А- на первом входе. Результат вычитания устройство управf. ления процессора по второму входу 10 сообщает блоку 1 управления. Если результат неотрицателен, т.е. A,j. А, из блока 2 через регистр 5, коммутатор 4 и выход 11 подается адрес А„ на второй вход АЛУ процессора,

0 соответствующий ранному типу событий. По сигналам от блока 1 управлетригния процессор подает на первый вход АЛУ адрес команды из адресного .регистра процессора и задает операцию

5 вычитания значения адреса А на пер-. BOM входе АЛУ из значения адреса А, на втором входе. Результат вычитания устройства управления процессора сообщает блоку 1 управления по входу 10. Если результат неотрицателен, т.е. , устанавливается в Ч триггер 46 в узле 7 регистрации, а в блоке 2 по фиксированному адресу формируется код, соответствующий данному типу событий. Блок 1 по выходу 12 посылает в процессор сигнал, разрешающий переход к выборке команды. Если при анализе триггера 47 оказывается, что он в состоянии либо адрес команды не попадает в заданный интервал А ,A,j. , блок 1 управления анализирует Tprfrrep 50. Если он установлен в , производится анализ попадания адреса коман ды (которая будет выполняться), находящегося в адресном регистре процессора, на попадание в интервал ад ресов А ,A,j , соответствующий данному типу событий k Если команда находится в указанной области памяти, по адресу в адресном регистре процессора она читается из оперативной памяти в регистр данных оперативной памяти процессора. В буферном регис ре 5 находится слово местной памяти вида оставшееся там после сравнения адре сов. С выхода регистра 5 часть слова (КОП) через коммутатор 4 по выходу 11 подается на второй вход АЛУ процессора. По сигналам от блока 1 процессор подает код операции выб ранной из памяти команды на первый вход АЛУ и задает операцию вычитани значения кода операции на первом вхо де из значения кода операции на вто ром входе. Результат вычитания процессор сообщает блоку 1 управления по входу 10. Если результат нулевой т.е. коды операции совпадают, устанавливается в триггер 46, а в блоке 2 по фикстрованному адресу формируется код, соответствующий дан ному типу событий. После этого блок 1, управления подает в процессор по выходу 12 сигнал разрешения перехода к выборке команды. Если значения кодов операции не совпадают, либо команда находится не в указанной области оперативной памяти, или триггер 50 находится в состоянии О, установка триггера 46 не производится. Устройству управ ления процессора разрешается переход к выборке и выполнению команды, Если триггер 46 установлен в , до окончания выполнения данной команды регистрация других событий, которые могут произойти в ходе ее выполнения, не производится,хотя соответствующие триггеры маски уста новлены в . В начале выборки команды адрес кома.нды из процессора по входной шине 9 через коммутатор 4 подается в буферный регистр 5. Из регистра 5 этот адрес запоминается в блоке 8 по адресу, определяемому значением счетчика 40. После записи слова в блок 8 значение счетчика 40 стека увеличивается на единицу. Кроме того, если в узле 7 триггер 45 установлен в , адрес текущей команды из буферного регистра 5 запоминается в блоке 2 по фиксированному адресу. Эти действия в устройстве производят параллельно с выборкой команды в процессоре. В ходе выполнения команды происходит обращение к ячейкам оперативной памяти либо к регистрам общего назначения или с плавающей точкой с целью изменения их содержимого. Если происходит обращение к оперативной памяти, сигнал обращения от устройства управления процессора по входу 10 поступает на вход блока 1 управления. Блок 1 вырабатывает сигнал установки в триггера 53. Затем анализируется триггер 48. Есблок 1 по ли он установлен в выходу 12 посылает в процессор сигнал для приостановки выполнения команды. Когда приостановка выполнения команда произошла, устройство управления процессора сообщает об этом блоку 1. После этого значение адреса, по которому производится обращение к памяти, из адресного регистра процессора подается на первый вход АЛУ. На второй вход АЛУ подаются значения адреса А и А,, соответствующие данному типу событий, и сравниваются со значением адреса А. Если адрес памяти попадает в заданный интервал адресов А, А,,в регистре регистрации масок событий производится установка в триггера 46, а в блоке 2 запоминается по фиксированному адресу код, соответствующий данному типу событий. Если триггер 48 маски в состоянии О, либо адрес памяти не попадает в интервал адресов A,A,j, триггер 46 не устанавливается и код в блоке 2 не запоминается. Причем, если триггер 48 маски находится в состоянии О, блок 1 не вырабатывает сигнал в устройство управления процессора на приостановку выполнения команды. В обоих случаях (зарегистрировано событие или нет) после анализа адреса памяти блок 1 по выходу 12 посылает в процессор сигнал на продолжение выполнения команды. Триггер 53 в узле 7 сбрасывается в О,

.В одной команде может производиться изменение содержимого нескольких ячеек оперативной памяти. Каждый раз адреса этих ячеек анализируются, если задан режим регистрации этого события. Но это происходит до тех пор, пока адрес одной из ячеек не попадет в изданный интервал. В результате устанавливается в i триггер 46, а прерывания выполнения команды для анализа последующих адресов ячеек памяти не производятся. При обращении к регистрам общего назначения или с плавающей точкой с целью изменения их содержимого .сигнал обращения от процессора через вход 10 поступает на вход блока If который вырабатывает сигнал установки в триггера 54 или 55 в зависимости от типа сигнала обращения Затем блок 1 анализирует триггер 51 или 52 маски в зависимости от того какой триггер (54 или 55) установлен . Если соответствующий триггер маск-и установлен в блок 1 посылает по выходу 12 сигнал в процессор на приостановку выполнения команды. После того, как приостановка произошла, о чем процессор сообщает блоку 1 сигналом по входу 10, адрес выполняемой команды из блока 2 через буферный регистр 5 и коммутатор 4 по выходу 11 подается на первый вход АЛУ процессора. На второй вход АЛУ подаются поочередно адреса А и А., соответствующие анализируемому типу событий, и сравниваются с адресом текущей команды. Если адрес команды находится в интервале адресов А.| ,, блок 1 посылает в процессор сигналы, по которым процессор подает номер регистра, к которому произошло обращение на первый вход АЛУ. в буферном регистре 5 находится слово местной памяти вида

оставшееся после сравнения адресов. Это слово подается на вход коммутатора 4, и с его выхода по выходу 11 номер регистра R, заносится на второй вход АЛУ. По сигналам от блока 1 устройство процессор задает в АЛУ операцию вычитания значения Щ на втором входе из значения R на первом входе и сообщает результат вычитания блоку 1. Если результат неотрицателен, т.е. R7/R , на второй вход АЛУ подается значение R и задается операция вычитания значения R на первом входе из значения R на втором входе. Если результат этого вычитания также, нертрицателен, т.е. ,., блок 1 посылает сигнал:установки в триггера 46, а в блоке 2 по фиксированному адресу запоминается код, соответствующий данному типу событий.

Если соответствующий триггер маслибо текуки не установлен в

щая команда не находится в заданной области памяти, либо номер регистра не попадает в интервал R,, RJ,триггер 46 не устанавливается и код прерывания не формируется. Кроме того, если при анализе оказывается, что триггер маски в состоянии О, блок 1 не вырабатывает сигнал в процессор на приостановку выполнения програмoмы.

В обоих случаях (зарегистрировано событие или нет) блок 1 посылает по выходу 12 сигнал в процессор для продолжения выполнения команды и

15 сбрасывает в О триггер 54 или 55. В одной команде может происходить изменение содержимого нескольких регистров. Номера этих регистров анализируются цо тех пор, пока

0 номер одного из них не попадает в . интервал R , Щ . В результате установлен в триггер 46, и последующие приостановки выполнения команды для анализа номера регистра не производятся.

5

В случае успешного выполнения команды перехода сигнал об этом, вырабатываемый в процессоре, подается в блок 1 по входу 10. Блок 1 устанавливает в Ч триггер 56. После

0 окончания выполнения команды бло

Iанализирует триггер. 49. Если он установлен в , адрес команды перехода из блока 2 через буферный регистр 5 и коммутатор 4 по выходу

5

IIподается на первый вход АЛУ процессора. На второй вход АЛУ поочередно подаются адреса А., и А,, соответствующие данному типу событий, и сравниваются с адресом команды. Если

0 команда перехода находится в заданной области оперативной памяти, т.е. ее адрес попадает в интервал А 2.J и триггер 56 установлен в , устанавливается в триггер 46, и в блоке 2 по фиксированному адресу

5 запоминается соответствующий данному событию код. В противном случае триггер 46 не устанавливается и код в местной памяти не запоминается.

Изобретение позв.оляет ЭВМ самой

0 регистрировать непредусмотренное изменение памяти и программно-доступ- . ных регистров. Причем отлаживаемая программа может выполняться совместно с другими программами, если ЭВМ

5 работает в многопрограммном 1 ежиме. По сравнению с прототипом время на отладку сокращается в 1,5-2 раза.

Экономический :ффект составляет 40000 руб в год.

0

Формула изобретения .

Устройство для отладки программ, содержащее блок управления, блок

65

местной памяти, регистр команд, коммутатор и буферный регистр, причем первый, второй и третий выходы коммутатора соединены соответственно с первым входом буферного регистра, первым выходом устройства и первым входом регистра команд, первый и второй выходы которого -соединены соответственно с первым входом коммутатора и первым входом блока местной памяти, первый, второй, третий ,четвертый и пятый выходы блока управления соединены соответственно с вторым входом буферного регистра,вторым выходом устройства, вторым входом коммутатора, вторым входом регистра команд, вторым входом блока местной памяти, выход которого соединен с третьим входом буферного регистра, первый и второй выходы буферного регистра соединены соответственно с третьим входом коммутатора и третьим входом блока местной памяти, первый и второй входы устройства соединены соответственно с четвертым входом коммутатора и первым входом блока управления, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения возможности фиксации событий, связанных с изменением содержания регистров группы ячеек памяти, в него введены дешифратор, узел регистрации и блок стековой памяти, причем третий выход регистра команд соединен с входом дешифратора, выход которого соединен с вторым входом блока управления, шестой и седьмой вь1ходы блока управления соединены соответственно с первым входом блока стековой памяти и входом узла регистрации, выход которого соединен с третьим входом блока управления, выход блока стековой памяти соединен с четвертым входом буферно го регистра, третий выход которого соединен с вторым входом блока стековой памяти.

2. Устройство по П.1, о т л и ч а ю щ е ее я тем, что блок управления содержит формирователь адреса микрокоманд, регистр адреса микрокоманд, блок памяти мик эокоманд, регистр микрокоманд и дешифратор, причем выход формирователя адреса .микрокоманд соединен с входом регистра микрокоманд, выход которого соединен с входом блока памяти микрокоманд, выход блока памяти микрокоманд соединен с входом регистра микрокоманд, первый и второй выходы которого соединены соответственно с первым входом формирователя адреса микрокоманд, и первым входом дешифратора, первый выход дешифратора соединен с вторым входом.формирователя адреса команд, остальные выходы дешифратора образуют группу выходов блока первый, второй и третий входы блока сЪединены соответственно с третьим, четвертым и пятым входами формирователя адреса микрокоманд, второй и третий входы блока соединены с вторы и третьим входом дешифратора.

Источники информации, принятые во внимание при экспертизе

1. Патент США 3673573, кл. 340-172.5, 1972.

2..Авторское свидетельство СССР № 598077, кл. G Об F 9/20, 1978.

3.Авторское свидетельство СССР № 277410, кл. G Об F 9/00, 1970.

4.Катцан. Вычислительные машины системы 370, М. , Мир., 1974 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Процессор | 1976 |

|

SU670935A1 |

| Устройство для коррекции микрокоманд | 1984 |

|

SU1164709A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

..jn

Т

9 11

10

-I

Процессор звм

.J Фиг..1

и

28

У.

37

3S

29

30

зг

J

JiZ

V. J5

Фиг. 3

3

4-/,/,

Фиг.

92

61

60

53

. ИЛИ

fi -.65

Авторы

Даты

1981-07-23—Публикация

1979-11-13—Подача