1

Изобретение относится к импульсной технике, в частности к устройствам, в которых нмпульсы выдаются в момейт времени, соот-, ветствующий определенной части амплитуды переднего фронта входного импульса.

Известны формирователи импульсов, в которых реализован метод формирования импульса в момент времени, соответствующий определенной части амплитуды переднего фронта входного импульса, содержащиеэлемент НЕ,- делитель напряжения, алемеит задержки, сумматор, днскримннатор нуля, . выходной формирователь, дискриминатор нижнего уровня 1.

Наиболее близким по технической сущности к изобретению является формирователь нмпульсов, содержащий элемент НЕ,, делитель напряжения, элемент задержки, сумматор, запоминающий блок, дискриминатор нуля, выходной ормирователь, дискриминатор нижнего уровня 21.

Так как дискриминатор иижиего уровня имеет Постоянную длительность выходного импульса, частота входных импульсов-не должна превыщать заданную величину, в противиом случае происходит наложение амплитуд входных импульсов в запоминающем блоке, что приводит к изменению момента времени формирования выходного им:пу. и делает невозможным применение известного формирователя для случайных потоков входных сигналов и ограничивает его быстродействие.

Цель изобретения - расширение функциональных возможностей и повышение быстродействия формирователя импульсов. Поставленная цель достигается тем, что в формирователь импульсов, содержащий элемент НЕ, вход которого соединен со входом делателя напряжения, а выход через элемеит задержки подключеи к первому входу сумматора, второй вход которого через запоминающий блок соединен с выходом делителя напряжения, причем выход сумма.г тора подключен к первому входу дискриминатора, выход которого соединен со входом выходного формирователя, введеиы два компа.ратора иижиего уровня, два триггера и элемент линейного пропускания, причем вход первого компаратора соединен с выходом

20 элемента задержки и первым входом сумматора, а выход его подключен ко входу сброса первого триггера, вход второго йомпаратора соединен с выходом элемента лииейного

пропускания и со входом делителя напряжения, а его выход подключен к установочным входам первого и второго триггеров, причем выход первого триггера соединен со вторыми входами запоминающего блока и дискриминатора, вход сброса подключен к выходу выходного формирователя, а выход второго триггера подключен ко входу управления элемента линейного пропускания.

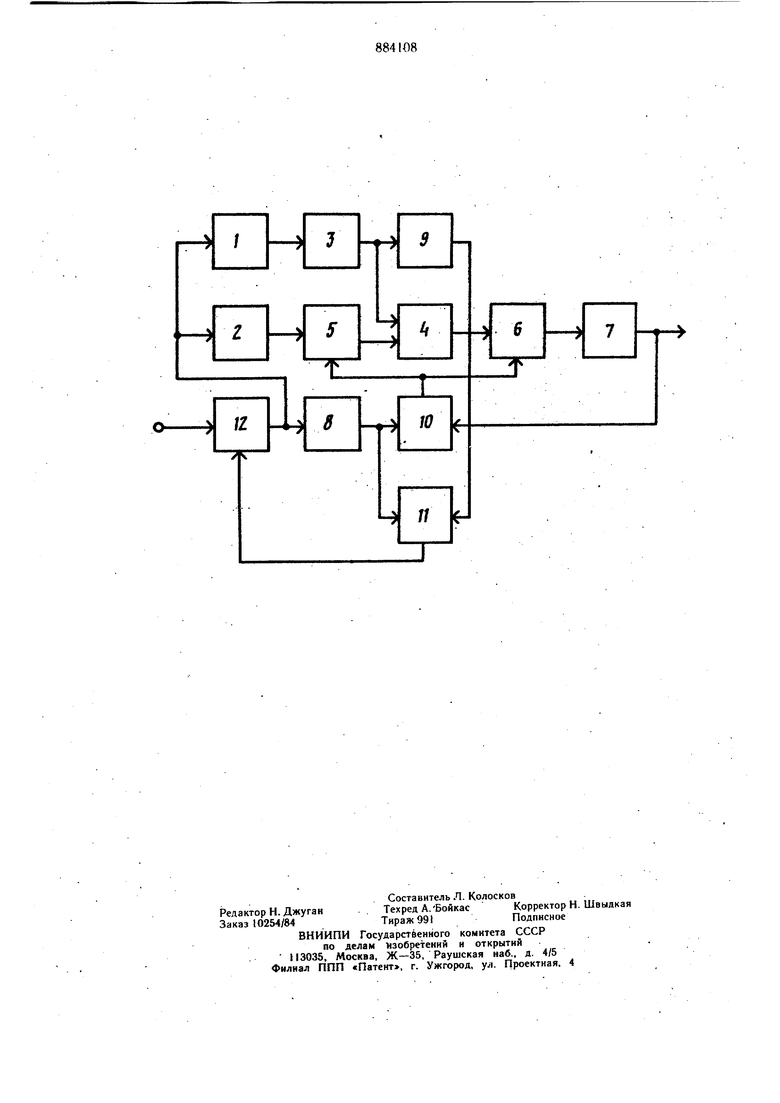

На чертеже представлена структурная электрическая схема формирователя импульсов.

Формирователь импульсов содержит элемент НЕ 1, делитель 2 напряжения, элемент 3 задержки, сумматор 4, запоминающий блок 5, дискриминатор 6 нуля, выходной формирователь 7, компараторы 8 и 9 нижнего уровня, триггеры 10 и 11, элемент 12 линейного пропускания.

До поступления сигналов на формирователь импульсов, запоминающий блок 5 и дискриминатор 6 блокированы триггером 10. Входной импульс через otKpbiTbm элемент 12 линей;)ого пропускания поступает на входы элемента НЕ 1, делителя 2 напряжения и компаратора 8 нижнего уровня. Компаратор 8 нижнего уровня, имея высокую чувствительность, срабатывает, причем длительность импульса на выходе компаратора равна длительности входного импульса и устанавливает в единичное состояние по началу импульса триггер 10, который снимает блокировку с запоминающего, блока 5 и дискриминатора 6. По спаду выходного импульса компаратора 8 устанавливается в единичное состояние триггер П, который закрывает элемент 12 линейноЧ.ГО пропускания, запрещая прохождение через него последующих входных импульсов. Выходной сигнал элемента НЕ 1, задержанный элементом 3 задержки, запускает компаратор 9 нижнего уровня, который работает аналогично компаратору 8, и одновременно поступает на первый вход сумматора 4, на второй вход которого подается сигнал с запоминающего блока 5. Полученный на выходе сумматора 4 биполярный сигнал поступает на дискриминатор 6, который в момент пересечения биполярным сигналом нуля вырабатывает импульс, . окончательно формируемый выходным формирователем 7, выходной импульс которого устанавливает в исходное состояние триггер 10. Триггер 11 приводится в исходное состояние по спаду выходного импульса компаратора 9.

Формула изобретения

Формирователь импульсов, содержащий элемент НЕ, вход которого соединен со входом делителя напряжения, а выход через элемент задержки подключен к первому входу сумматора, второй вход которого через

запоминающий блок соединен с выходом делителя напряжения, причем выход сумматора подключен к первому входу дискриминатора, выход которого соединен со входом выходного формирователя, отличающийся тем, что, с целью расщирения функциональных возможностей и повышения быстродействия, в него введены два компаратора нижнего уровня, два триггера и элемент линейного пропускания, причем вход первого компаратора соединен с выходом элемента задержки и первым входом сумматора, а выход его подключен ко входу сброса первого триггера, вход второго компаратора соединен с выходом элемента линейного Пропускания и со входом делителя напряжения, а его выход подключен к установочным входам первого и второго триггеров, причем выход первого триггера соединен со вторыми входами запоминающего блока и дискриминатора, вход сброса подключен к выходу выходного формирователя, а выход второго триггера подключен ко входу

управления элемента линейного пропускания.

Источники информации, принятые во внимание при экспертизе

1.Формирователь импульсов. Дубна, принт. ОНЯН 13-3700, 1968. с. 225.

2.Авторское свидетельство № 597082, кл. Н 03 К 5/153, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1986 |

|

SU1370753A1 |

| Способ формирования периодических двуполярных колебаний с заданным фазовым сдвигом и устройство для его реализации | 2016 |

|

RU2625047C1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПЛОТНОСТИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ СЛУЧАЙНОГО ПРОЦЕССА | 2000 |

|

RU2174706C1 |

| Устройство для снятия диаграммы направленности антенны | 1984 |

|

SU1334097A1 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| Устройство для измерения восприимчивости и частотной избирательности каналов радиоприемника к побочным составляющим несущей частоты | 1982 |

|

SU1104431A1 |

| СТАБИЛИЗИРОВАННЫЙ ЭЛЕКТРОПРИВОД | 2016 |

|

RU2621288C1 |

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1780033A1 |

| Устройство для формирования последовательности импульсов | 1983 |

|

SU1157676A1 |

Авторы

Даты

1981-11-23—Публикация

1980-02-13—Подача