20

25

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении командно- программных систем управления. ,

Цель изобретения - повышение достоверности работы устройства.

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема одного из блоков памяти, на фиг.З - функциональная схема пер- оого блока контроля , на фигЛ - функциональная схема второго блока контроля, на фиг.5 - функциональная схема кодирующего блокаJ на фиг.6 - схе- J5 ijia соединения коммутационного узла. Устройство для дешифрации команд Ьодержит первый блок 1 контроля, ходной регистр 2, первый 3 и второй

дешифраторы, первую группу 5 элементов И, группу 6 элементов ИЛИ, блоки 7 и 8 памяти, вторую 9 и тре- Гью 10 группы элементов И, второй 0лок 11 контроля, регистр 12 адреса, лок 12 сравнения, третий дешифратор }Ц, триггер 15, выход 16 контроля риема информации устройства, кодирующий блок 17 и выход 18 программных команд устройства.

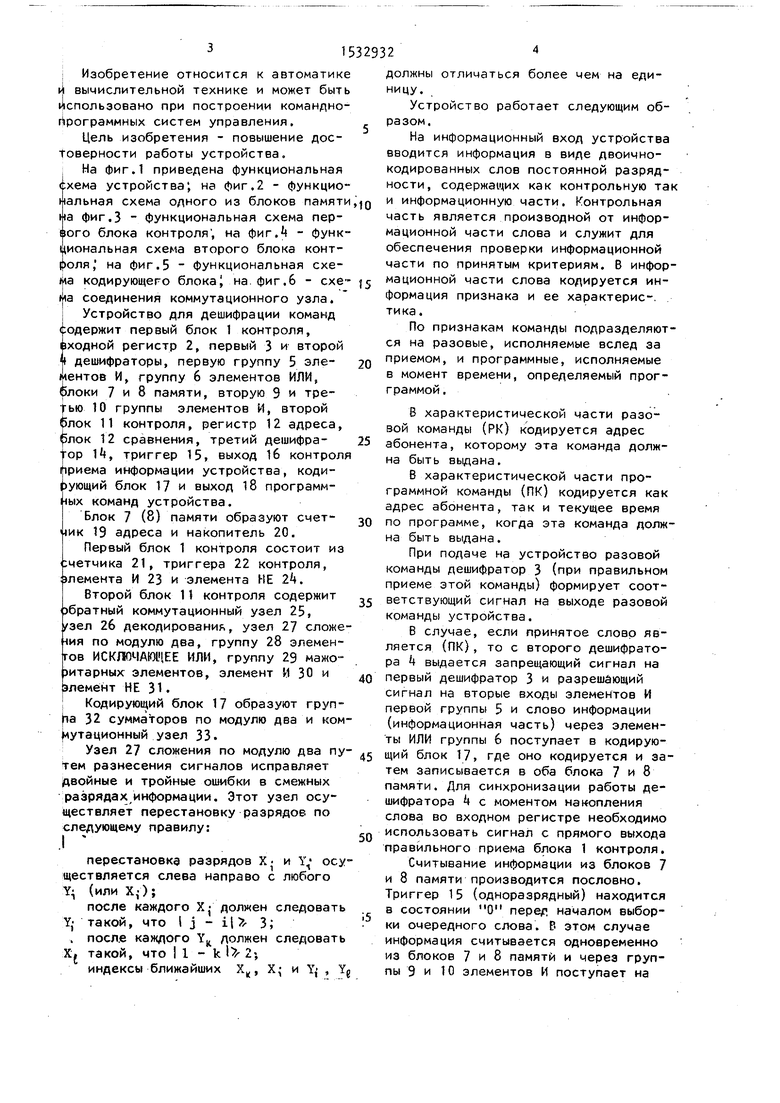

Блок 7 (8) памяти образуют счетчик 19 адреса и накопитель 20.

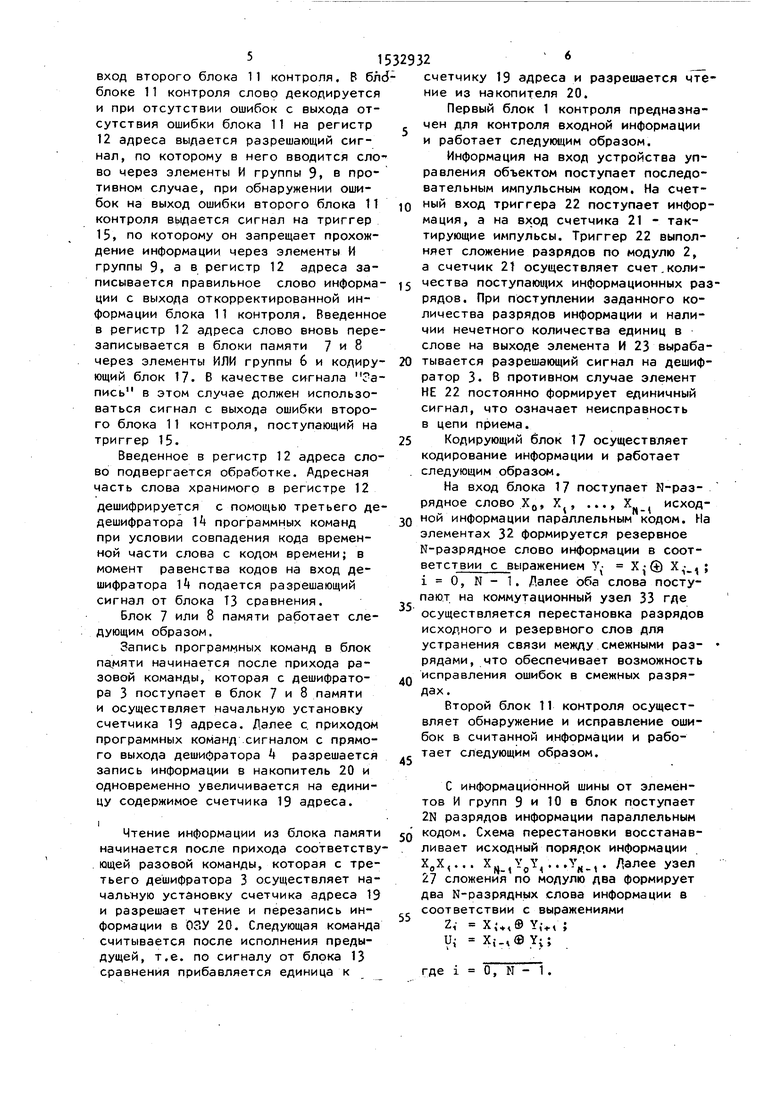

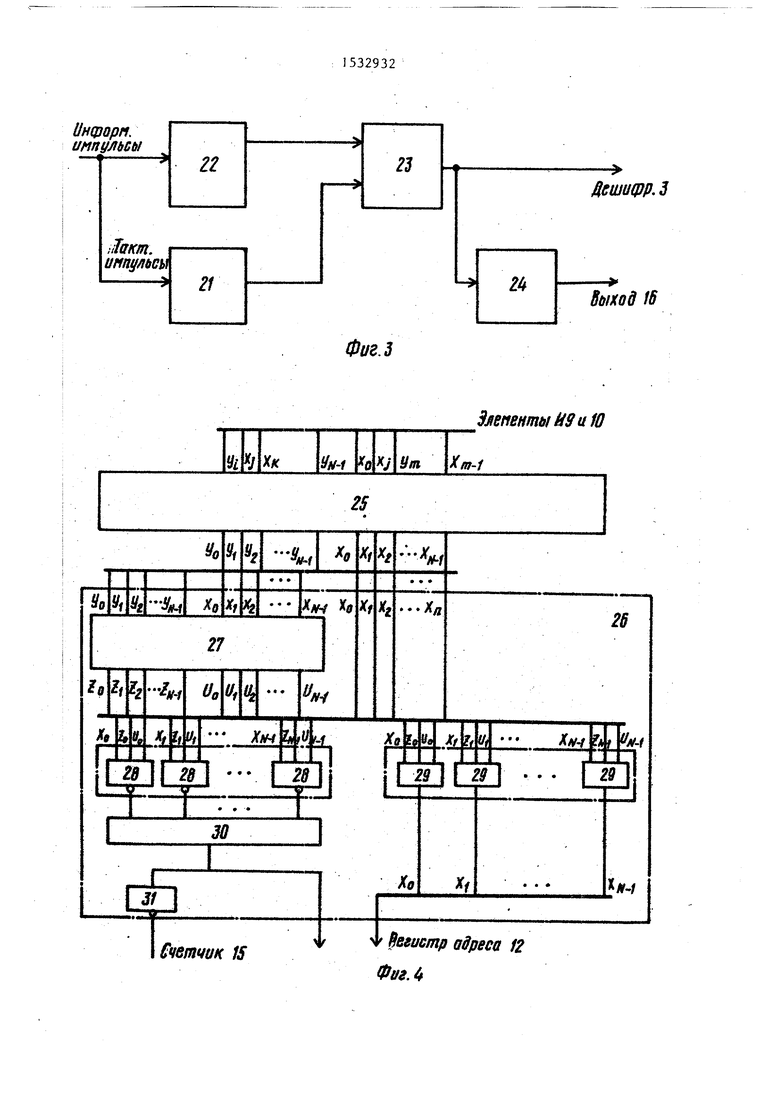

Первый блок 1 контроля состоит из счетчика 21, триггера 22 контроля, элемента И 23 и элемента НЕ 2k.

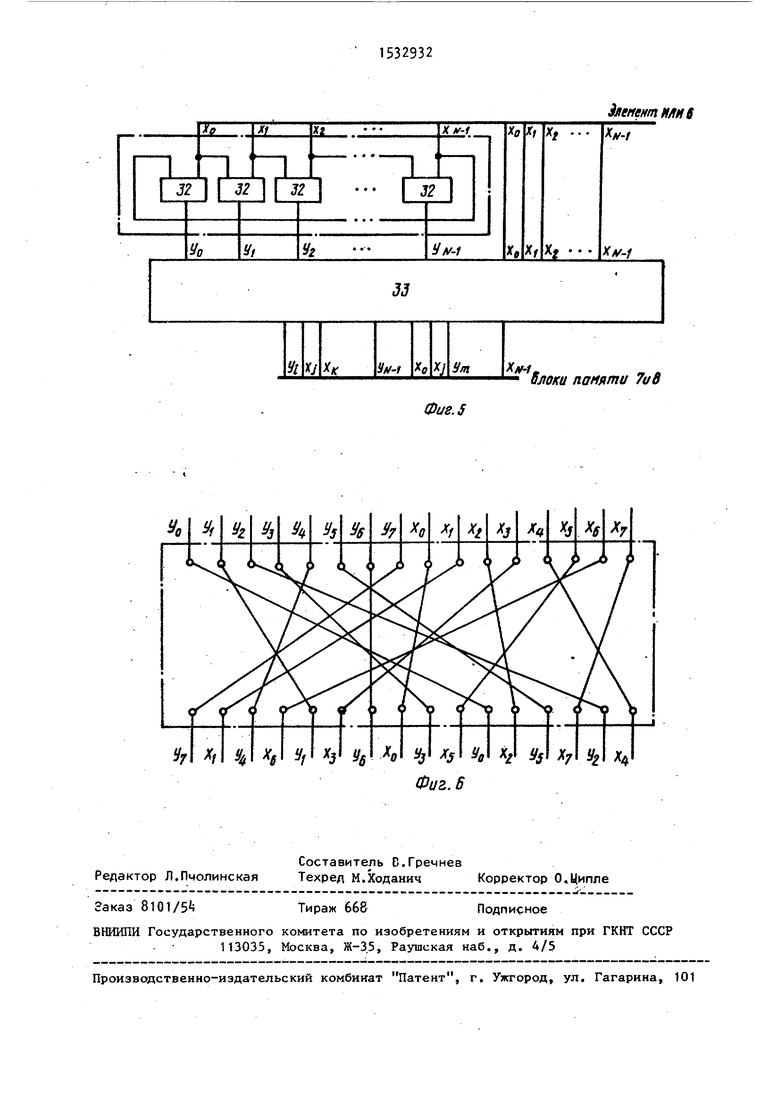

Второй блок 11 контроля содержит обратный коммутационный узел 25, зел 26 декодирования,, узел 27 сложе- я по модулю два, группу 28 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу 29 мажо- эитарных элементов, элемент И 30 и элемент НЕ 31.

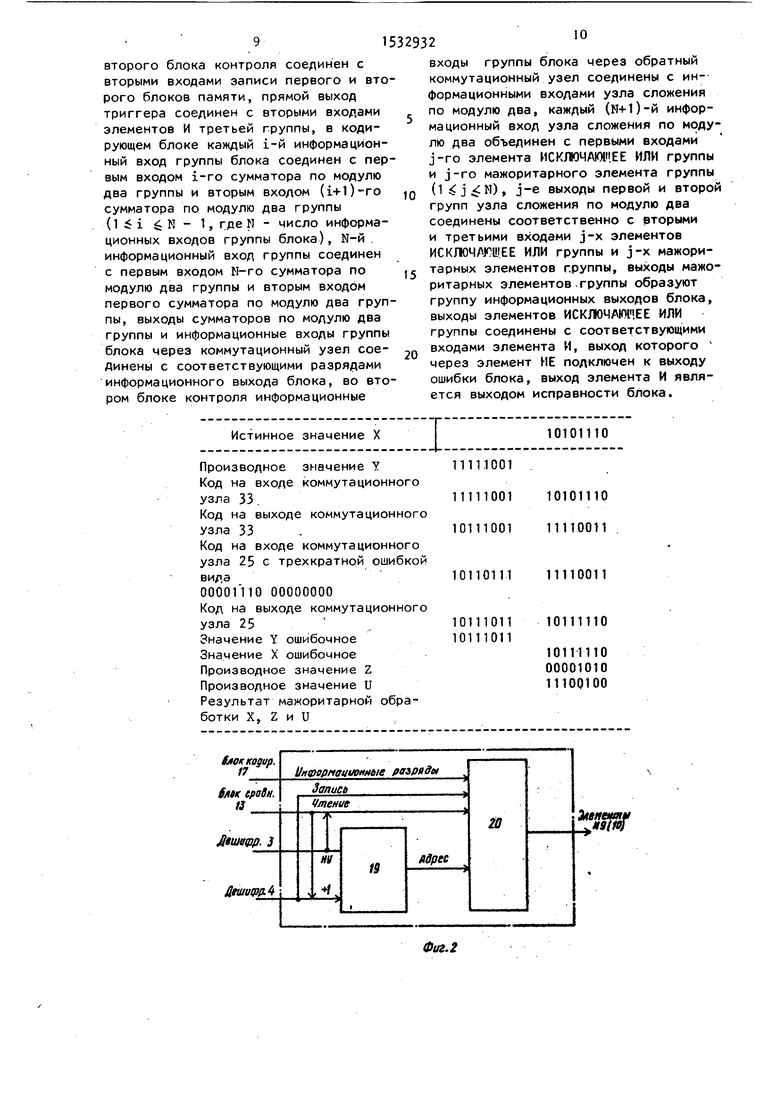

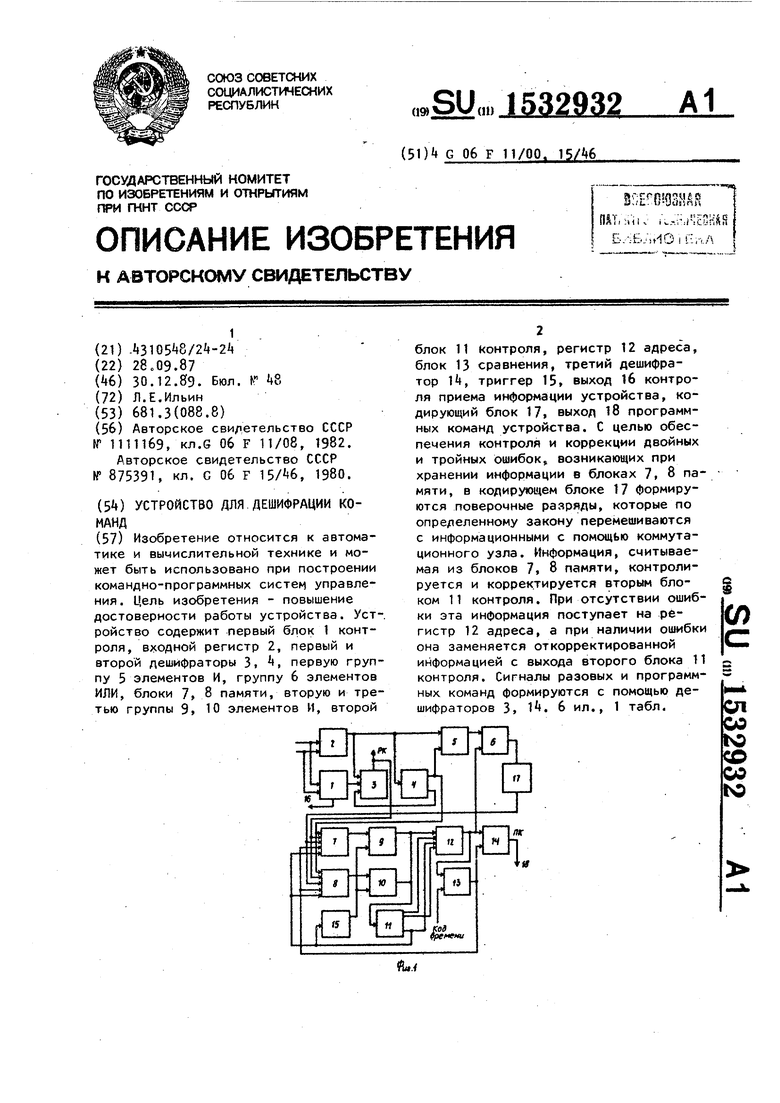

Кодирующий блок 17 образуют груп- Иа 32 сумматоров по модулю два и ком- Мутационный узел 33.

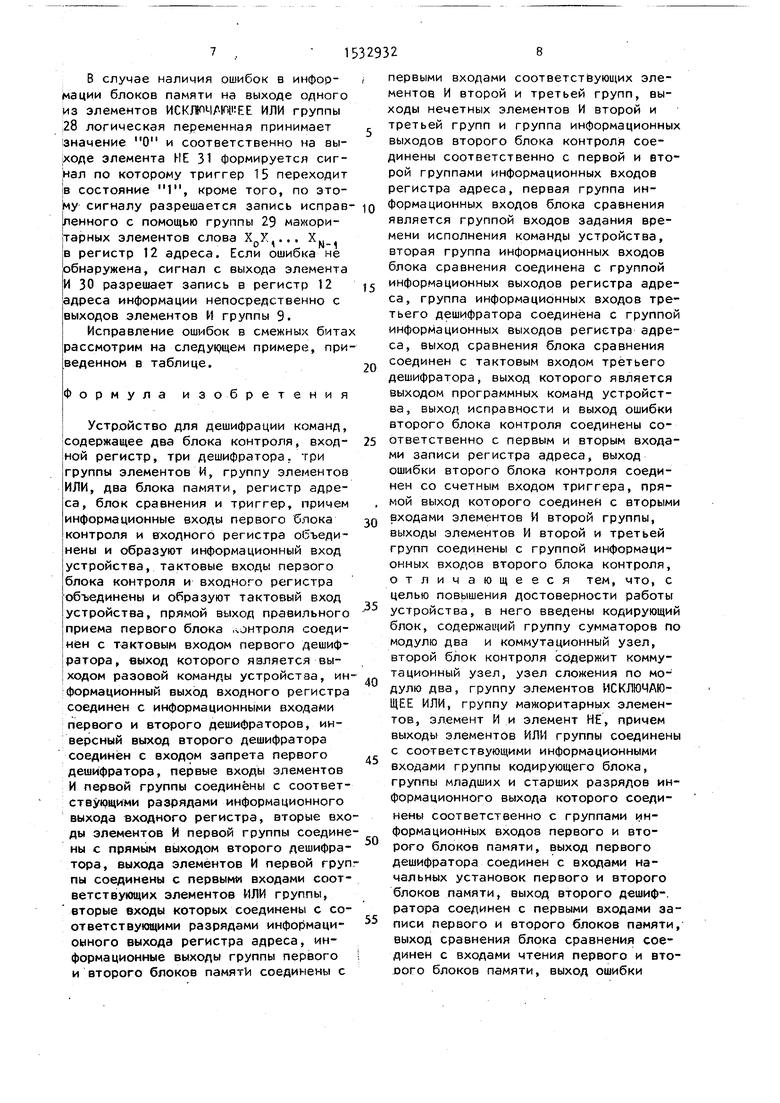

Узел 27 сложения по модулю два пу- тем разнесения сигналов исправляет двойные и тройные ошибки в смежных разрядах информации. Этот узел осуществляет перестановку разрядов по следующему правилу: .I

перестановка разрядов Х- и Y,1 осуществляется слева направо с любого Y (или Х-);

после каждого Х- должен следовать Y,- такой, что I j -Ј(/ 3; . после каждого YK должен следовать X. такой, что I 1 - k l

15329324

должны отличаться более чем на единицу.

Устройство работает следующим образом.

На информационный вход устройства вводится информация в виде двоично- кодированных слов постоянной разрядности, содержащих как контрольную так и информационную части. Контрольная часть является производной от информационной части слова и служит для обеспечения проверки информационной части по принятым критериям. В информационной части слова кодируется информация признака и ее характеристика.

По признакам команды подразделяются на разовые, исполняемые вслед за приемом, и программные, исполняемые в момент времени, определяемый прог- граммой.

30

35

40

50

индексы ближайших Хк, Х- и Y,Ч

В характеристической части разовой команды (РК) кодируется адрес абонента, которому эта команда должна быть выдана.

В характеристической части программной команды (ПК) кодируется как адрес абонента, так и текущее время по программе, когда эта команда должна быть выдана.

При подаче на устройство разовой команды дешифратор 3 (при правильном приеме этой команды) формирует соответствующий сигнал на выходе разовой команды устройства.

В случае, если принятое слово является (ПК), то с второго дешифратора k выдается запрещающий сигнал на первый дешифратор 3 и разрешающий сигнал на вторые входы элементов И первой группы 5 и слово информации (информационная часть) через элементы ИЛИ группы 6 поступает в кодирующий блок 17, где оно кодируется и затем записывается в оба блока 7 и 8 памяти. Для синхронизации работы дешифратора k с моментом накопления слова во входном регистре необходимо использовать сигнал с прямого выхода правильного приема блока 1 контроля.

Считывание информации из блоков 7 и 8 памяти производится пословно. Триггер 15 (одноразрядный) находится в состоянии О перед началом выборки очередного слова. В этом случае информация считывается одновременно из блоков 7 и 8 памяти и через группы 9 и 10 элементов И поступает на

25

30

35

40

50

В характеристической части разовой команды (РК) кодируется адрес абонента, которому эта команда должна быть выдана.

В характеристической части программной команды (ПК) кодируется как адрес абонента, так и текущее время по программе, когда эта команда должна быть выдана.

При подаче на устройство разовой команды дешифратор 3 (при правильном приеме этой команды) формирует соответствующий сигнал на выходе разовой команды устройства.

В случае, если принятое слово является (ПК), то с второго дешифратора k выдается запрещающий сигнал на первый дешифратор 3 и разрешающий сигнал на вторые входы элементов И первой группы 5 и слово информации (информационная часть) через элементы ИЛИ группы 6 поступает в кодирующий блок 17, где оно кодируется и затем записывается в оба блока 7 и 8 памяти. Для синхронизации работы дешифратора k с моментом накопления слова во входном регистре необходимо использовать сигнал с прямого выхода правильного приема блока 1 контроля.

Считывание информации из блоков 7 и 8 памяти производится пословно. Триггер 15 (одноразрядный) находится в состоянии О перед началом выборки очередного слова. В этом случае информация считывается одновременно из блоков 7 и 8 памяти и через группы 9 и 10 элементов И поступает на

вход второго блока 11 контроля. В блоке 11 контроля слово декодируется и при отсутствии ошибок с выхода отсутствия ошибки блока 11 на регистр 12 адреса выдается разрешающий CMI- нал, по которому в него вводится слово через элементы И группы 9 в противном случае, при обнаружении ошибок на выход ошибки второго блока 11 контроля выдается сигнал на триггер 15, по которому он запрещает прохождение информации через элементы И группы 9, а в регистр 12 адреса за

счетчику 19 адреса и разрешается чтение из накопителя 20.

Первый блок 1 контроля предназначен для контроля входной информации и работает следующим образом.

Информация на вход устройства управления объектом поступает последовательным импульсным кодом. На счетный вход триггера 22 поступает информация, а на вход счетчика 21 - тактирующие импульсы. Триггер 22 выполняет сложение разрядов по модулю 2, а счетчик 21 осуществляет счет.коли

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления объектом | 1984 |

|

SU1234850A2 |

| Устройство для управления объектом | 1980 |

|

SU875391A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для контроля цифровых печатных узлов | 1983 |

|

SU1179233A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении командно-программных систем управления. Цель изобретения - повышение достоверности работы устройства. Устройство содержит первый блок 1 контроля, входной регистр 2, первый и второй дешифраторы 3,4, первую группу 5 элементов И, группу 6 элементов ИЛИ, блоки 7,8 памяти, вторую и третью группы 9,10 элементов И, второй блок 11 контроля, регистр 12 адреса, блок 13 сравнения, третий дешифратор 14, триггер 15, выход 16 контроля приема информации устройства, кодирующий блок 17, выход 18 программных команд устройства. С целью обеспечения контроля и коррекции двойных и тройных ошибок, возникающих при хранении информации в блоках 7,8 памяти, в кодирующем блоке 17 формируются поверочные разряды, которые по определенному закону перемешиваются с информационными с помощью коммутационного узла. Информация, считываемая из блоков 7,8 памяти, контролируется и корректируется вторым блоком 11 контроля. При отсутствии ошибки эта информация поступает на регистр 12 адреса, а при наличии ошибки она заменяется откорректированной информацией с выхода второго блока 11 контроля. Сигналы разовых и программных команд формируются с помощью дешифраторов 3,14. 6 ил.

писывается правильное слово информа- $ чества поступающих информационных раз- ции с выхода откорректированной ин- рядов. При поступлении заданного ко- формации блока 11 контроля. Введенное личества разрядов информации и нали- в регистр 12 адреса слово вновь пере- чип нечетного количества единиц в записывается в блоки памяти 7 и 8 слове на выходе элемента И 23 выраба- через элементы ИЛИ группы 6 и кодиру- 20 тывается разрешающий сигнал на дешифратор 3. В противном случае элемент НЕ 22 постоянно формирует единичный сигнал, что означает неисправность в цепи приема.

25 Кодирующий блок 17 осуществляет кодирование информации и работает следующим образом.

На вход блока 17 поступает N-раз- рядное слово Х0, X , ..., Хм, исходющий блок 17. В качестве сигнала Запись в этом случае должен использоваться сигнал с выхода ошибки второго блока 11 контроля, поступающий на триггер 15.

Введенное в регистр 12 адреса слово подвергается обработке. Адресная часть слова хранимого в регистре 12

дешифрируется с помощью третьего де- дешифратора 14 программных команд при условии совпадения кода временной части слова с кодом времени; в момент равенства кодов на вход дешифратора 1 подается разрешающий сигнал от блока ТЗ сравнения.

Блок 7 или 8 памяти работает следующим образом.

Запись программных команд в блок памяти начинается после прихода разовой команды, которая с дешифратора 3 поступает в блок 7 и 8 памяти и осуществляет начальную установку счетчика 19 адреса. Далее с приходом программных команд сигналом с прямого выхода дешифратора k разрешается запись информации в накопитель 20 и одновременно увеличивается на единицу содержимое счетчика 19 адреса.

i

Чтение информации из блока памяти

начинается после прихода соответствующей разовой команды, которая с третьего дешифратора 3 осуществляет начальную установку счетчика адреса 19 и разрешает чтение и перезапись информации в ОЗУ 20. Следующая команда считывается после исполнения предыдущей, т.е. по сигналу от блока 13 сравнения прибавляется единица к

35

3Q ной информации параллельным кодом. На элементах 32 формируется резервное N-разрядное слово информации в соот- ветствии с выражением Ух- Х-© X.,-,, ; , N - 1. Далее оба слова поступают на коммутационный узел 33 где осуществляется перестановка разрядов исходного и резервного слов для устранения связи между смежными разрядами, что обеспечивает возможность

.- исправления ошибок в смежных разря- 4U

дах.

Второй блок 11 контроля осуществляет обнаружение и исправление ошибок в считанной информации и работает следующим образом. 45

С информационной шины от элементов И групп 9 и 10 в блок поступает 2N разрядов информации параллельным JQ кодом. Схема перестановки восстанавливает исходный порядок информации XeX,... ..., . Далее узел 27 сложения по модулю два формирует два N-разрядных слова информации в соответствии с выражениями

2,- Х + © y,v ;

Ш Y;;

55

где i 0, N - 1.

ной информации параллельным кодом. На элементах 32 формируется резервное N-разрядное слово информации в соот- ветствии с выражением Ух- Х-© X.,-,, ; , N - 1. Далее оба слова поступают на коммутационный узел 33 где осуществляется перестановка разрядов исходного и резервного слов для устранения связи между смежными разрядами, что обеспечивает возможность

исправления ошибок в смежных разря-

дах.

Второй блок 11 контроля осуществляет обнаружение и исправление ошибок в считанной информации и работает следующим образом.

С информационной шины от элементов И групп 9 и 10 в блок поступает 2N разрядов информации параллельным кодом. Схема перестановки восстанавливает исходный порядок информации XeX,... ..., . Далее узел 27 сложения по модулю два формирует два N-разрядных слова информации в соответствии с выражениями

2,- Х + © y,v ;

Ш Y;;

где i 0, N - 1.

В случае наличия ошибок в информации блоков памяти на выходе одного из элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы 28 логическая переменная принимает значение О и соответственно на выходе элемента НЕ 31 формируется сигнал по которому триггер 15 переходит в состояние 1, кроме того, по это- toy сигналу разрешается запись исправ Ценного с помощью группы 29 махюри- 1тарных элементов слова XX.... Хы |в регистр 12 адреса. Если ошибка не обнаружена, сигнал с выхода элемента |И 30 разрешает запись в регистр 12 адреса информации непосредственно с выходов элементов И группы 9.

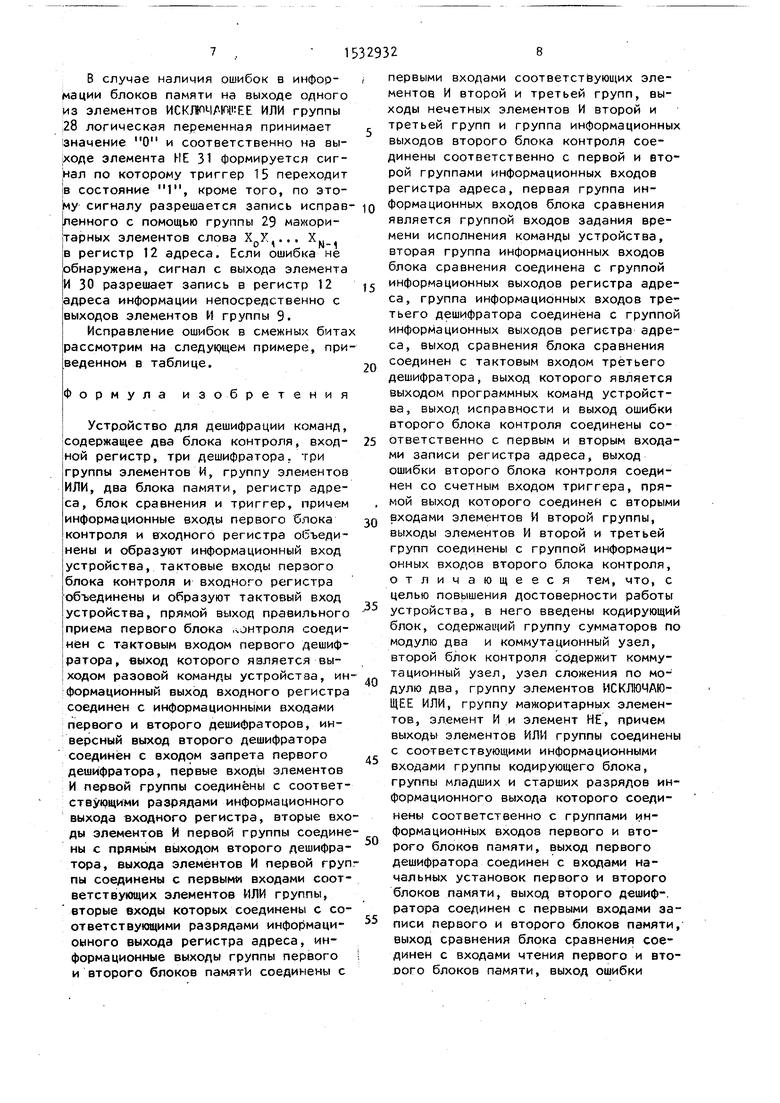

Исправление ошибок в смежных бита рассмотрим на следующем примере, приведенном в таблице.

Формула изобретения

Устройство для дешифрации команд, содержащее два блока контроля, входной регистр, три дешифратора, три группы элементов И, группу элементов ИЛИ, два блока памяти, регистр адреса, блок сравнения и триггер, причем информационные входы первого блока контроля и входного регистра объединены и образуют информационный вход устройства, тактовые входы первого блока контроля и входного регистра объединены и образуют тактовый вход устройства, прямой выход правильного приема первого блока .онтроля соединен с тактовым входом первого дешифратора, выход которого является выходом разовой команды устройстза, информационный выход входного регистра соединен с информационными входами первого и второго дешифраторов, инверсный выход второго дешифратора соединен с входом запрета первого дешифратора, первые входы элементов И первой группы соединены с соответствующими разрядами информационного выхода входного регистра, вторые входы элементов И первой группы соединены с прямым выходом второго дешифратора, выхода элементов И первой группы соединены с первыми входами соответствующих элементов ИЛИ группы, вторые входы которых соединены с соответствующими разрядами информационного выхода регистра адреса, информационные выходы группы первого и второго блоков памяти соединены с

0

5

0

5

0

5

0

5

первыми входами соответствующих элементов И второй и третьей групп, выходы нечетных элементов И второй и третьей групп и группа информационных выходов второго блока контроля соединены соответственно с первой и второй группами информационных входов регистра адреса, первая группа информационных входов блока сравнения является группой входов задания времени исполнения команды устройства, вторая группа информационных входов блока сравнения соединена с группой информационных выходов регистра адреса, группа информационных входов третьего дешифратора соединена с группой информационных выходов регистра адреса, выход сравнения блока сравнения соединен с тактовым входом третьего дешифратора, выход которого является выходом программных команд устройства, выход исправности и выход ошибки второго блока контроля соединены соответственно с первым и вторым входами записи регистра адреса, выход ошибки второго блока контроля соединен со счетным входом триггера, прямой выход которого соединен с вторыми входами элементов И второй группы, выходы элементов И второй и третьей групп соединены с группой информационных входов второго блока контроля, отличающееся тем, что, с целью повышения достоверности работы устройства, в него введены кодирующий блок, содержащий группу сумматоров по модулю два и коммутационный узел, второй блок контроля содержит коммутационный узел, узел сложения по модулю два, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу мажоритарных элементов, элемент И и элемент НЕ, причем выходы элементов ИЛИ группы соединены с соответствующими информационными входами группы кодирующего блока, группы младших и старших разрядов информационного выхода которого соединены соответственно с группами информационных входов первого и второго блоков памяти, выход первого дешифратора соединен с входами начальных установок первого и второго блоков памяти, выход второго дешиф-. ратора соединен с первыми входами записи первого и второго блоков памяти, выход сравнения блока сравнения соединен с входами чтения первого и вто- оого блоков памяти, выход ошибки

второго блока контроля соединен с вторыми входами записи первого и второго блоков памяти, прямой выход триггера соединен с вторыми входами элементов И третьей группы, в кодирующем блоке каждый i-й информационный вход группы блока соединен с первым входом i-ro сумматора по модулю два группы и вторым входом (i+l)-ro сумматора по модулю два группы О $ i N - 1, где N - число информационных входов группы блока), N-й информационный вход группы соединен с первым входом М-го сумматора по модулю два группы и вторым входом первого сумматора по модулю два группы, выходы сумматоров по модулю два группы и информационные входы группы блока через коммутационный узел соединены с соответствующими разрядами информационного выхода блока, во втором блоке контроля информационные

Истинное значение X

10

53293210

входы группы блока через обратный коммутационный узел соединены с информационными входами узла сложения по модулю два, каждый (М+1)-й информационный вход узла сложения по модулю два объединен с первыми входами j-ro элемента ИСКЛЮЧАЮ ЕЕ ИЛИ группы и j-ro мажоритарного элемента группы (1 ), j-e выходы первой и второй групп узла сложения по модулю два соединены соответственно с вторыми и третьими входами j-x элементов ИСКЛЮЧАВШЕЕ ИЛИ группы и j-x мажоритарных элементов группы, выходы мажоритарных элементов группы образуют группу информационных выходов блока, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с соответствующими входами элемента И, выход которого v через элемент НЕ подключен к выходу ошибки блока, выход элемента И является выходом исправности блока.

15

20

I

10101110

Фиг.З

Счетчик 1S

Зле пен mm Н9 и 10

ФогЛ

УГ Х1 4И W W W Уб °l $ 5 Уо V W 7 W 4

Фиг. 6

Составитель В.Гречнев Редактор Л.Пчолинская Техред М.Ходанич Корректор О.Ципле

Заказ 8101/54

Тираж 668

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-3,5, Раушская наб., д. Д/5

Фие.5

Подписное

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для управления объектом | 1980 |

|

SU875391A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-30—Публикация

1987-09-28—Подача