3

однородной врлчислнте.лыи)1 ( .rr-)v;fтуры матрицу рапмером и « m вмчис:лительных блоков 1 , группу из п блоков 2 перрключеиия каналов, группу из п блоков 3 ке1/4

1/493809

,лючсн1 и : 1мHill , уги. Л 4 формирп- пания I orTciR, г- И тны 1 учел 5, узел 6 th(7pMHpun, с-11тл1а.г1с (Л каза, элемент ИР, 7, -злрмрн - И.ЧИ 8, 1 з.л. ф-лы, 9 ял„

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок обработки матричной вычислительной системы | 1991 |

|

SU1827675A1 |

| Система для обмена информацией | 1980 |

|

SU980087A1 |

| Модуль матричного коммутатора | 1990 |

|

SU1793436A2 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

| Устройство для сопряжения | 1981 |

|

SU964622A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ ТРЕХ МАТРИЦ И ВЫЧИСЛЕНИЯ ДВУМЕРНОГО ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1993 |

|

RU2066878C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения высокопроизводительных вычислительных систем. Цель изобретения - повышение надежности вычислительных систем, построенных на базе модулей однородной вычислительной структуры. Для этого модуль однородной вычислительной структуры содержит матрицу размером NXM вычислительных блоков 1, первую группу из N блоков 2 переключения каналов, вторую группу из N блоков 3 переключения каналов, узел 4 формирования тестов, счетный узел 5, узел 6 формирования сигнала отказа, элемент НЕ 7 элемент ИЛИ 8. 1 з.п. ф-лы, 9 ил.

Изобретение относится к вычисли- тельно1т технике и может быть использовано при построении вычислительных средств на базе модулей однородной вычислительной среды, нгшример, при построении матричных и систологических процессоров,

Цель изобретения - повьииение надежности вычислительных систем, построен1 Ь Х на базе модуля однородной вычислительной структуры

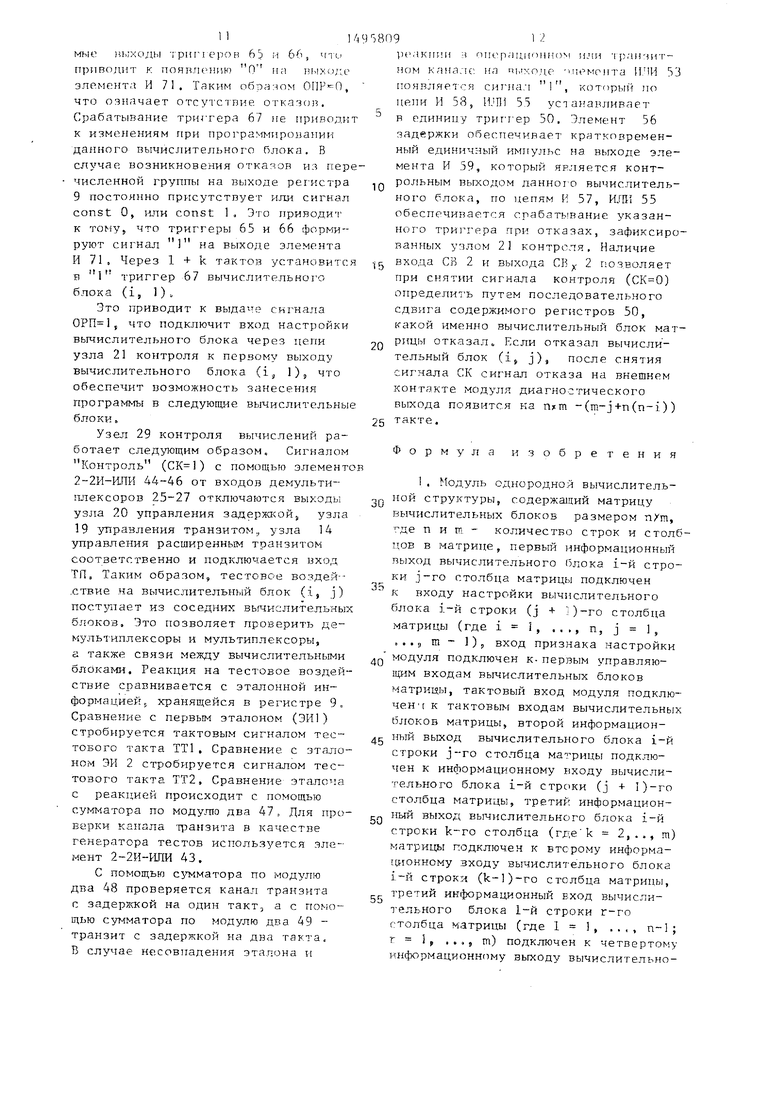

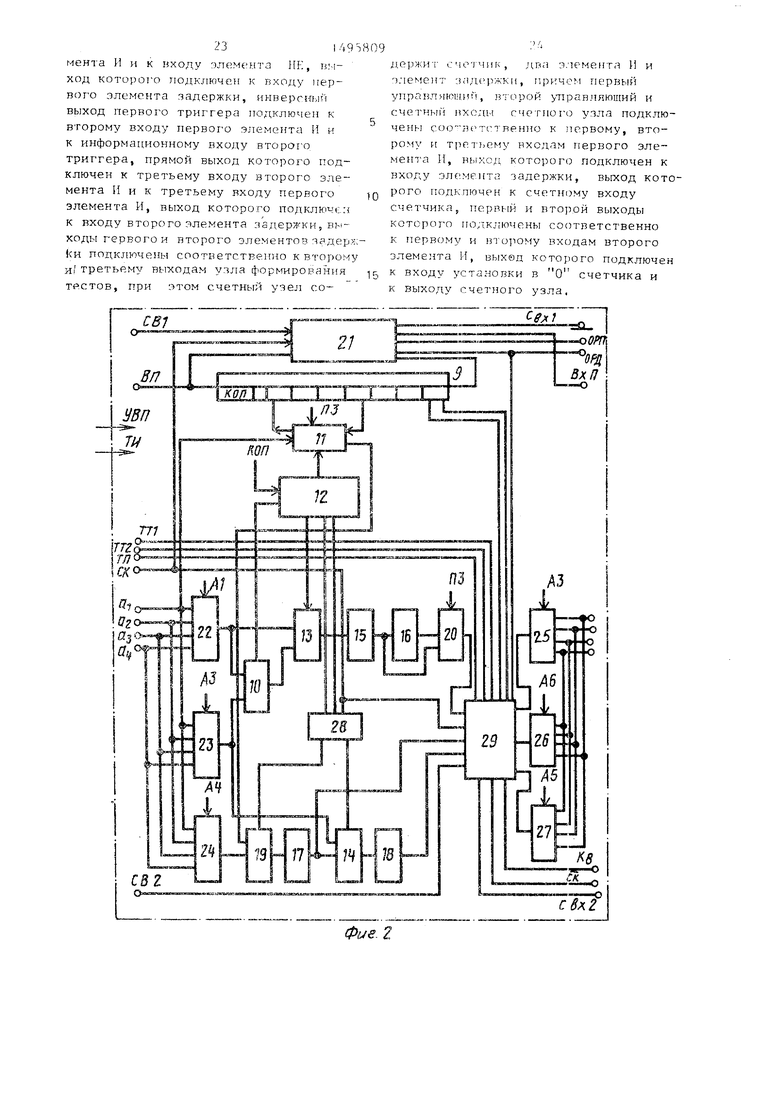

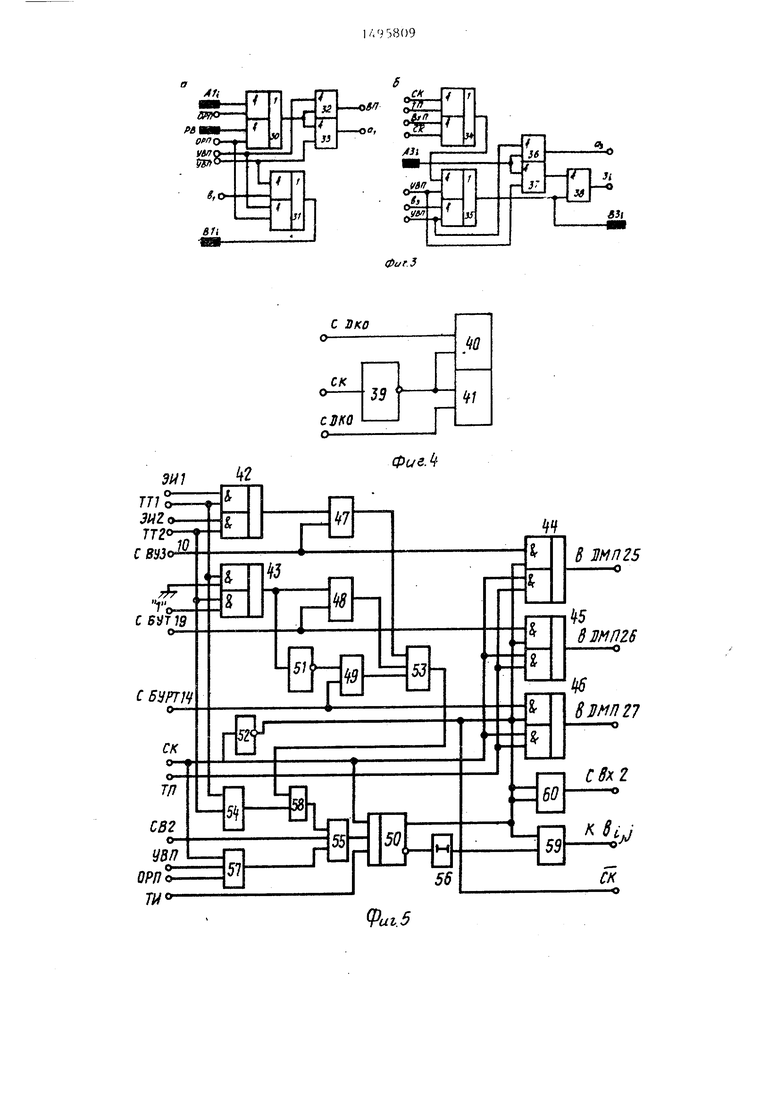

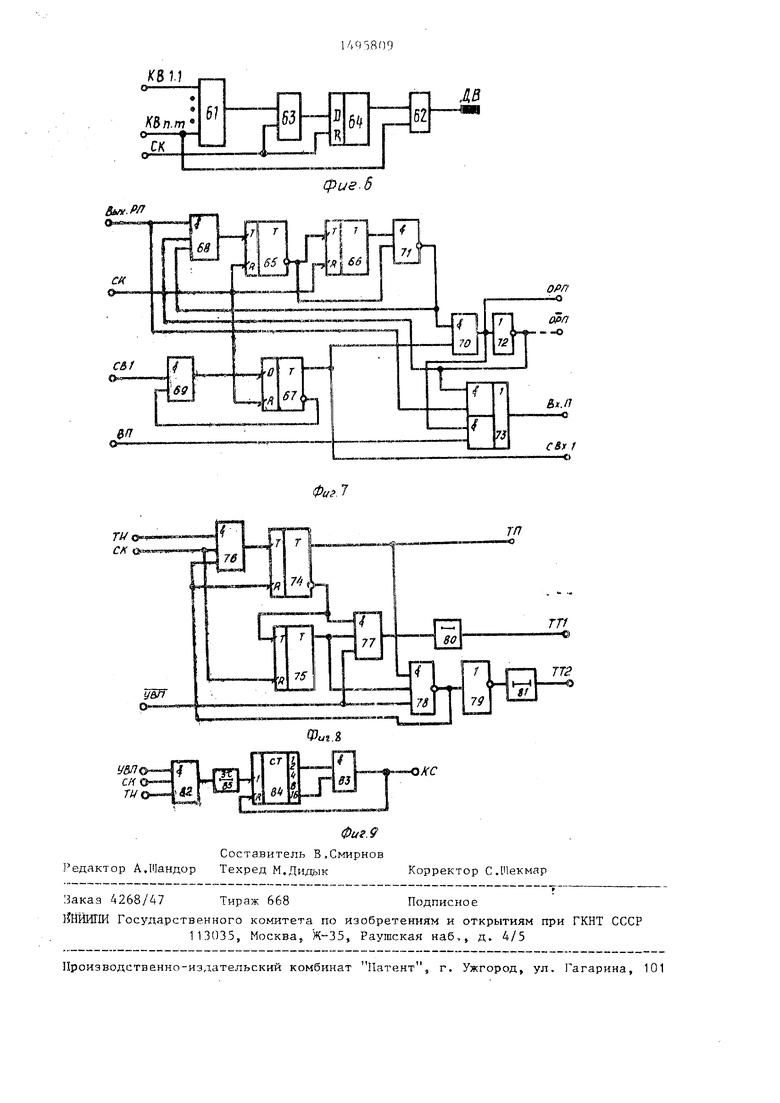

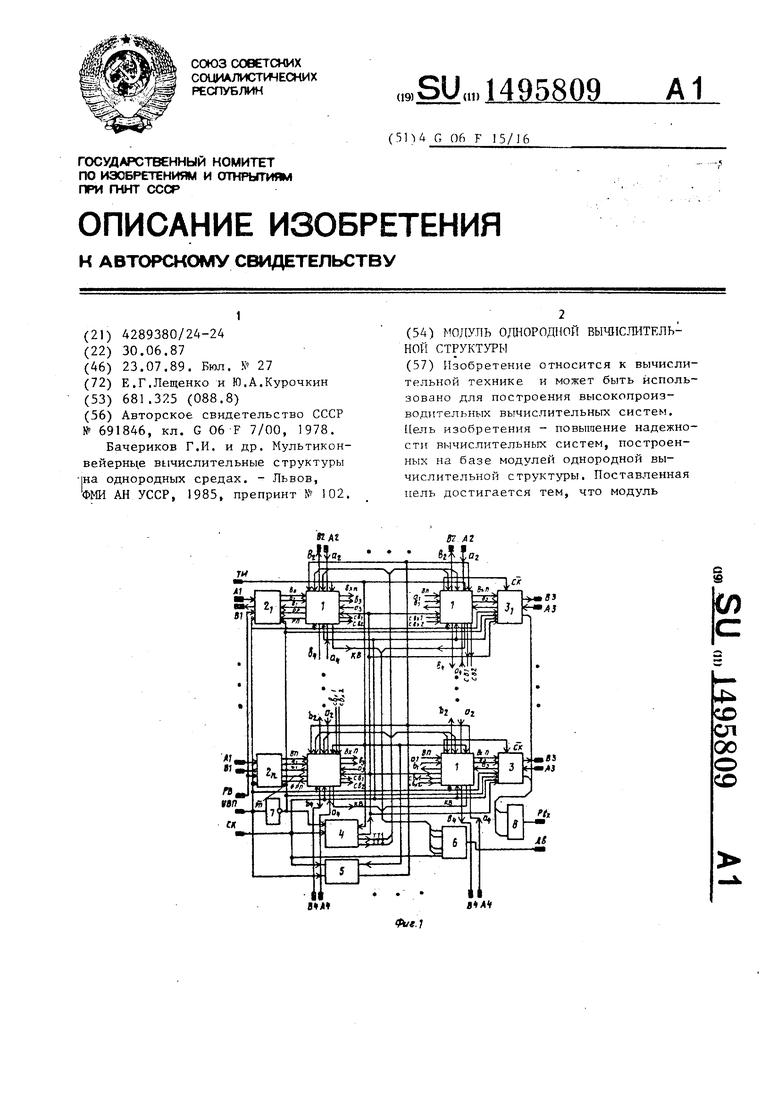

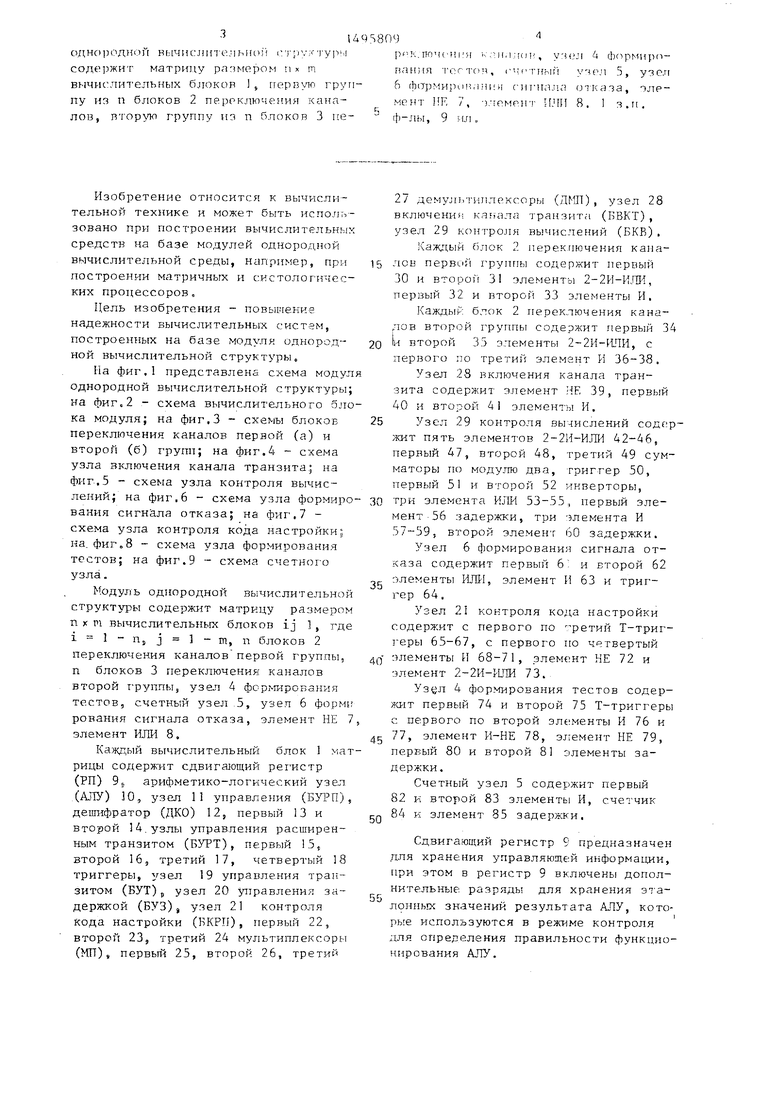

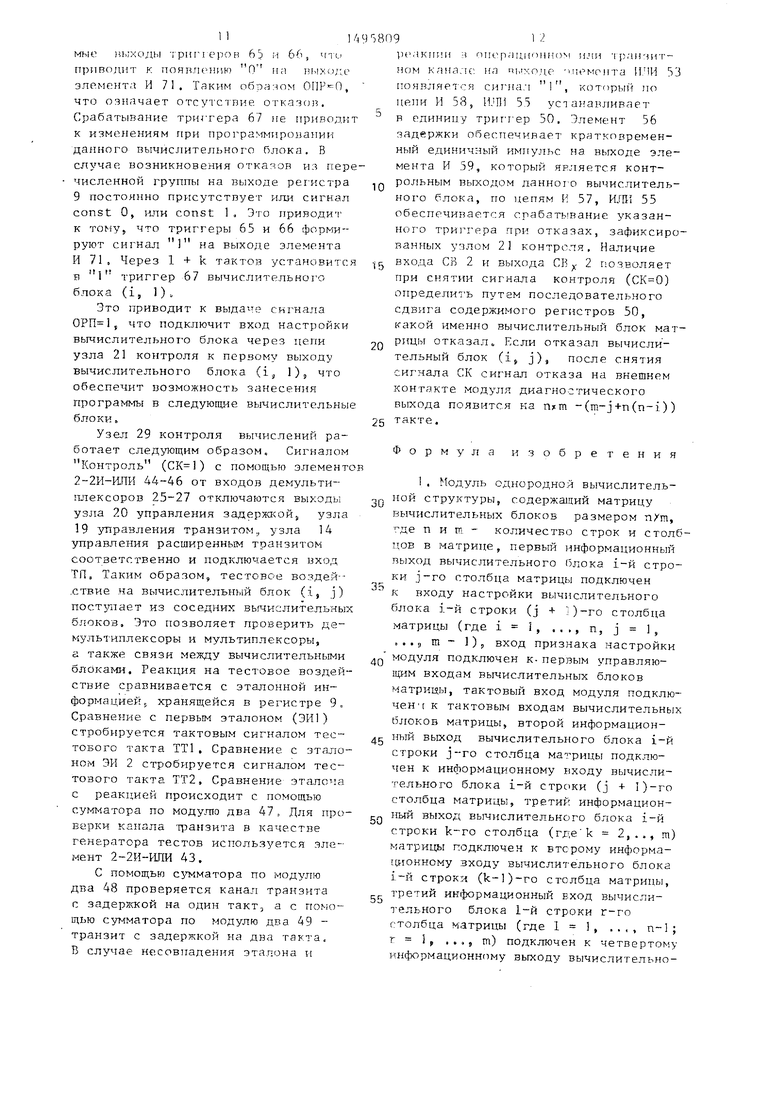

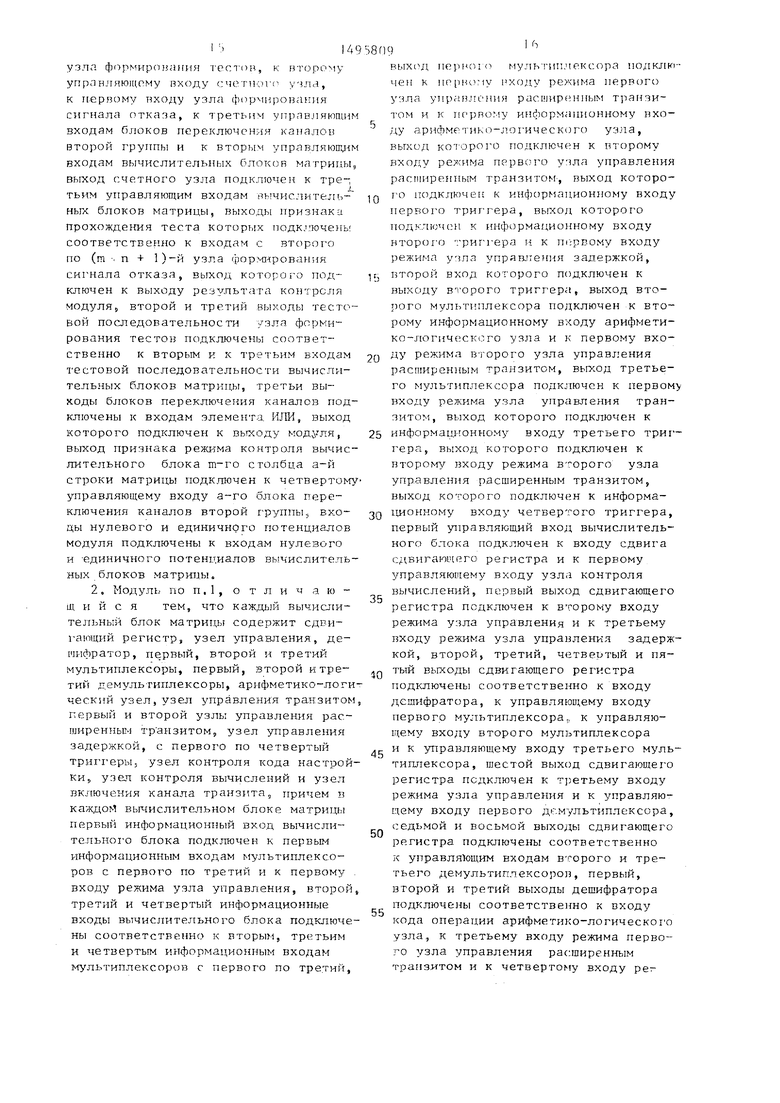

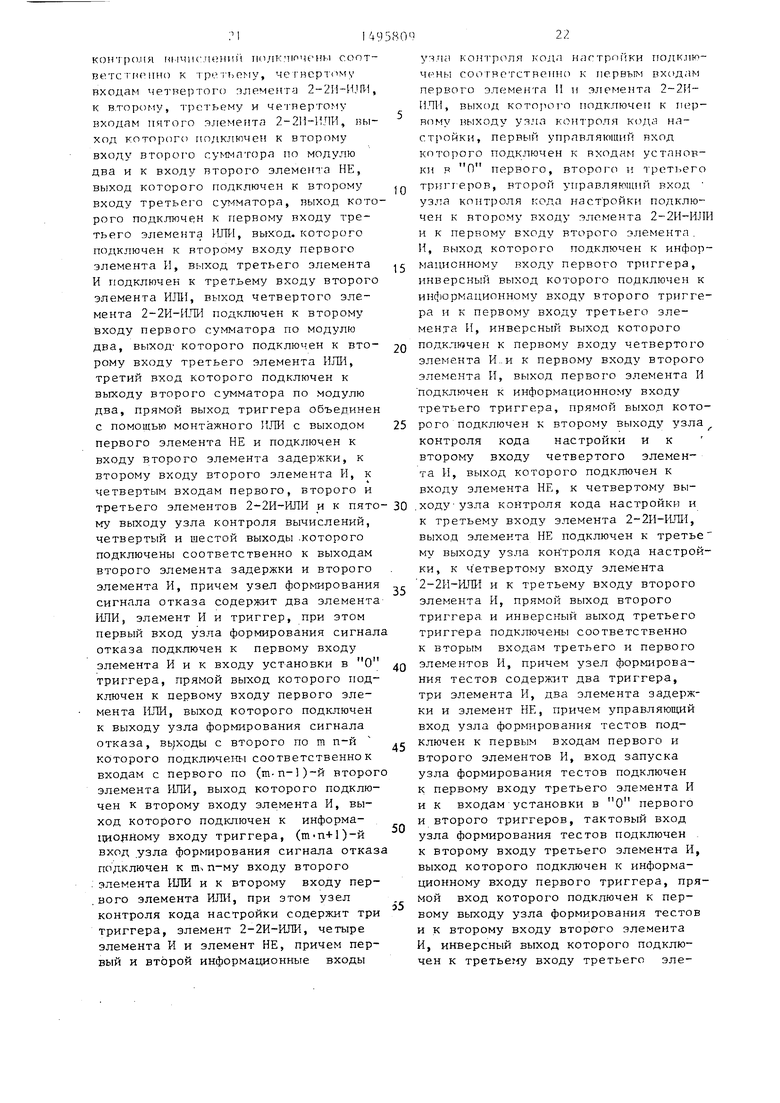

На фиг,1 представлена схема модул однородной вычислительной структуры; на фиг, 2 - схема вь числительного блока модуля; на фиг.З - схемы блоков переключения каналов первой (а) и второй (б) групп; на фиг.4 - схема узла включения канала транзита.; на фиг.З - схема узла контроля вычислений; на фиг.6 - схема узла формирования сигнала отказа; на фиг,7 - схема узла контроля кода настройки;, на, фиг„8 - схема узла формирования тестов; на фиг.9 - схема счетного узла.

Модуль однородной вычислительной структуры содержит матрицу размером п X m вычислительных блоков ij 1, где

т.

п блоков 2

переключения каналов первой группы, п блоков 3 переключения каналов второй группы, узел 4 формирования тестов, счетный узел .5, узел 6 форми рования сигнала отказа, элемент НЕ 7 элемент ИЛИ 8,

Каждый вычислительный блок 1 матрицы содержит сдвига}ощий регистр (РП) 95 арифметико-логический узел (АЛУ) 30, узел 11 управления (), дешифратор (ДКО) 12, первый 13 и Второй 14.узлы управления расширенным транзитом (БУРТ), первый 15, второй 16, третий 17, четвертый 18 триггеры, узел 19 управления транзитом (БУТ)р узел 20 управления задержкой (БУЗ), узел 21 контроля кода настройки (БКРП), первый 22, второй 23, третий 24 мультиплексоры (МП), первьш 25, второй 26, третий

5

0

5

0

5

0

5

0

5

27 демул.тнплексоры (ДМП) , узел 28 включении кя . ала транзита (БВКТ) , узел 29 контроля вь числений (БКВ) .

Каждый блок 2 переключения каналов первой группы содержит первый 30 и второй 31 элементы 2-2И-ЦГ И, первый 32 и второй 33 элементы И.

Каждый блок 2 перек,лючения кана- дов второй группы содержит первый 34 U второй 35 элементы 2-2И-1-1ЛИ, с первого по третий элемент Pi 36-38.

Узел 28 включения канала транзита содержит элемент НЕ 39, первый 40 и второй 41 элемент Ь И.

Узел 29 контроля вычислений содер- ;кит пять элементов 2-2И-ИЛ1 1 42-46, первый 47, второй 48, третий 49 сумматоры по модулю два, триггер 50, первый 51 и второй 52 инверторы, три элемента ИЛИ 53-55, первый элемент -56 задержки, три элемента И 57-59. второй элемент 60 задержки.

Узел 6 формирования сигнала отказа содержит первый 6 и второй 62 элементы ИЛИ, элемент И 63 и триггер 64.

Узел 21 контроля кода настройки содержит с первого по фетий Т-триг- 1-еры 65-67, с первого по четвертый элементы И 68-71, элемент НЕ 72 и элемент 2-2И-ШШ 73.

4 формирования тестов содержит первый 74 и второй 75 Т-триггеры с первого по второй элементы И 76 и 77, элемент И-НЕ 78, элемент НЕ 79, первый 80 и второй 81 элементы задержки .

Счетный узел 5 содержит первый 82 и второй 83 элементы И, счетчик 84 к элемент 85 задержки.

Сдвигающий регистр 9 предназначен для хранения управляющей информащии, при этом в регистр 9 включены дополнительные разряды для хранения эта- лонных значений результата АЛУ, кото- рьге используются в режиме контроля для определения правильности функционирования АЛУ.

Учел 2) контроля кода настройки предназначен для контроля регистра 9 в режиме программирования, В случае, возникновения неи справности типа const О или const 1 в одном из разрядов регистра 9 узел 21 контроля блокирует регистр 8 и восстанавливает возможность занесения программы в последующие вычислительные блоки, формируя при этом сигнал отказа, который воспринимается узлом 29 контроля вычислений. Узел 28 включения канала транзита при поступлении сигнала контроля производит принудительное включение канала транзита по контуру мультиплексора 24,узел 19 управления транзитом - D-триггер 17 узел 14 управления расширенным транзитом . D-триггер 18 узел 29 контроля вычислений путем подачи соответствующих управляющих воздействий на узел 19 управления транзито и узел 14 управления расширенным транзитом, необходимость которого обуславливается наличием операций генерация константы и Расширенный транзит, при которых характер передачи данных по транзитному каналу значительно затрудняет возможность контроля канала. Поэтому в режиме Контроль происходит принудительное включение канала транзита по указанному контуру. Узел 29 контроля вычислений производит контроль операцион- но-транзитного канала вычислительног блока в режиме Контроль путем срав нения реакции операционно-транзит- ного канала на. тестовое воздействие и эталонных значений, которые хранятся в регистре 9,

Для обеспечения режима контроля вычислительных блоков, объединенных в модуль, предусмотрен узел 4 формирования тестов, который генерирует тест как для проверки регистра 9, так и для проверки операционно-тран- зитного канала. Тестовое воздействие подается на все вычислительные блоки одновременно. Схема подключения внешних входов модуля с использованием блоков переключения каналов 1 и 2 обеспечивает подключение внешнего контакта модуля входа в зависимости от режима работы либо к входу настройки, либо к информационному входу вычислительных блоков, кроме того при отказе (обрьш, короткое замыкание) внешней связи в граничных столбцах матрицы или при отказе регистра 9 в одной из вычислительных блокпп левого гралтичного столбца по сигналу с соответствующего узла 21 контроля . подключается информационный (резервный) выход предыдущего модуля и информационный (резервный) вход данного модуля. Узел 6 формирования

0 сигнала отказа соединен с контроль- ными выходами всех вычислительных блоков модуля и формирует сигнал отказа модуля, причем каждый последующий отказ вызывает срабатывание ука5 занного узла и вьздачу сигнала отказа. Счетный узел 5 необходим для обеспечения работы узла 21 контроля кода настройки и обеспечивает последовательное срабатывание указанных узлов

0 во всех вычислительных блоках модуля однородной вычислительной структуры.

Вычислительный блок работает следующим образом.

5 Для настройки на выполнение конкретной операции вычислительный блок переводится в режим программирования с помощью сигнала на управление вводом программы, равного единице. Перед

0 занесением преграммы происходит одновременное тестирование всех вычислительных блоков, имеющихся в модуле. Тест регистра 9 представляет собой чередующуюся последовательность нуц.лей и единиц, которая подается на внещние контакты выходов ВЗ . модуля. Таким обра.зом, каждый последующий модуль является псевдогенератором тестов для каждого последующего. По0 этому происходит проверка не только регистра 9 каждого вычислительного блока модуля, но и контактов AI и ВЗ.. При использовании одного модуля тестовая последовательность по5 дается извне. Блоки переключения каналов первой и второй групп при сигналах управления вводом программы и контроля, равных единице, обеспечивают подключение контакта AI. к

0 входу ввода программы ВП вычислительного блока i, а выхода тестовой последовательности ТП узла 4 - к внешнему контакту ВЗ -. Если отсутствуют обрывы (короткие замыкания) во внешg них контактах модуля AI и ВЗ ., а

также отказы в виде const 1 и const 0 в регистре 9, то через 1 тактов

(где 1 - число разрядов в регистре 9) тестовая последовательность по7U

является на выходе регистра 9 -и ре- гистрируе тся узлом 21 контроля.

Счетный узел последовательно опрашивает (контрольный сигнал ) узлы 21 контроля всех вычислительных блоков. Если узел 21 контроля зарегистрировал тестовую лоследователь- ность на выходе регистра 9, лоследни считается исправным и контур обхода регистра 9 с помощью целей узла 21 контроля не подключается. Если при контрольном сигнале KCrl узел 21 контроля не зарегистрировал тестовую последовательность, он блокирует выход регистра 9 и подключает контур обхода. Это дает возможность заносить код настройки в регистр 9 последующих блоков при отказе регистра 9 всех блоков модуля однород- ной вычислительной структуры, сигнал контроля СК с внешнего контакта модуля снимается и производится запись кодов настройки в вычислительные блоки. При снятии сигнала конт- роля узел 2 переключения канала подключает вывод программы к внешне му контакту B3j. Если произошел отказ внешнего контакта ВЗ , или внешнго контакт-а А1 , этот отказ интер- претируется узлом 21 Контроля зычис лительного левого граничного столбца как отказ собственного регистра 9. Помимо включения контура блокировки регистра 9 с помощью блоков 1 и 2 переключения каналов происходит подключение выхода РБ , в предыдущем модуле однородной вычислительной структуры и резервного внешнего контакта входа данного модуля. Тем самым сохраняется возможность занесения программы в вычислительные блоки. После записи программы снимается сигнал управления вводом программы. Снятие сигнала управлени вводом программы приводит к переключению с помощью блоков 1 и 2 переключения каналов внешнего контажтов AI., A3-, BI., B3j на информационны входы (выходы) al. аЗ, (в1, вЗ) сооветственно. Работа модуля однородно вычислительной структуры в вычислений ничем не отличается от работы прототипа,

Для проверки правильности выполнния конкретной функции, на которую настроен данный вычислительный блок вводится режим Контроль, который уста1 авливается подачей на внеюзний

5 0 о ,

0

8

контакт foдyля гит налл контроля ( К-1 . По г. контроля уяел 21 контроля отключает выХ ЪЧЬ олерацион- но-транзитного уз.ча каждого блока от демультиллексоров 22-24 и подключает к входам указанных демультиплексоров выход узла 4 формирования тестов. Узел 28 включения каиа,ла транзита настраивает канал транзита на передачу данных с выхода мультиплексора 24 на входы узла 21 контро.т7я. Узел 4 начинает формировать гестслвую последовательность в виде сигнала 101 и тактовые сигналы ТТ1, ТТ2, которые воспринимаются узлом 21 контроля. Сигналы ТТ1, ТТ2 появляются с задержкой соответственно третьего и четвертого тактов после начала формирования тестовой последовательности. По сигналам ТС 1 и ТС2 з узле 21 контроля происходит сравнение информации с выхода узла 20 управления задержкой и эталонной информации, хранящейся в поле ЭЙ регистра 9, а также сравнение информации на выходах D-триггеров 17 и 18 с эталоном, формируемым узлом 21 контроля. На основании результатов контроля формируется сигнал контроль но го входа в узле 21 контроля, а также сигнал на второй выход СВ 2. Сигнал на контрольном выходе КВ указывает наличие нару1лений в функционировании олерадионно-транзитной части вычислительного блока. Данный сигнал поступает в узел формирования сигнала отказа который на основании сигнала контрольного выхода от какого-либо вычислительного блока модуля формирует сигтчал на внешнем контакте модуля диагностического выхода.

Таким образом, за четыре такта происходит контроль всех вычислительных блоков модулей однородной вычислительной структуры. При этом для операции Сложение ; И, И-НЕ, ЗП1 обеспечивается полный контроль всех узлов вычислительных блоков, участвующих в выполнении данной операции, Для операции ИСКЛЮЧАЩЕЕ ИЛИ данный метод не позволяет выявлять отказы, приводяш,ие к const на выходах одного из элементов 10, 13, 15, 16, 20. При контроле операции Расширенный транзит неконтролируемым остается мультиплексор 23, при операции Генерация константы данный метод

контроля не позволяет коитролиро;:ать узел 11 упрлвлештя.

Рассмотрим работу первого и вто - рого блоков переключения каналов. Число данных блоков в модуле однородной вычислительной структуры равно числу строк п матрицы вычислительны блоков. По сигналу управления ввода программы с помощью элементов 2-2И-ИЛ1-1 30 и И 32 происходит подключение соответствующего внешнего контакта А1. к входу настройки вычислительного блока, а с помощью элемента 2-2И-ИПИ 34 (при отсутствии сигнала контр ,.) и элемента 2-2И-ИЛИ 35 - подключение первого выхода вычислительного блока к соответствующему внешнему контакту ВЗ.. С помощью элемента 2-2И-ИЛИ 31 подготавливается цепь для передачи сигнала отказа регистра вычислительного блока (i,O (ОРП) в блок 2 переключения каналов ближайшего левого модуля, в кото ром, в свою очередь, с помощью элементов И 37 и 38 подготавливается цепь включения внешнего контакта модуля информационного (резервного) выхода. При возникновении отказа регистра 9 вычислительного блока (i, 1) или отказе внешнего контакта А1j, или отказе внешнего контакта ВЗ в ближайшем левом модуле однородной вычислительной структуры сигнал отказа ОРП подключает внешний контакт модуля резервного выхода ближайшего левого модуля с помощью элемента И 38 и элемента ИЛИ 8 и внешнего контакта А1. рассматриваемого модуля однородной вычислительной структуры с помощью элемента 2-2Й-ИЛИ 30. При снятии сигнала управления вводом программы УВП-1 элементы 2-2И-ИЛИ 32, И 33 и 2-2И-ИЛИ 35 подключают к соответствующим внешним контактам модуля информационный вход al и информационный выход вЗ.

При снятии сигнала управления , вводом кодов настройки блоки 1 и 2 переключения каналов не обеспечивают восстановление цепей передачи информации между модулями. В этом случае с помощью перепрограммирования (ре- жим перепрограммирования в случае отказов внешнего контакта модуля обеспечивается работой блока 2 переключения каналов и блока 3 переключения каналов 3 ) можно обойти отказавший вычислительный блок.

0

5

0

5

Узел 4 формирования тестов работает TojTi)KO в режиме Контроль. При сигнале контроля CKrl открывается вентиль (элемент И 76) и на прямом выходе триггера 74, который является формирователем тестовой последовательности, с приходом тактовых импульсов фop п pyeтcя. последовательность Нулей и единиц..При наличии сигнала управления вводом програм () на выходе эле -1ента И-НЕ 78 присутствует уровень логической 1 и блокировка элемента И 76 возможна только снятием сигнала контроля СК, что и делается после завершения проверки регистром 9 всех вычислительных блоков находящихся в данном модуле однородной вычислительной структуры.

При контроле регистра 9 выходы ТТ1 и ТТ2 узла 4 не используются. Режиму контроля операционно-транзит- ного узла соответствуют сигналы контроля и управления вводом про- грамм - (). В этом случае на выходе тестовой последовательности (ТП) появляется последовательность 101, после чего с помощью эле- 0 мента И-НЕ 7В происходит блокировка элемента И 76 и генерация тестовой последовательности прекращается. На выходах тестового такта TTi (ТТ2) .появляется единичный сигнал соответственно через третий и четвертый .такты после подачи сигналов контроля и управления вводом программы . Счетный узел 5 производит выдачу сигнала (уровень логической 1) через каждые 1 тактов.

Узел 21 контроля кода настройки работает след тощим образом.

Работа данного узла начинается с приходом сигнала контроля , по которому Обнуляются триггеры 65- 67. Это означает, что на выходе элемента И 71 и элемента НЕ 72 присутствует уровень логической 1, триггер 65 открыт для приема информации с выхода регистра 9. Тестовая последовательность с выхода ТП узла 4 формирования тестовой последовательности в случае отсутствия отказов вида const О и const 1 в регистре 9

5

0

5

0

и отказов внешнего контакта B3j и А1 : через 1 тактов появится на выходе регистра 9 вычислительного блока (i, 1). Последовательность 101 устанавливает . в состояние 1

поя111 /

мые ньгходы -григтерон 65 и 66, MTLJ пряводнт к появлению О нп ных М/ю элемента И 71. Таким обманом , что означает отсутст вне отказоп. Срабатывание триггера 67 не приводит к изменениям при программиронании данного вычислительного блока, В случае возникновения отказов из перечисленной группы на 7зыходе рег истра 9 постоянно присутствует или сигнал const О, или const 1, Это приводит к тому, что триггеры 65 и 66 формируют сигнал 1 на выходе элемента И 71, Через 1 + k тактон установится в 1 триггер 67 вычислительного блока (1, 1).

Это приводит к выдаче сигнала ОРП, что подключит вход настройки вьгчислительнот О блока через цепи узла 21 контроля к первому выходу вычислительного блока (i, l)j что обеспечит возможность занесения программь в следующие вычислительные блоки,

Узел 29 контроля вычислений работает следующим образом. Сигналом Контроль (СК) с помощью элементо 2 2И-ИЛИ 44-46 от входов демульти- suieKcopoB 25-27 отключаются выходы узла 20 управления задержкой, узла 19 управления транзитом,, узла 14 управления расширенным транзитом соответственно и подключается вход ТП, Таким образом, тестовое воздей-- ,ствие на вычислительньш блок (i, j) поступает из соседних вычислительных блоков. Это позволяет проверить де- мультиплексоры и мультиплексоры, а также связи между вычислительньми блоками. Реакдия на тестовое воздействие сравнивается с эталонной информацией, хранящейся в регистре 9. Сравнение с первым эталоном (ЭИ1) стробрфуется тактовым сигналом тестового такта ТТ1, Сравнение с эталоном ЭЙ 2 стробируется сигналом тестового такта ТТ2, Сравнение этапс а с реакцией происходит с помощью сумматора по модулю два 47„ Для проверки капала транзита в качестве генератора тестов используется элемент 2-2И-ШИ 43.

С помощью сумматора по модулю два 48 проверяется канал транзита с задержкой на один такт, а с помо-- щью сумматора по модулю два 49 - транзит с задержкой на два такта. В случае несовпадения эталона и

91

реакции и операцпонмом или ipaM-iirr- ном канале; на ni.ixone -июмоита ИЛИ 53 появляется сит на;: 1 , который по цепи И 58, 11411 55 устанавливает в единицу тригт ер 50, Элемент 56 задержки обеспечивает кратковременный единичный импульс на выходе элемента И 59, который является контрольным выходом данного вычислительного блока, по цепям И 57, ИШ 55 обеспечивается срабатывание указанного трИ1Л ера при отказах, зафиксированных узлом 21 контроля. Наличие

5

0

5

0

5

0

5

входа СВ 2 и выхода СВ- 2 позволяет при снятии сигнала контроля () определить путем последовательного сдвига содержимого регистров 50, какой именно В1)1числительный блок матрицы отказал„ Если отказал вычислительный блок (ij j), после снятия сигнала СК сигнал отказа на внешнем контакте модуля диагностического выхода появится ка плт -(m-j+n(n-i)) такте.

Формула изобретения

I. Модуль однородной вычислительной структуры, содержшдий матрицу вычислительнь Х блоков размером nXm, п и т, - количество строк и столбцов в матрице, первый информационный выход вычислительного блока i-й строки j-ro столбца матрицы подключен к входу настройки вычислительного блока i-й строки (j 4- 1)-го столбца матрицы (где i I, ..,,п, , . . .,, m - 1 ) 5 вход признака настройки модуля подключен к-первым управляю- 1ЦИМ входам вычислительных блоков матрицы, тактовый вход модуля подключена к тактовым входам вычислительных блоков матрицы, второй информационный выход вычислительного блока i-й строки j-ro столбца ма -рицы подключен к информационному входу вычислительного блока i-й строки (j + 1)-го столбца матрицы, третий информационный выход вычислительного блока i-й строки k-ro столбца (rAe k 2,.., m) матрицы подключен к втсрому информационному зходу вычислительного блока i-й строки (k-l)-ro столбца матрицы, третий ин1 юрмационный вход вычисли- т ельного блока 1-й строки г-го столбца матрицы (где 1 1, ,,,, n-l; г. f ... 9 m) подключен к четвертому информационному выходу вычислительноli1A

го блокп (1 + I)-o i piiKn столбца матрицы, четнор гые ииф(1р мл пшенные выходы В111чнг.лительных бпокс в г:ервой строки с парного тю m-fi столбцов матрицы подключены соответственно к выходам с первот-о по т-й первой группы модуля, четвертый информационный вход пычислительног о блока р-й строк столбца матрицы (где ,.,,,п) подключен к пятому информационному выходу вычислительного блока (р-1)-й строки г-го столбца матрицы, четвертые информационные входы вычислительных блоков первой строки с первого по столбцов матрицы подключены соответственно к информационным входам с .первого по т-й первой rpynra i модуля, третьи информационные входы вычислительных блоков п-й строки с первого по т-й столбцов матрицы подключены соответственно к информационным входам с первого по ш-й второй группы модуля, пятые информационные выходы вычислительных блоков п-й строки с первого по тл-й столбцов матрицы подключены соответственно к выходам с первого по т-й второй группы модуля, отличающийся тем, , с целью повышения надежности, контролепригодности и сокращения времени прог раммирования модул в него введены с первого по п-й блоки переключения каналов первой группы, с первого по п-й блоки переключения канллов второй группы, узел формирования тестов, счетный узел, узел формирования сигналов отказа, элемент ИЛИ и элемент НЕ, причем информационные входы с первого по п-и третьей группы модуля подключены соответственно к первым информационным входам блоков переключения каналов с первого по п-й первой группы, информационные входы с первого по п-й четвертой группы модуля подключены соответственно к первым информационным входам блоков переключения каналов с первого по п-й второй группы, первые выходы блоков переключения каналов с первого по п-й первой группы подключены соответственно к выходам с первого по п-й третьей группы модуля, первые выходы блоков перекл очения каналов с первого по п-й второй группы подключены соответственно к выходам с первого по п-й четвертой группы, информационный вход которого подключен

8091-

к вторым инф()nци) входам блоков переключе {ия каналов первой группы, вход признака настройки модуля подключен к первым управляюи1им входам всех блоков переключения каналов цервой и BTOpoii групп, к первому управляющему входу счетного узла и к входу элемента НЕ, выход которого Q подключен к вторым управляющим вхо- дa блоков перек.гмчепия каналов первой и второй rpirnn и к },-правляюпему входу узла формирования тестов, шестой и седьмой инфор ационные выходы g вычислительного блока а-й строки Ь-го столбца aтpицы (где а 1 , ,.., п, b 1, ..., m-1) подключены соответственно к пятому и шестому инфop aциoнным входам вычисл11тельного 0 6noka (b + 1)-го столбца а-й строки матрицы, шестой и седьмой информа- гдаонкые выходы вычислительного блока т-го столбца c-I строки матрицы (где с 1, ,.., п-1) подключены 5 соответственно к пятому и шестому

информационным входам вычислительного блока первого столбца (с+1)-й строки матрипь, второй и третий выходы а-го блока переключения каналов первой 0 группы подключены соответственно к входу настройки и к первому информационному входу вычислительного блока первого столбца а-й строки матрицы, третий, восьмой и девятый информационные выходы вычислительного блока первого столбца а-й строки ь)атрицы подключены соответственно к третье гу информационному, третьему управляющему и четвертому управляющему входам п а-го блока переключения каналов первой группы, первый и второй информационные выходы и второй информационный вход вычислительного блока т-го столбца а-й строки матрицы подключе- ны соответственно к второму информационному, третьему информационному входам и к второму выходу а-го блока переключения каналов второй группы, тактодый вход модуля подключен к счетномз входу счетного узла и к тактовому входу узла формирования тестов, первый выход тестовой последовательности которого подключен к четвертым информационным входам бло- ков переключения каналов второй

группы и первым входам тестовой последовательности вычислительных блоков матрицы, вход признака контроля модуля подключен к входу запуска

5

узлп фо;1миронання тестов, к упранляЮ1цпму вхсзду счет-ноге ysjia, к первому входу узла фор мирования сигнала отказа, к третьим управляющим входам блоков псреключсняя каналов второй группы и к вторым управляюпу1м входам вр)1числительных блоков матрицы выход счетного узла подключен к третьим управляющим входам вычислитель- ньгх блоков матрицы, выходы признака прохождения теста которьгх подключень соответственно к входам с второго по (т . п + 1)-й узла фор о рОБапия сигнала отказа, выход которого подключен к выходу результат-а контроля модуля5 второй и третий выходы тестс- - вой последовательности узла формирования тестов подключены соответственно к вторым и к третьим входам тестовой последовательности вычислительных блоков матрицы, третьи выходы блоков переключения каналов подключены к входам элемента. ИЛИ, выход которого подключен к вьтходу модуля, выход признака режима контроля вычис- .пительного блока т-го столбца а-й строки матрицы подключен к четвертому управляющему входу а-го блока переключения каналов второй группы, входы нулевого и единичного потенциа1; ов модуля подключены к входам нулевого и -единичного потенциалов вычислительных блоков матрицы,

2, Модуль по п,1, отличающийся тем, что каж,цый вычис-гш- тельный блок матриць содержит сдвигающий регистр, узел управления, дешифратор, первый, второй и третий мультиплексорь, первый, второй и третий демульгиплексоры, арифметико-логический узел, узел управления тран:знтом первый и второй узлы управления рас- ширенньм тр анзитом, узел управления задержкой, с первого по четвертый триггеры, узел контроля кода настройки, узел коргтроля вычислений и узел включения канала транзита, причем в каждом вычислительном блоке матрицы первый информационный вход вычисли- тельно1 о блока подключен к первьм информационным входам мультиплексоров с первого по третий и к первому входу режима узла управления, второй третий и четвертый информационные входы вычислительного блока подключены соответственно к вторым, третьим и четвертым информационным входам мультиплексоров с первого по третий.

, пернси 1 мут Ь гиплексора подклкг- чен к црриопу рходу рекима nepB(jro узла уцрагзлс ния расширенным транзитом и к KC pBor.iy информационному входу арифметико-логического узл.а, выход которого подключен к второму входу режима перв(;го узла управления расширенным транзитом, выход которого подключен к информационному входу

первого триггера, выход которого подключен к информационному входу второго тригч-ера и: к пг;рвому входу режима узла упраштения задержкой,

, 1 торой вход которого псщключен к выходу второго триггера, выход второго мультиплексора подключен к второму информационному входу арифметико-логического узла и к первому вхо0 режима второго узла управления расширенным транзитом, выход третьего мультиплексора подключен к первому входу режима узла управления транзитом, выход которого подключен к

5 информационному входу третьего триггера, выход которого подключен к второму ззходу режима второго узла управления расщиренным транзитом, выход которого подключен к информа0 ционному входу четвертого триггера, первый управляюш.ий вход вычислительного блока подключен к входу сдвига сдвигаюигего регистра и к первому управляюишму входу узла контроля вычислений, первый выход сдвигающего регистра подключен к второму входу режима узла управления и к третьему входу режима узла управления задержкой,, второй, третий, четвертый и пяQ тый выходы сдвигающего регистра подключены соответственно к входу дешифратора, к управляющему входу первого мультиплексора,, к управляю- 1дему входу второго мультиплексора и к управляющему входу третьего мультиплексора, шестой выход сдвигающего регистра подключен к третьему входу режима узла управления и к управляющему входу первого демультиплексора, седьмой и восьмой выходы сдвигающего регистра подключены соответственно к управляющим входам второго и третьего демультиплексороп, первый, второй и третий выходы дещифратора подключены соответственно к входу кода операции арифметико-логического узла, к третьему входу режима первого узла управления расширенным транзитом и к четвертому входу per

5

5

0

5

i; I

жима vMin 1. р|1ия, nfpHMii ш.кход KOT(ip( Tio;iP.iiK)4on к втгфгчму вхс ду режима узла управления траи: нтом, второй выход учла упранлення подключен к входу считывання-запися сдвигающего регистра, первые выходы де- мультиплексоров с лервого ло третий объедилены с помощью монтажного ИПИ и подключены к второму информационному выходу вычислительного блока, вторые выходы демультиллексоров с рервого по тро-тий объедин ены с помощью монтажного ИЛИ и подключены к третьему информационному выходу вычислительного блока, третьи вькоды демультиплексоров с первого по третий объединены с помощью монтажного ИЛИ и подключены к .четвертому информационному выходу вычислительного блока, четвертые выходы демультиплексоров с первого по третий объединены с помощью монтажного ИЛИ и подключен к пятому информационному выходу вычислительного блока, тактовый вход которого подключен к синхровходам сдвигающего регистра и арифметико- логического узла и узла контроля вычислений, первыйJ второй и третий входы тестовой последовательности вычислительного блока подключены соответственно к первому, второму и третьему информационным входам узла контроля вычислений, первый, второй и третий выходы которого подключены соответственно к информационным входам первого, второго и третьего демультиплексоров, второй управляющий вход вычислительного блока подключен к входу режима узла включения канала транзита, к второму управляющему входу узла контроля вь числений и к первому управляющему входу узла контроля кода настройки, первый, второй и третий выходы которого подключены соответственно к первому, шестому и восьмому информационным выходам вычислительного блока, пятый и шестой информационные входы которого подключены соответственно к первому информационному входу узла контроля кода настройки и к четвертому информационному входу узла контроля вычислений, вход настройки вычислительного блока подключен к второму информационному входу узла контроля кода настройки и к информа- 1 ионному входу сдвигающего регистра, выход переноса которого подключен к

38П918

тор(тму упрлр.ч я(мчрму т хоцу узля

контроля кола НЛГ-ТроГтКИ, ЧРТЕЧ РТЬЧЙ

вь ход которог О подключен к ;1енятому информационному выходу вычислительно- го блока и к входу режима узла контроля вычислений, четвертый, пятый и пюстой выходы KOTOpoi-o подключены соответственно к седьмому информаig ционному виходу, ВЫХОДУ признака режима контроля и к выходу признака прохождения теста вычислительного блока, третий и четвертый выходы дешифратора подключены соответствен15 но к первому и второму yпpaвляюнtим входам узла включения канала транзита, первый и второй выходы которого подключены соответственно к третьим входам режима узла управления транзиQ том и второго узла управления расширенным транзитом, девятый и десятый входы сдвигаюр1;его регистра , выход узла управления задержкой, выходы третьего и четвертого триггеров под25 ключены соответственно к третьему и четвертому управляющим входам, пятому, шестому и седьмому информацион- входам узла контроля вычислений, входы нулевого и единичного потенциа0 лов вычислительного блока подключены соответственно к входам нулевого и единичного потенциалов узла контроля вычислений, лри этом каждый блок переключения каналов первой группы содержит два элемента 2-2И-1ШИ и два элемента И, причем в каждом блоке Переключения каналов первой группы первый, второй и третий информационные входы блока переключения каналов

Q первой группы подключены соответственно к первому входу первого элемента 2-2И-ИЛИ, к второму входу первого элемента 2-2И-15Л1 и к первому входу второго элемента 2-2И-ИЛИ, первый

5 управляющий в,ход блока переключения каналов первой группы подключен к первому входу первого элемента И, к второму входу второго элемента 2-2И-1ШИ, второй управляющий вход

5

0

блока переключеш я первой

группы подключен к первому входу второго элемента И и к третьему входу второго элемента 2-2И-ИЛИ, третий управляюрщй вход блока переключения каналов первой группы подключен к третьему входу первого элемента 2-2И-ИЛИ, выход которого подключен к вторым входам первого и второго элементов И, четвертый управляющий

ход узла переключения каналов прр- пой группы подключен к четвертым иходам первого и второго элементов 2-2Я-ИЛИ, выходы второго элемента 11 2И-ИЛИ, первого и второго элементов И подключены соответственно к rrepBONfy, второму и к третьему выходам узла переключения каналов первой группы, при этом узел переключения каналов второй группы содержит два элемента 2-2И-ИЛИ и три элемента И, лрйчем в каждом блоке переключения каналов второй группы первый информа 1ДИОННЫЙ вход блока переключения ка- малов второй группы подк:лючен к первым входам первого и второго элементов И, второй, третий и четвертый информационные входы блока переключения каналов второй группы подключены соответственно к первому входу rtepBoro элемента 2-2И-ИЛИ, к первому зходу второго элемента 2-2И-И.Ш 1 и к второму входу первого элемента 2-2И-И,ПИ, первый управляющий вход блока переключения каналов второй группы подключен к второму входу второго элемента 2-2И-Р1ШТ и к второму входу первого элемента И, выход которого подключен к первому входу третьего элемента И, второй управ- гхяющий вход блока переключения кан:а нов второй группы подключен к третье му входу второго элемента 2-2И-ИЛИ , и к второму 71ХОДУ второго элемента И, третий и четвертый уппавляюшие входы блока переключения кана,аов второй гр лглы подключены соответственно к третьему и к четвертому входам первого элемента 2-2И-ИЛ1 1, выход которого тгодключен к четвертому входу второго элемента 2-2И-5ШИ,, выход которого подключен к второму входу третьего элемента И и к первому выходу блока переключения каналов второй группы, выходы второго и третьего элементов И подключены соответственно к второму и к гретьему вьгходам блока переключения каналов второй группы, при этом узел включения канала транзита содерж-ит два элемента И и элемент НЕ, причем первый, второй управляющие входы и вход режима узла включения канала транз15т подключен соответственно к первому входу первого элемента И,, к первому входу второго элемента И и к входу элемента НЕ, выход которого подключе к вторым входам первог О и второго

элементор М, выходы которых подклю- чень);. с(1отне-1ч:твенно к первому и второму выходам узла включения транзита, причем узел контроля вычислений содержит пять элементов 2-2И-11ЛИ, триггер, два элемента задержки, три сумматора по модулю два, два элемента НЕ, три элемента ИЛИ и три элемента И, причем первый инаЬормационный

вход узла контроля вычислений подключен к первым входам первого, второго s-: третьег о элементов 2--2И-ИЛИ, выходы которых г;одключеуы соответственно

к.первому, второму и третьему выходам узла контроля вычислений, второй информационный вход которого подключен к первым входам четвертого элемента 2-2И-1ШИ, пятого элемента

2-21-1-ИЛИ и первого элемента ИЛИ, ;ыход которого подключен к первому входу первого элемента И, выход которого подключен к первому входу второго элемента ИЛИ, выход которого

Г1одктаочен к информационному входу триггера, инверсный выход которого подключен к входу первого элемента задержки, выход которого подключен к перв-ому входу второго элемента И,

третий информациоиньй вход узла контроля вычислений подключен к вторьЕМ входам первого элемента ИЛИ, четвертох о и пятого элементов 2-2И- ИЛИ, четвертый информационньш вход

узла контроля вычислений подключен к второму входу второго элемента ИЛИ, пятый информационный вход узла контроля вычислений подключен к первому входу первого сумматора по

модулю два и к второму входу первого элемента 2-2И-ИЛИ, шестой информационный вход узла контроля вычислений подключен к первому входу второго сумматора по модулю два и к

второму входу второго элемента 2-2И-ИЛИ, седьмой информационный вход узла контроля вычислений подключен к первому входу третьего сумматора но модулю два и к второму входу третьего элемента 2-2И-ИЛИ, второй управляющий вход узла контроля вычислений подключен к входу первого элемента НЕ, к первому входу третьего элемента И, к входу установки в О

триггера и к третьим входам первого, второго и третьего элементов 2-2И- ШИ, третий, четвертый и первый вход режима, тактовый вход, входы нулевого и единичного потенциалов узла

контроля нмчпслений ноякпючгиы соот- ветс I ruMiHo к iperijeMv, чегнсртсму входам tjeTBeproro злемеиту , к второму, третьему и четвертому входам пятого элемента 2-211-И,ПИ, выход которого гктдключен к второму входу второг о сумматора по модулю два и к входу второго элемента НЕ, выход которого подключен к второму входу третьего суг матора, выход которого подключен к ггервому входу третьего элемента ИЛИ, выход, которого подключен к второму входу первого элемента И, выход третьего элемента И подключен к третьему входу второго элемента ИЛИ, выход четвертого элемента 2-2И-ИЛИ подключен к второму входу первого сумматора по модулю два, выход- которого подключен к второму входу третьего элемента ИЛИ, третий вход которого подключен к выходу второго сумматора по модулю два, прямой выход триггера объединен с помощью монтажного ИЛИ с выходом первого элемента НЕ и подключен к входу второго элемента задержки, к второму входу второго элемента И, к четвертым входам первого, второго и третьего элементов 2-2И-ИЛИ и к пято му выходу узла контроля вычислений, четвертый и шестой выходы .которого подключены соответственно к выходам второго элемента задержки и второго элемента И, причем узел формирования сигнала отказа содержит два элемента ИЛИ, элемент И и триггер, при этом первый вход узла формирования сигнал отказа подключен к первому входу элемента И и к входу установки в О триггера, прямой выход которого подключен к первому входу первого элемента ИЛИ, выход которого подключен к выходу узла формирования сигнала отказа, вь)ходы с второго по m n-pi которого подключего соответственно к входам с первого по (т-п-)-й второг элемента ИЛИ, выход которого подключен к второму входу элемента И, выход которого подключен к информа- iijiOjiHOMy входу триггера, (т-п+О-й вход узла формирования сигнала отказ подключен к т п-му входу второго . элемента ИЛИ и к второму входу пер- .вого элемента ИЛИ, при этом узел контроля кода настройки содержит три триггера, элемент 2-2И-ИЛИ, четыре элемента И и элемент НЕ, причем первый и второй информационные входы

10

5

0

5

0

5

0

5

0

уялл контроля кода настройки подключены соогветствепнс1 к первым первого элемента И и элемента 2-2И ИЛИ, выход которот о подключен к первому выходу уяла контроля К(да настройки, первый управляющий вход которого подключен к входам установки R П первого, второго и третьего тригг-еров, второй управляющий вход узла контроля 1сода настройки подключен к второму входу элемента 2-2И-ШШ и к первому входу второго элемента. И, выход которого подключен к информационному входу первого триггера, инверсный выход которог о подключен к информационному входу второго триггера и к первому входу третьего зле- мен.та И, инверсный выход которого подключен к первому входу четвертого элемента И..и к первому входу второго элемента И, выход первого элемента И подключен к информационному входу третьего триггера, прямой выход которого подключен к второму выходу узла контроля кода настройки и к второму входу четвертого элемента И, выход которого подключен к входу элемента НЕ, к четвертому вы- .ходу-узла контроля кода настройки и к третьему входу элемента 2-2Р1-ЮТ, выход элемента НЕ подключен к третье му выходу узла кон троля кода настройки, к ч етвертому входу элемента 2-2И-ИЛИ и к третьему входу второго элемента И, прямой выход второго триггера, и инверсный выход третьего триггера подключены соответственно к вторым входам третьего и первого элементов И, причем узел формирования тестов содержит два триггера, три элемента И, два элемента задержки и элемент НЕ, причем управляющий вход узла формирования тестов подключен к первым входам первого и второго элементов Р1, вход запуска узла формирования тестов подключен к первому входу третьего элемента И и к входам установки в О первого и второго триггеров, тактовый вход узла формирования тестов подключен - к второму входу третьего элемента И, выход которого подключен к информационному входу первого триггера, прямой вход которого подключен к первому выходу узла формирования тестов и к второму входу второго элемента И, инверсный выход которого подключен к третьег-iy входу третьего элеФае. 2

CeWo

Фс/г.

Ц

8 лмпгз

с

5

8импгб

о

НМЛ 27

CS}(2

о

У

ск

-о

Ф«.5

| Ячейка однородной вычислительной среды | 1977 |

|

SU691846A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Бачериков Г.И | |||

| и др | |||

| Мультикон- вейернце вычислительные структуры на однородных средах | |||

| - Львов, ФМИ АН УССР, 1985, препринт № 102. | |||

Авторы

Даты

1989-07-23—Публикация

1987-06-30—Подача