(54) ФАЗОМЕТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазометр | 1979 |

|

SU849096A1 |

| Цифровой фазометр | 1982 |

|

SU1075187A1 |

| Фазометр | 1978 |

|

SU765750A1 |

| Помехоустойчивый цифровой фазометр | 1979 |

|

SU1002979A1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Цифровой фазометр | 1983 |

|

SU1128187A1 |

| Инфранизкочастотный фазометр | 1990 |

|

SU1775683A1 |

| Цифровой фазометр | 1986 |

|

SU1348744A1 |

| СПОСОБ ФАЗИРОВАНИЯ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ ЗАДАННОЙ ЧАСТОТЫ В ПРОСТРАНСТВЕННО РАЗНЕСЕННЫХ ЦЕНТРАЛЬНОМ И ОКОНЕЧНОМ ПУНКТАХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2057394C1 |

| Инфранизкочастотный фазометр | 1980 |

|

SU924614A1 |

1

Настоящее изобретение относится кэлектроизмерительной технике и может быть использовано для измерения сдвига фаз между гармоническими сигналами.

Известен фазометр, содержащий первый и второй усилители-ограничители, выходы которых через дифференцирукнцие цепи подключены к входам триггера, выход которого подключен к индикаторному прибору 1.

Недостатками известного устройства являются невозможность измерения фазовых сдвигов близких к О, вследствие сбоев в работе триггера при почти одновременном поступлении запускающих импульсов на его входы, погрешности за счет асимметрии уровней ограничения в усилителях-ограничителях, влияния конечной длительности фронтов выходных импульсов усилителей-ограничителей и дифференцирующих цепей.

Известен фазометр, содержащий первое и второе входные устройства, первую и вторую формирующие цепи, каскад совпадений, усредняющее уст-ройство, причем выходы входных устройств через формирующие цепи подключены к входам каскада совпадений.

выход каскада совпадений, выход каскада совпадений соединен с входом усредняющего устройства, к выходу которого подключен индикатор 2.

Недостатком известного устройства является неоднозначность отсчета фазовых сдвигов в пределах -180°-0°-+ +180° . .

Наиболее близким к изобретению

10 является фазометр, содержащий усилители-ограничители, линии задержки, схемы антисовпадения, усредняющие схемы, вычитающую схему, индикаторы модуля и знака разности фаз, причем,

15 выходы усилителей-ограничителей соединены со входами первой схемы аитисовпадения, выход которой через первую схему усреднения соединен с индикатором модуля разности фаз,

20 входы первой и второй линий задержки соединены с выходами соответствующих усилителей-ограничителей, а их выходы - с первыми входами второй и третьей схем антисовпадения, второй

25 вход второй схемы антисовпадения соединен с выходом второго усилителяограничителя, а второй вход третьей схемы антисовпадения соединен с выходом первого усилителя-ограничите30ля, выходы второй и третьей схем аитисовпадения через схемы усреднения соединены со входами вычитающей схемы, выход которой соединен со входом индикатора знака разности фаз 3.

Этот фазометр обеспечивает определение не только модуля, но и знака измеряемой разности фаз в пределах -180°-0°-+180°.

Недостатками известного устройств является погрешность определения знака разности фаз при измерении фазовых сдвигов, близких к О, возникающая из-за возможного неравенства времен задержек линий задержки, инерционность в определении знака разности фаз при ее переходе О вследствие наличия схем усреднения в канале определения знака разности фаз, погрешность обусловленная асим.1етрией уровней ограничения в усилителях-ограничителях, а также наличие двух индикаторов, что усложняет работу оператора и снижает производительность труда.

Цель изобретения - повышение точности и быстродействия определения знака сдвига фаз при измерении малых фазовых сдвигов.

Поставленная цель достигается тем что в фазометр,содержащий первые и вторые формирователи, инверторы, элементы задержки, элементы совпадения, элемент логического сложения, узел суммирования и усреднения с дифференциальными входами и индикатор, причем, вход второго формирователя подключен ко второму входному сигналу, а. выходы первого и второго формирователей подключены ко входам первого и второго инверторов, выходы которых подключены ко входам соответственно первого и второго элементов задержки.и первым входом. второго и первого элементов совпадения, вторые входы которых подключены соответственно к выходам второго и первого формирователей, а выходы к первому и второму входам элемента логического сложения, введены третий четвертый, пятый и шестой элементы совпадения, и второй триггеры первый и второй и третий ключи, первый и второй пороговые элементы, сумматор, масштабный преобразователь источник опорного напряжения, коммутатор и фазосдвигающий блок, причем, вход последнего подключен к первому входному сигналу и первому, а выход ко второму входам коммутатора, выход которого подключен ко входу первого формирователя, первые входы третьего и четвертого элементов совпадения подключены ко входам первого .и второго элементов задержки, вторые-- к выходам первого и второго элементов совпадения, а выходы - к первым и вторым входам первого триггера соответственно, причем,.первыйи второй выходы последнего подключены соответственно к первым входам пятого и шестого элементов совпадения, вторые входы которых подключены к выходу элемента логического сложения, а выходы - ко вторым входам соответственно первого и второго ключей, первые входы которых подключены к выходу источника опорного напряжения, а выходы соответственно к первым и вторым входам узла суммирования и усреднения, выход которого подключен к входам первого и второго пороговых элементов и первому входу сумматора, ,выход которого подключен к индикатотору, а второй вход - к выходу третьего ключа, первый вход которого через масштабный преобразователь подключен к выходу источника опорного напряжения, а второй - к третьему входу коммутатора и выходу второго триггера, первый и второй входы которого подключены соответственно к выходам первого и второго пороговых элементов.

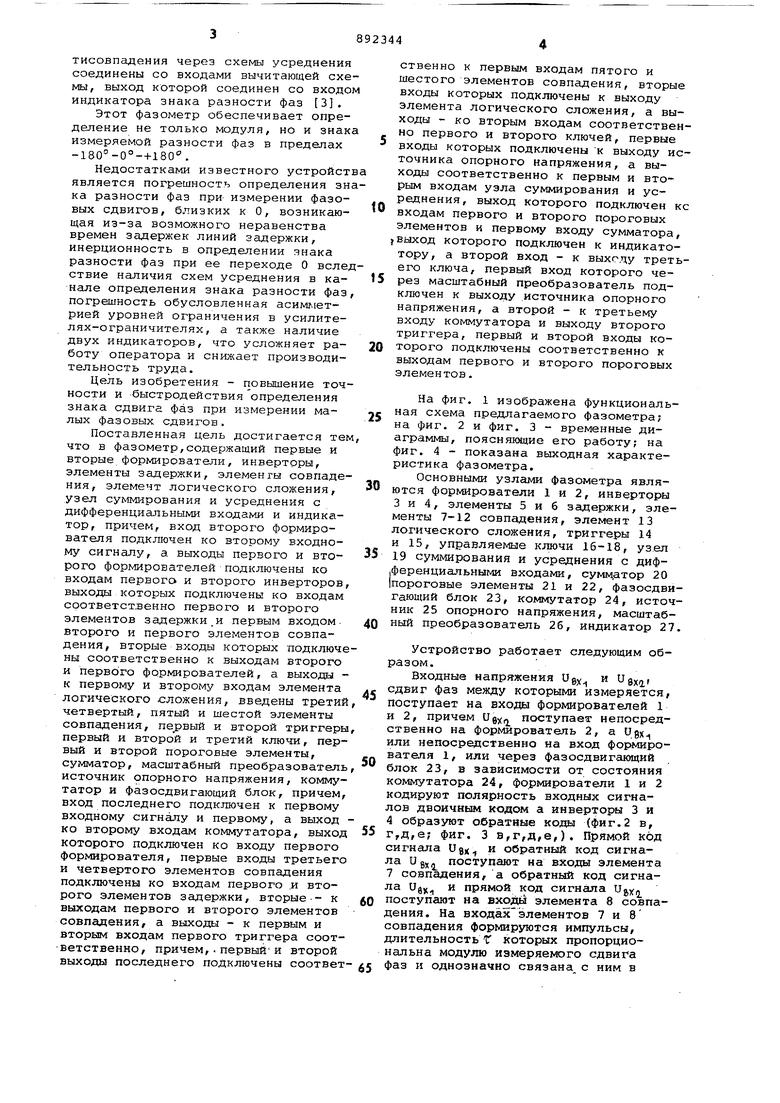

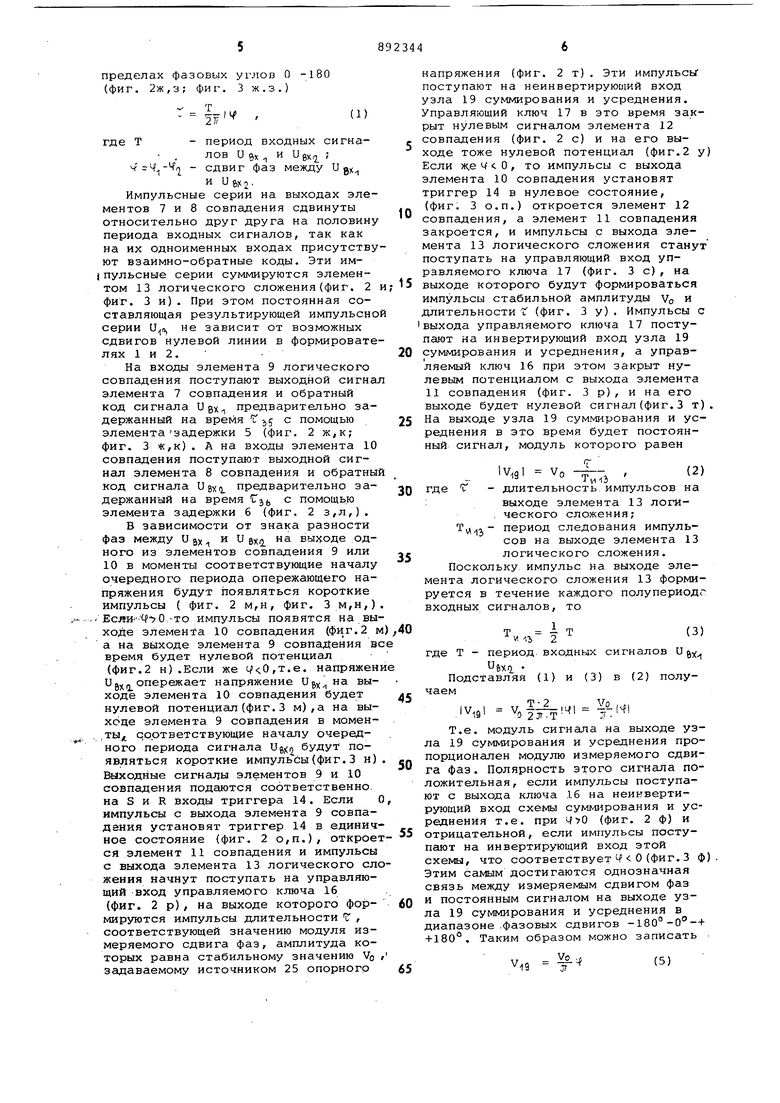

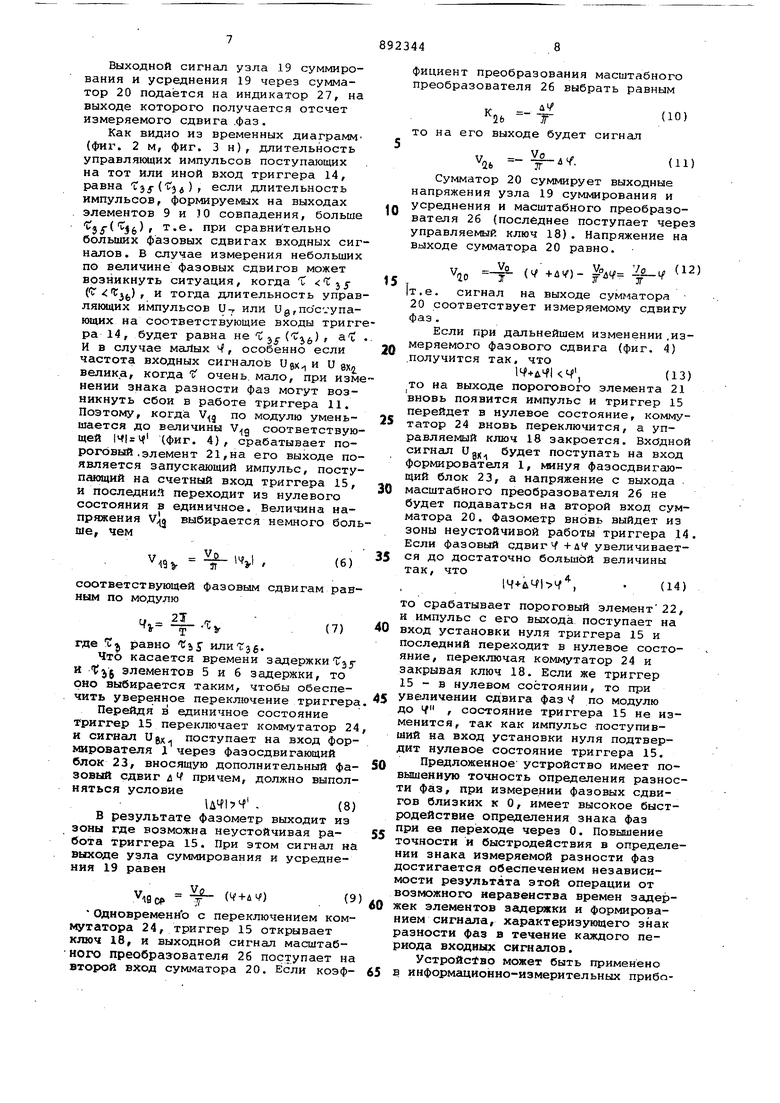

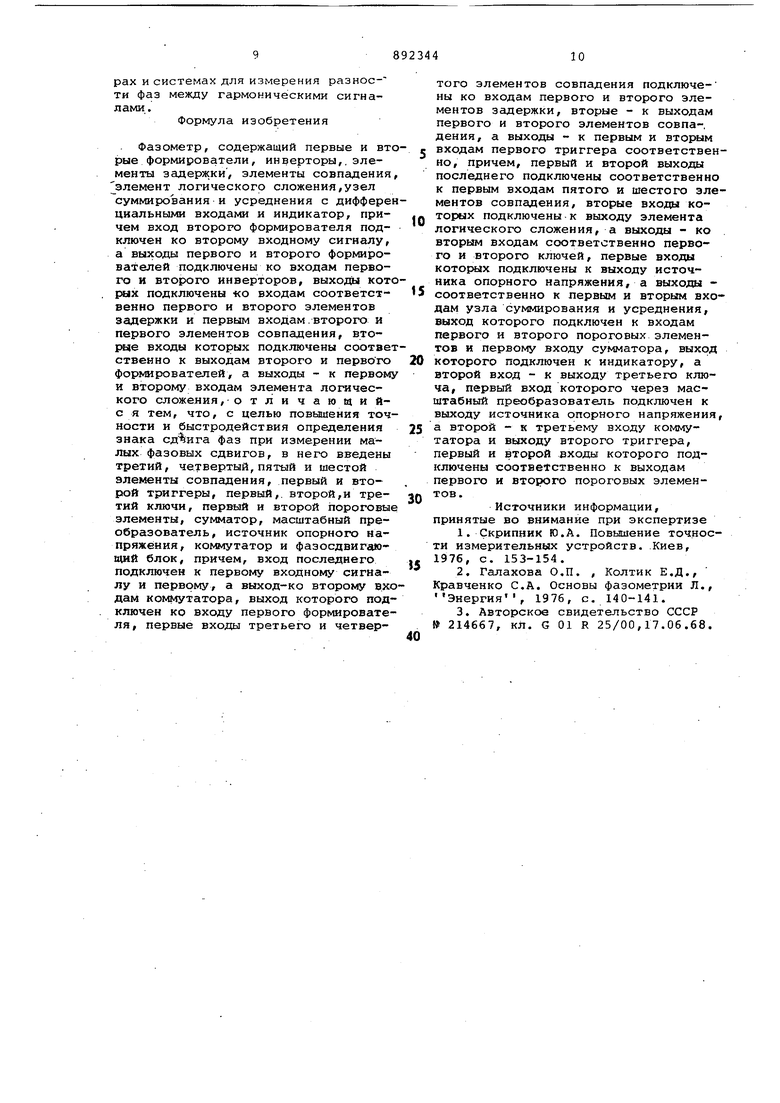

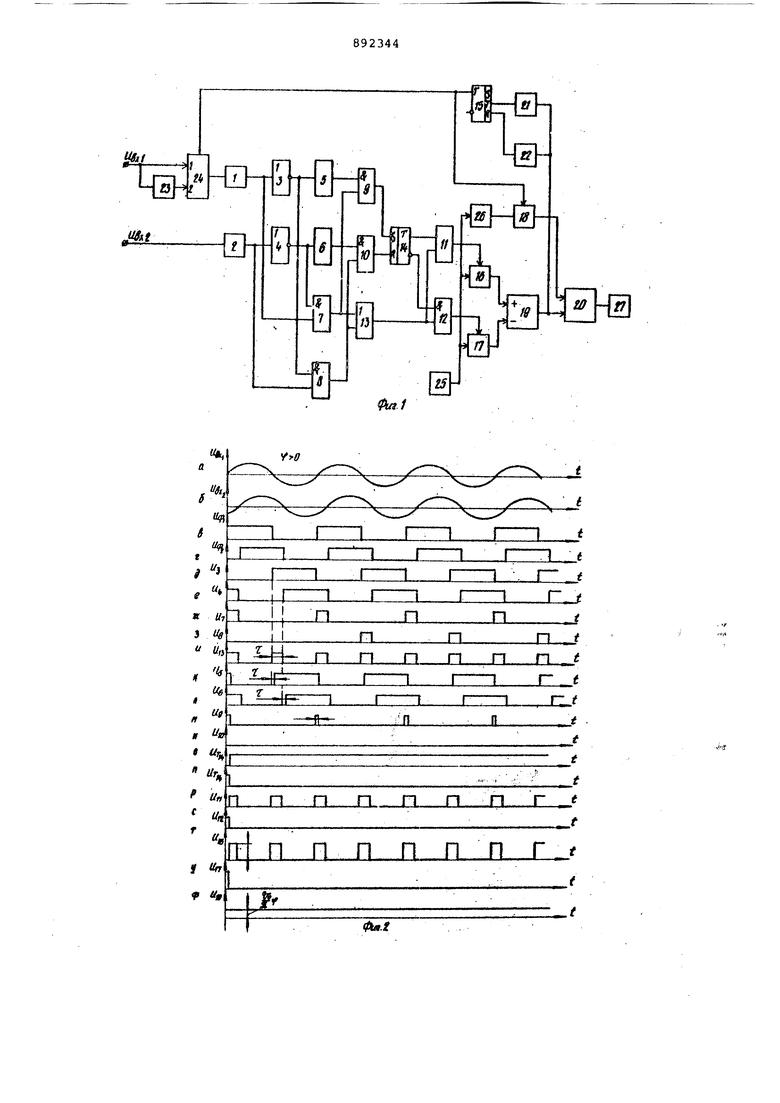

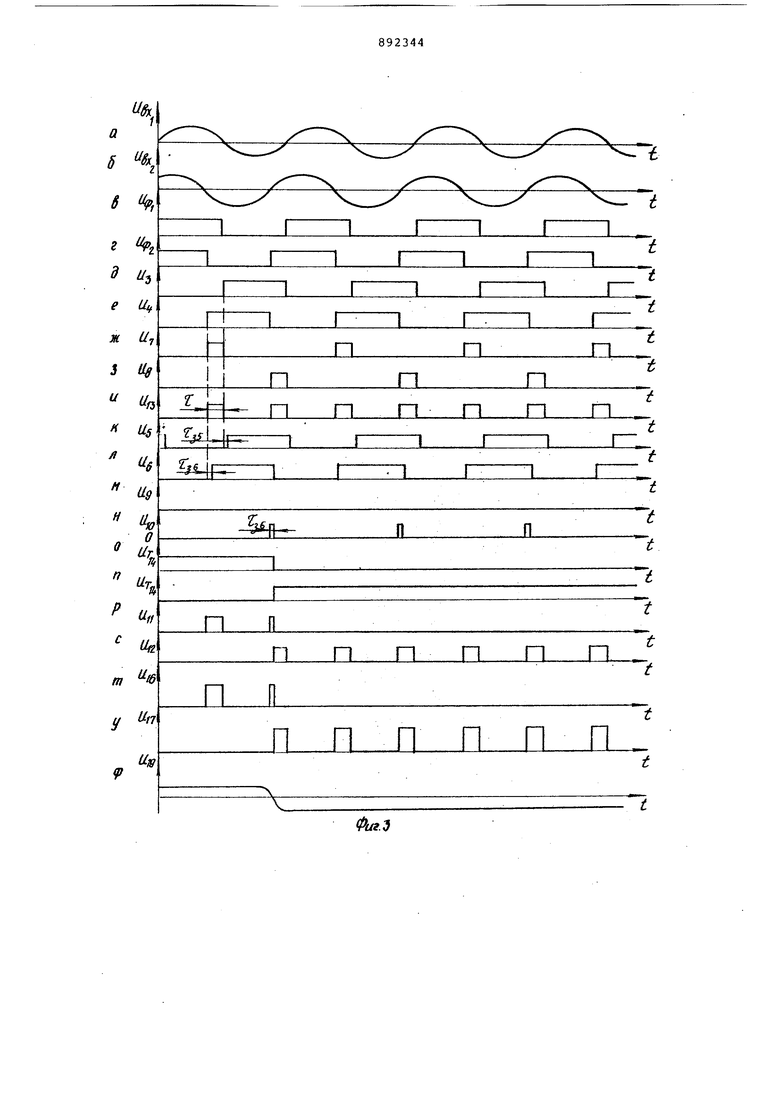

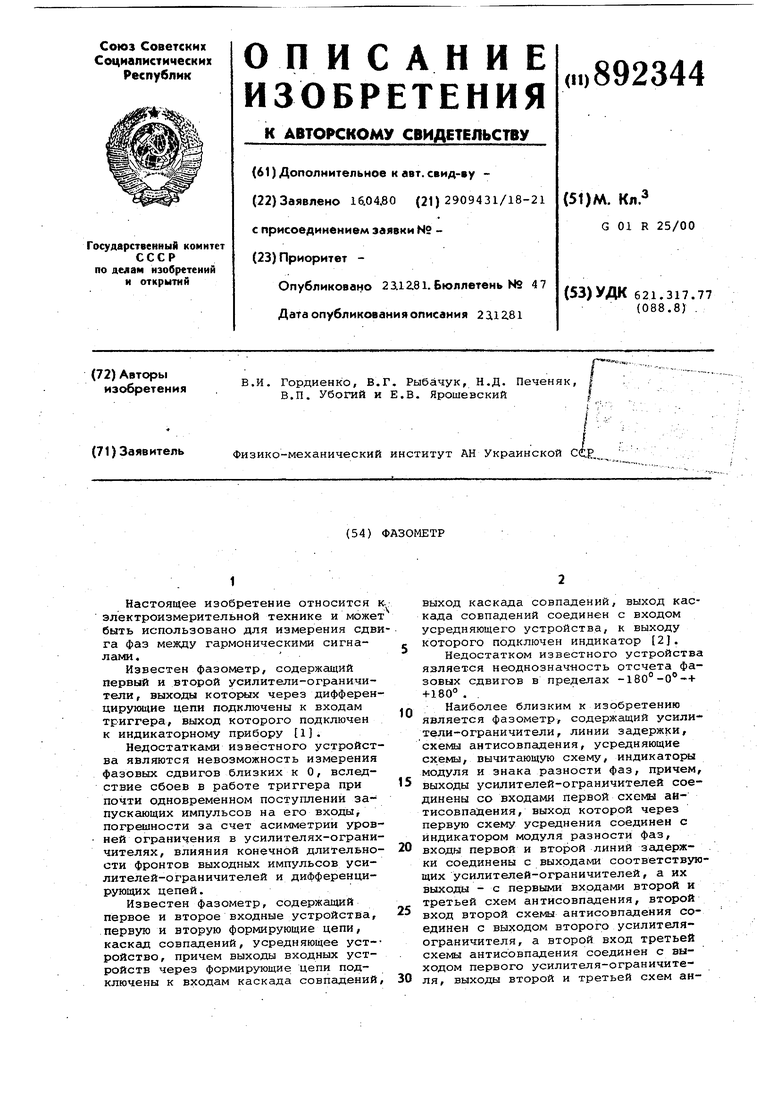

На фиг. 1 изображена функциональная схема предлагаемого фазометра; на фиг. 2 и фиг. 3 - временные диаграммы, поясняющие его работу; на фиг. 4 - показана выходная характеристика фазометра.

Основными узлами фазометра являются формирователи 1 и 2, инверторы

3и 4, элементы 5 и б задержки, элементы 7-12 совпадения, элемент 13 логического сложения, триггеры 14

и 15, управляемые ключи 16-18, узел 19 суммирования и усреднения с диф.ференциальными входами, сумматор 20 (пороговые элементы 21 и 22, фазосдвигающий блок 23, коммутатор 24, источник 25 опорного напряжения, масштабНЕЛй преобразователь 26, индикатор 27

Устройство работает следующим образом.

Входные напряжения Ug,; и , сдвиг фаз между которыми измеряется, поступает на входы формирователей 1 и 2, причем иду поступает непосредственно на формирователь 2, а Ugx или непосредственно на вход формирователя 1, или через фазосдвигающий блок 23, в зависимости от состояния коммутатора 24, формирователи 1 и 2 кодируют полярность входных сигналов двоичным кодом а инверторы 3 и

4образуют обратные кода (фиг.2 в, г,д,е; фиг, 3 в,г,д,е,). Прямой код сигнала Ug и обратный код сигнапоступают на входы элемента

ла и

вхо.

7 совпадения, а обратный код сигнала Uj и прямой код сигнала поступают на вхоДы элемента 8 совпадения. На входах элементов 7 и 8 совпадения формируются импульсы, длительностьТ которых пропорциональна модулю иэмеряемого сдвига фаз и однозначно связана с ним в пределах фазовых углов О -180 (фиг. 2ж,з; фиг. 3 ж.з.) - период входных сигна . лов и вх и Uex ; - сдвиг фаз между U g и и бх 2 . Импульсные серии на выходах элементов 7 и 8 совпадения сдвинуты относительно друг друга на половину периода входных сигналов, так как на их одноименных входах присутству ют взаимно-обратные коды. Эти имj пульсные серии суммируются элементом 13 логического сложения(фиг. 2 фиг, 3 и). При этом постоянная составляющая результирующей импульсно серии , не зависит от возможных сдвигов нулевой линии в формировате лях 1 и 2. . На входы элемента 9 логического совпадения поступают выходной сигна элемента 7 совпадения и обратный код сигнала Ugx предварительно задержанный на время Тjj с помощью элементазадержки 5 (фиг. 2 ж,к; фиг. 3 ж,к). А на входы элемента 10 совпадения поступают выходной сигнал элемента 8 совпадения и обратны код сигнала Ugyij предварительно задержанный на время Tjj, с помощью элемента задержки 6 (фиг. 2 з,л,). В зависимости от знака разности фаз между U gx и b-x/i, а одного из элементов совпадения 9 или 10 в моменты соответствующие началу очередного периода опережающего напряжения будут появляться короткие импульсы ( фиг. 2 м,н, фиг. 3м,и,) Если1-Ч 70-то импульсы появятся на вы ходе элемента 10 совпадения (фиг. 2 а на выходе элемента 9 совпадения в время будет нулевой потенциал (фиг.2 н) .Если же ,т.е. напряжен и опережает напряжение Ug на выходе элемента 10 совпадения будет нулевой потенциал (фиг.3 м),а на выходе элемента 9 совпадения в момен,ты соответствующие началу очередного периода сигнала Ug, будут появляться короткие импульсы(фиг.3 н) Выходные сигналы элементов 9 и 10 совпадения подаются соответственно на S и R входы триггера 14. Если импульсы с выхода элемента 9 совпадения установят триггер 14 в единич ное состояние (фиг. 2 о,п.), открое ся элемент 11 совпадения и импульсы с выхода элемента 13 логического сл жения начнут поступать на управляющий вход управляемого ключа 16 (фиг. 2 р), на выходе которого формируются импульсы длительности Т, соответствующей значению модуля измеряемого сдвига фаз, амплитуда которых равна стабильному значению VQ задаваемому источником 25 опорного напряжения (фиг. 2 т) . Эти импульсы поступают на неинвертирующий вход узла 19 суммирования и усреднения. Управляющий ключ 17 в это время закрыт нулевым сигналом элемента 12 совпадения (фиг. 2с) и на его выходе тоже нулевой потенциал (фиг.2 у) Если Ч О , то импульсы с выхода элемента 10 совпадения установят триггер 14 в нулевое состояние, (фиг. 3 о.п.) откроется элемент 12 совпадения, а элемент 11 совпадения закроется, и импульсы с выхода элемента 13 логического сложения станут поступать на управляющий вход управляемого ключа 17 (фиг. 3с), на выходе которого будут формироваться импульсы стабильной амплитуды VQ и длительности i:f (фиг. 3 у) . Импульсы с выхода управляемого ключа 17 поступают на инвертирующий вход узла 19 суммирования и усреднения, а управляемый ключ 16 при этом закрыт нулевым потенциалом с выхода элемента 11 совпадения (фиг. 3 р), и на его выходе будет нулевой сигнал(фиг.3 т). На выходе узла 19 суммирования и усреднения в это время будет постоянный сигнал, модуль которого равен 9 ° T,j - длительность импульсов на яе : выходе элемента 13 логи. ческого сложения; период следования импульсов на выходе элемента 13 логического сложения. Поскольку импульс на выходе элемента логического сложения 13 формируется в течение каждого полупериодг входных сигналов, то т - т , ,j 2 где Т - период входных сигналов U Подставляя (1) и (3) в (2) получаем v, 15,4, .1 т.е. модуль сигнала на выходе узла 19 суммирования и усреднения пропорционален модулю измеряемого сдвига фаз. Полярность этого сигнала положительная, если импульсы поступают с выхода ключа 16 на неинвертирующий вход схемы сумкшрования и усреднения т.е. при (фиг. 2 ф) и отрицательной, если импульсы поступают на инвертирующий вход этой схемы, что соответствует Ч О (фиг. 3 ф) Этим самым достигаются однозначная связь между измеряемым сдвигом фаз и постоянным сигналом на выходе узла 19 суммирования и усреднения в диапазоне .фазовых сдвигов -180°-0°-+ +180°. Таким образом можно записать Выходной сигнал узла 19 суммирования и усреднения 19 через сумматор 20 подаётся на индикатор 27, на выходе которого получается отсчет измеряемого сдвига,фаз. Как видно из временных диаграмм (фиг. 2 м, фиг. 3 н), длительность управляющих импульсов поступающих на тот или иной вход триггера 14, равна T3j-()f если длительность импульсов, формируемых на выходах элементов 9 и 30 совпадения, больше ) , т.е. при сравнительно больших фазовых сдвигах входных сиг налов. В случае измерения небольших по величине фазовых сдвигов может возникнуть ситуация, когда Г «tjjCir t j,), и тогда длительность управ ляющих импульсов у-т или Ug,nocjynaющих на соответствующие входы тригг ра 14, будет равна не t 3 (tj) , at И в случае маЛых Ч, особенно если частота входных сигналов Ugx, и и gx, велика, когда S очень, мало, при изме нении знака разности фаз могут возникнуть сбои в работе триггера 11. Поэтому, когда по модулю уменьшается до величины соответствующей 1Ч|гл | (фиг. 4) , срабатывает пороговый .элемент 21,на его выходе появляется запускающий импульс, постуПсмснций на счетный вход триггера 15, и последний переходит из нулевого состояния в единичное. Величина напряжения V выбирается немного боль ше, чем 1 , соответствующей фазовым сдвигам равным по модулю и - 21 где t, равно Vt, илиТГзбЧто касается времени задержки Tj И fjg элементов 5 и 6 задержки, то оно выбирается таким, чтобы обеспечить уверенное переключение триггера Перейдя в единичное состояние триггер 15 переключает коммутатор 24 и сигнал Ujx-, поступает на вход формирователя i через фазосдвигающий блок 23, вносящую дополнительный фазовый сдвиг л причем, должно выполняться условие . (8) В результате фазометр выходит из зоны где возможна неустойчивая работа триггера 15. При этом сигнал на выходе узла суммирования и усреднения 19 равен . Одновременно с переключением коммутатора 24, триггер 15 открывает ключ 18, и выходной сигнал масштабного преобразователя 26 поступает на второй вход сумматора 20. Если коэффициент преобразования масштабного преобразователя 26 выбрать равным чь -Т-(10) то на его выходе будет сигнал а. . (11) Сумматор 20 суммирует выходные напряжения узла 19 суммирования и усреднения и масштабного преобразователя 26 (последнее поступает через управляемый ключ 18). Напряжение на выходе сумматора 20 равно. Vi ( +dv) Vc,c/ S-t |т.е. сигнал на выхода сумматора 20 соответствует измеряемому сдвигу фаз . Если при дальнейшем изменении.измеряемого фазового сдвига (фиг. 4) получится так. что ,(13) ТО на выходе порогового элемента 21 вновь появится импульс и триггер 15 перейдет в нулевое состояние, коммутатор 24 вновь переключится, а управляемый ключ 18 закроется. Входной сигнсШ и будет поступать на вход формирователя 1, кмнуя фазосдвигаиощий блок 23, а напряжение с выхода масштабного преобразователя 26 не будет подаваться на второй вход сумматора 20. Фазометр вновь выйдет из зоны неустойчивой работы триггера 14. Если фазовый сдвиг / +ДЧ увеличивается до достаточно большой величины так, что l4-t-u l 4, то срабатывает пороговый элемент22, и импульс с его выхода поступает на вход установки нуля триггера 15 и Последний переходит в нулевое состояние, переключая коммутатор 24 и закрывая ключ 18. Если же триггер 15 - в нулевом состоянии, то при увеличении сдвига фаз по модулю до Ч , состояние триггера 15 не изменится, так как импульс поступивший на вход установки нуля подтвердит нулевое состояние триггера 15. Предложенное устройство имеет повышенную точность определения разности фаз, при измерении фазовых сдвигов близких к О, имеет высокое быстродействие определения знака фаз при ее переходе через О. Повышение точности и быстродействия в определении знака измеряемой разности фаз достигается обеспечением независимости результата этой операции от вoз южнoro неравенства времен задержек элементов задержки и формированием сигнала, характеризующего знак разности фаз в течение каждого периода входных сигналов. Устройство может быть применено в информационно-измерительных прибоpax и системах для измерения разности фаз между гармоническими сигналами.

Формула изобретения

Фазометр, содержащий первые и вторые формирователи , инверторы,, элементы задержки, элементы совпадения, элемент логического сложения,узел суммирования и усреднения с дифференциальными входами и индикатор, причем вход второго формирователя подключен ко второму входному сигналу, а выходы первого и второго формирователей подключены ко входам первого и второго инверторов, выхода которых подключены «о входам соответственно первого и второго элементов задержки и первым входам.второго и первого элементов совпадения, вторые входы которых подключены соответственно к выходам второго и первого формирователей, а выходы - к первому и второму входам элемента логаческого сложения,отличающийс я тем, что, с целью повышения точности и быстродействия определения знака сдвига фаз при измерении малых фазовых сдвигов, в него введены третий, четвертый,пятый и шестой элементы совпадения, первый и второй триггеры, первый,, второй,и третий ключи, первый и второй пороговые элементы, сумматор, масштабный преобразователь, источник опорного напряжения, коьвлутатор и фаэосдвигаюедий блок, причем, вход последнего подключен к первому входному сигналу и первому, а выход-ко второму входам коммутатора, выход которого подключен ко входу первого формирователя, первые входы третьего и четвертого элементов совпадения подключены ко входам первого и второго элементов задержки, вторые - к выходам первого и второго элементов совпа-. дения, а выходы - к первым и входам первого триггера соответственно, причем, первый и второй выходы последнего подключены соответственно к первым входам пятого и шестого элементов совпадения, вторые входы которых подключенык выходу элемента

0 логического сложения, а выходы - ко вторым входам соответственно первого и второго ключей, первые входы которых подключены к выходу источника опорного напряжения, а выходы 5соответственно к первым и вторым входам узла суммирования и усреднения, выход которого подключен к входам первого и второго пороговых элементов и первому входу сумматора, выход

0 которого подключен к индикатору, а второй вход - к выходу третьего ключа, первый вход которого через масштабный преобразователь подключен к выходу источника опорного напряжения, а второй - к третьему входу комму5татора и выходу второго триггера, первый и второй входы которого подключены соответгственно к выходам первого и второго пороговых элементов.

0

Источники информации, принятые во внимание при экспертизе

5

№ 214667, кл. G 01 R 25/00,17.06.68.

0

«,

rrf п п п п п п г t

1

Р Ug

.t

фмЛ 5 8, дz/э еи жa JUe ii9 О пп Г1 т % п I у f п ,

Авторы

Даты

1981-12-23—Публикация

1980-04-16—Подача