(54) СЛЕДЯЩИЙ СТОХАСТИЧЕСКИЙ ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Стохастическое устройство для возведения в целую степень | 1981 |

|

SU962941A2 |

| Следящий стохастический интегратор | 1977 |

|

SU681431A1 |

| Стохастический преобразователь | 1977 |

|

SU732946A1 |

| СТОХАСТИЧЕСКИЙ ИНТЕГРАТОР | 1972 |

|

SU428411A1 |

| Следящий стохастический интегратор | 1979 |

|

SU789998A1 |

| Устройство для моделирования нейрона | 1989 |

|

SU1709356A1 |

| Вероятностное устройство для деления чисел | 1981 |

|

SU962939A1 |

| Вероятностный интегратор | 1980 |

|

SU900283A1 |

| Усилитель вероятности | 1978 |

|

SU750498A1 |

| Следящий стохастический интегратор | 1990 |

|

SU1728868A1 |

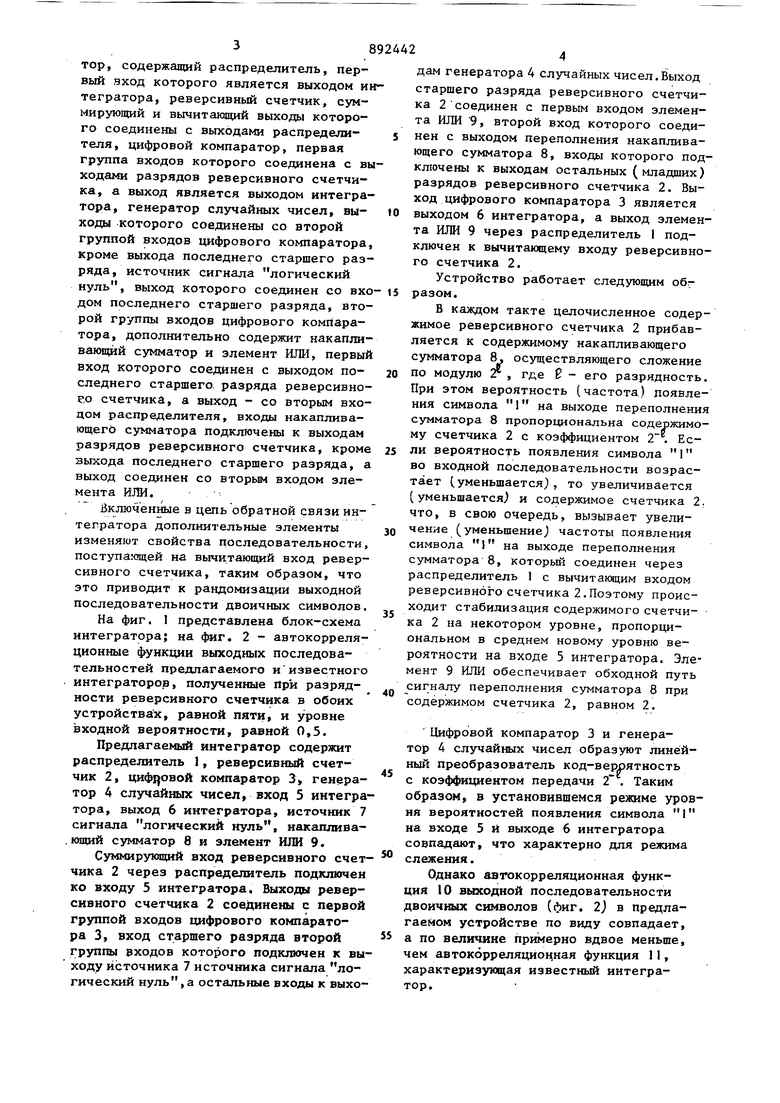

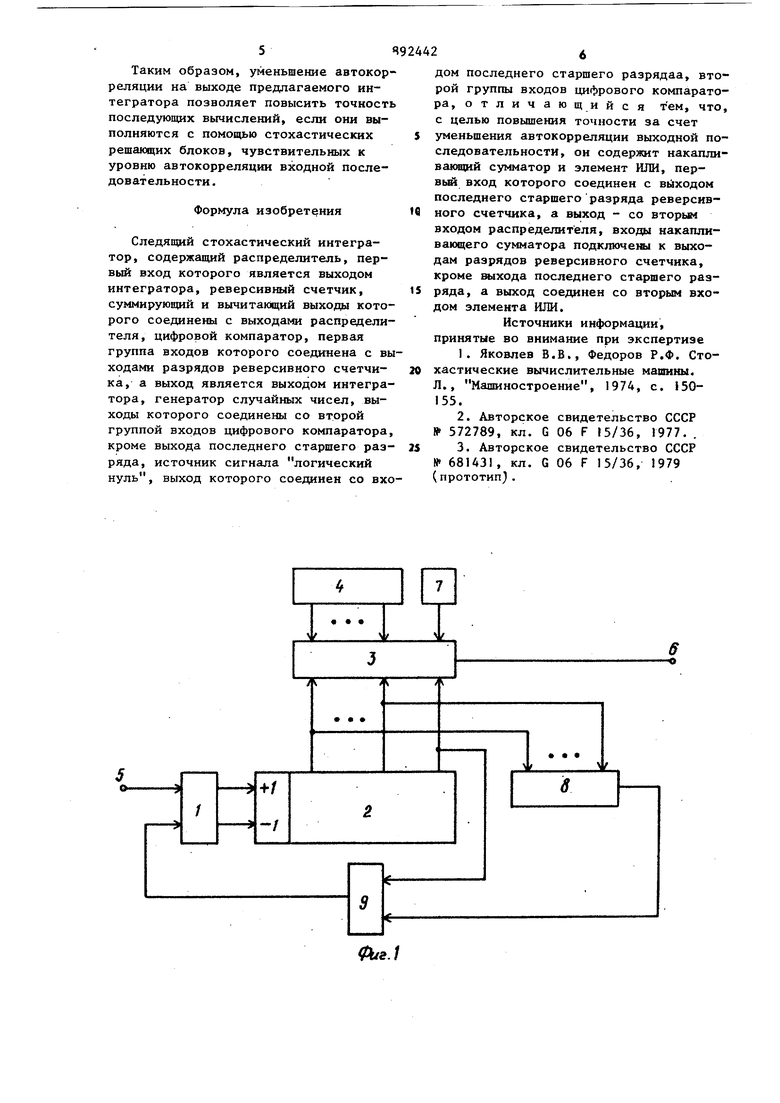

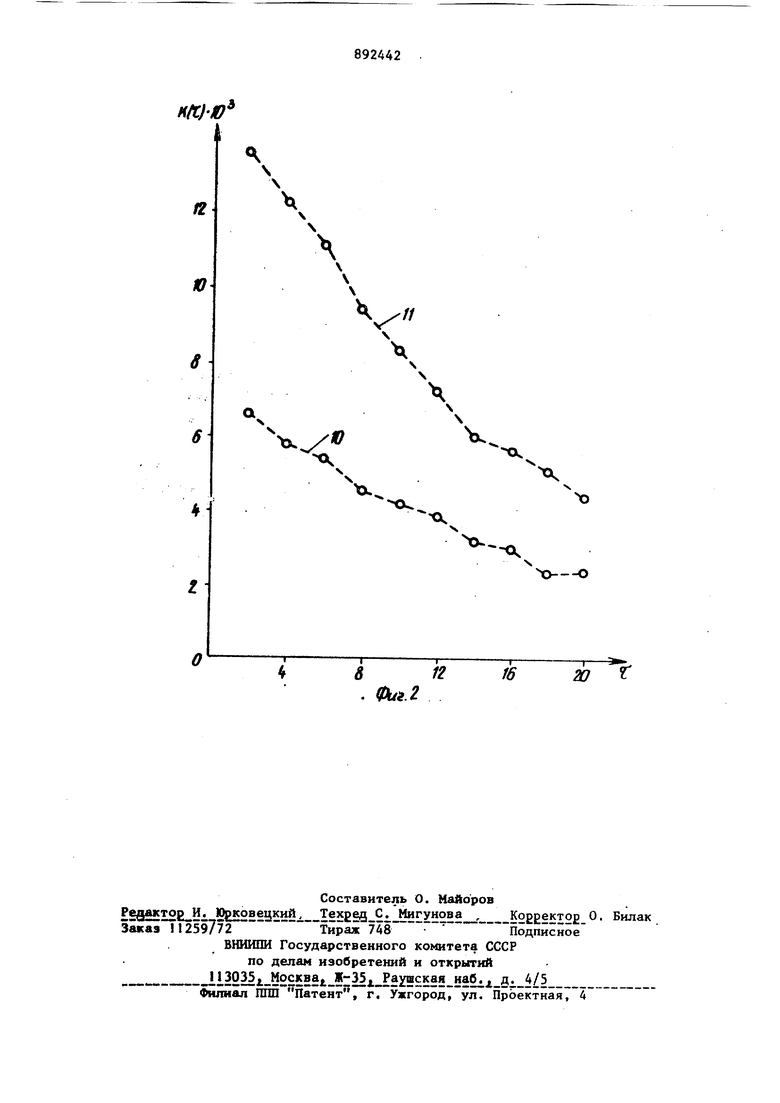

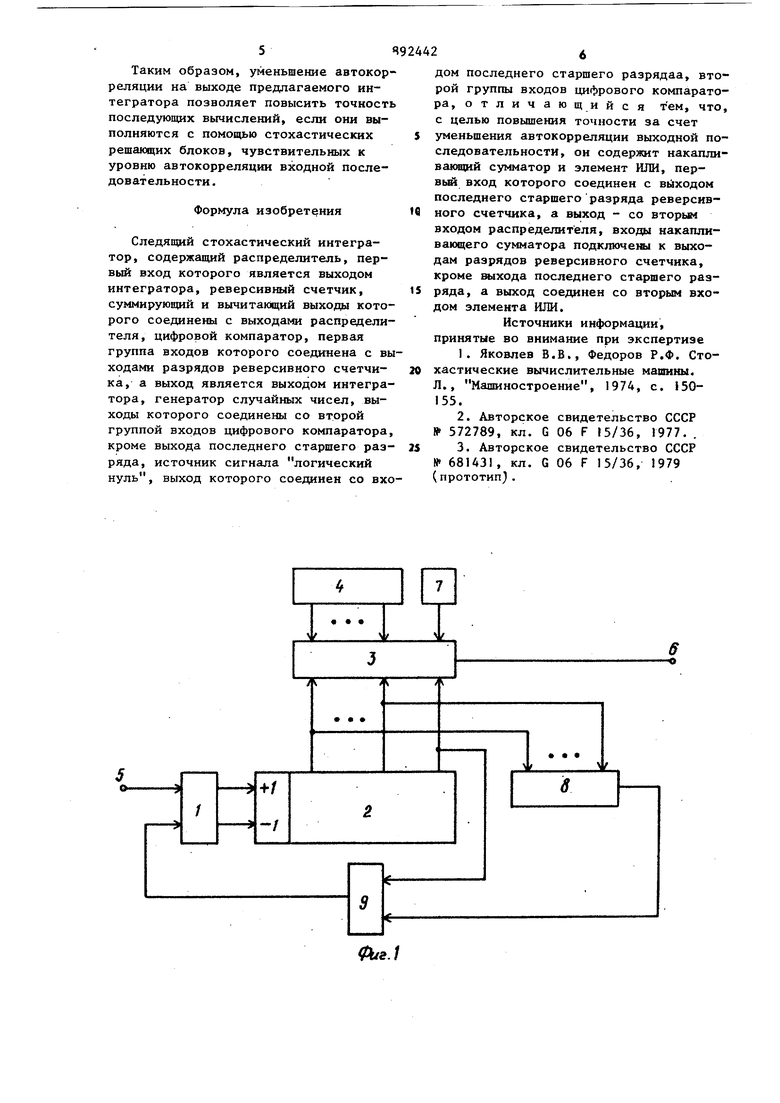

Изобретение относится к вычислительной технике и предназначено для использования в стохастических вычислительных устройствах. Известны следящие стохастические интеграторы, иcпoльзye a le для выполнения операции экспоненциального сглаживания 1 IK I2j . Однако случайные последовательности двоичных символов, генерируеьоле на выходах этих интеграторов, обладают автоко реляцией, которая служит источником при последу ющих преобразованиях выходгапс стохастических nepeMeHioiix. Наиболее близким к предлагаемому изобретению является следяв(ий стохастический интегратор, содержали блок распределения, реверсивный счет чик, генератор случайных чисел и циф ровой компаратор (блок сравнения/, 1эыход которого является выходом интегратора и через блок распределени соединен с вычитакяцим входом реверсивного счетчика, суммирующий вход которого через блок распределения подключен ко входу интегратора, а выходы соединены с первыми входами цифрового компаратора, второй вход старшего разряда компаратора подключен к выходу источника сигнала логический нуль, а вторые входы остальных разрядов - к выходам генератора случайных чисел СЗЗ. Однако наличие автокорреляции в выходной последовательности этого интегратора может привести к ошибкам при выполнении последующих вычислений с помощью стохастических преобразователей, содержащих элементы памяти, например при возведении выходной переменной интегратора в целую степень . Цель изобретения - повышение точности за счет уменьшения автокорреляции выходной последовательности. Поставленная цель достигается тем, что следящий стохастический интегратор, содержащий распределитель, первый вход которого является выходом ин тегратора, реверсивный счетчик, суммирующий и вычитающий выходы которого соединены с выходами распределителя, цифровой компаратор, первая группа входов которого соединена с вы ходами разрядов реверсивного счетчика, а выход является выходом интегратора, генератор случайных чисел, выходы которого соединены со второй группой входов цифрового компаратора, кроме выхода последнего старшего разряда, источник сигнала логический нуль, выход которого соединен со вхо дом последнего старшего разряда, второй группы входов цифрового компаратора, дополнительно содержит накапливающий сумматор и элемент ИЛИ, первый вход которого соединен с выходом последнего старшего, разряда реверсивноF,o счетчика, а выход со вторым входом распределителя, входы накапливающего сумматора подключены к выходам разрядов реверсивного счетчика, кроме выхода последнего старшего разряда, а выход соединен со вторым входом элемента ИЛИ. Включенные в цепь обратной связи интегратора дополнительные элементы изменяют свойства последовательности, поступа:ощей на вычитающий вход реверсивного счетчика, таким образом, что это приводит к рандомизации выходной последовательности двоичных символов. На фиг. 1 представлена блок-схема интегратора; на фиг 2 - автокорреляционные функции выходных последовательностей предлагаемого иизвестного интеграторов, полученные при разрядности реверсивного счетчика в обоих устройствах, равной пяти, и уровне входной вероятности, равной 0,5. Предлагаемый интегратор содержит распределитель 1, реверсивный счетчик 2, компаратор 3 генератор 4 случайных чисел, вход 5 интегра тора, выход 6 интегратора, источник 7 сигнала логический нуль, накаплива.ющий сумматор 8 и элемент ИЛИ 9. Суммирующий вход реверсивного счет чика 2 через распределитель подключен ко входу 5 интегратора. Выходы реверсивного счетчика 2 соединены с первой группой входов цифрового компаратора 3, вход старшего разряда второй группы входов которого подключен к вы ходу источника 7 источника сигнала логический нуль,а остальные входы к выходам генератора 4 случайных чисел.Выход старшего разряда реверсивного счетчика 2 соединен с первьге входом элемента ИЛИ 9, второй вход которого соединен с выходом переполнения накапливающего сумматора 8, входы которого подключены к выходам остальных (младших) разрядов реверсивного счетчика 2. Выход цифрового компаратора 3 является выходом 6 интегратора, а выход элемента ИЛИ 9 через распределитель I подключен к вычитающему входу реверсивного счетчика 2. Устройство работает следующим обг разом. В каждом такте целочисленное содержимое реверсивного счетчика 2 прибавляется к содержимому накапливающего сумматора 8, осуществляющего сложение по модулю 2 , где 0 - его разрядность. При этом вероятность (частота) появления символа 1 на выходе переполнения сумматора 8 пропорциональна содержимо - Есму счетчика 2 с коэффициентом 2 ли вероятность появления символа 1 во входной последовательности возрастает (уменьшается), то увеличивается (уменьшается) и содержимое счетчика 2. что, в свою очередь, вызывает увеличение (уменьшение) частоты появления символа 1 на выходе переполнения сумматора 8, который соединен через распределитель 1 с вычитающим входом реверсивного счетчика 2.Поэтому происходит стабилизация содержимого счетчика 2 на некотором уровне, пропорциональном в среднем новому уровню вероятности на входе 5 интегратора. Элемент 9 ИЛИ обеспечивает обходной путь сигналу переполнения сумматора 8 при содержимом счетчика 2, равном 2. Цифровой компаратор 3 и генератор 4 случайных чисел образуют линейный преобразователь код-вероятность с коэффициентом передачи 2 . Таким образом, в установившемся режиме уровня вероятностей появления символа I на входе 5 и выходе 6 интегратора совпадают, что характерно для режима слежения. Однако авгокорреляционная функция 10 выходной последовательности двоичных символов (фиг. 2) в предлагаемом устройстве по виду совпадает, а по величине примерно вдвое меньше, чем автокорреляционная функция 1I, характеризующая известный интегратор.

Таким образом, уменьшение автокорреляции на выходе предлагаемого интегратора позволяет повысить точность последующих вычислений, если они выполняются с помощью стохастических решающих блоков, чувствительных к уровню автокорреляции входной последовательности.

Формула изобретения

Следящий стохастический интегратор, содержащий распределитель, первый вход которого является выходом интегратора, реверсивный счетчик, суммирующий и вычитающий выходы которого соединены с выходами распределителя, цифровой компаратор, первая группа входов которого соединена с выходами разрядов реверсивного счетчика, а выход является выходом интегратора, генератор случайных чисел, выходы которого соединены со второй группой входов цифрового компаратора, кроме выхода последнего старшего разряда, источник сигнала логический нуль, выход которого соединен со входом последнего старшего разрядаа, второй группы входов цифрового компаратора, отличающийся тем, что, с целью повышения точности за счет

уменьшения автокорреляции выходной последовательности, он содержит накапливаютцй сумматор и элемент ИЛИ, первыя вход которого соединен с вйходом последнего старшего разряда реверсивного счетчика, а выход - со вторьм входом распределителя, входы накапливающего сумматора подключеша к выходам разрядов реверсивного счетчика, кроме выхода последнего старшего разряда, а выход соединен со вторым входом элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

Л., Машиностроение, 1974, с. 150155.

&

-о

+/

ов

(еьг./

KfCj-Ю

в

6

t

V

V.

X

-X)-о

тЭ

ю Г

12

16

Фи.г

Авторы

Даты

1981-12-23—Публикация

1980-05-05—Подача