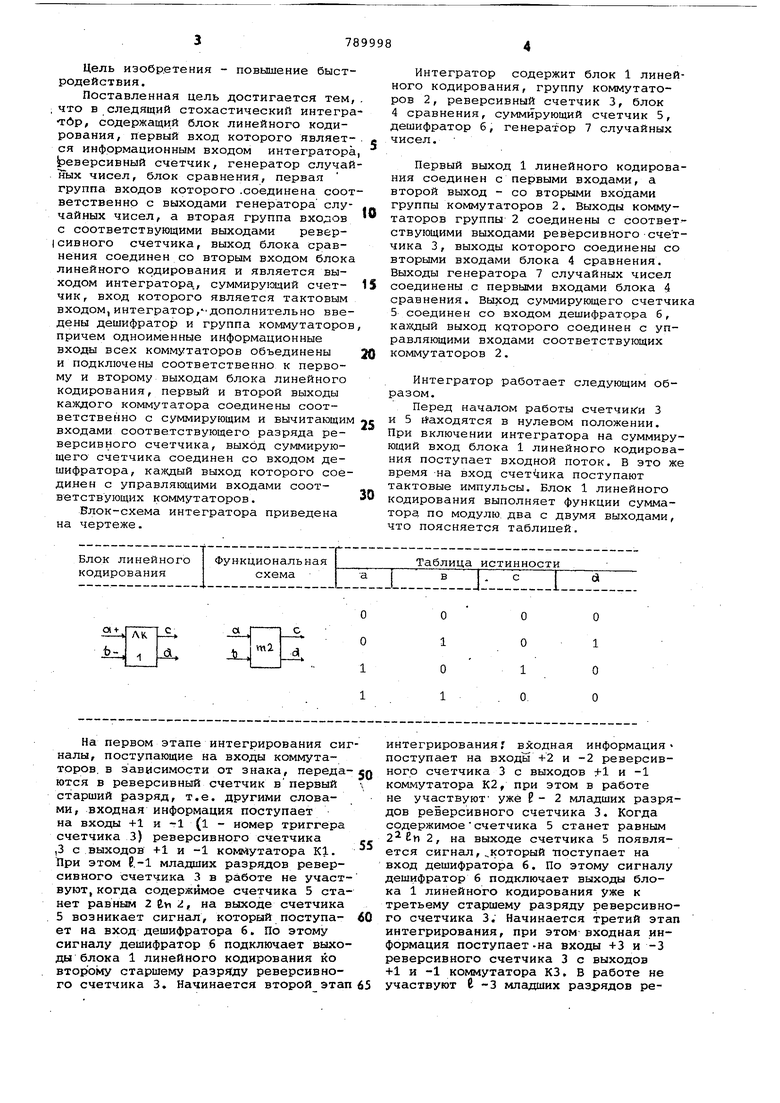

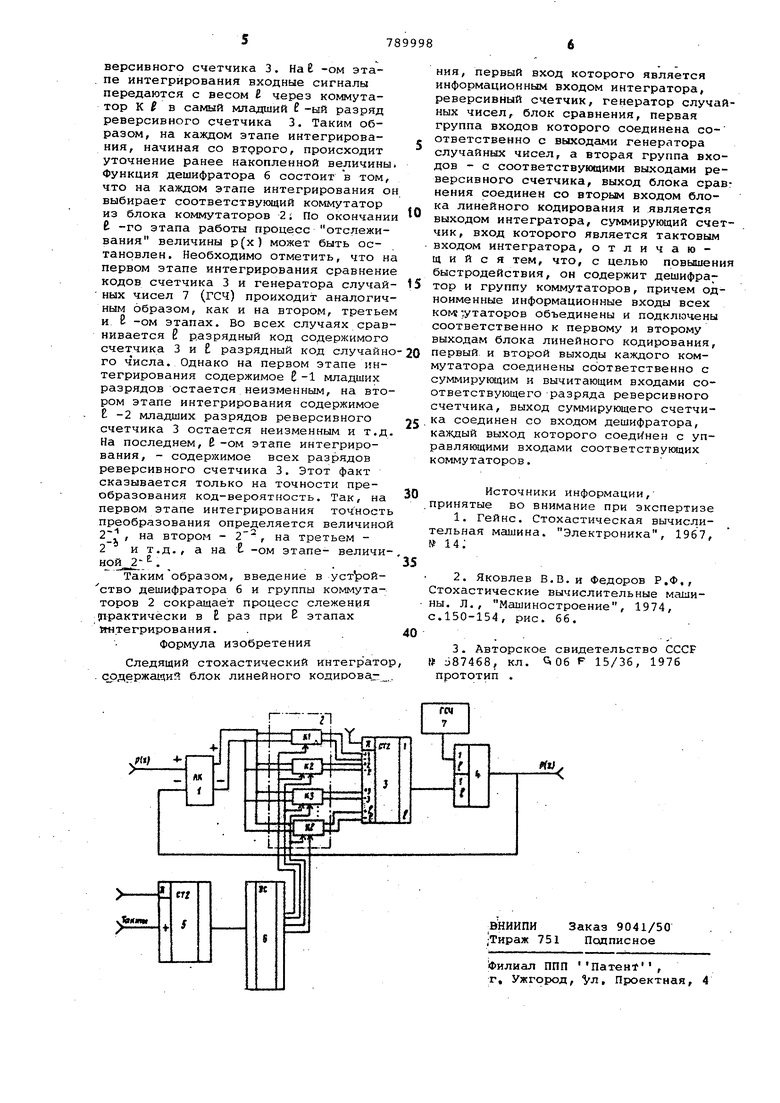

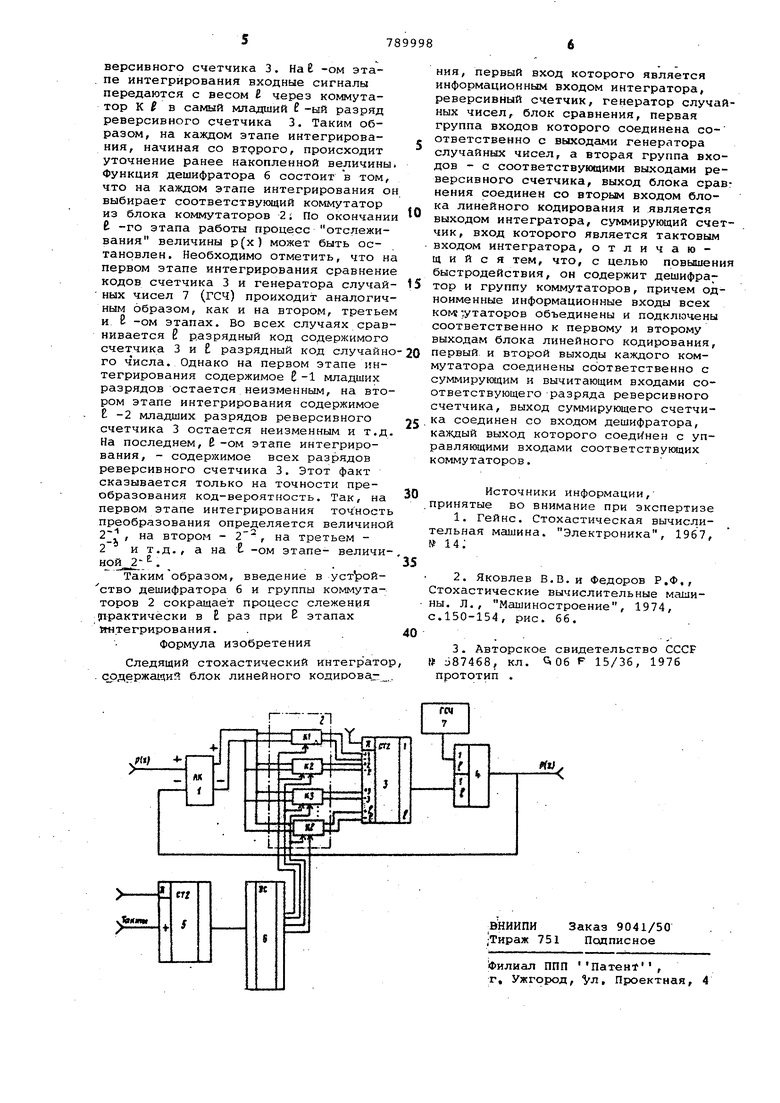

Изобретение относится к вычислительной технике и может быть исполь зовано в качестве одного из основных многофункциональных узлов в стохаст ческих вычислительных машинах. Известны стохастические следящие интеграторы, .содержащие последовател но соединенные счетчик; схему сравнения, генератор случайных чисел, входы и выходы которых связаны 100%обратной связью l . Основными недостатками таких интеграторов являются сложность и невысокое быстродействие. Известен также следящий стохастический интергратор,содержащий блок линейного кодирования, первый вход которого соединен с информационным входом интегратора и последовательно соединенные реверсивный счетчик, схему сравнения и генератор случайных чисел, выходы разрядов которого соединены с первыми входами одноиме ных разрядов схемы сравнения, вторы -входы которых соединены с выходами одноименных разрядов реверсивного счетчика, выход схемы сравнения сое динен со вторым входом блока линейного кодирования и выходом интеграто ра f2j. Основным недостатком этого интегратора является ограниченное быстродействие. Наиболее близким по технической сущности является следящий стохастический интегратор, содержащий блок линейного кодирования, блок-реверсивный счетчик,блок сравнения,генератор случайных чисел, суммирующий счетчик и коммутатор, первый и второй информационные входы которого соединены соответственно с первым и вторым входами блока линейного кодирования, первый и второй выходы коммутатора соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика, а третий и.четвертый выходы соединены соответственно с суммиРУ1СНДИМ и вычитающим входами половины старших разрядов реверсивного счетчика, при этом вход суммирующего счетчика соединен с тактовым входом интегратора, а выход - с управляющим входом коммутатора, Работа этого интегратора для достижения заданной точности при уменьшенном числе тактов интегрирования посредством счетчика и коммутатора организуется в два этапа 1з1. Его недостаток - .ограниченное быстродействие. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, .что в следящий стохастический интегра тбр, содержащий блок линейного кодирования, первый вход которого является информационным входом интегратора реверсивный счетчик, генератор случай ных чисел, блок сравнения, первая группа входов которого .соединена соот ветственно с выходами генератора случайных чисел, а вторая группа вхо;аов с соответствующими выходами ревер1СИВНОГО счетчика, выход блока сравнения соединен со вторым входом блока линейного кодирования и является выходом интегратора., суммирующий счетчик, вход которого является тактовым ВХОДОМ)интегратор,дополнительно введены дешифратор и группа коммутаторов причем одноименные информационные входы всех коммутаторов объединены и подключены соответственно к первому и второму выходам блока линейного кодирования, первый и второй выходы каждого коммутатора соединены соответственно с суммирующим и вычитающим входами соответствующего разряда реверсивного счетчика, выход суммирующего счетчика соединен со входом дешифратора, каждый выход которого соединен с управляющими входами соответствующих коммутаторов. Влок-схема интегратора приведена на чертеже. Интегратор содержит блок 1 линейного кодирования, группу коммутаторов 2, реверсивный счетчик 3, блок 4сравнения, суммирующий счетчик 5, дешифратор 6, генератор 7 случайных чисел, Первый выход 1 линейного кодирования соединен с первыми входами, а второй выход - со вторыми входами группы коммутаторов 2. Выходы коммутаторов группы 2 соединены с соответствующими выходами реверсивного счетчика 3, выходы которого соединены со вторыми входами блока 4 сравнения. Выходы генератора 7 случайных чисел соединены с первыми входами блока 4 сравнения. Выход суммирующего счетчика 5соединен со входом дешифратора 6, каждый выход которого соединен с управляющими входами соответствующих коммутаторов 2. Интегратор работает следующим образом. Перед началом работы счетчики 3 и 5 (Находятся в нулевом положении. При включении интегратора на суммирующий вход блока 1 линейного кодирования поступает входной поток. В это же время -на вход счетчика поступают тактовые импульсы. Блок 1 линейного кодирования выполняет функции сумматора по модулю два с двумя выходами, что поясняется таблицей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий стохастический интегратор | 1982 |

|

SU1061141A1 |

| Следящий стохастический интегратор | 1990 |

|

SU1728868A1 |

| Следящий стохастический интегратор | 1977 |

|

SU681431A1 |

| Следящий стохастический интегратор | 1980 |

|

SU892442A1 |

| Стохастический интегратор | 1978 |

|

SU744607A1 |

| Устройство для моделирования нейрона | 1989 |

|

SU1709356A1 |

| Стохастический интегратор | 1980 |

|

SU942017A1 |

| СТОХАСТИЧЕСКИЙ ИНТЕГРАТОР | 1972 |

|

SU428411A1 |

| Вероятностный интегратор | 1980 |

|

SU900283A1 |

| Вероятностное устройство для извлечения корня | 1981 |

|

SU962937A1 |

На первом этапе интегрирования сиг налы, поступающие на входы коммутаторов, в зависимости от знака, передаются в реверсивный счетчик в первый старший разряд, т.е. другими словами, входная информация поступает на входы +1 и -1 (1 - номер триггера счетчика 3) реверсивного счетчика ,3 с выходов +1 и -1 коммутатора К1. При этом .- младших разрядов реверсивного счетчика 3 в работе не участвуют, когда содержимое счетчика 5 станет равным 2 ftvi i, на выходе счетчика 5 возникает сигнал, который поступает на вход дешифратора б. По этому сигналу дешифратор 6 подключает выходы блока 1 линейного кодирования ко второму старшему разряду реверсивного счетчика 3, Начинается второй этап интегрирования входная информация поступает на входы +2 и -2 реверсивного счетчика 3 с выходов i-1 и -1 коммутатора К2, при этом в работе не участвуют уже Р - 2 младших разрядов реверсивного счетчика 3. Когда содержимоесчетчика 5 станет равным 2, на выходе счетчика 5 появляется сигнал, который -поступает на вход дешифратора 6. По этому сигналу дешифратор 6 подключает выходы блока 1 линейного кодирования уже к третьему старшему разряду реверсивного счетчика 3. Начинается третий этап интегрирования, при этом- входная информация поступает -на входы +3 и -3 реверсивного счетчика 3 с выходов +1 и -1 коммутатора КЗ, В работе не участвуют Е -3 младших разрядов ре

Авторы

Даты

1980-12-23—Публикация

1979-01-04—Подача