(Б) УСТРОЙСТВО для УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДОМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для систем управления вентильными электроприводами | 1977 |

|

SU746598A1 |

| Способ управления вентильным преобразователем | 1980 |

|

SU955506A1 |

| Устройство для вычисления параметров управления вентильным преобразователем | 1980 |

|

SU949761A1 |

| Вентильный электропривод постоянного тока | 1985 |

|

SU1372567A1 |

| Устройство для управления вентильным преобразователем | 1979 |

|

SU786817A1 |

| Устройство для управления электродвигателем постоянного тока | 1977 |

|

SU928579A1 |

| Устройство для управления вентильнымпРЕОбРАзОВАТЕлЕМ | 1979 |

|

SU824397A1 |

| Устройство для управления вентильным преобразователем | 1981 |

|

SU987779A1 |

| Дифференцирующее устройство | 1980 |

|

SU888141A1 |

| Устройство для измерения параметровВЕНТильНОгО пРЕОбРАзОВАТЕля | 1979 |

|

SU838943A1 |

t

Изобретение относится к электротехнике и может быть использовано в различных высокоточных и быстродействующих системах управления вентильным электроприводом постоянного тока..

Известно введение в контур регулирования замкнутых систем управления устройства, формирукхцего одновременно сигналы,пропорциональные ошибке регулирования, интегралу от этой ошибки и ее производной. Такие устройства получили название ПИД - регулиторы 111.

Известно вычислительное устройство для определения соотношений между частотными сигналами для получения сигналов в виде аналоговых необходимых при построении высокоточных и быстродействующих приводов. . Это устройство предназначено для работы в частотнофазовой системе с усилителем мощности,управляемым от широтно-импульсного модулятора 12.

В случае использования вентильного преобразователя в качестве усилителя мощности это устройство не может быть непосредственно использовано в вентильном электроприводе, где частота питающей сети вентильного преобразователя не совпадает с частотой определения фазового сдвига и существенно ниже ее,Vпоэтому определение текущего значения (шибки регулирования или

to дефференциала от ошибки нецелесообразно. Так, например, в быстродействующем ве;нтильном электроприводе с малоинерционными двигателями при большом диапазоне регулирования скорости в

ts зоне малых скоростей наблюдаются пульсации скорости с частотой коммутации вентилей вплоть до 100 и даже шаговый режим движения.

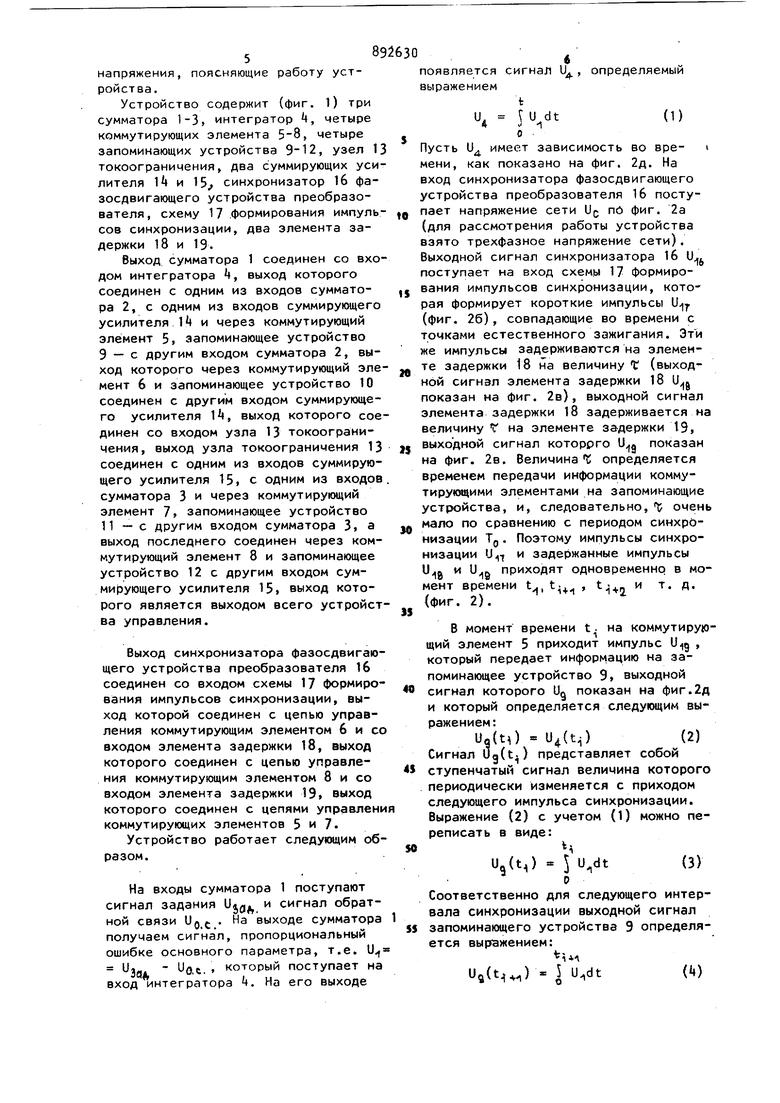

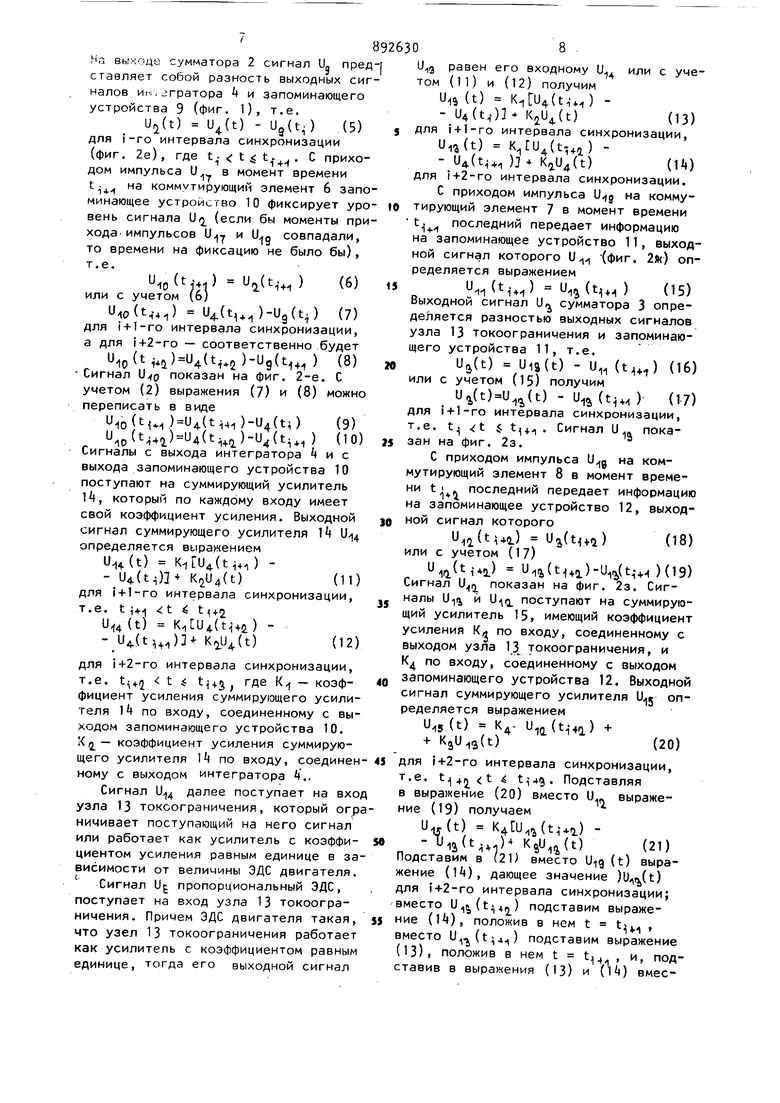

При наличии пульсаций скорости

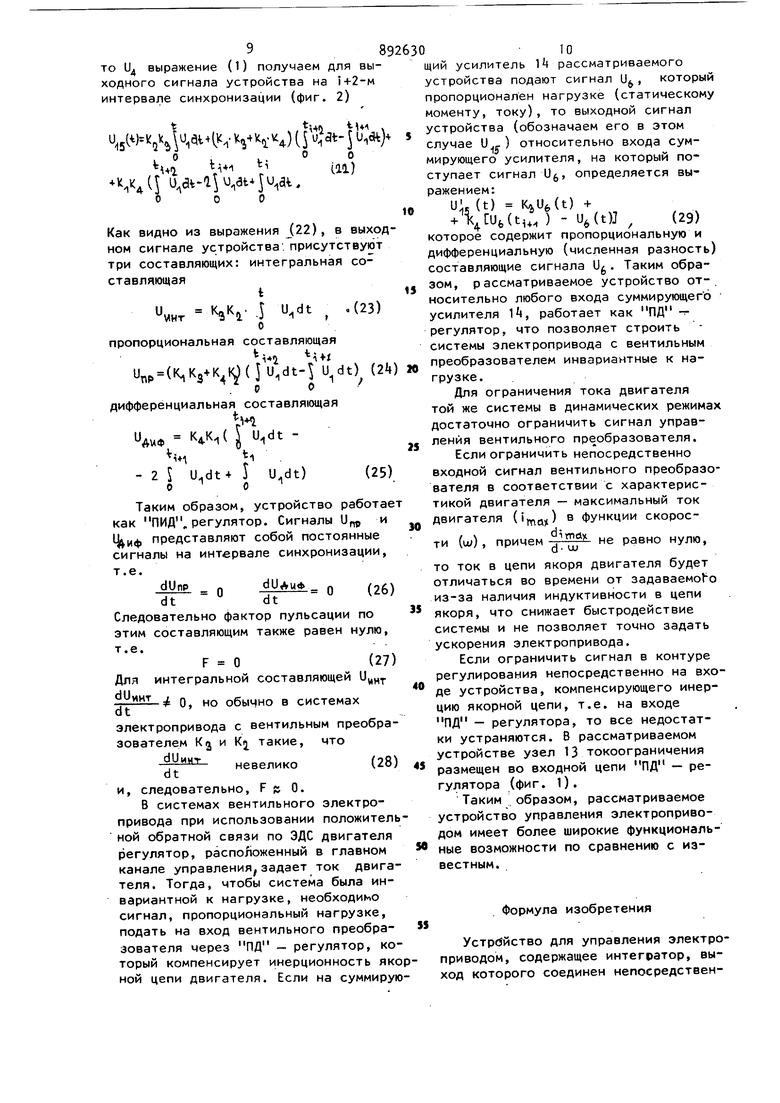

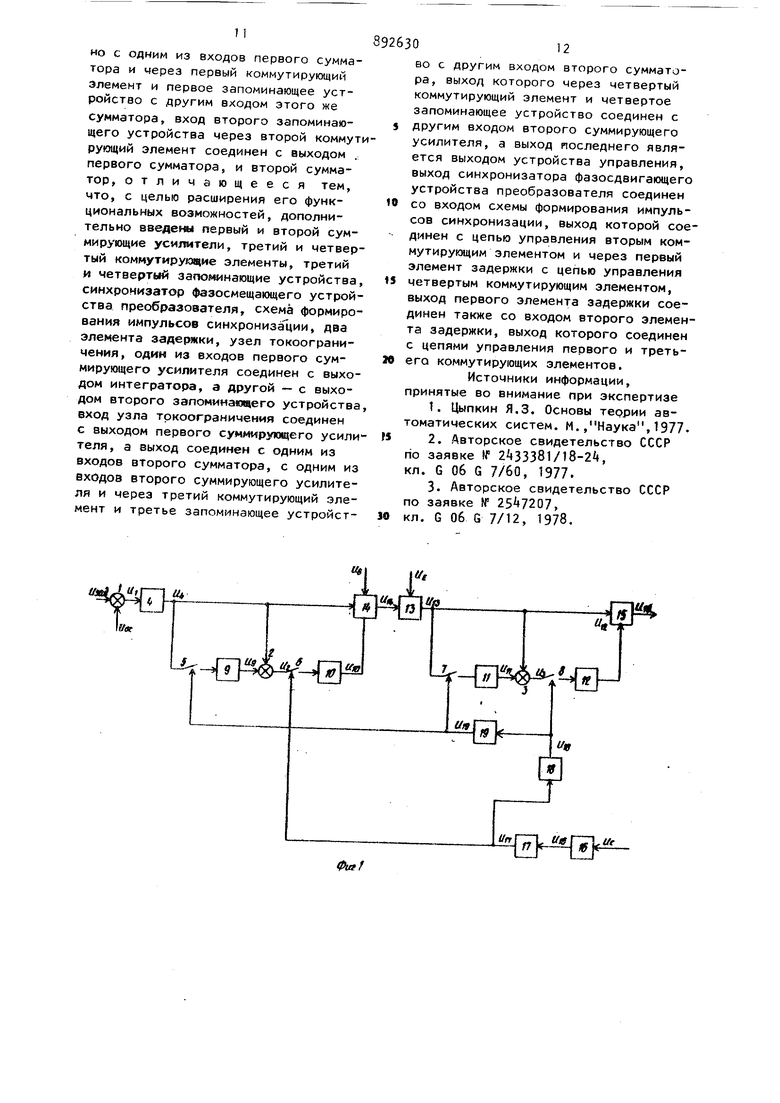

20 внутри интервала вентильности теряется однозначное соответствие между сигналом задания скорости в момент включения очередного вентиля и текущими значениями скорости внутри интервала вентильности. В этом случае бли кие к мгновенным знамениям ошибки ил ее производной не могут быть использованы непосредственно для управлени приводом. Наиболее близким техническим реше нием является устройство, содержащее интегратор, выход которого соединен с одним из входов первого сумматора и через первый коммутирующий элемент и первое запоминающее устройство с другим входом этого же сумматора, вход второго запоминающего устройства через второй коммутирующий элемент соединен с выходом первого сумматора, и второй сумматор 3. Однако это устройство обладает не достатками усложняющими его реализацию в качестве ПИД - регулятора в системе вентильного электропривода с высоким быстродействием. В динамических режимах, когда интервал вентильности значительно отличается от величины т 2JF о - т- uut где m - пульсность силовой схемы ии - круговая частота сети. В усредненных значениях пропорциональной и дифференциальной составляю щих выходного сигнала устройства появляется неучитываемая ошибка (импульсы управления используются в качестве синхронизирующих), которую за ранее предусмотреть и учесть с помощью существующих инженерных методов очень трудно. Если импульсы синхронизации не связаны с импульсами управления, а например, с точками естественного зажигания, то в этих точках пропорциональная и дифференциальная составляющие выходного сигнала устройства не будут иметь ошибки, но импульсы управления вентильным преобразователем приходят в другие моменты времени (между импульсам синхронизации) в эти моменты времени выходной сигнал устройства еще не содержит правильной информации о про порциональной и дифференциальной составляющих и, следовательно, появляется неучитываемая ошибка. Если бы в этом случае пропорциональная и дифференциальная составляю щие были верны, то, так как интервал синхронизации постоянный, расчет можно внести известным инженерным ме 0 тодом, Z - преобразования учитыйая переменное запаздывание импульса управления относительно импульса синхронизации. Данное устройство не устраняет фактора пульсаций, хотя и уменьшает его влияние. Структура устройства не позволяет использовать его при построении систем электропривода инвариантных к нагрузке, располагать узел токоограничения таким оптимальным образом, чтобы задавать более точно ускорение электропривода в динамических режимах. Цель изобретения - расширение функциональной возможности устройства. Поставленная цель достигается тем, что в него дополнительно введены первый и второй суммирующие усилители, третий и четвертый коммутирующие элементы, третий и четвертый запоминающие устройства, синхронизатор фазосдвигающего устройства преобразователя, схема формирования импульсов синхронизации, два элемента задержки, узел токоограничения, один из входов первого суммирующего усилителя соединен с выходом интегратора, а другой - с выходом второго запоминающего устройства, вход узла токоограничения соединен с выходом первого суммирующего усилителя, а выход соединен с одним из входов второго сумматора, и через третий коммутирующий элемент и третье запоминающее устройство с другим входом второго сумматора, выход которого через четвертый коммутирующий элемент и четвертое запоминающее устройство соединен с другим входом второго суммирующего усилителя, а выход последнего является выходом устройства управления, выход синхронизатора фазосдвигающего устройства, преобразователя соединен со входом схемы формирования импульсов синхронизации, выход которой соединен с цепью управления вторым коммутирующим элементом и через первый элемент задержки с цепью управления четвертым коммутирующим элементом, выход первого элемента задержки соединен также со входом второго элемента задержки, выход которого соединен с цепями управления первого и третьего коммутирующих элементов. На фиг. 1 изображена структурная схема устройства; на фиг. 2 - эпюры напряжения, поясняющие работу устройства. Устройство содержит (фиг. 1) три сумматора 1-3, интегратор 4, четыре коммутирующих элемента 5-8, четыре запоминающих устройства , узел 1 токоограничения, два суммирующих уси лителя I и 15 синхронизатор 16 фазосдвигающего устройства преобразователя, схему 17 .формирования импуль сов синхронизации, два элемента задержки 18 и 19. Выход сумматора 1 соединен со вхо дом интегратора , выход которого соединен с одним из входов сумматора 2, с одним из входов суммирующего усилителя I и через коммутирующий элемент S, запоминающее устройство 9 - с другим входом сумматора 2, выход которого через коммутирующий эле мент 6 и запоминающее устройство 10 соединен с другим входом суммирующего усилителя 1 , выход которого сое динен со входом узла 13 токоограничения, выход узла токоограничения 13 соединен с одним из входов суммирующего усилителя 15, с одним из входов сумматора 3 и через коммутирующий элемент 7, запоминающее устройство 11 - с другим входом сумматора 3, а выход последнего соединен через коммутирующий элемент 8 и запоминающее устройство 12 с другим входом сумми 5ующего усилителя 15, выход которого является выходом всего устройст ва управления. Выход синхронизатора фазосдвигающего устройства преобразователя 16 соединен со входом схемы 17 формирования импульсов синхронизации, выход которой соединен с цепью управления коммутирующим элементом 6 и со входом элемента задержки 18, выход которого соединен с цепью управления коммутирующим элементом 8 и со входом элемента задержки 19, выход которого соединен с цепями управлени коммутирующих элементов 5 и 7. Устройство работает следукяцим образом. На входы сумматора 1 поступают сигнал задания Ujg и сигнал обратной связи UQ . На выходе сумматора получаем сигнал, пропорциональный ошибке основного параметра, т.е. U Ujg - Uo,t, , который поступает на вход интегратора . На его выходе 8 появляется сигнал Ц, определяемый выражением и dt Пусть U имеет зависимость во врепени, как показано на фиг. 2д. На вход синхронизатора фазосдвигающего устройства преобразователя 16 поступает напряжение сети U(; пи фиг. 2а (для рассмотрения работы устройства взято трехфазное напряжение сети). Выходной сигнал синхронизатора 16 0.. поступает на вход схемы 17 формирования импульсов синхронизации, которая формирует короткие импульсы U (фиг. 26), совпадающие во времени с точками естественного зажигания. Эти же импульсы задерживаются на элементе задержки 18 на величину t (выходной сигнал элемента задержки 18 U, показан на фиг. 2в), выходной сигнал элемента задержки 18 задерживается на величину V на элементе задержки 19, выходной сигнал которрго U показан на фиг. 2в. Величинам определяется временем передачи информации коммутирукедими элементами на запоминающие устройства, и, следовательно, очень мало по сравнению с периодом синхронизации Тд. Поэтому импульсы синхронизации и задержанные импульсы 4 Ч.ц приходят одновременно в Ut мент времени (фиг. 2). в момент времени t. на коммутирующий элемент 5 приходит импульс , который передает информацию на запоминающее устройство 9, выходной сигнал которого Un показан на фиг.2д и который определяется следующим выражением:Ua(tO U(t)(2) Сигнал Ug(t) представляет собой ступенчатый сигнал величина которого периодически изменяется с приходом следующего импульса синхронизации. Выражение (2) с учетом (1) можно переписать в виде: ti u(t) 5 (3) Соответственно для следующего интервала синхронизации выходной сигнал запоминающего устройства 9 определяется вырпажением: Ua(t.,) « u,dt 8 На выходе сумматора 2 сигнал Ug пред ставляет собой разность выходных СИ1- налов И)-г ; гратора и запоминающего устройства 9 (фиг. 1), т.е. U(t) U(t) - Ug(t.) (5) для i-го интервала синхронизации (фиг. 2е), где t. t t . С приходом импульса и в момент времени 14.1 коммутирующий элемент 6 запо минающее устройство 10 фиксирует уро вень сигнала UQ (если бы моменты при хода-импульсов U и совпадали, то времени на фиксацию не было бы), и..) U.(t.,, ) ЧО или с учетом (6) (t,-,,) и4.(1,)-ид(ц) (7) для i+1-го интервала синхронизации, а для i+2-го - соответственно будет ()U4()-U9(tH, ) (8) Сигнал показан на фиг. 2-е. С учетом (2) выражения (7) и (8) можно переписать в виде (t,)U4()-U4(tO (9) (ti4a)-U4(Ц ) (ю) -ц/ .| -тI Сигналы с выхода интегратора ч и с выхода запоминающего устройства 10 поступают на суммирующий, усилитель 14, который по каждому входу имеет свой коэффициент усиления. Выходной сигнал суммирующего усилителя И U/ определяется выражением U.,4.(t) KirU4(ti4 ) -U4.(ti)J+ (t)(11) для i+1-го интервала синхронизации, т.е. t j.. t (t) K,U4(ti+) -U( K/i.U4.(t) (12) для i+2-го интервала синхронизации, т.е. t , где К., - коэффициент усиления суммирующего усилителя 1 по входу, соединенному с выходом запоминающего устройства 10. К2 - коэффициент усиления суммирующего усилителя k по входу, соединенному с выходом интегратора ,, Сигнал далее поступает на вход узла 13 токсограничения, который огра ничивает поступающий на него сигнал или работает как усилитель с коэффициентом усиления равным единице в зависимости от величины ЭДС двигателя. Сигнал Ug пропорциональный ЭДС, поступает на вход узла 13 токоограничения. Причем ЭДС двигателя такая, что узел 13 токоограничения работает как усилитель с коэффициентом равным единице, тогда его выходной сигнал 08 равен его входному U, или с учетом (11) и (12) получим (t) Кх, U4.(ti4-t ) (t,.)b KjU(t)(13) для i+1-го интервала синхронизации, Ui(t) ) (t, )J+ M4(t) (Й) для i+2-го интервала синхронизации. С приходом импульса на коммутирующий элемент 7 в момент времени t. последний передает информацию на запоминающее устройство 11, выходной сигнал которого , (фиг. 2л) определяется выражением и,, (t,4i) и,(Цн ) (15) Выходной сигнал U,j сумматора 3 определяется разностью выходных сигналов узла 13 токоограничения и запоминающего устройства 11, т.е. U5(t) Ui3(t) - U () (16) или с учетом (15) получим U4(t)U(t) - и,а (, ) (17) для i+1-го интервала синхронизации. Сигнал и „ покат.е. t. t {ft зан на фиг. 2з. С приходом импульса на коммутирующий элемент 8 в момент времени tjj. последний передает информацию на запоминающее устройство 12, выходНОИ сигнал которого U(t(l.) U5(tf+(i) или с учетом (17) u,a() (Ч4г)-Мци )(19) Сигнал показан на фиг. 2з. Си1- налы и U(j поступают на суммирующий усилитель 15, имеющий коэффициент усиления Кд по входу, соединенному с выходом узла Ц токоограничения, и К по входу, соединенному с выходом запоминающего устройства 12. Выходной сигнал суммирующего усилителя Ц определяется выражением U.5(t) КА- Uia(ti4i) + i; и - - ., . для i+2-го интервала синхронизации, т.е. Н5 Подставляя в выражение (20) вместо U выражение (19) получаем () () - U-,j (t ;) (t) (21) Подставим в (21) вместо (t) выражение (Н), дающее значение )U,(a(t) ля i+2-го интервала синхронизации; вместо и ((2) подставим выраже ие (И), положив в нем t t;j. , вместо U(t;i4) подставим выражение (13), положив в нем t 1; , и, подтавив в выражения (13) и (14) вместо ид выражение (1) получаем для выходного сигнала устройства на i+2-м интервале синхронизации (фиг. 2) ) ( и V ° V и ua i ЧЧ ., о 00 Как видно из выражения (22), в выход ном сигнале устройства присутствуют три составляющих: интегральная составляющаяЧЧ I пропорциональная составляющая ) (2k О О дифференциальная составляющая -АМФ ,( I U,dt Jl . - 2 I U.dt4 U.dt) (25 Таким образом, устройство работа как ПИД, регулятор. Сигналы 0 и l,ф представляют собой постоянные сигналы на интервале синхронизации, т.е. dUnP „ dUAu dt dt Следовательно фактор пульсации по этим составляющим также равен нулю, т.е. F О(27 Для интегральной составляющей U, .: 4 О, но обычно в системах электропривода с вентильным преобра зователем Кд и Kj такие, что dUMHT невелико следовательно, F 0. В системах вентильного электропривода при использовании положител ной обратной связи по ЭДС двигателя регулятор, расположенный в главном канале управления задает ток двига теля. Тогда, чтобы система была инвариантной к нагрузке, необходимо сигнал, пропорциональный нагрузке, подать на вход вентильного преобразователя через ПД - регулятор, ко торый компенсирует инерционность як ной цепи двигателя. Если на суммиру 8 10 щий усилитель 14 рассматриваемого устройства подают сигнал U, который пропорционален нагрузке (статическому моменту, току), то выходной сигнал устройства (обозначаем его в этом случае U, ) относительно входа суммирующего усилителя, на который поступает сигнал и, определяется выражением:и (t) ) + + Ufc(tu. ) - U(t)J , (29) которое содержит пропорциональную и дифференциальную (численная разность) составляющие сигнала U. Таким образом, рассматриваемое устройство относительно любого входа суммирующег6 усилителя 1, работает как ПД -:регулятор, что позволяет строить системы электропривода с вентильным преобразователем инвариантные к нагрузке. Для ограничения тока двигателя той же системы в динамических режимах достаточно ограничить сигнал управления вентильного преобразователя. Если ограничить непосредственно входной сигнал вентильного преобразователя в соответствии с характеристикой двигателя - максимальный ток двигателя () функции скоросmanти (ш), причем -j: не равно нулю, то ток в цепи якоря двигателя будет отличаться во времени от зaдaвaeмo o из-за наличия индуктивности в цепи якоря, что снижает быстродействие системы и не позволяет точно задать ускорения электропривода. Если ограничить сигнал в контуре регулирования непосредственно на входе устройства, компенсирующего инерцию якорной цепи, т.е. на входе ПД - регулятора, то все недостатки устраняются. В рассматриваемом устройстве узел 13 токоограничения размещен во входной цепи ПД - регулятора (фиг. 1). Таким образом, рассматриваемое устройство управления электроприводом имеет более широкие функциональные возможности по сравнению с известным. Формула изобретения Устройство для управления электроприводом, содержащее интегратор, выход которого соединен непосредственно с одним из входов первого сумматора и через первый коммутирующий элемент и первое запоминающее устройство с другим входом этого же сумматора, вход второго запоминающего устройства через второй коммути рующий элемент соединен с выходом . первого сумматора, и второй сумматор, отличающееся тем, что, с целью расширения его функциональных возможностей, дополнительно ввея&ны первый и второй суммируищие усилители, третий и четвертый коммутирукадие элементы, третий и четвертый запоминающие устройства, синхронизатор фазосмещающего устройства преобразователя, схема формирования импульсов синхронизаЧ ии, два элемента задержки, узел токоограничения, один из входов первого суммирующего усилителя соединен с выходом интегратора, а другой - с выходом второго запоминающего устройства вход узла тркоограничения соединен с выходом первого суммирующего усили теля, а выход соединен с одним из входов второго сумматора, с одним из входов второго суммирующего усилителя и через третий коммутирующий элемент и третье запоминающее устройстWot

1 Г -

0

U

ив

Urr 0 во с другим входом второго сумматора, выход которого через четвертый коммутирующий элемент и четвертое запоминающее устройство соединен с другим входом второго суммирующего усилителя, а выход последнего является выходом устройства управления, выход синхронизатора фазосдвигающего устройства преобразователя соединен со входом схемы формирования импульсов синхронизации, выход которой соединен с цепью управления вторым коммутирующим элементом и через первый элемент задержки с цепью управления четвертым коммутирующим элементом, выход первого элемента задержки соединен также со входом второго элемента задержки, выход которого соединен с цепями управления первого и третьего коммутирующих элементов. Источники информации, принятые во внимание при экспертизе 1. Цыпкин Я.З. Основы теории автоматических систем. М.,Наука,1977. 2. Авторское свидетельство СССР по заявке № 2it3338l/l8-24, кл. G Об G 7/60, 1977. 3. Авторское свидетельство СССР по заявке W , кл. G 06 G 7/12, 1978,

Авторы

Даты

1981-12-23—Публикация

1980-04-11—Подача