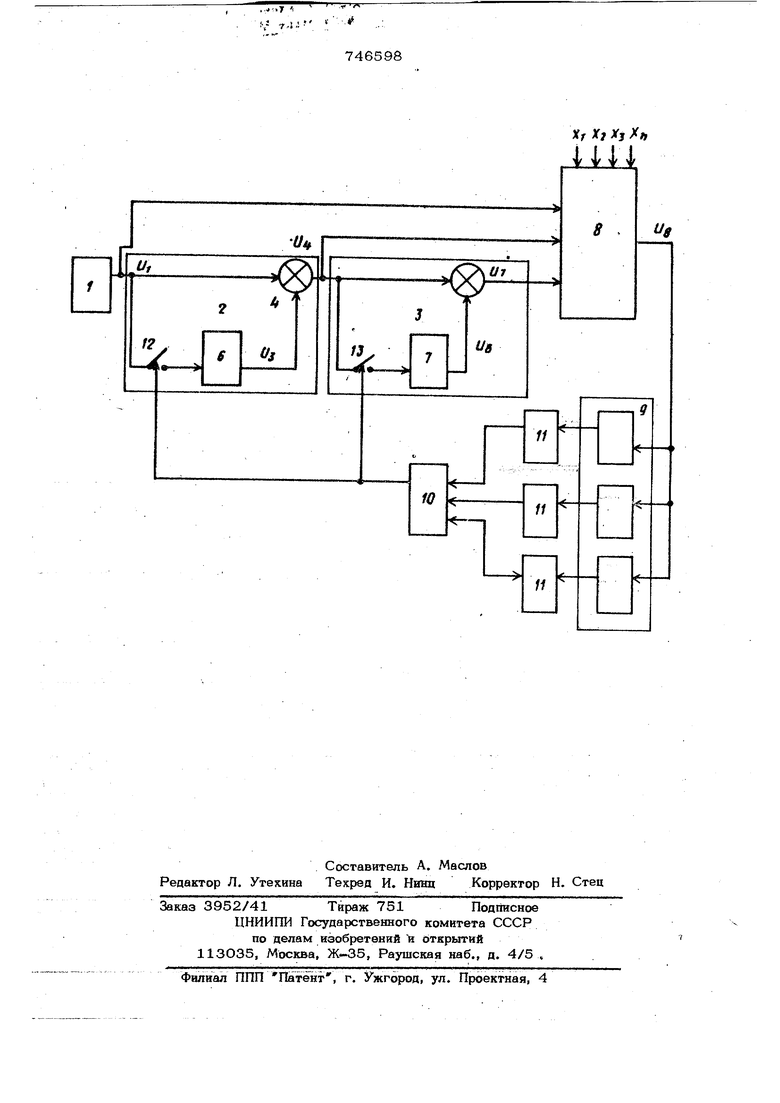

Изобретение относится к области автоматики и вычислительной техники и уложат быть использовано в различнык высокоточных и быстродействующих системах управления, например , вентильными электроприводами (регуляторами положения скорости (частоты), соотношения скоростей (частот)). В системах такого типа в качестве усилителей мощности могут быть использо ваны как высокочастотные, полностью управляемые усилители мощности так и вентильные преобразователи различного типа, вентильные двигатели ll. Недостаток таких устройств заключается в разрывном характере интегральной составляющей от ошибки в заданной зоне фазового сдвига. Наиболее близким техническим решением к изобретению является вычислительное устройство для систем управления вентильными электропроводами (ВП) содержащее последовательно включенные блоки формирования интегральной ошибки формирования ошибки и дифференциала ошибки, выходы которых подключены к соответствующим входам ВП, подсоединенного выходом к трем входам блока импульсно-фазового управления 2. Недостатком прототипа является невозможность непосредственного использования, например, для управления различными вентильными системами регулирования, т. е. для случаев, когда выработ ка конечных дискретных команд на управление силовым элементом происходит несинхронно с входным устройством, дающим текущую, близкую к мгновенным значениям, информацию об ошибке по основному параметру и ее дифференциалу. Целью изобретения является повышение точности работы устройства за счет синхронизации вычислений с работой силового узла электропривода. Поставленная цель достигается тем, что предложенное устройство содержит три формирователя коротких импульсов и элемент ИЛИ, выход которого подключен к управляющим входам блоков формирова ния ошибки и дифференциала ошибки, а тр вкода подсоединены к выходам соответствующих формирователей коротких импульсов, подключенных входами к трем выходам блока импульсного фазового управления, а также тем, что в нем кажды блок формироваййя ошибки и дифференциала ошибки выполнен в виде сумматора, узла памяти и коммутирующего элемента информационный вход которого соединен с первым входом сумматора и является информационным входом блока, управляющий вход является управляющим входом блока, а выход подсоединёнко второму входу сумматора, выход которого является выходом блока. На чертеже изображена структурная .схема вычислительного устройства. Устройство содержит линейный во . всем рабочем диапазоне блок 1 формирования интегральной ошибки основного параметра (частоты, скорости и т. д.), т. е. обычный интегратор на базе операционнрго усилителя, реверсивный счетчик широкодиапазонный фазовый дискриминатор с аналоговым или цифровым выходом я т. Д. выход которого подключен к последовательно соединенным блокам формирования ошибки 2 и дифференциала ошибки 3. Эти блоки 2 и 3 содержат сумматоры 4 и 5 и узлы памяти 6 и 7 с выходом канала дифференциала ошибки (по ча тоте, скорости и т. д.). Выходы блоков 1, 2 и 3 подсоединены наряду с дополнительными командами (Jf , i(i, 3, ... , Xt), характеризующими токовый режим якорной цепи двигателя, режим движения привода, номер работающего комплекса и т. д. ко входам собственно регулятора 8 ВП, где осуществляется масштабирование сигналов, характеризующих oшибку и ее изменения во времени, с учетом характера работы привода на текущем интервале вентильности. Выход регулятора 8 подсоединен к блоку импульсно-фа- эбвогб упраншения 9. Выходы блока 9 подключены ко входам логического элемента ИЛИ 10 через формирователи коротких импульсов 11. Выход элемента ИЛИ (сборка импульсов синхронизйции) подсоединен ко входам управления коммутирующих элементов 12 и 13 блокрв 2 и 3. Устройство работает следующим образом. Сигнал I7j, про торциональный интегральной ошибке основного параметра (например, по частоте) в широком диапазоне фазового сдвига 2Jr/ Afctt, (1) поступает на вход первого сумматора 4 непосредственно и на вход первого узла памяти 6 через первый коммутирующий элемент 12, замыкающийся на время записи этого сигнала в первый узел памяти, причем периодически запись (фиксация) в узле памяти в производится в моменты формирования каждого управляющего импульса системы импульсно-фазо- вого управления ВП. Зафиксированный сигнал Uj ( id) с выхода узла памяти 6 сравнивается с текущим значением Ui(,i} ( .). На выходе сумматора 4 получаем сигнал U4(t-,+At)xTJj(it4dt)-t;j(t) .. при At(ti.i-tL) , (2) характеризующий изменение интегральной составляющей ошибки в течение (t+1) интервала вентильности. Известно, что в зоне малых управляющих воздействий интервал вентильности практически постоянен и равен Т г -пульсность силовой схемы где -т. ВП; -циклическая частота сети. Сигнал с выхода сумматора 4 в конце (t +1)-го интервала , t,(ii..t) Ut(tui)(4) в связи с примерно постоянным интерваом вентильности пропорционален среднему значению ошибки по частоте (скорости на каждом интервале венгильности). В тех случаях когда частота (скорость) на выходе регулятора по каким-либо причинам чзменяется внутри интервала вентильности в одном из рабочих режимов, регулирование этих параметров ведется только по их среднему значению (т. е. текущие, мгновенные значения регулируемого параметра имеют неоднозначную завидвмость относительно сигнала управления ВП в момент формирования очерес1ного управляющего импульса в системе фазового управления). Это же можно сказать и о общем случае гулирования вентильных регуляторов. При отсутствии пульсаций выходного параметра внутри интервала вентильности мгновенные его значения равны средним за этот интервал. В связи с этим в са мом общем случае для построения быстродействующих вентильных регуляторов информация о мгновенных текущих значениях ошибки по частоте (скорости) не может быть непосредственно использована для управления ВП. Ее необходимо перед этим усреднить тем или иным образом. Причем наиболее оптимальное решение этого вопроса - усреднение на интервале вентильности (т. е. на временном интервале между двумя соседними управляющими импульсами ВП), так как при этом в систему регулирования вводится минимальная инерция (запаздывание). Аналогично с учетом вышеизложенного рещается задача по вычислению среднего значения дифференциала от оши ки по частоте J: (ошибки по ускорению в случае, если выходные параметры (путь, скорость) l7():.)-T7e,(tO 3j Причем сигнал с выхода сумматора 5 j конце (t +1)-го интервала .t)U4 tLHVl/b(tO (10) Сигналы 1 , 1/(,, U;j поступают на вход регулятора 8 вместе с дополнительными командами Xi , Х , Xj п рактеризующими режим работы привода, характер изменения его отдельных параметров, превышение отдельных параметров и т. д. С помощью дополнительных команд по некоторому алгоритму оптими зации управления осуществляется масшта бирование сигналов tTf , 1/1, , у, , при фо мировании выходного сигнала регулятора Применение рассматриваемого вычислительного устройства в различных сист мах регулирования (в частности на базе ВП) позволяет повысить их точность и быстродействие вплоть по пpeдeльныxi теоретически возможных величин (повышение частоты среза вентильных систем до граничной частоты ВП. Формула изобретения Вычислительное устройство для систем управления.вентильными электроприводами, содержащее последовательно включенные блоки формирования интегральной ошибки, формирования ошибки и дифференциала ошибки, выходы которых подключены к соответствующим входам регулятора вентильного электропривода, подсое- диненнога выходом к трем входам блока импульспо-фазового управления, отличающееся тем, что, с Целью повышения точности работы устройства за счет синхронизации вычислений с работой силового узла электропривода , оно содержит три формирователя коротких импульсов и элемент ИЛИ, выход которого подключен к управляющим входам блоков формирования ошибки и дифференциала ошибки, а три входа подсоединены к выходам соответствующих формирователей коротких импульсов., подключенных входами к трем выходам блока импульс- koro фазового управления. 2. Устройство по п. 1 о т л и ч а to щ е е с я тем, что в нем каждый блок формирования ошибки и дифференциала ошибки выполнен в виде сумматора, узла памяти и коммутирующего элемента, информационный вход которого соединён с первым входом сумматора и является информационным входом блока, управляющий вход является управляющим входом блока, а выход подсоединен ко второму входу сумматора, выход которого является выходом блока. Источники информации, принятые во внимание при экспертизе 1.Амдрущук В. В. Теоретическое и экспериментальное исследование высокоточной системы электропривода с беспазовой машиной постоянного тока. Диссертация на соискание научной степени кандидата технических наук. Л., 1973. 2.Авторское свидетельство СССР по заявке N 2461749/24, кл &,06 G 7/12, 17.03.77 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления вентильным преобразователем | 1985 |

|

SU1277319A1 |

| Способ фазового управления асинхронным электродвигателем и устройство для его осуществления | 1978 |

|

SU928582A1 |

| Устройство для управления электроприводом | 1980 |

|

SU892630A1 |

| Электропривод с раздельным управлением | 1989 |

|

SU1817220A1 |

| Устройство для управления электро-дВигАТЕлЕМ пОСТОяННОгО TOKA | 1976 |

|

SU797041A1 |

| Адаптивный регулятор тока для управляемых вентильных преобразователей | 1990 |

|

SU1786627A1 |

| Регулятор скорости для вентильного электропривода постоянного тока | 1977 |

|

SU738084A1 |

| Устройство для вычисления статического момента вентильного электропривода | 1979 |

|

SU947880A1 |

| Частотно-регулируемый электропривод грузоподъемного механизма | 1985 |

|

SU1365333A1 |

| Способ раздельного управления реверсивным вентильным электроприводом и устройство для его осуществления | 1984 |

|

SU1354377A1 |

Авторы

Даты

1980-07-05—Публикация

1977-11-23—Подача