(5) ИЗ-ТРИГГЕР

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер | 1980 |

|

SU892666A1 |

| Триггерное устройство | 1981 |

|

SU966856A1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

| Триггерное устройство | 1981 |

|

SU970647A1 |

| Распределитель | 1982 |

|

SU1051710A1 |

| Триггерное устройство | 1980 |

|

SU991579A1 |

| Процессор для умножения вектора на матрицу размером S @ N | 1990 |

|

SU1751780A1 |

| Умножитель частоты | 1989 |

|

SU1709310A1 |

| ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1986 |

|

SU1424694A1 |

| Анализатор электрических сигналов | 1986 |

|

SU1425714A1 |

I

Изобретение относится к импульсной технике.

Известен MS-триггер, содержащий основной и вспомогательный триггерыр.

Недостатками этого триггера йв ляются отсутствие возможности изменять коэффициент счета и работать от положительного и отрицательного фронтов..

Известен также MS-триггер, содержащий два основных (M-master) и один вспомогательный (S-save) триггеры12.

Недостатком триггера является то, что MS-триггер может работатьлибо в режиме счета, либо в режиме запоминания информации. Для многих схем импульсной техники, в том числе схем с переменными параметрами, наличие только этих функций создает значительные трудности при проектировании и увеличивает размеры проектируемых устройств.

Цель изобретения - расширение функциональных возможностей MS-триггера, закл очаккдееся в том, что триггер получает возможность изменять коэффициент счета с 2 на 1, изменять фазу выходного сигнала, работать по положительному и отрицательному перепаду тактового сигнала раздельно или совместно, формировать на выходе последовательности, состоящие из тактовых

10 импупьсоа,

Постаалеиная цепь достигается тем, что в HS-триггере, содержащем первый основной триггер, второй основной триггер, вспомогательный триггер и

ts кнаертор, вход которого соединен с тактовой шиной, первый информационный вход вспомогательного триггера соединен с выходом первого основного триггера, счетный вход первого

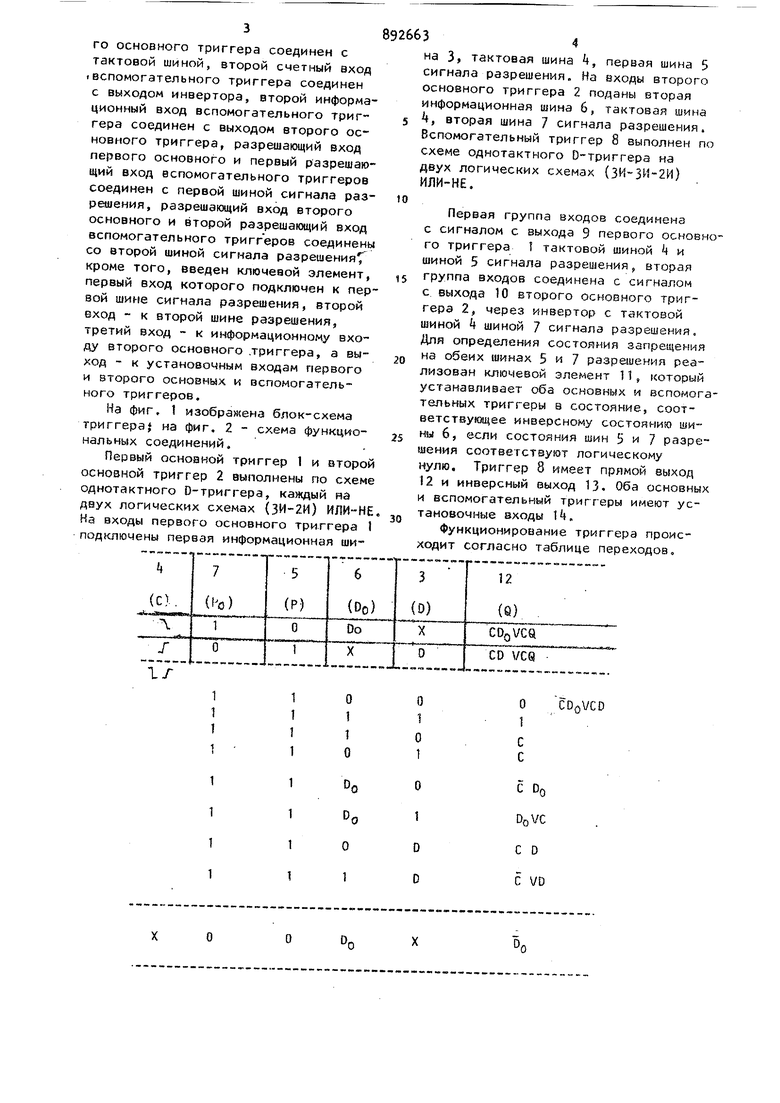

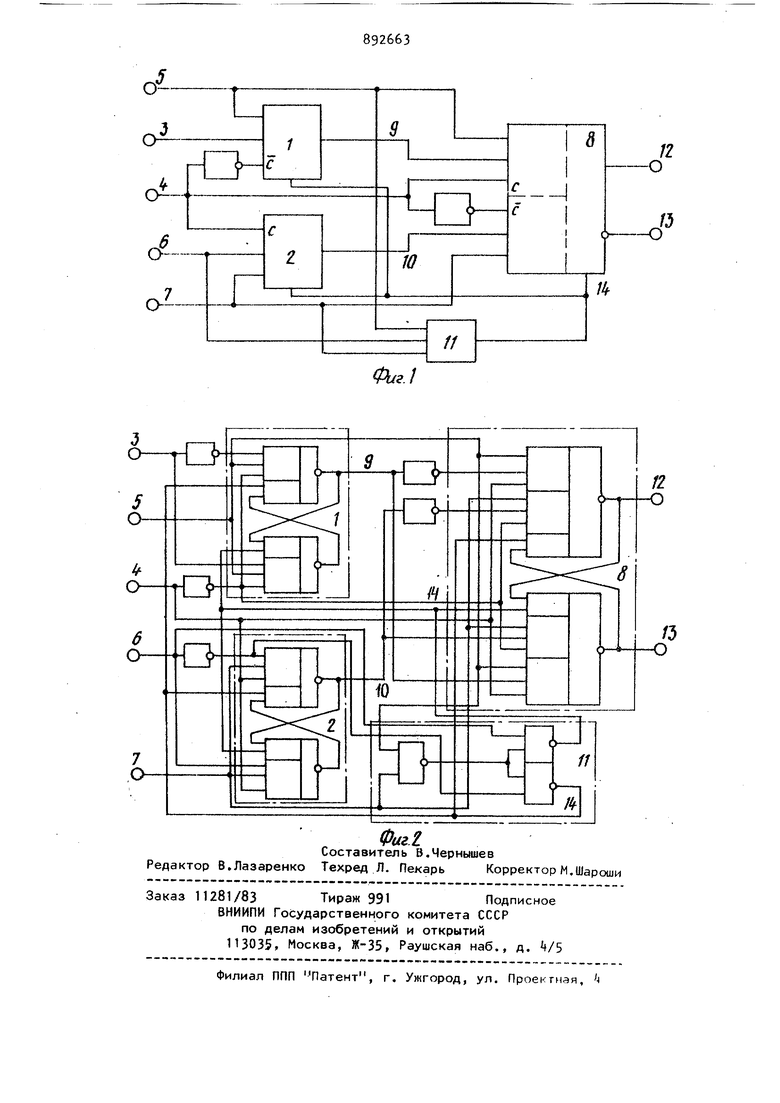

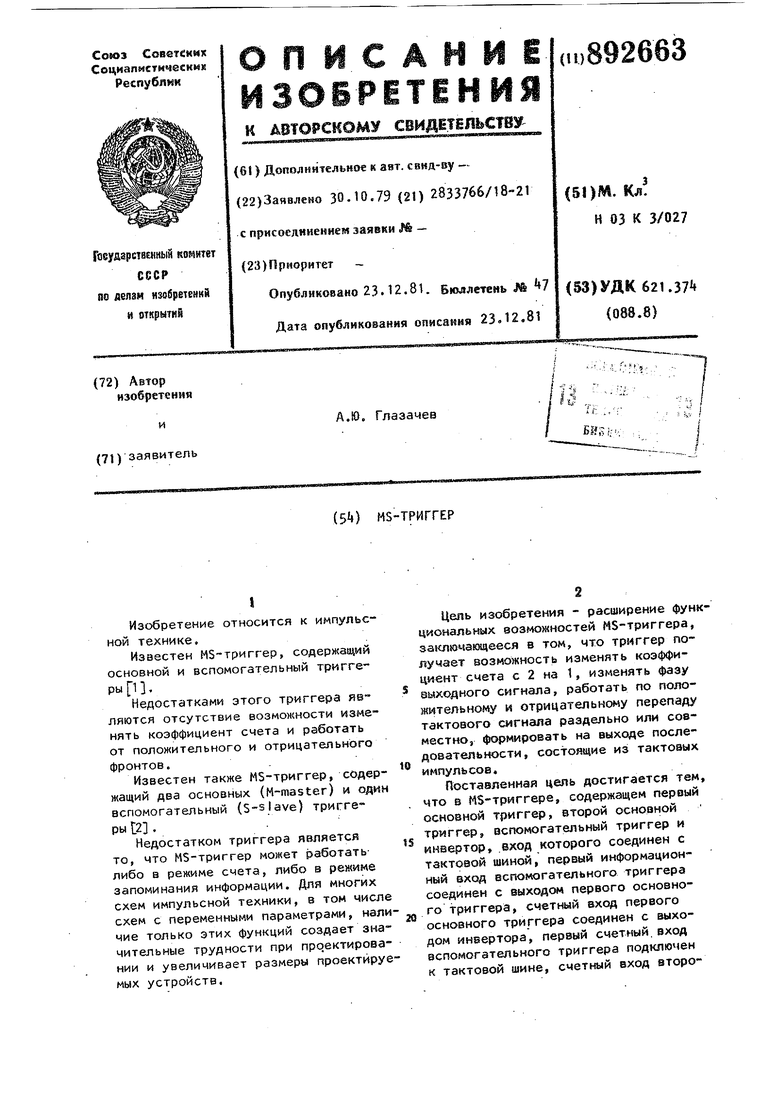

20 основного триггера соединен с выходом инвертора, первый счетный,вход вспомогательного триггера подключен к тактовой шине, счетный вход второго основного триггера соединен с тактовой шиной, второй счетный вход Iвспомогательного триггера соединен с выходом инвертора, второй информационный вход вспомогательного триг гера соединен с выходом второго основного триггера, разрешающий вход первого основного и первый разрешающий вход вспомогательного триггеров соединен с первой шиной сигнала разрешения, разрешающий вход второго основного и второй разрешающий вход вспомогательного триггеров соединены со второй шиной сигнала разрешения кроме того, введен ключевой элемент, первый вход которого подключен к пер вой шине сигнала разрешения, второй вход - к второй шине разрешения, третий вход к информационному входу второго основного .триггера, а выход - к установочным входам первого и второго основных и вспомогательного триггеров. На фиг, 1 изображена блок-схема триггераJ на фиг. 2 - схема функциональных соединений. Первый основной триггер 1 и второ оснозной триггер 2 выполнены по схем однотактного D-триггера, каждый на двух логических схемах (ЗИ-2И) На входы первого основного триггера подключены первая информационная шиCDoVCDа 3, тактовая шина 4, первая шина 5 игнала разрешения. На входы второго сновного триггера 2 поданы вторая нформационная шина 6, тактовая шина , вторая шина 7 сигнала разрешения. спомогательный триггер 8 выполнен по хеме однотактного D-триггера на вух логических схемах (ЗИ ЗИ-2И) ЛИ-НЕ. Первая группа входов соединена с сигналом с выхода 9 первого основного триггера 1 тактовой шиной и шиной 5 сигнала разрешения, вторая группа входов соединена с сигналом с выхода 10 второго основного триггера 2, через инвертор с тактовой шиной k шиной 7 сигнала разрешения. Для определения состояния запрещения на обеих шинах 5 и 7 разрешения реализован ключевой элемент 11, который устанавливает оба основных и вспомогательных триггеры 8 состояние, соответствуюцее инверсному состоянию шины 6, если состояния шин 5 и 7 разре шения соответствуют логическому нулю. Триггер 8 имеет прямой выход I2 и инверсный выход 13. Оба основных и вспомогательный триггеры имеют установочные входы I. Функционирование триггера происходит согласно таблице переходов. Рассмотрим работу триггера so все режимах, которые определяются сигналами разрешения с шин 5 (Р) и 7 (P Если сигналы разрешения Р (10), то в этом случае к вспомоготельному триггеру 8 подключен первый основиой триггер 1, второй основной триггер 2 в это время находится в состоянии Память и на вспомогательный триггер влияния не оказывает. Вся схема работает в этом случае как О-триггер с записью во вспомогательный триггер положительным перепадом тактового сигнала, входная информация вво7,ится по информационной шине 3 первого основного тригге ра, состояние информационного входа 6 второго основного триггера может быть любым. Работа в таком режиме описывается уравнением CDvCQ, которое является уравнением D-триггера с записью положительным пере™ падом тактового сигнала. Если сигналы разрешения PPQ(Q), то в этом случае к вспомогательному триггеру 8 подключен второй основной триггер 2, первый основной триггер 1 в это время находится в состоянии Память и на вспомогательный триггер влияния не оказывает. Вся схема работает в этом случае как D-триггер с записью во вспомогательный триггер отрицательным перепадом тактового сигнала, входная инфор мация вводится по информационной шине 6 второго основного триггера, состояние информационной шины 3 первого основного триггера мо)ет быть любым. Работа в таком режиме описывается уравнением CD VCQ .которое является уравнением D-триггера с записью отрицательным перепадом тактового сигнала. Если сигналы разрешения PPQ(11), то в этом случае к вспомогательному триггеру 8 подключены оба основных триггера и во время прохождения отри цательного уровня тактового сигнала входная информация будет записыватьс по шине 3 в первый основной триггер а во вспомогательный триггер 8 из вт рого основного триггера 1 будет передаваться содержащаяся в нем инфо мация. Во время прохождения положительного уровня тактового сигнала входная информация будет записываться по шине 6 во второй оснорной триг гер 2, а во вспомогательный триггер 8 из первого основного триггера 1 бу дет передаваться содержащаяся в нем инфорг-оция. Такой вид работы рассмотрен в третьей графе таблицы переходов и определен формулой CDjjVCD. В этом режиме на состояние выходной- информации будут оказывать воздействие две информационные шины 3 и 6, в связи с чем рассмотрим состояние выходной информации 12(9) в зависимости от всех возможных комбинаций сигналов 3{D) и 6(Do) , Сигналы D(jD (00). 8 этом случае положительным уровнем тактового сигнала ноль запишется во второй основной триггер 2, а отрицательным в первый основной триггер 1, во вспо могательный триггер 8 ноль будет передаваться положительным уровнем тактового сигнала из первого основ ного триггера, а отрицательным из второго основного триггера. Сигналы DjjO « (11). В этом случае положительным уровнем тактоаого сигнала единица запишется во второй основной триггер 2, а отрицательным 8 первый основной триггер 1, во вспомогательный триггер 8 единица будет передаваться положительным уровнем тактового сигнала из пеоаого основного триггера, а отрицательным из второго основного триггера. Сигналы D0b (io). В этом случае положительным уровнем тактового си|- нала единица запишется во второй основной триггер 2, а отрицательным уровнем тактового сигнала ноль запишется 8 первый основной триггер 1, во Bcnof-югательный триггер ноль будет передаваться положительным уровнем тактового сигнала из первого основного триггера, а единица будет передаваться отрицательным уровнем TaKtoвого сигнала из второго основного триггера, таким образом, с каждым изменением уровня тактового сигнала информация на выходе 12 триггера будет изменять саое состояние на противоположное по отношению к действующему в данный момент уровню тактового сигнала и на выходе 12 будет сигнал,инверсный тактовому сигналу, в формулах он указан как С. Сигналы ОдО (01). В этом случае положительным уровнем тактового сигнала ноль запишется ео второй основной триггер 2, а отрицательным уровнем тактового сигнала единица запишется в первый основной триггер 1 , во вспомогательный триггер 8 ноль 7 будет передаваться отрицательным уровнем тактового сигнала из второго основного триггера, а единица будет передаваться положительным уровнем тактового сигнала из первого основного триггера, таким образом, с канщым изменением уровня тактового сигнала информация на выходе 12 триггера будет изменять свое состояние на состояние, соответствую щее действующему в данный момент уровню тактового сигнала, и на вы ходе 12 будет сигнал, совпадающий с тактовым сигналом, в формулах он указан как С. Рассмотрим также характеристики триггера, если на одной из шин 3 (В) или 6( находится постоянный сигнал а на другой сигнал изменяется по какому-либо закону. Сигналы Од О (0о1). 8 этом Случае в первом основном триггере 1 будет постоянная единица, записанная отрицательным уровнем тактового сигнала, а во второй основной триггер 2 соот ветствущая информация будет запи, сываться полойадтельным уровнем такт вого сигнала в зависимости от состоя ния входа 6(DO) во вспомогательный триггер 8 из основного тригг ра положи тел bi-ftiM уровнем тактового сигнала будет передаваться единица, а из второго основного триггера отри цательным уровнем тактового сигнала его состояние в данный момент, та КИМ образом, на выходе 12 будет обра зовываться сигнал., имеющий привязку к положительному уровню и импульсы отрицательной полярности с длительностью, равной длительности отрицательного уровня тактового сигнала в те моменты, когда отрицательным уров нем тактового сигнала во вспомогательный триггер из второго основного триггера будет переписываться ноль, формула образования выходного сигнала в данном режиме ,которая озна чает, если DQ-I, то , а если РО(О), то Сигналы DQD (DQO). В этам слумае в первом основном триггере 1 будет постоянный нолЬр записанный отрицательным уровнем тактового сигна ла, а во второй основной триггер 2 соответствующая информация будет записываться положительным уровнем так тового сигнала в зависимости от состояния входа 6(Dg), во вспомогательный триггер 8 из первого основного триггера положительным уровнем такто вого сигнала будет передаваться ноль, а из второго основного триггера, отрицательным уровнем тактового сигнала его состояние в данный момент, таким образом, на выходе 12 будет образовываться; сигнаЛр имеющий привязку к отр.ицательному уровню и им пульсы положительной полярности с длительностью, равной .длительности отрицательного уровня тактового сигнала в те моменты, когда отрицательным уровнем тактового сигнала во вспомогательный триггер из второго основного триггера будет переписываться единица, формула образования выходного сигнала в данном режиме CDg, которая означает если DO О, то Q О, а если DO 1, то Q С. Сигналы DgD (00) „ В этом случае во втором основном триггере 2 будет постоянно ноль, записанный положительным уровнем тактового сигнала, а в первом основном триггере 1 соотзетствующая информация будет записана отрицательным уровнем тактового сигна ла в зависимости от состояния входа 3(0), во вспомогательный триггер 8 из второго основного триггера отрицательным уровнем тактового сигнала будет передаваться ноль, а из первого основного триггера положительным уровнем тактового сигнала его состояние в данный момент, таким образом, ,„ ,, ..i выходе 1г будет образовываться сигнал, имеющий привязку к отрицательHOf-ty уровню и иипульсы положительной полярности с длительностью, равной длительности положител ьного уровня такта в те моменты, когда положительным уровнем тактового сигналс во вспомогательный триггер из первого основного триггера будет переписываться единица, формула образования выходного сигнала в данном режиме CD, которая означает, если , то , а если D- 1, то . Сигналы DQP (10), В этом случае во втором основном триггере 2 будет постоянно единица, записанная положительным уровнем тактового сигнала, а в первый основной триггер 1 соот ветствующая информация будет записываться отрицательным уровнем тактового сигнала в зависимости от состояния шины 3(0), во вспомогательный триггер 8 из второго основного триггера 2 отрицательным уровнем тактового сигнала будет передаваться един ца, а из первого основного триггера 1 положительным уровнем тактового сигнала его состояние в данный момент, таким образом,на выходе 12. будет образовываться сигнал, имеющий привязку к положительному уровню и импульсы отрицательной полярности с длительностью, равной длительности положительного уровня тактового сигнала в те моменты, когда положительным уровнем тактового сигнала во вспомогательный триггер из первого основного триггера будет переписываться ноль, формула образования выходного сигнала в данном режиме CVD, которая означает, если , то , а если , то . Если сигналы DQ и D оба изменяются по какому-либо закону, то на выходе 12 образуется сигнал, состоящий из комбинаций рассмотренных выше частных случаев, который описывается формулой CDoVCD. Если сигналы разрешения РРд (00), то в этом случае первый основной триггер, второй основной триггер и вспомогательный триггер отключены от воздействия своих тактовых входов и информационных входов,но при сигна лах ) ключевой элемент П опре деляет это состояние сигналов разрешения и подключает сигнал шины 6(Do) к установочном входам первого основного триггера, второго основного три гера и вспомогательного триггера, в результате чего все они устанавливаются в состояние Do, инверсное к состоянию шины 6, а это значит, что информация на выходе 12 будет отслеж вать инверсное состояние шины 6(Do) и будет происходить непосредственная передача входной информации на выход триггера. Из рассмотренных режимов работы триггера можно заключить, что триг гер может работать по положительному и отрицательному перепаду тактового сигнала раздельно или совместно, а также изменять коэффициент счета с 2 на 1 и фазу выходного сигнала, формировать на выходе последовательности, состоящие из тактовых импульсов необходимой полярности с длительностью импульса, равной либо дли тельности положительного уровня тактового сигнала, либо длительности отрицательного уровня тактового сигнала использовать триггер как манипулятор фазы по тактовому сигналу при PPQ (11) и CDo VCD , передавать входную информацию непосредственно на выход, кроме того, триггер сохраняет все возможности MS-триггера с установочными входами. Формула изобретения MS-триггер, содержащий первый основной триггер, второй основной триггер, вспомогательный триггер и инвертор,вход которого соединен с тактовой шиной,первый информационный вход вспомогательного триггера соединен с выходом первого основного триггера, счетный вход первого основного триггера соединен с выходом инвертора, первый счетный вход вспомогательного триггера подключен к тактовой шине, отличающийся тем, что, с целью расширения функциональных возможностей, счетный . вход второго основного триггера соединен с так,товой шиной, второй счетный вход вспомогательного триггера соединен с выходом инвертора, второй информационный вход вспомогательного триггера соединен с выходом второго основного триггера, разрешающт вход первого основного и первый разрешающий вход вспомогательного триггеров соединены с первой шиной сигнала разрешения , разрешаю)ций вход второго основного и второй разрешающий вход вспомогательного триггеров соединены со второй шиной сигнала разрешения, кроме того, введен ключевой элемент, первый вход которого подключен к первой шине сигнала разрешения, второй вход к 1зторой шине разрешения, третий входк информационному входу второго основного триггера, а выход - к установочным входам первого и второго основных и вспомогательного триггеров. Источники информации, принятые во внимание при экспертизе 1. Агаханян Т.М. и др. Интегральные триггеры устройств автоматики, М,, 1978, с. 12, рис. I,. 2. Патент США № 3917961, кл. 307/2 3, 1975.

Авторы

Даты

1981-12-23—Публикация

1979-10-30—Подача