-JL Фиг/

элемент ИЛИ 5, элемент И 6, два регистра 7, 11, сумматор-вычигатель 8, элемент И-НЕ 9 и блок 10 элементов И, соединенные между собой функционально, блок 12 управления и синхронизации, включающий в себя счетчик по модулю три, дешифратор, деа триггера.

элемент НЕ, четыре элемента И, счетчик по модулям S и N, счетчик по модулям (S+1) и (NH) и два коммутатора, соединенные между собой функционально, и блок 13 выдачи коэффициентов матрицы. 2 з.п. ф-лы, 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КООРДИНАТ | 1991 |

|

RU2007749C1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1508228A1 |

| Процессор цифровой обработки сигналов | 1990 |

|

SU1789991A1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2017 |

|

RU2727555C2 |

| Устройство для поиска минимального значения интенсивности размещения в тороидальных системах при направленной передаче информации | 2016 |

|

RU2628329C1 |

| Устройство для преобразования координат вектора в трехмерном пространстве | 1986 |

|

SU1403062A1 |

| Вычислительное устройство | 1986 |

|

SU1361546A1 |

Изобретение относится к цифровой вычислительной технике и может использоваться в системах цифровой обработки сигналов.

Известно устройство для быстрого умножения вектора на матрицу, содержащее регистр сдвига, вычислительный блок, состоящий из реверсивных счетчиков и шин свйзи, две группы коммутаторов, шины управления, управляющий вход, элемент И и информационный вход-выход. Однако это устройство может выполнять вычисления только для вектора, координатами которых являются 1,0. Это значит, что в системах обработки информации входной сигнал, использующийся в качестве вектора, должен быть проквантован на два уровня. Это приводит к сильным погрешностям вычислений и ограничивает область применения устройства.

Известен процессор для умножения матрицы на вектор, содержащий систолическую матрицу из двоичных обрабатывающих элементов, синхронно включаемых импульсами синхронизации Каждый элемент соединен с соседними элементами в данном ряду и колонке В каждом цикле синхронизации обрабатывающий элемент умножает вектора на элемент матрицы. Недостатком данного устройства является его сложность, так как количество обрабатывающих элементов равно числу элементов матрицы.

Наиболее близким к данному по технической сущности и достигаемому эффекту является процессор для умножения вектора на матрицу, содержащий в общем случае S +N-1 последовательно соединенных процессорных элементов (ПЭ) где SxN - это размер матрицы. В свою очередь, каждый процессорный элемент содержит три регистра, сумматор, умножитель. Координаты вектора Y А X, имеющие в начальный момент нулевое значение, поступают и проходят через ПЭ справа налево, в то времся как компоненты вектора X двигаются слев а направо. Элементы матрицы вводятся в ПЭ сверху вниз.

Однако это устройство оказывается сложным при решении большого числа заг дач цифровой обработки сигналов. Как пра- вило такие задачи сводятся к умножению вектора (сигнала) на некоторую матрицу ненулевых элементов. В настоящее время наиболее широкое распространение в системах передачи информации, радиолокации, радионавигации получили бинарные сигналы. Для них элементами матрицы являются ±1 и. следовательно, можно изменить структуру ПЭ, исключив наиболее сложный и дорогостоящий блок-умножитель. Наиболее характерными задачами являются умножение вектора на матрицу размера SxN, где S N - задача корреляционного декодирования корректирующего кода мощности S и длины N, S N - задача поиска синхронизирующего сигнала, т.е. умножение вектора на матрицу-циркулянт. Для сигналов средних и больших длин N

2 ; S « IM - задача вычисления коэффициентов корреляции между входным сигналом и S последовательностями длины N.

Для решения большинства этих задач использование известного процессора может быть невозможным ввиду сложности реализации

Целью изобретения является расширение области применения за счет возможности умножения вектора на бинарную

матрицу и упрощение процессора. Процессор ориентирован на обработку бинарных сигналов. В структуре процессора учтены современные требования к проектированию СБИС. Для этого вычислительный узел

процессора строится на характерных топологических фрагментах (процессорных элементах) с локальными связями между ними. Структура процессора по сравнению с прототипом позволяет с минимальной аппаратурной сложностью построить более эффективный вычислитель решающий разнообразные задачи.

Поставленная цель достигается за счет того, что в процессоре, содержащем S + N-1

последовательно соединенных процессорных элементов, причем первый информа- ционный вход i-ro процессорного элемента О 2, S + N-1) соединен с первым информационным входом (i-1)-ro процессорного элемента, а первый информационный выход

последнего процессорного элемента является информационным выходом процессора, используется К последовательно соединенных процессорных элементов (К S при Мпри5 М), дешифратор, блок управления и синхронизации и блок выдачи коэффициентов матрицы, причем второй информационный вход первого процессорного элемента является информационным входом процессора, второй ин- формационный выход 1-го процессорного элемента (i 1.K). соединен с вторым информационным входом (i+1)-ro процессорного элемента, первые входы управления всех процессорных элементов соединены с входом управления блока управления и синхронизации, входом управления блока выдачи коэффициентов матрицы и являются входом управления режимом работы процессора, тактовый вход и вход пред- установки блока управления и синхронизации являются тактовым входом и входом предустановки процессора, соответственно, первый выход управления блока управления и синхронизации соединен с входом дешифратора, К выходов которого соединены соответственно с вторым управляющими входами К процессорных элементов, первый и второй тактовые выходы блока управления и синхронизации являются первым и вторым тактовыми выходами процессора, третий тактовый выход блока управления и синхронизации соединен с тактовыми входами всех процессорных элементов, второй выход управления блока управления и синхронизации соединен с адресным входом блока выдачи коэффициентов матрицы, i-й выход которого соединен с третьим информационным входом i-ro процессорного элемента, а (К+1)-й выход блока выдачи коэффициентов матрицы соединен с синх- ровходом блока управления и синхронизации, информацинный вход-выход каждого процессорного элемента соединен с общей информационной шиной, являющейся ин- формационным входом-выходом процессора.

Процессорный элемент содержит первый и второй коммутаторы, первый и второй регистры, сумматор-вычитатель, элемент И, блок элементов И, элемент ИЛИ, элемент И-НЕ и шинный формирователь, причем управляющие входы первого и второго коммутаторов соединены с первым входом элемента ИЛИ, первым входом элемента И- НЕ, входом управления шинного формирователя и являются первым входом управления процессорного элемента, второй вход управления которого соединен с вторым входом элемента ИЛИ, вторым входом элемента И-НЕ и входом выборки кристалла шинного формирователя, первый вход элемента И соединен с тактовым входом второго регистра и является тактовым входом процессорного элемента, выход элемента ИЛИ-с вторым входом элемента И, выход которого соединен с тактовым входом первого регистра, выход первого коммутатора соединен с первым информационным входом сумматора-вычитателя, второй информационный вход которого соединен с выходом первого регистра и является вторым информационным выходом процессорного элемента, выход второго коммутатора соединен с информационным входом первого регистра, разрядные выходы сумматора-вычитателя соединены соответственно с первыми входами элементов И блока и с группой входов шинного формирователя, группа входов-выходов которого является информационным входом-выходом процессорного элемента, выход элемента И-НЕ соединен с вторыми входами элементов И группы, выходы которых соединены с информационным входом второго регистра, выход которого соединен с первым входом первого коммутатора и является первым информационным выходом процессорного элемента, первый информационный вход которого соединен с вторым входом первого коммутатора, второй информационный вход процессорного элемента соединен с первым входом второго коммутатора, второй вход которого соединен с группой выходов шинного формирователя,

Блок управления и синхронизации содержит первый, второй и третий счетчики, первый и второй триггеры, первый и второй коммутаторы, дешифратор, первый-чет- вертый элементы И и элемент НЕ, причем тактовый вход блока управления и синхронизации соединен со счетным входом первого счетчика, вход установки в ноль кбторого соединен с входами установки в ноль второго и третьего счетчика, первого и второго триггеров и является входом предустановки блока управления и синхронизации, вход управления режимом которого соединен с входами управления второго и третьего счетчиков и первого и второго коммутаторов, выходы которых являются первым и вторым тактовыми выходами блока управления и синхронизации, первый и второй выходы управления которого соединены соответственно с выходам третьего и второго счетчиков, выход первого счетчика соединен с входом дешифратора, первый выход которого соединен со счетным входом второго счетчика, второй выход дешифратора соединен с первыми входами

первого и второго элементов И и с вторым входом первого коммутатора, первый вход которого соединен с выходом второго элемента И, второй вход которого является входом синхронизации блока управления и синхронизации, третий тактовый выход которого соединен с третьим выходом дешифратора, тактовым входом первого триггера и первым входом третьего элемента И, выход которого соединен с первым входом второго коммутатора, второй вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с выходом второго элемента И, второй вход четвертого элемента И соединен с вторым входом третьего элемента И, с прямым выходом второго триггера, информационный вход которого соединен с шиной логической единицы, выход первого элемента И соединен со счетным входом третьего счетчика, второй вход второго элемента И соединен с входом элемента НЕ, выход которого соединен с тактовым входом второго триггера и входом установки в единицу первого триггера, информационный вход которого соединен с шиной логического нуля, прямой выход первого триггера соединен со вторым входом первого элемента И.

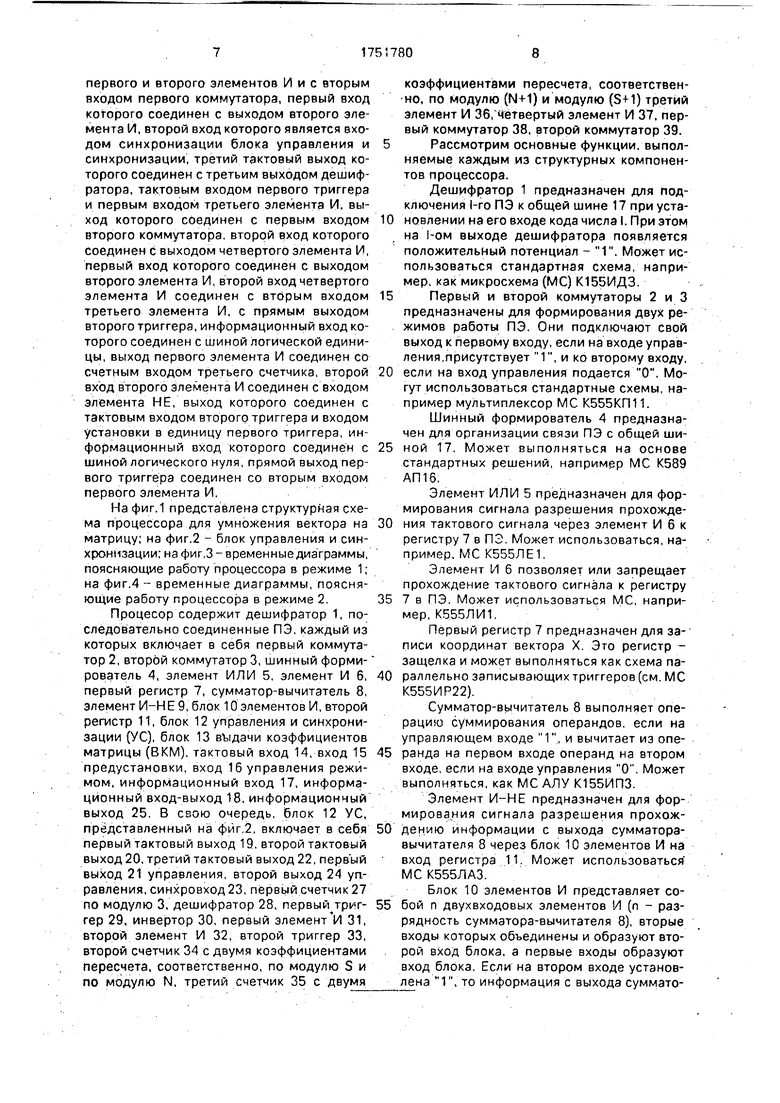

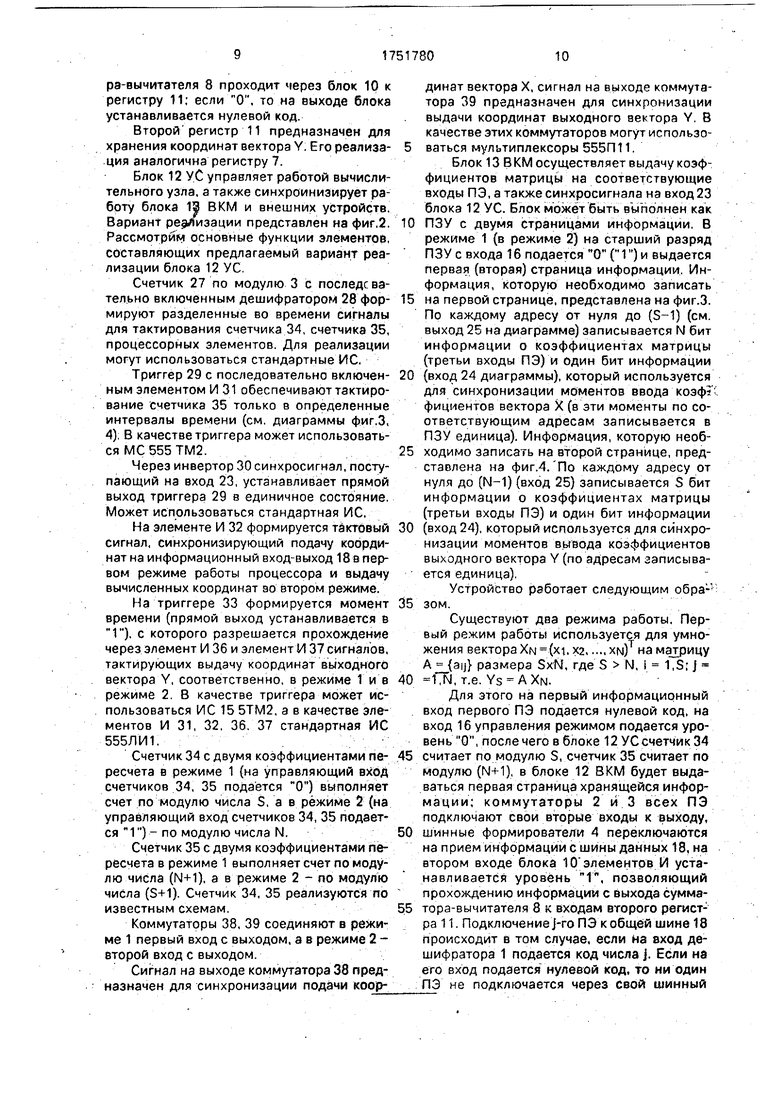

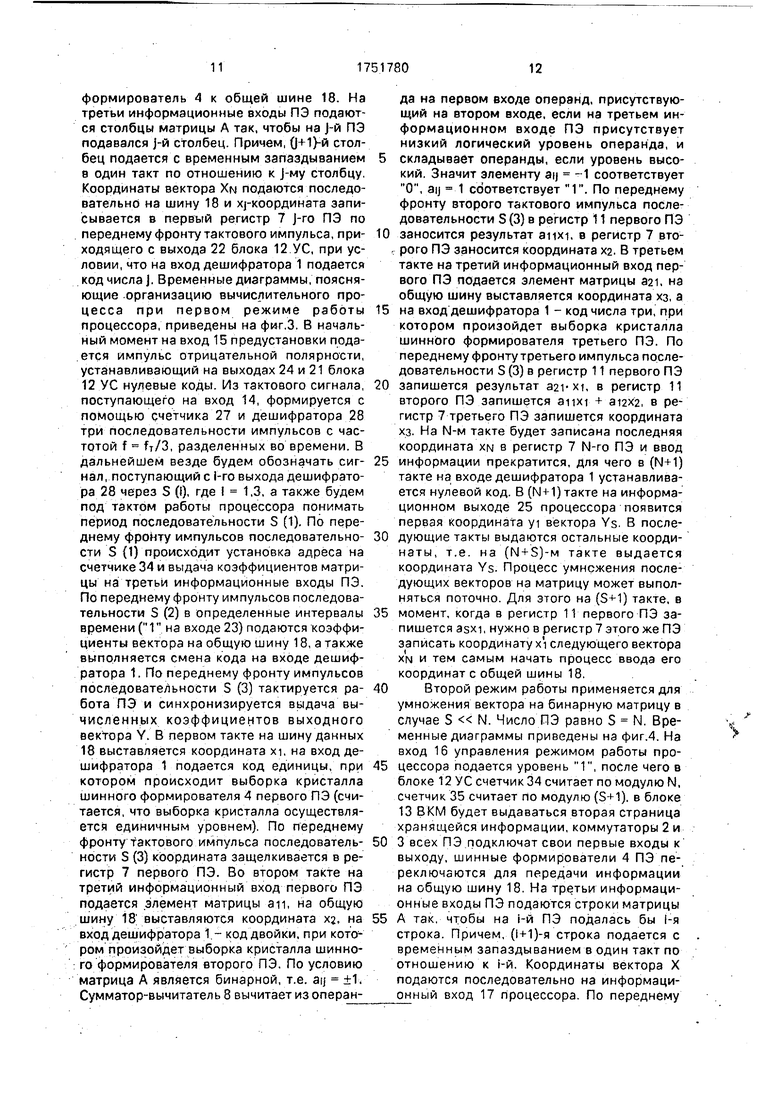

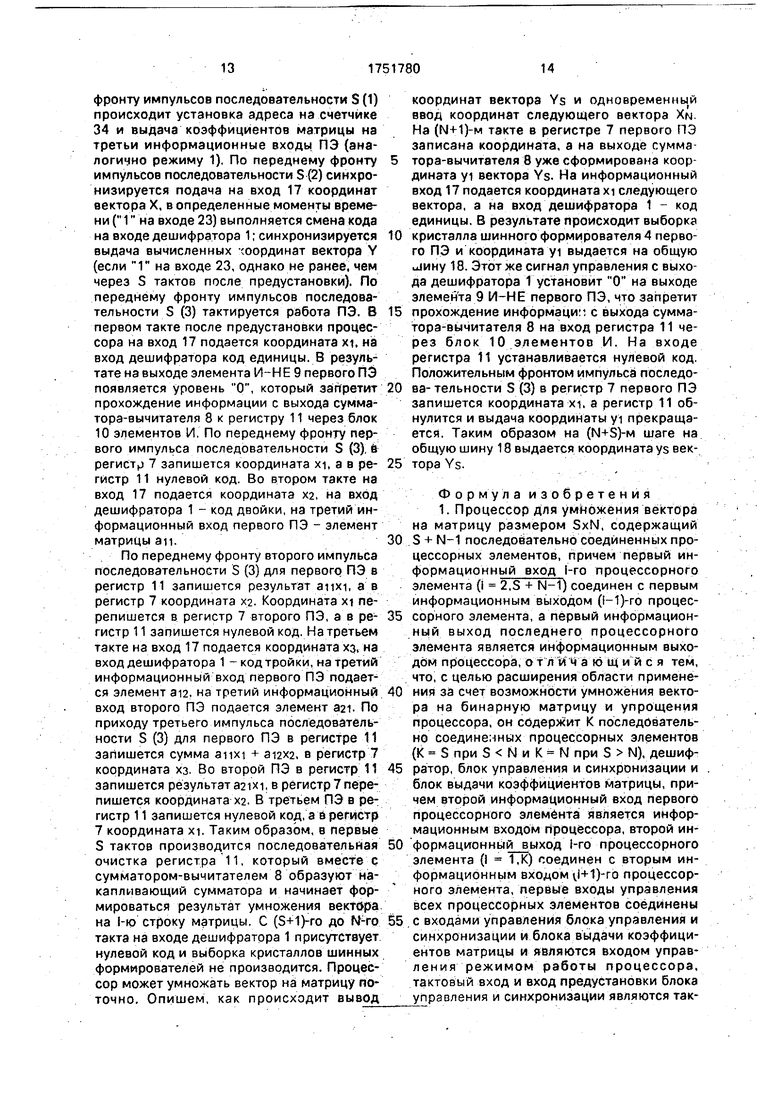

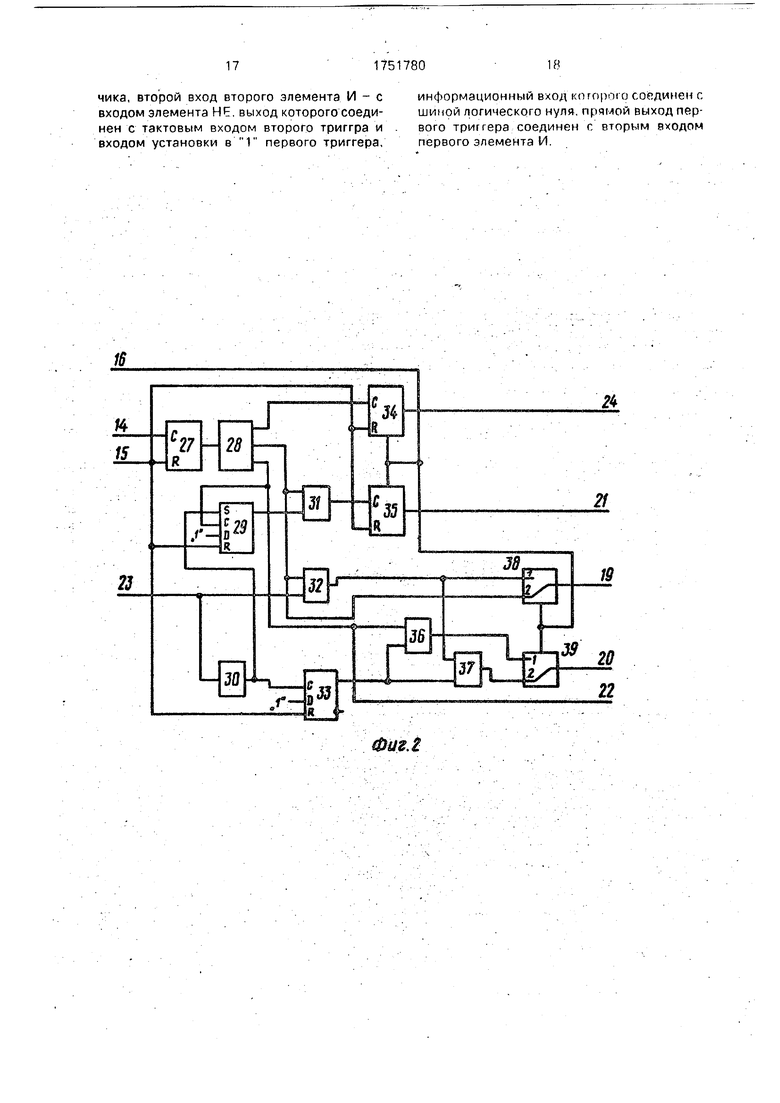

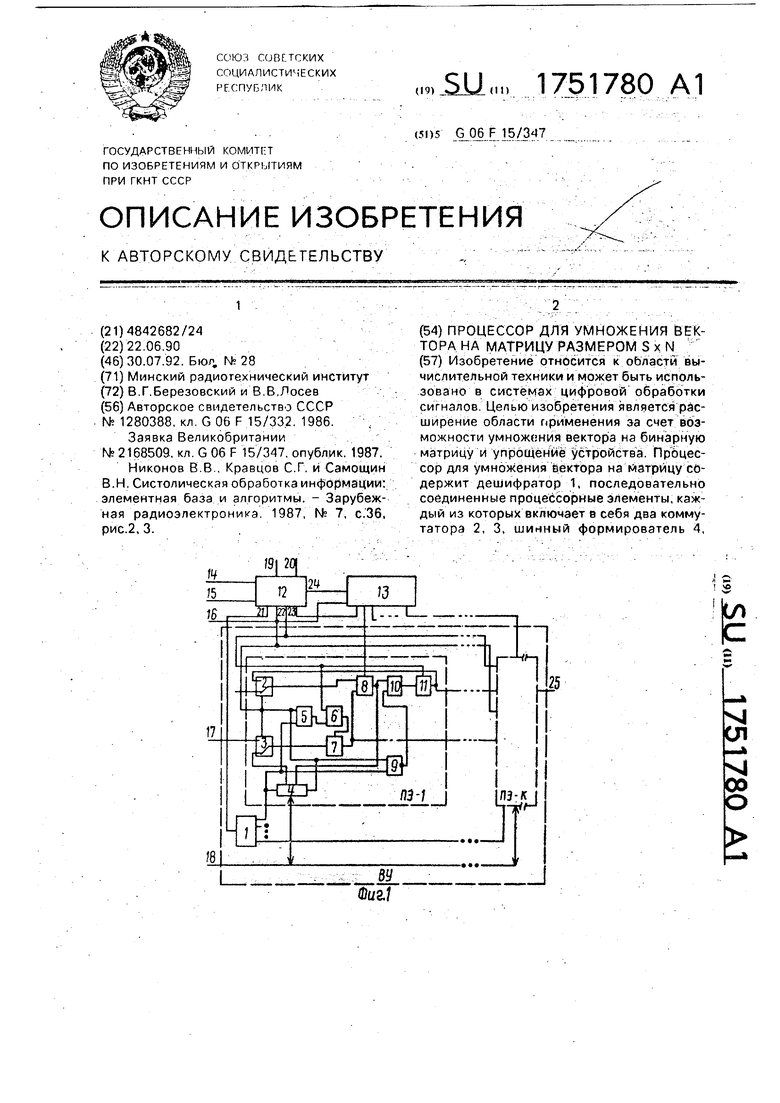

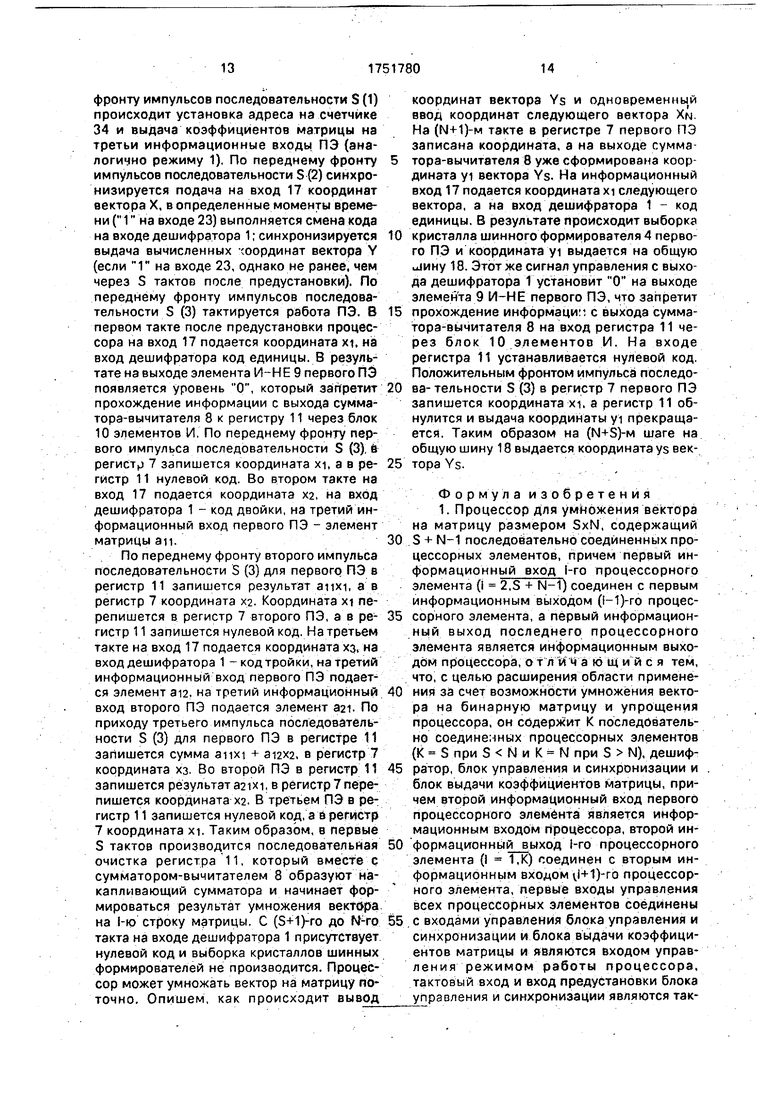

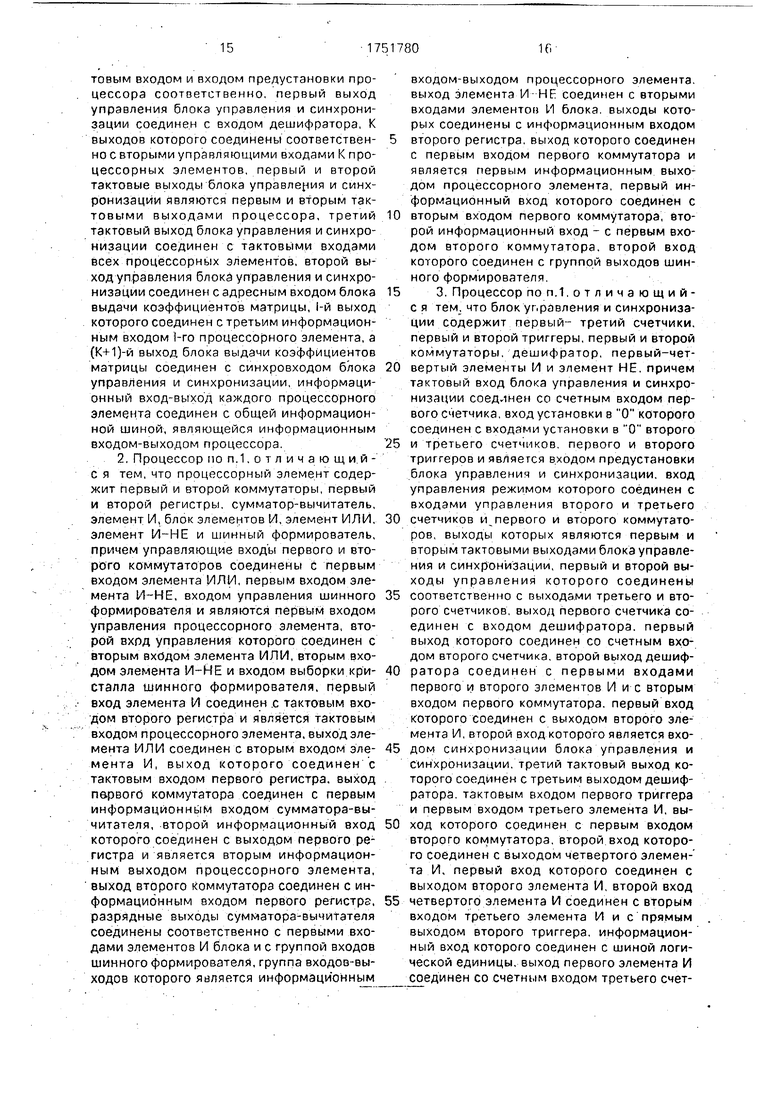

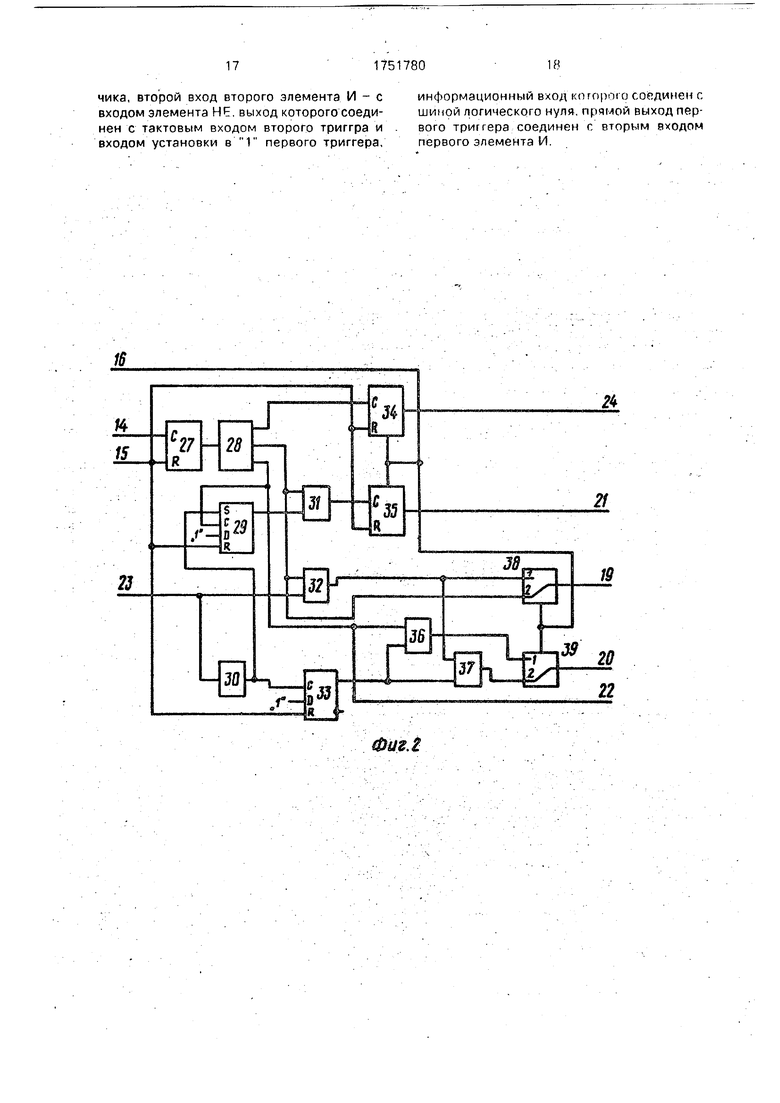

На фиг.1 представлена структурная схема процессора для умножения вектора на матрицу; на фиг.2 - блок управления и синхронизации; на фиг,3-временные диаграммы, поясняющие работу процессора в режиме 1; на фиг.4 - временные диаграммы, поясняющие работу процессора в режиме 2.

Процесор содержит дешифратор 1, последовательно соединенные ПЭ, каждый из которых включает в себя первый коммутатор 2, второй коммутатор 3, шинный формирователь 4, элемент ИЛИ 5, элемент И б, первый регистр 7, сумматор-вычитэтель 8, элемент И-НЕ 9, блок 10 элементов И, второй регистр 11, блок 12 управления и синхронизации (УС), блок 13 выдачи коэффициентов матрицы (ВКМ), тактовый вход 14, вход 15 предустановки, вход 16 управления режимом, информационный вход 17, информационный вход-выход 18, информационный выход 25. В свою очередь, блок 12 УС, представленный на фиг 2, включает в себя первый тактовый выход 19, второй тактовый выход 20, третий тактовый выход 22, первый выход 21 управления, второй выход 24 управления, синхровход 23, первый счетчик 27 по модулю 3, дешифратор 28, первый триггер 29. инвертор 30, первый элемент И 31, второй элемент И 32, второй триггер 33, второй счетчик 34 с двумя коэффициентами пересчета, соответственно, по модулю S и по модулю N, третий счетчик 35 с двумя

коэффициентами пересчета, соответственно, по модулю (N+1) и модулю (S+1) третий элемент И 36, четвертый элемент И 37, первый коммутатор 38, второй коммутатор 39.

Рассмотрим основные функции, выполняемые каждым из структурных компонентов процессора.

Дешифратор 1 предназначен для подключения 1-го ПЭ к общей шине 17 при уста0 новлении на его входе кода числа I. При этом на 1-ом выходе дешифратора появляется положительный потенциал - 1. Может использоваться стандартная схема, например, как микросхема (МС) К155ИДЗ.

5Первый и второй коммутаторы 2 и 3

предназначены для формирования двух режимов работы ПЭ. Они подключают свой выход к первому входу, если на входе управления,присутствует 1, и ко второму входу,

0 если на вход управления подается О. Могут использоваться стандартные схемы, например мультиплексор МС К555КП11.

Шинный формирователь 4 предназначен для организации связи ПЭ с общей ши5 ной 17. Может выполняться на основе стандартных решений, например МС «589 АП16,

Элемент ИЛИ 5 предназначен для формирования сигнала разрешения прохожде0 ния тактового сигнала через элемент И 6 к регистру 7 в ПЭ Может использоваться, например, МС К555ЛЕ1.

Элемент И 6 позволяет или запрещает прохождение тактового сигнала к регистру

5 7 в ПЭ. Может использоваться МС, например, К555ЛИ1.

Первый регистр 7 предназначен для записи координат вектора X. Это регистр - защелка и может выполняться как схема па0 раллельно записывающих триггеров (см. МС К555ИР22).

Сумматор-вычитатель 8 выполняет операцию суммирования операндов, если на управляющем входе 1, и вычитает из опе5 ранда на первом входе операнд на втором входе, если на входе управления О. Может выполняться, как МС АЛУ К155ИПЗ.

Элемент И-НЕ предназначен для формирования сигнала разрешения прохож0 дению информации с выхода сумматора- вычитателя 8 через блок 10 элементов И на вход регистра 11 Может использоваться МС К555ЛАЗ.

Блок 10 элементов И представляет со5 бой п двухвходовых элементов И (л - разрядность сумматора-вычитателя 8), вторые входы которых объединены и образуют второй вход блока, а первые входы образуют вход блока. Если на втором входе установлена 1, то информация с выхода сумматора-вычитателя 8 проходит через блок 10 к регистру 11; если О, то на выходе блока устанавливается нулевой код.

Второй регистр 11 предназначен для хранения координат вектора Y. Его реализация аналогична регистру 7.

Блок 12 УС управляет работой вычислительного узла, а также синхроинизирует работу блока 13 ВКМ и внешних устройств. Вариант реализации представлен на фиг,2. Рассмотрим основные функции элементов, составляющих предлагаемый вариант реализации блока 12 УС.

Счетчик 27 по модулю 3 с последе ва- тельно включенным дешифратором 28 формируют разделенные во времени сигналы для тактирования счетчика 34, счетчика 35, процессорных элементов. Для реализации могут использоваться стандартные ИС.

Триггер 29 с последовательно включенным элементом И 31 обеспечивают тактирование счетчика 35 только в определенные интервалы времени (см. диаграммы фиг.З, 4). В качестве триггера может использоваться МС 555 ТМ2.

Через инвертор 30 синхросигнал, поступающий на вход 23, устанавливает прямой выход триггера 29 в единичное состояние. Может использоваться стандартная ИС,

На элементе И 32 формируется тактовый сигнал, синхронизирующий подачу координат на информационный вход-выход 18 в первом режиме работы процессора и выдачу вычисленных координат зо втором режиме.

На триггере 33 формируется момент времени (прямой выход устанавливается в 1), с которого разрешается прохождение через элемент И 36 и элемент И 37 сигналов, тактирующих выдачу координат выходного вектора Y, соответственно, в режиме 1 и в режиме 2. В качестве триггера может использоваться ИС 15 5ТМ2, а в качестве элементов И 31, 32, 36. 37 стандартная ИС 555ЛИ1,

Счетчик 34 с двумя коэффициентами пересчета в режиме 1 (на управляющий вход счетчиков 34, 35 подается О) выполняет счет по модулю числа S, а в режиме 2 (на управляющий вход счетчиков 34, 35 подается 1) - по модулю числа N.

Счетчик 35 с двумя коэффициентами пересчета в режиме 1 выполняет счет по модулю числа (N+1), а в режиме 2 - по модулю числа (S+1). Счетчик 34, 35 реализуются по известным схемам.

Коммутаторы 38, 39 соединяют в режиме 1 первый вход с выходом, а в режиме 2 - второй вход с выходом.

Сигнал на выходе коммутатора 38 предназначен для синхронизации подачи координат вектора X, сигнал на выходе коммутатора 39 предназначен для синхронизации выдачи координат выходного вектора Y, В качестве этих коммутаторов могут использо- ваться мультиплексоры 555П11.

Блок 13 В КМ осуществляет выдачу коэффициентов матрицы на соответствующие входы ПЭ, а также синхросигнала на вход 23 блока 12 УС. Блок может быть выполнен как

0 ПЗУ с двумя страницами информации. В режиме 1 (в режиме 2) на старший разряд ПЗУ с входа 16 подается О ( 1) и выдается первая (вторая) страница информации. Информация, которую необходимо записать

5 на первой странице, представлена на фиг.З. По каждому адресу от нуля до (S-1) (см. выход 25 на диаграмме) записывается N бит информации о коэффициентах матрицы (третьи входы ПЭ) и один бит информации

0 (вход 24 диаграммы), который используется для синхронизации моментов ввода коэфТ фициентов вектора X (в эти моменты по соответствующим адресам записывается в ПЗУ единица). Информация, которую необ5 ходимо записать на второй странице, представлена на фиг.4. По каждому адресу от нуля до (N-1) (вход 25) записывается S бит информации о коэффициентах матрицы (третьи входы ПЭ) и один бит информации

0 (вход 24), который используется для синхронизации моментов вывода коэффициентов выходного вектора Y (по адресам записывается единица).

Устройство работает следующим обра5 зом.

Существуют два режима работы. Первый режим работы используется для умножения вектора XN(xi,X2XN)T на матрицу

А размера SxN, где S N, i 1,S; j

0 1,N, т.е. Ys AXN.

Для этого на первый информационный вход первого ПЭ подается нулевой код, на вход 16 управления режимом подается уровень О, после чего в блоке 12 УС счетчик 34

5 считает по модулю S, счетчик 35 считает по модулю (N+1), в блоке 12 ВКМ будет выдаваться первая страница хранящейся информации; коммутаторы 2 и 3 всех ПЭ подключают свои вторые входы к выходу,

0 шинные формирователи 4 переключаются на прием информации с шины данных 18, на втором входе блока 10 элементов И устанавливается уровень 1, позволяющий прохождению информации с выхода сумма5 тора-вычитателя 8 к входам второго регистра 11. Подключение -гоПЭ к общей шине 18 происходит в том случае, если на вход дешифратора 1 подается код числа J. Если на его вход подается нулевой код, то ни один ПЭ не подключается через свой шинный

формирователь 4 к общей шине 18. На третьи информационные входы ПЭ подаются столбцы матрицы А так, чтобы на J-й ПЭ подавался j-й столбец. Причем, 0+1)и столбец подается с временным запаздыванием в один такт по отношению к j-му столбцу. Координаты вектора XN подаются последовательно на шину 18 и Xj-координата записывается в первый регистр 7 J-ro ПЭ по переднему фронту тактового импульса, приходящего с выхода 22 блока 12 УС, при условии, что на вход дешифратора 1 подается код числа. Временные диаграммы, поясняющие организацию вычислительного процесса при первом режиме работы процессора, приведены на фиг.З. В начальный момент на вход 15 предустановки подается импульс отрицательной полярно сти, устанавливающий на выходах 24 и 21 блока 12 УС нулевые коды. Из тактового сигнала, поступающего на вход 14, формируется с помощью счетчика 27 и дешифратора 28 три последовательности импульсов с частотой f fr/З, разделенных во времени. В дальнейшем везде будем обозначать сигнал, поступающий с 1-го выхода дешифратора 28 через S (f), где 1,3, а также будем под тактом работы процессора понимать период последовательности S (1). По переднему фронту импульсов последовательности S (1) происходит установка адреса на счетчике 34 и выдача коэффициентов матрицы на третьи информационные входы ПЭ. По переднему фронту импульсов последовательности S (2) в определенные интервалы времени (1 на входе 23) подаются коэффициенты вектора на общую шину 18, а также выполняется смена кода на входе дешифратора 1, По переднему фронту импульсов последовательности S (3) тактируется работа ПЭ и синхронизируется выдача вычисленных коэффициентов выходного вектора Y. В первом такте на шину данных 18 выставляется координата XL на вход дешифратора 1 подается код единицы, при котором происходит выборка кристалла шинного формирователя 4 первого ПЭ (считается, что выборка кристалла осуществляется единичным уровнем). По переднему фронту тактового импульса последовательности S (3) координата защелкивается в регистр 7 первого ПЭ. Во втором такте на третий информационный вход первого ПЭ подается элемент матрицы аи, на общую шину 18 выставляются координата хг, на вход дешифратора 1 - код двойки, при котором произойдет выборка кристалла шинного формирователя второго ПЭ. По условию матрица А является бинарной, т.е. а ±1. Сумматор-вычитатель 8 вычитает из операнда на первом входе операнд, присутствующий на втором входе, если на третьем информационном входе ПЭ присутствует низкий логический уровень операнда, и

складывает операнды, если уровень высокий. Значит элементу aij -1 соответствует О, aij 1 соответствует 1. По переднему фронту второго тактового импульса последовательности S (3) в регистр 11 первого ПЭ

0 заносится результат anxi, в регистр 7 вто- , рого ПЭ заносится координата Х2. В третьем такте на третий информационный вход первого ПЭ подается элемент матрицы 321, на общую шину выставляется координата хз, а

5 на вход дешифратора 1 - код числа три, при котором произойдет выборка кристалла шинного формирователя третьего ПЭ. По переднему фронту третьего импульса последовательности S (3) в регистр 11 первого ПЭ

0 запишется результат 321-xt, в регистр 11 второго ПЭ запишется anxi + 312x2, в регистр 7 третьего ПЭ запишется координата хз. На N-м такте будет записана последняя координата XN в регистр 7 N-ro ПЭ и ввод

5 информации прекратится, для чего в (N+1) такте на входе дешифратора 1 устанавливается нулевой код. В (N+1) такте на информационном выходе 25 процессора появится первая координата yi вектора YS. В после0 дующие такты выдаются остальные координаты, т.е. на (N + S)-M такте выдается координата YS. Процесс умножения последующих векторов на матрицу может выполняться поточно. Для этого на (5+1) такте, в

5 момент, когда в регистр 11 первого ПЭ запишется asxi, нужно в регистр 7 этого же ПЭ записать координату xi следующего вектора XN и тем самым начать процесс ввода его координат с общей шины 18.

0 Второй режим работы применяется для умножения вектора на бинарную матрицу в случае S « N. Число ПЭ равно S N. Временные диаграммы приведены на фиг.4. На вход 16 управления режимом работы про5 цессора подается уровень 1, после чего в блоке 12 УС счетчик 34 считает по модулю N, счетчик 35 считает по модулю (S+1), в блоке 13 ВКМ будет выдаваться вторая страница хранящейся информации, коммутаторы 2 и

0 3 всех ПЭ подключат свои первые входы к выходу, шинные формирователи 4 ПЭ переключаются для передачи информации на общую шину 18. На третьи информационные входы ПЭ подаются строки матрицы

5 А так, чтобы на i-й ПЭ подалась бы 1-я строка. Причем, (М)-я строка подается с временным запаздыванием в один такт по отношению к i-й. Координаты вектора X подаются последовательно на информаци- онный вход 17 процессора. По переднему

фронту импульсов последовательности S (1) происходит установка адреса на счетчике 34 и выдача коэффициентов матрицы на третьи информационные входы ПЭ (аналогично режиму 1), По переднему фронту импульсов последовательности S (2) синхронизируется подача на вход 17 координат вектора X, в определенные моменты времени (1 на входе 23) выполняется смена кода на входе дешифратора 1; синхронизируется выдача вычисленных координат вектора Y (если 1 на входе 23, однако не ранее, чем через S тактов после предустановки). По переднему фронту импульсов последовательности S (3) тактируется работа ПЭ. В первом такте после предустановки процессора на вход 17 подается координата xi, на вход дешифратора код единицы. В результате на выходе элемента И-НЕ 9 первого ПЭ появляется уровень О, который запретит прохождение информации с выхода сумма- тора-вычитателя 8 к регистру 11 через блок 10 элементов И, По переднему фронту первого импульса последовательности S (3) в регистр 7 запишется координата XL а в ре- гистр 11 нулевой код. Во втором такте на вход 17 подается координата ха, на вход дешифратора 1 - код двойки, на третий информационный вход первого ПЭ - элемент матрицы аи.

По переднему фронту второго импульса последовательности S (3) для первого ПЭ в регистр 11 запишется результат anxi, а в регистр 7 координата Х2. Координата xi перепишется в регистр 7 второго ПЭ, а в ре- гистр 11 запишется нулевой код. На третьем такте на вход 17 подается координата хз, на вход дешифратора 1 -код тройки, на третий информационный вход первого ПЭ подается элемент 312, на третий информационный вход второго ПЭ подается элемент aai. По приходу третьего импульса последовательности S (3) для первого ПЭ в регистре 11 запишется сумма anxi + 312x2, в регистр 7 координата хз. Во второй ПЭ в регистр 11 запишется результат 321x1, в регистр 7 перепишется координата Х2. В третьем ПЭ в регистр 11 запишется нулевой код, а в регистр 7 координата xi. Таким образом, в первые S тактов производится последовательная очистка регистра 11, который вместе с сумматором-вычитателем 8 образуют накапливающий сумматора и начинает формироваться результат умножения вектора на 1-ю строку матрицы. С (S+1)-ro до №-го такта на входе дешифратора 1 присутствует кулевой код и выборка кристаллов шинных формирователей не производится. Процессор может умножать вектор на матрицу поточно. Опишем, как происходит вывод

координат вектора YS и одновременный ввод координат следующего вектора XN На (N+1)-M такте в регистре 7 первого ПЭ записана координата, а на выходе сумма- тора-вычитателя 8 уже сформирована координата yi вектора YS. На информационный вход 17 подается координата xi следующего вектора, а на вход дешифратора 1 - код единицы. В результате происходит выборка кристалла шинного формирователя 4 первого ПЭ и координата yi выдается на общую ишну 18. Этот же сигнал управления с выхода дешифратора 1 установит О на выходе элемента 9 И-НЕ первого ПЭ, что запретит прохождение информации с выхода сумма- тора-вычитателя 8 на вход регистра 11 через блок 10 элементов И. На входе регистра 11 устанавливается нулевой код. Положительным фронтом импульса последо- ва- тельности S (3) в регистр 7 первого ПЭ запишется координата XL а регистр 11 об- нулится и выдача координаты yi прекращается. Таким образом на (N+S)-M шаге на общую шину 18 выдается координата ys вектора YS.

Формула изобретения 1. Процессор для умножения вектора на матрицу размером SxN, содержащий S + N-1 последовательно соединенных процессорных элементов, причем первый ин- формационный вход 1-го процессорного элемента (i 2,S + N-1) соединен с первым информационным выходом (Ы)-го процессорного элемента, а первый информационный выход последнего процессорного элемента является информационным выходом процессора, отличающийся тем, что, с целью расширения области применения за счет возможности умножения вектора на бинарную матрицу и упрощения процессора, он содержит К последовательно соединенных процессорных элементов (К S при S N и К N при S N), дешифратор, блок управления и синхронизации и блок выдачи коэффициентов матрицы, причем второй информационный вход первого процессорного элемента является информационным входом процессора, второй информационный выход 1-го процессорного элемента (i 1,K) соединен с вторым информационным входом }+1)-го процессорного элемента, первые входы управления всех процессорных элементов соединены с входами управления блока управления и синхронизации и блока выдачи коэффициентов матрицы и являются входом управления режимом работы процессора, тактовый вход и вход предустановки блока управления и синхронизации являются тактовым входом и входом предустановки процессора соответственно, первый выход управления блока управления и синхронизации соединен с входом дешифратора, К выходов которого соединены соответствен- но с вторыми управляющими входами К процессорных элементов, первый и второй тактовые выходы блока управления и синхронизации являются первым и вторым тактовыми выходами процессора, третий тактовый выход блока управления и синхронизации соединен с тактовыми входами всех процессорных элементов, второй выход управления блока управления и синхронизации соединен с адресным входом блока выдачи коэффициентов матрицы, 1-й выход которого соединен с третьим информационным входом 1-го процессорного элемента, а (К+1)-й выход блока выдачи коэффициентов матрицы соединен с синхровходом блока управления и синхронизации, информационный вход-выход каждого процессорного элемента соединен с общей информационной шиной, являющейся информационным входом-выходом процессора

2, Процессор по п.1, о т л и ч а ю щ и и - с я тем, что процессорный элемент содержит первый и второй коммутаторы, первый и второй регистры, сумматор-вычитатель, элемент И, блок элементов И, элемент ИЛИ, элемент И-НЕ и шинный формирователь, причем управляющие входы первого и второго коммутаторов соединены с первым входом элемента ИЛИ, первым входом элемента И-НЕ, входом управления шинного формирователя и являются первым входом управления процессорного элемента, второй вход управления которого соединен с вторым входом элемента ИЛИ, вторым входом элемента И-НЕ и входом выборки кри- сталла шинного формирователя, первый вход элемента И соединен с тактовым входом второго регистра и является тактовым входом процессорного элемента, выход элемента ИЛИ соединен с вторым входом эле- мента И, выход которого соединен с тактовым входом первого регистра, выход первого коммутатора соединен с первым информационным входом сумматора-вы- читателя, второй информационный вход которого соединен с выходом первого регистра и является вторым информационным выходом процессорного элемента, выход второго коммутатора соединен с информационным входом первого регистра, разрядные выходы сумматора-вычитателя соединены соответственно с первыми входами элементов И блока и с группой входов шинного формирователя, группа входов-вы- ходое которого является информационным

входом-выходом процессорного элемента выход элемента И HF соединен с вторыми входами элементов И блока выходы которых соединены с информационным входом второго регистра, выход которого соединен с первым входом первого коммутатора и является первым информационным выходом процессорного элемента, первый информационный вход которого соединен с вторым входом первого коммутатора, второй информационный вход - с первым входом второго коммутатора, второй вход которого соединен с группой выходов шинного формирователя

информационный вход которою соединен с шиной логического нуля прямой выход первого триггера соединен г вторым входом первого элемента И

Zk

Фаг. г

Фаг.З

r

Фаг Л

Ь

Авторы

Даты

1992-07-30—Публикация

1990-06-22—Подача