/с

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Масштабный преобразователь кодов | 1988 |

|

SU1569994A1 |

| Способ определения частотной характеристики испытуемого объекта и устройство для его осуществления | 1984 |

|

SU1223074A1 |

| Цифровой измеритель скважностипРяМОугОльНыХ иМпульСОВ | 1979 |

|

SU808955A1 |

| Способ измерения длительности периодических импульсов | 1986 |

|

SU1390596A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 1991 |

|

RU2023309C1 |

| Измеритель разности фаз | 1990 |

|

SU1800382A1 |

Изобретение относится к измерительной технике и может использоваться в аналого-цифровых преобразователях информации. Цель изобретения - повышение точности и достоверности измерения временных интервалов и периода частотно-модулированных последовательностей импульсов. Устройство содержит вход 1, пороговый блок 2, RS-триггер 3, элемент И 5, генератор 4 импульсов, счетчик 6 импульсов, элемент ИЛИ 7, регистр 8, триггер 9. За счет введения новых элементов и блоков, элемента И-ИЛИ 10, блока совпадения 11, блока 12 управления, формирователя 13 импульсов, делителя 14 частоты на два и образования новых связей цель изобретения достигается в результате исключения потери информации при совпадении границ измеряемых временных интервалов с импульсами последовательности тактовых импульсов. 4 з.п. ф-лы, 3 ил.

о

vj hO

Изобретение относится к измерительной технике и может быть использовано в аналого-цифровых преобразователях информации.

Цель изобретения - повышение точности и достоверности измерения случайных временных интервалов.

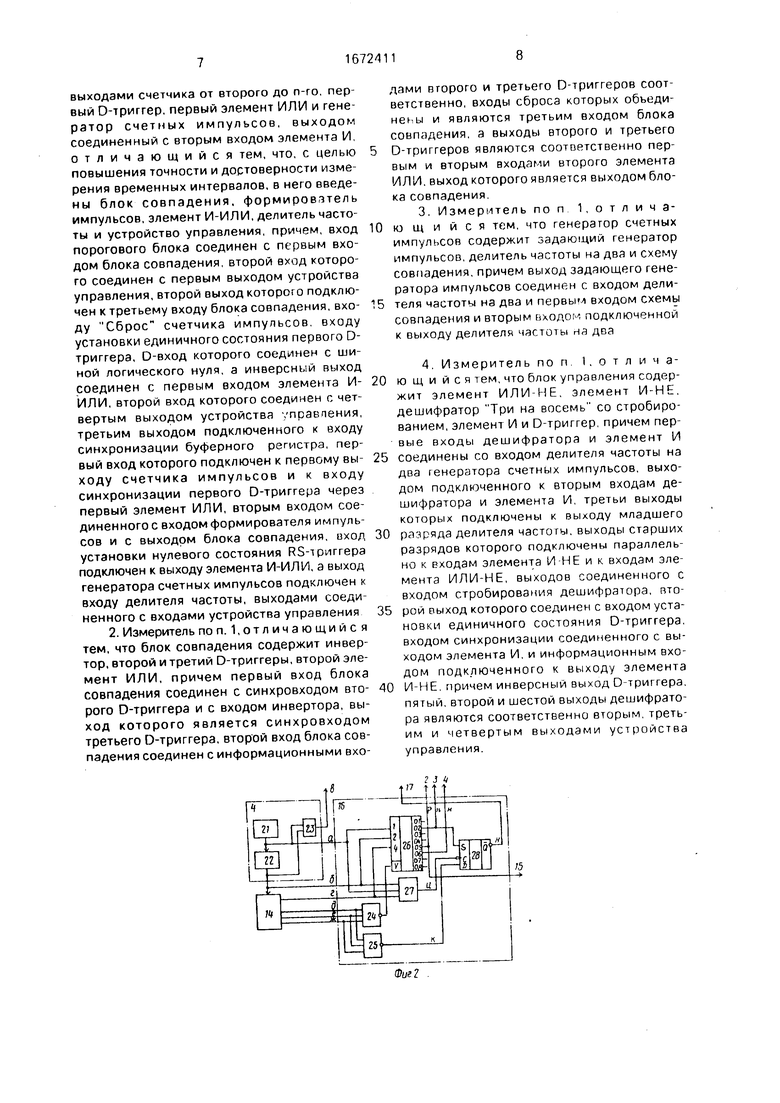

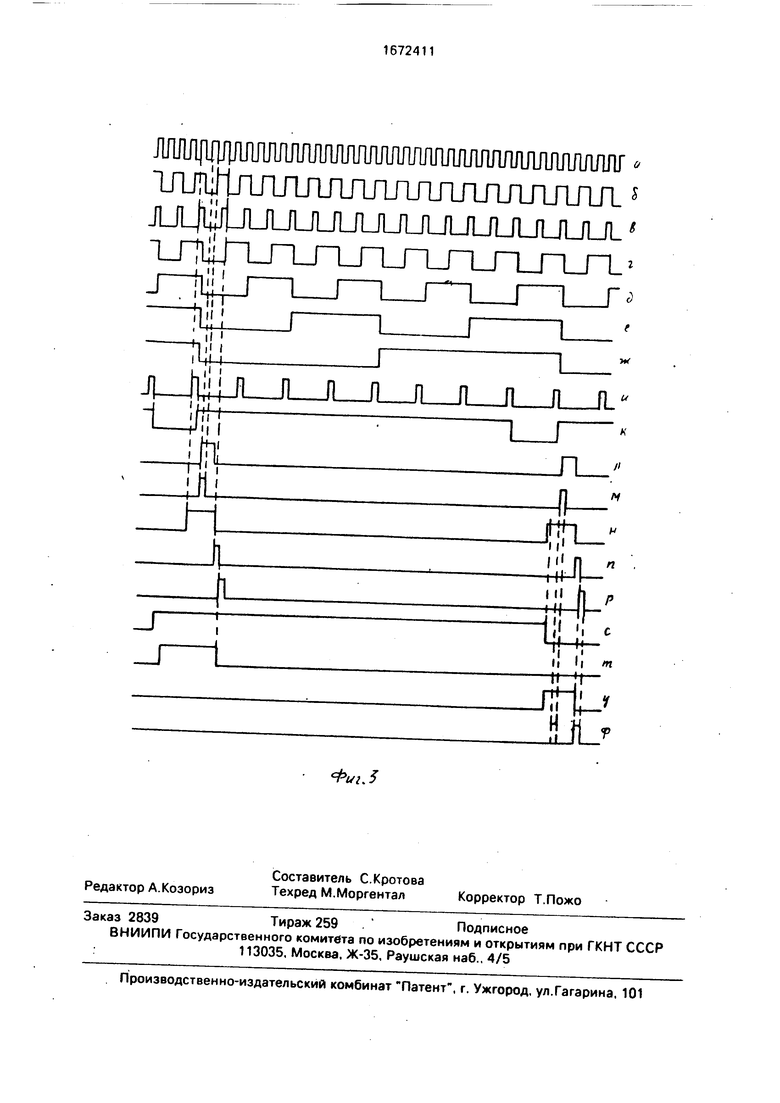

На фиг. 1 приведена функциональная схема измерителя временных интервалов; на фиг. 2 - схема устройства управления совместно с генератором счетных импульсов и делителем частоты; на фиг. 3 - времен- ные диаграммы работы устройства измерителя временных интервалов.

Устройство содержит вход 1 устройства, пороговый блок 2, служащий для формирования старт-импульсов из переднего или заднего фронтов входного сигнала, RS-триггер З, генератор 4 счетных импульсов, элемент И 5, счетчик 6 импульсов, первый элемент ИЛИ 7, буферный регистр 8, первый D-триггер 9, элемент И-ИЛИ 10, блок 11 совпадения, устройство 12 управления, формирователь 13 импульсов, делитель 14 частоты, шину 15, выходы 16 буферного регистра 8, причем вход 1 устройства последовательно соединен с пороговым блоком 2, RS-триггером З, генератор 4 импульсов соединен с вторым входом первого элемента И 5, первым входом которого является выход RS-триггера З, выход элемента И 5 является входом синхронизации счетчика б импульсов, первый выход которого является первым входом второго элемента ИЛИ 7. выход которого является первым входом регистра 8, первый выход счетчика 6 соединен с син- хровходом триггера 9, информационный вход которого соединен с шиной логического О, а инверсный выход является первым входом элемента И-ИЛИ 10, выход которого является входом сброса первого триггера 3, первый вход блока 11 совпадения соединен с входом устройства, с входом порогового блока, второй вход блока 11 совпадения является первым выходом устройства 12 управления, третий вход блока 11 совпадения соединен с входом сброса счетчика 6 импульсов, входом установки триггера 9 и является вторым выходом устройства 12 управления, выход блока 11 совпадения является вторым входом элемента ИЛИ 7 и входом формирователя 13 импульсов, выход которого является третьим входом элемента И-ИЛИ 10, второй вход которого является четвертым выходом устройства 12 управления, выход генератора 4 соединен с входом делителя 14 частоты на два, выходы которого соединены с соответствующими входами устройства.12 управления, пятый выход которого подключен к шине 15 измерителя, а

выходы регистра 8 являются выходами 16 устройства.

Блок 11 совпадения состоит из инвертора 17. второго 18 и третьего 19 D-триггеров

и элемента ИЛИ 20, служит для формирования импульсов переменной длительности при совпадении переднего или заднего фронта входного сигнала с так называемой зоной неопределенности.

0Генератор 4 счетных импульсов содержит задающий, генератор 21, делитель 22 частоты на два, схему 23 совпадения.

Устройство 12 управления содержит элемент ИЛИ-НЕ 24. элемент И-НЕ 25, де5 шифратор 26, элемент И 27 и D-триггер 28. Устройство работает следующим образом.

В исходном состоянии при отсутствии сигналов на входе 1 устройства RS-триггер

0 3, счетчик 6, второй 18 и третий 19 D-тригге- ры находятся в нулевом состоянии, а первый D-триггер 9 - в единичном состоянии. Уровень логического О на выходе RS-триг- гера 3 запрещает прохождение счетных им5 пульсов (фиг. Зв) через элемент И 5 на счетный вход счетчика 6. Уровень логического О на выходе первого D-триггера 9 запрещает прохождение импульсов (фиг. Зм) через элемент И-ИЛИ 10 на вход установки

0 нулевого состояния RS-триггера З. Уровни логического О на выходах второго 18 и третьего 19 D-триггеров обеспечивают непосредственную передачу информации с первого выхода счетчика 6 через первый

5 элемент ИЛИ 7 на первый вход буферного регистра 8, которая переписывается на его выходы 16 каждым импульсом с третьего выхода устройства 12 управления.

С приходом фронта входного сигнала в

0 интервале между импульсами зоны неопределенности (например, передний фронт импульса на фиг. Зс) устройство работает как обычный измеритель интервалов времени, реализующий метод последовательного

5 счета счетных импульсов в течение интервала, ограниченного старт- и стоп-импульса- ми. При этом с каждым фронтом входного сигнала пороговый блок 2 формирует импульс, переключающий RS-триггер З в еди0 ничное состояние. Уровень логической 1 на его выходе разрешает прохождение импульсов генератора 4 счетных импульсов через элемент И 5 на счетный вход счетчика. Первый же импульс, появившийся на пер5 вом выходе (младшего разряда) счетчика 6, переключает первый D-триггер 9. Уровень логической 1, появившийся на его выходе, разрешает прохождение основных импульсов сброса (фиг. Зм) с четвертого выхода устройства 12 управления через элемент ИИЛИ 10 на вход установки нулевого состояния RS-триггера З. Первый же импульс (фиг. Зм), поступивший на вход установки нулевого состояния RS-триггера З, устанавливает его в О, что приводит к запиранию элемен- та И 5 и прекращению поступления счетных импульсов на счетный вход счетчика 6, после чего импульсы (фиг. Зп) переписывают информацию с выходов счетчика 6 в буферный регистр 8, а импульсы (фиг. Зр)с второго выхода устройства 12 управления сбрасывают в О счетчик 6 и устанавливают в единичное состояние первый D-триггер 9. Блок 11 совпадения при этом не работает, так как на D-входах второго 18 и третьего 19 D-тригге- ров в момент прихода фронта входного сигнала поддерживается уровень логического О, снимаемый с первого выхода устройства 12 управления, поэтому на выходе второго элемента ИЛИ 20 установлено напряжение логического О, не влияющее на передачу значения младшего разряда на первом выходе счетчика б через первый элемент ИЛИ к первому входу буферного регистра 8, и, кроме того, формирователь импульсов 13 не формирует дополнительных импульсов сброса. При каждом появлении фронта входного сигнала в интервале между импульсами зоны неопределенно- сти(фиг. Зн)описанная процедура повторя- ется.

С приходом положительного или отрицательного фронта входного сигнала в некоторый момент времени, совпадающий с импульсом зоны неопределенности (фиг. Зн), например, задний фронт импульса на фиг. Зс, наряду со срабатыванием порогового блока 2 и RS-триггера З переключается либо второй D-триггер 18. либо третий D- триггер 19. Уровень логической 1, появив- шийся на одном из входов второго элемента ИЛИ 20, передается на его выход (фиг. Зт), откуда поступает на второй вход первого элемента ИЛИ 7 и на вход формирователя 13 импульсов и поддерживается до тех пор, пока появившийся на третьем выходе устройства 12 управления импульс (фиг. Зп) не перепишет логическую 1 с выхода первого элемента ИЛИ 7 в младший разряд буферного регистра 8, после чего импульс (фиг. Зр) установит счетчик 6 и второй 18 и третий 19 D-триггеры в нулевое состояние, а формиро- ватель 13 импульсов сформирует короткий дополнительный импульс сброса (фиг. Зф) по спаду импульса на его входе, который передастся через элемент И-ИЛИ 10 на вход установки нулевого состояния RS- триггера 3.

Таким образом, если фронт входного сигнала попадает в интервал времени, ограниченный зоной неопределенности (фиг Зн), то обеспечивается запись логической 1 в младший разряд буферного регистра 8 независимо от состояния младшего разряда на первом выходе счетчика 6.

При появлении фронта входного сигнала одновременно с границей зоны неопределенности (фиг. Зн), либо в интервале между передней границей зоны неопределенности и основным импульсом сброса, на четвертом выходе устройства 12 управления (фиг. Зм) возможно появление сдвоенных импульсов сброса, основного и дополнительного (показано пунктиром на фиг. Зф). Однако это не приводит к искажению информации на выходе буферного регистра 8, так как при этом происходит дублирование информации на его входе, т.е. счетчик б просчитывает только один счетный импульс (фиг. Зв), формируя на первом входе первого элемента ИЛИ 7 логическую 1, а на втором входе первого элемента ИЛИ 7 тоже формируется логическая 1 в результате срабатывания блока 11 совпадения.

Информация о сдвиге фронтов импульсов входного сигнала относительно положе- ния тактовой последовательности импульсов, представленная в виде кода на выходах 16 буферного регистра 8, сохраняется неизменной в интервале между импульсами (фиг. Зп). В течение этого времени информация может быть использована для дальнейшей обработки или индикации. Синхронизация устройств - потребителей этой информации осуществляется тактовыми импульсами (фиг. Зп), снимаемыми с шины 15.

Таким образом, введение в измеритель временных интервалов блока совпадения, формирователя импульсов, элемента И- ИЛИ. делителя частоты и устройства управления позволяет повысить точность измерения случайных временных интервалов и периода частотно-модулированных последовательностей импульсов за счет исключения потери информации при совпадении границ измеряемых временных интервалов с импульсами последовательности тактовых импульсов. Величина остаточной ошибки измерения случайных временных интервалов определяется разрядностью используемого кода и не превышает одной единицы младшего разряда. При увеличении разрядности кода эта ошибка может быть сделана достаточно малой.

Формула изобретения

выходами счетчика от второго до п-го, первый D-триггер. первый элемент ИЛИ и генератор счетных импульсов, выходом соединенный с вторым входом элемента И, отличающийся тем, что, с целью повышения точности и достоверности измерения временных интервалов, в него введены блок совпадения, формирователь импульсов, элемент И-ИЛИ, делитель частоты и устройство управления, причем, вход порогового блока соединен с первым входом блока совпадения, второй вход которого соединен с первым выходом устройства управления, второй выход которого подключен к третьему входу блока совпадения, входу Сброс счетчика импульсов, входу установки единичного состояния первого D- триггера, D-вход которого соединен с шиной логического нуля, а инверсный выход соединен с первым входом элемента И- ИЛИ, второй вход которого соединен с четвертым выходом устройства управпения, третьим выходом подключенного к входу синхронизации буферного регистра, первый вход которого подключен к первому выходу счетчика импульсов и к входу синхронизации первого D-триггера через первый элемент ИЛИ, вторым входом соединенного с входом формирователя импульсов и с выходом блока совпадения, вход установки нулевого состояния RS-триггера подключен к выходу элемента И-ИЛИ, а выход генератора счетных импульсов подключен к входу делителя частоты, выходами соединенного с входами устройства управления

импульсов содержит задающий генератор импульсов, делитель частоты на два и схему совпадения, причем выход задающего генератора импульсов соединен с входом дели- теля частоты на два и первым входом схемы совпадения и вторым входом подключенной к выходу делителя частоты на два

соединены со входом делителя частоты на два генератора счетных импульсов, выходом подключенного к вторым входам дешифратора и элемента И, третьи выходы которых подключены к выходу младшего

разряда делителя частоты, выходы старших разрядов которого подключены параллельно к входам элемента И-НЕ и к входам элемента ИЛИ-НЕ, выходов соединенного с входом стробировамия дешифратора, второй выход которого соединен с входом установки единичного состояния D-триггера. входом синхронизации соединенного с выходом элемента И, и информационным входом подключенного к выходу элемента

И-НЕ, причем инверсный выход D-триггера. пятый, второй и шестой выходы дешифратора являются соответственно вторым, третьим и четвертым выходами устройства управления.

МЛЛЩЩШ1Ш1ШШЛШШЛЛЛЛЛШиШШ1ЛЛЛШШПШ

ТЛ 1|11ЛЛЛЛГ1Г1

JUl iijUULJULJUUl

| Устройство для измерения временныхиНТЕРВАлОВ | 1979 |

|

SU842696A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1991-08-23—Публикация

1988-12-06—Подача