(5Ю ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический аналого-цифровой преобразователь | 1981 |

|

SU947874A1 |

| Интегратор | 1988 |

|

SU1596353A1 |

| Способ широтно-импульсного преобразования напряжения и широтно-импульсный модулятор | 1986 |

|

SU1361709A1 |

| Интегратор для модуляционного радиометра | 1986 |

|

SU1401424A1 |

| Интегратор | 1981 |

|

SU955106A1 |

| Интегратор | 1979 |

|

SU834715A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Интегратор с управляемым ограничением выходного сигнала | 1986 |

|

SU1305724A1 |

| Устройство для усреднения импульсной последовательности | 1988 |

|

SU1524071A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в устройствах .автоматики и измерительной техники, в частности в устройствах сжатия динамического диапазона и других функциональных преобразователях.

Известны матеграторы, в которых логарифмическое сжатие осуществлено путем подключения к выходу интегратора комплементарных логарифмических преобразователей l,

Недостаток известных интеграторов с логарифмическим сжатием результата интегрирования заключается в их сложности, так как в интегратор вводятся дополнительные операционные усилители.

Кроме того, ухудшается отношение сигнал/шум, особенно для слабых сигналов. Это вызвано наличием шумовой составляющей во входном каскаде логарифматора,а также воздействием наводок на проинтегрированный сигнал до лога;;:

рифмического преобразования его, несмотря на непосредственную близость интегратора и логарифматора.

Наиболее близок к предлагаемому по технической сущности интегратор, содержащий токозадающую цепь, выходом связанную с одним из концов конденсаторов и входом операционного усилителя f2.

Недостатком данного интеграто)й

10 является невозможность выполнения ло гарифмического сжатия одновременно с интегрированием, т.е. он имеет ограниченные функциональные возможности.

15

Цель изобретения - расширение функциональных возможностей интегратора за счет логарифмического сжатия проинтегрированного сигнала.

Поставленная цель достигается

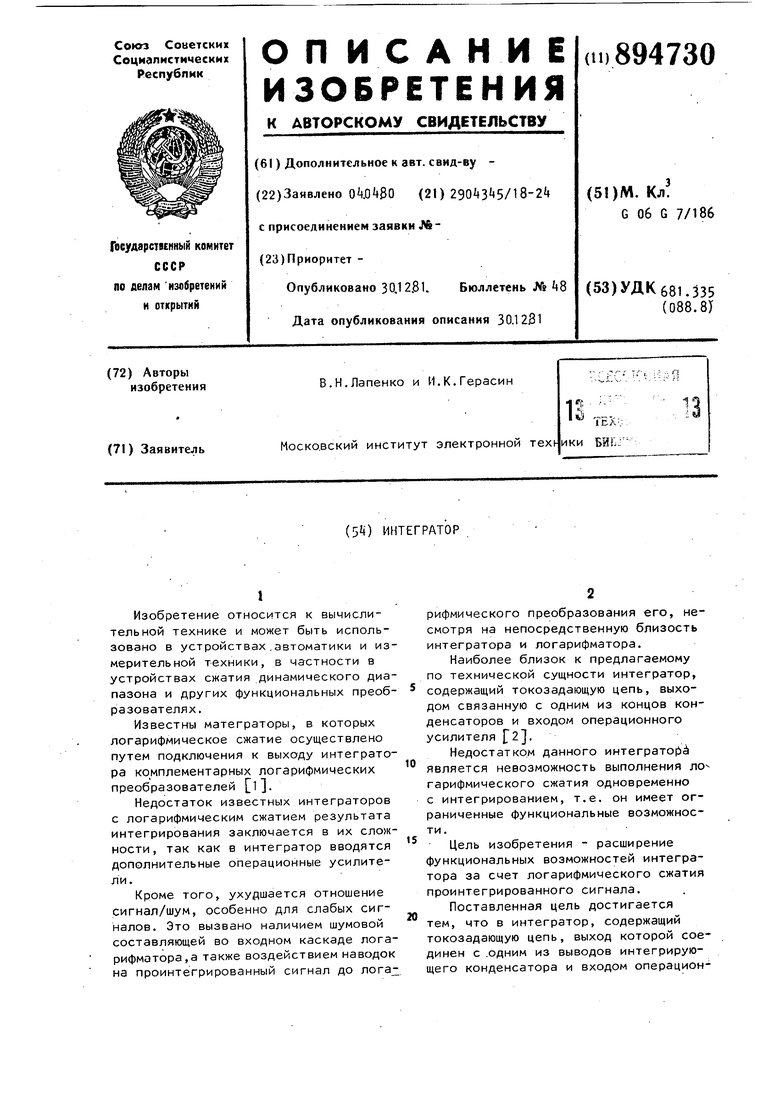

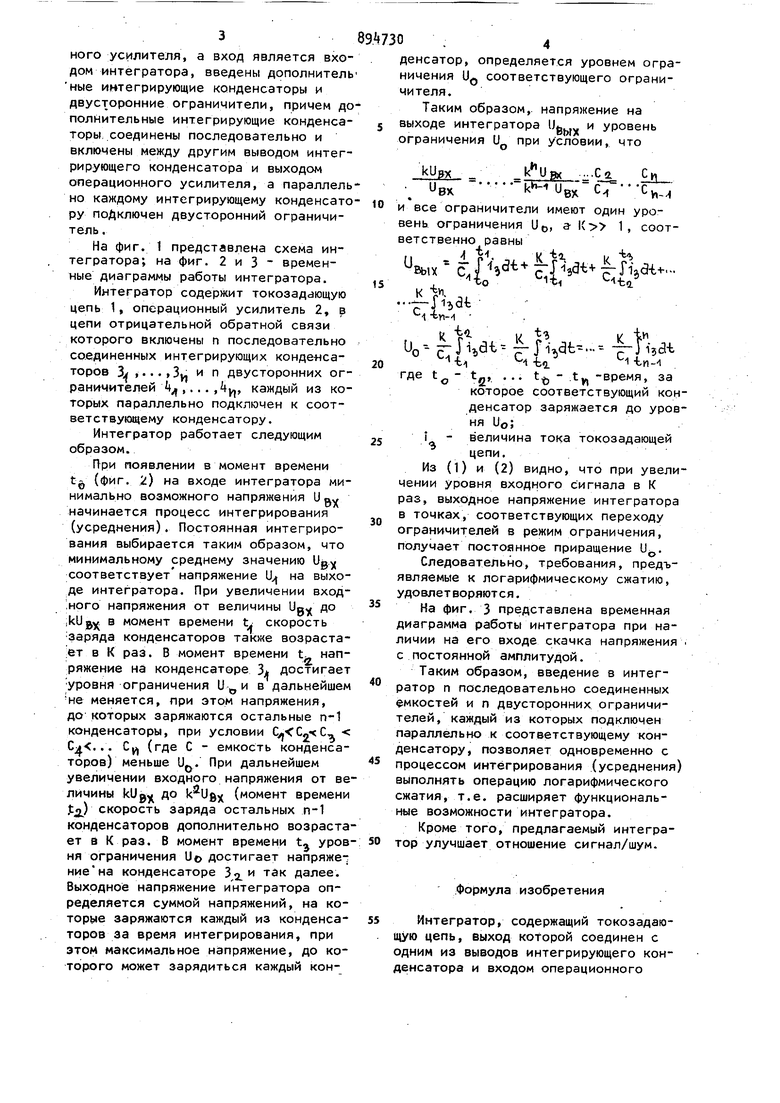

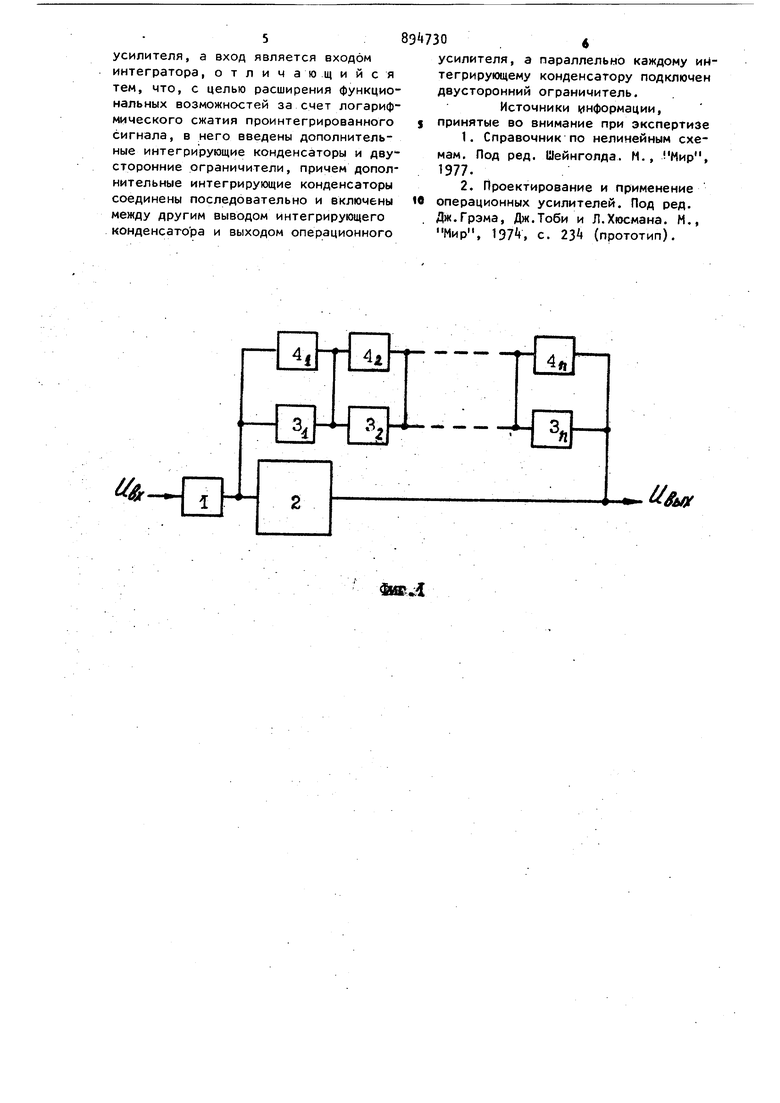

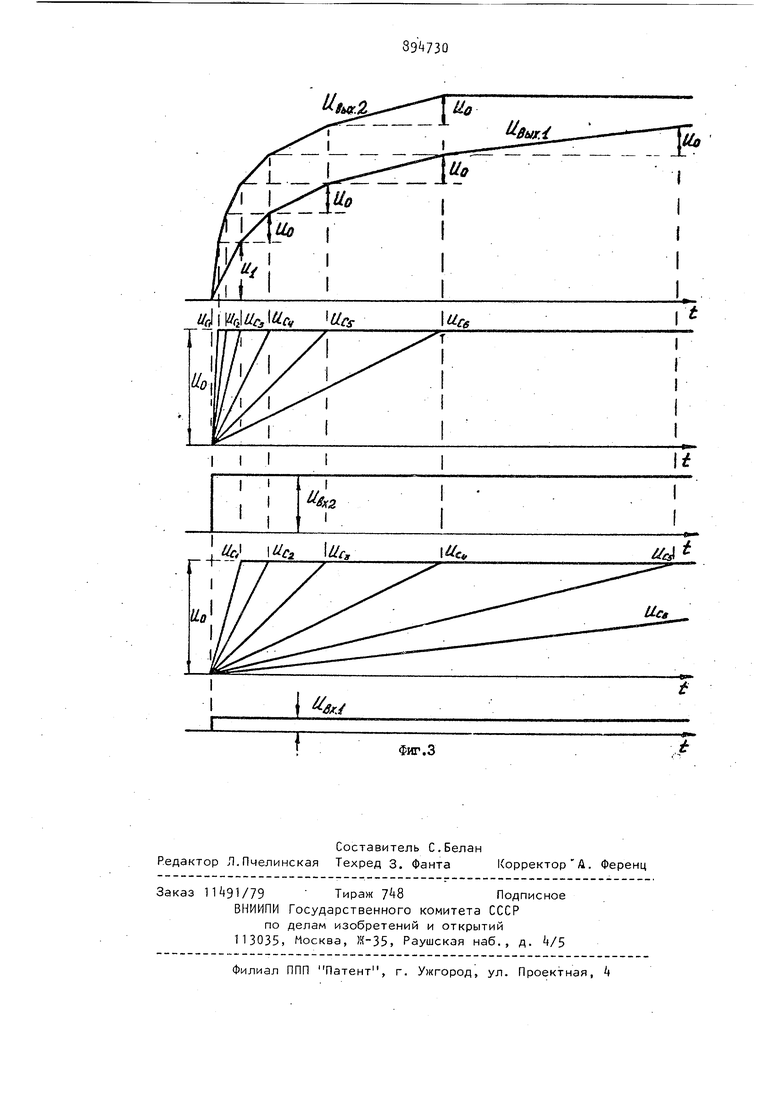

20 тем, что в интегратор, содержащий токозадающую цепь, выход которой соединен с .одним из выводов интегрирующего конденсатора и входом операционного усилителя, а вход является входом интегратора, введены дополнитель ные интегрирующие конденсаторы и двусторонние ограничители, причем до полнительные интегрирующие конденсаторы, соединены последовательно и включены между другим выводом интегрирующего конденсатора и выходом операционного усилителя, а параллель но каждому интегрирующему конденсато ру подключен двусторонний ограничитель . На фиг. 1 представлена схема интегратора; на фиг. 2 и 3 временные диаграммы работы интегратора. Интегратор содержит токозадающую цепь 1, операционный усилитель 2, в цепи отрицательной обратной связи которого включены п последовательно соединенных интегрирующих конде-нсаторов 3 ,..., Зу. и п двусторонних ограничителей i ,... ,4у|, каждый из которых параллельно подключен к соответствующему конденсатору. Интегратор работает следующим образом. появлении в момент времени t (фиг. 2) на входе интегратора минимально возможного напряжения U «у начинается процесс интегрирования (усреднения). Постоянная интегрирования выбирается таким образом, что минимальному среднему значению Ug.y соответствует напряжение Щ на выходе интегратора. При увеличении вход,ного напряжения от величины Ugy до ikUgy в момент времени t, скорость заряда конденсаторов также возрастает в К раз. В момент времени t напряжение на конденсаторе 3 достигает уровня ограничения U , и в дальнейшем не меняется, при этом напряжения, АО которых заряжаются остальные п-1 С., конденсаторы, при условии СА... С (где С - емкость конДенсаторов) меньше U... При дальнейшем увеличении входного напряжения от личины kUgy до ( (момент времени з) скорость заряда остальных п-1 конденсаторов дополнительно возраста ет в К раз. В момент времени Ц уров ня ограничения Uo достигает напряжениена конденсаторе З. и тик далее. Выходное напряжение интегратора определяется суммой напряжений, на которуе заряжаются каждый из конденсаторов за время интегрирования, при этом максимальное напряжение, до которого может зарядиться каждый конденсатор, определяется уровнем ограничения UQ соответствующего ограничителя. Таким образом, напряжение на выходе интегратора и уровень ограничения Ц р при условии, что kUgx, .С С и все ограничители имеют один уровень ограничения Ut,, а- К 1 , соответственно равны V, .. Kt. -I fei.К г I/ t) Bb,x- cJV i: 3ai rijai... toti-bi -f|i3at --1 -tn-i , к К p. .. Oo-fji p-Iisai - ji, i di i-tn 4 4-, c-t-fci Де tg,... t -время, за которое соответствующий конденсатор заряжается до уровня UoJ i - величина тока токозадающей цепи. Из (1) и (2) видно, что при увеличении уровня входного сигнала в К раз, выходное напряжение интегратора в точках, соответствующих переходу ограничителей в режим ограничения, получает постоянное приращение U,. Следовательно, требования, предъявляемые к логарифмическому сжатию, удовлетворяются. На фиг. 3 представлена временная диаграмма работы интегратора при наличии на его входе скачка напряжения . с постоянной амплитудой. Таким образом, введение в интегратор п последовательно соединенных емкостей и п двусторонних ограничителей, каждый из которых подключен параллельно к соответствующему конденсатору, позволяет одновременно с процессом интегрирования (усреднения) выполнять операцию логарифмического сжатия, т.е. расширяет функциональные возможности интегратора. Кроме того, предлагаемый интегратор улучшает отношение сигнал/шум. Формула изобретения Интегратор, содержащий токозадающую цепь, выход которой соединен с одним из выводов интегрирующего конденсатора и входом операционного

усилителя, а вход является входом интегратора, отличающийся тем, что, с целью расширения функцио нальных возможностей за счет логариф мического сжатия проинтегрированного сигнала, в него введены дополнительные интегрирующие конденсаторы и дву сторонние ограничители, причем допол нительные интегрирующие конденсаторы соединены последовательно и включены между другим выводом интегрирующего конденсатора и выходом операционного

Э 730«

усилителя, а параллельно каждому интегрирующему конденсатору подключен двусторонний ограничитель.

Источники информации, принятые во внимание при экспертизе

Дж.Грэма, Дж.Тоби и Л.Хюсмана. М., Мир, 197, с. 23 (прототип).

Лв

//dlKJ o Ar л«а I /. Uc,

Авторы

Даты

1981-12-30—Публикация

1980-04-04—Подача