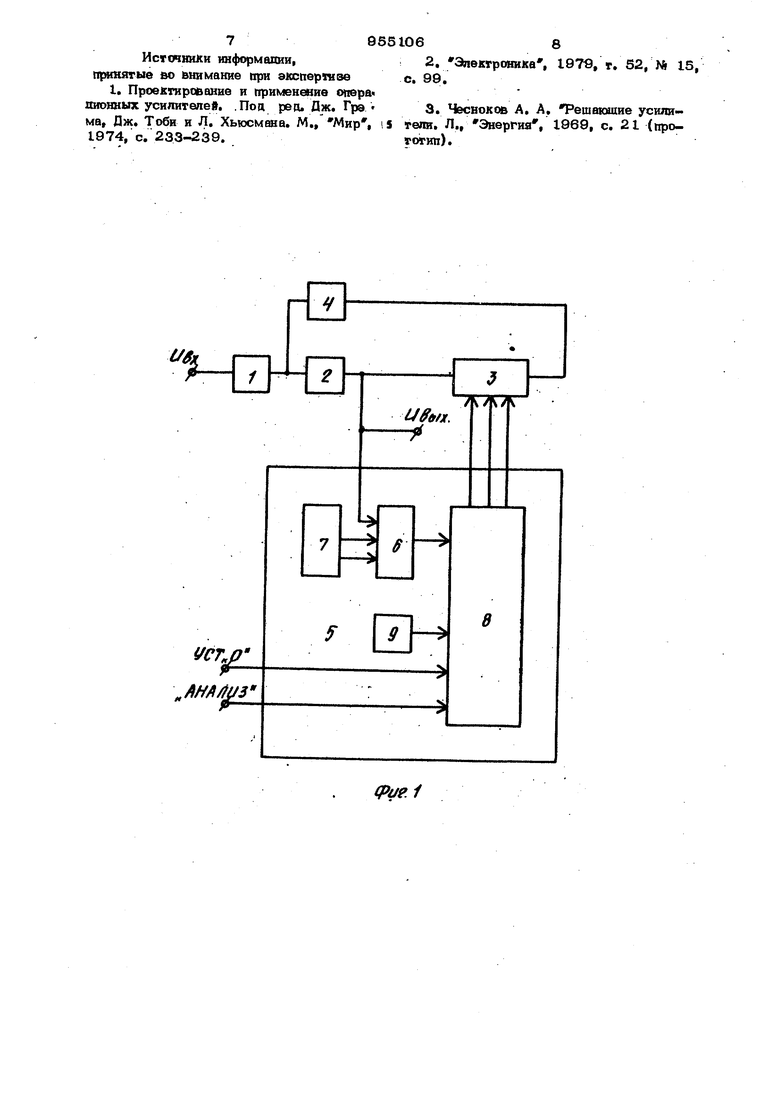

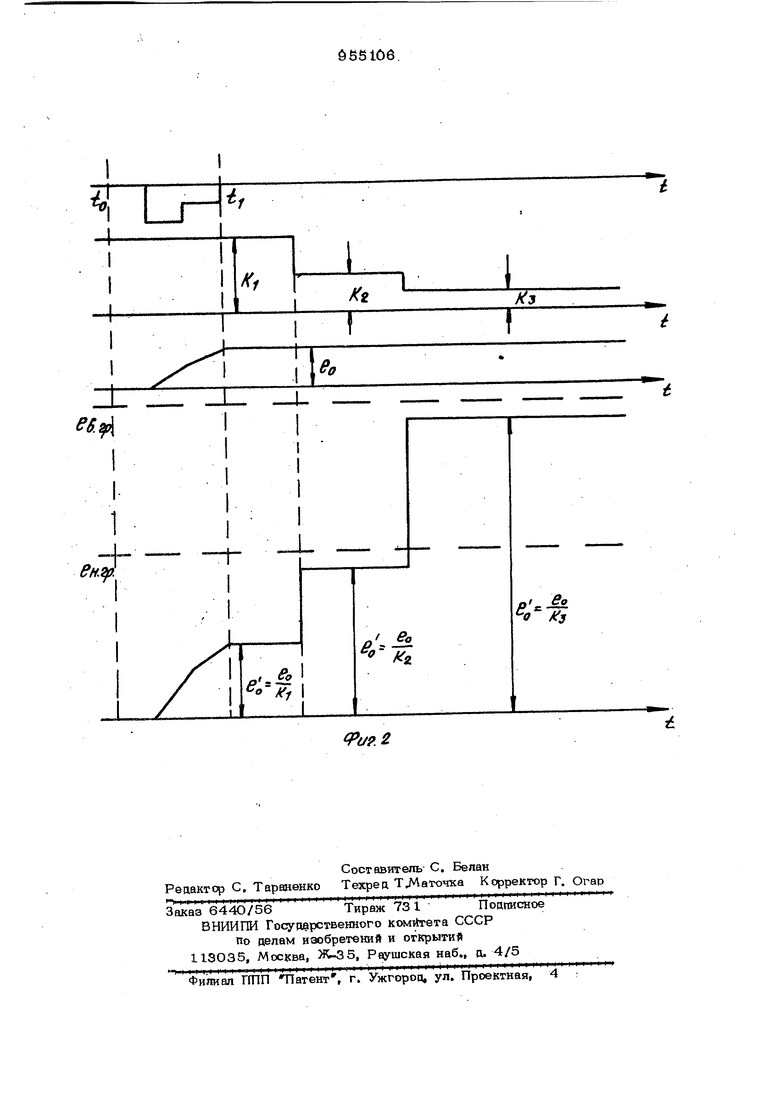

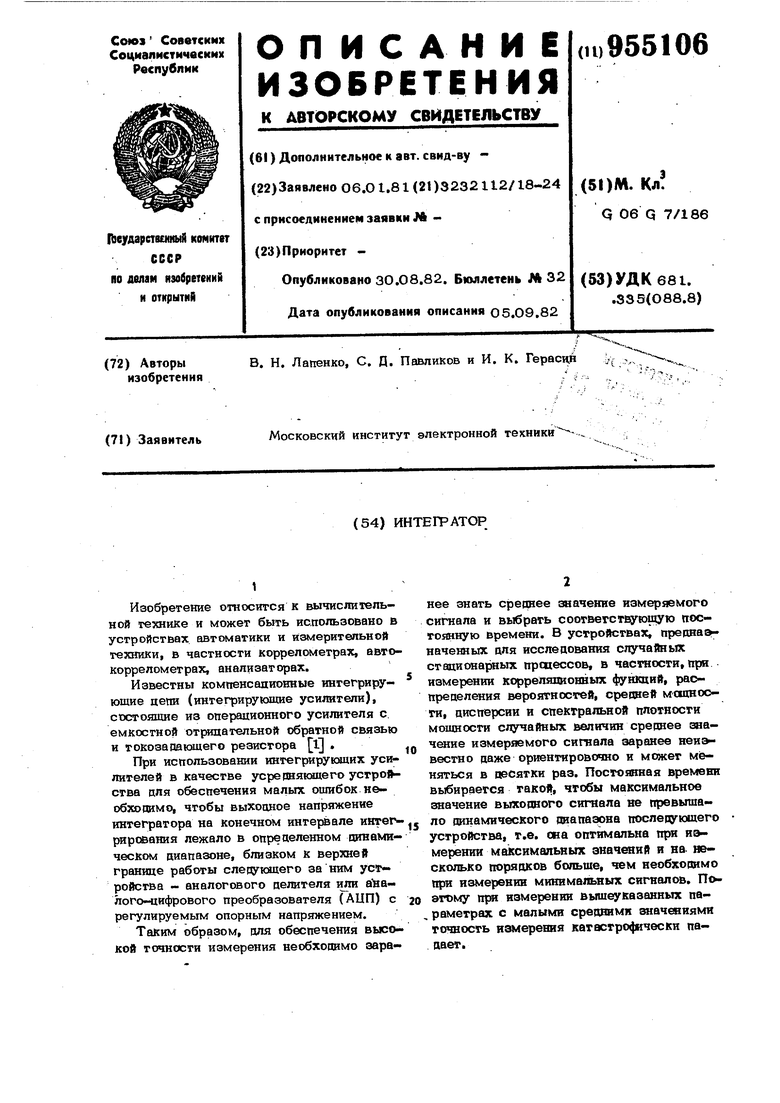

Изобретение относится к вычислительной технике и может быть использовано в устройствах автоматики и измерительной техники, в частности коррелометрах, автокоррелометрах, анализаторах. Известны компенсапионные интегрирующие цепи (интегрируюнше усилители), состоящие из операционного усилителя с емкостной отрицательной обратной связью и токозадающего резистора 1 . При использовании интегрирующих усилителей в качестве усредняющего устройства для обеспечения малых ошибок необходимо, чтобы выхоцное напряжение интегратора на конечном интервале ингегрирования лежало в определенном оинамн- ческом диапазоне, близком к верхней границе работы слетокяцего за ним устройства - аналогового делителя или айалого-цифрового преобразователя (АЦП) с регулируемым опорным напряжением. Таким образом, для обеспечения высокой точности измерения необходимо заранее знать среднее значение измеряемого сигнала и выбрать соответствующую постоянную времени. В устройствах, предназначенных для исследования случайных стационарных пршессов, в частности, при измерении корреляционных функций, распределения вероятностей, средней модности, дисперсии н спектральной плотности мощности случайных величин среднее значение измеряемого сигнала заранее неизвестно даже ориентировочно и может меняться в десятки раз. Постоянная времени выбирается такой, чтобы максимальное значение выходного сигнала не превышало динамического днапагюна последующего устройства, т.е. сна оптимальна при и мерении максимальных значений и на. несколько порядков больше, чем необходимо при измерении минимальных сигналов. Ut эгому щт измерении вышеуказанных параметрах с малыми срешгамк значениями точность намерения катастрофически падает. 395 Точность усреяне1шя может быть повышена п|эи использовании в АЦП ус ил ителя с программным коэффициентом усиления .2J.. . Однако это усложняет устройство и повышает его стоимссть. Наиболее близким к предлагаемому является интегратор, содержащий токозадающую цепь, выходом связанную с входом усилителя, в цепи отрицательной обратной связи, которого включены последовательно соединенные делитель напряжения и конденсатор. Д остоинством данного интегратора является простота, а гаКже возможность подстройки при помощи делителя постоянной интегрирования, вызванной разбросом емкости конденсатора. При этом необходимо отметить, что абсолютная величина переменного резистора, испольЕ геМого в качестве делителя, не влияет на точность интегратора, которая зависит только от отношения плеч переменного резистора. т.е. от коэффициента передачи делителя з Недостатком интегратора является ни кая точность при измерении случайных процессов, так Как заранее невозможно знать среднее значение измеряемого сигнала и установить необходимую величину постоянной времени интегрирования. Цель изобретения-- повышение точности интегрирования. Поставленная цель достигается тем, что в интегратор, содержащий токозадающую цепь, подключенную к вхочу операционного усилителя, выход которого является выходом .интегратора, и интегрирующий конденсатор, одна обкладка,, которого поцключена к входу операционного усилителя, введены блок с переменным коэффициентом ,передачи и блок управления, вход которог подключен к Выходу операционного усилит ля, а выход соединен с управляющим входом блока с переменным коэффициентом передачи, включенным между другой обкладкойИнтегрирующего конденсатора и выходом операционного усилителя, при этом блок управления содержит схему сравнения, орин из входов котооой являет ся первым входом блока управления, другие входы с выходами источни.ка опорньпс напряжений, а выход подключе к информаиионному входу сдаигового регистра, тактируюпшй вход которого соеданей с генератором тактовых импульсов, установочный вход сдвигового .регистра и вход раг ешения Ейлдются соответственно 6 установочным входом и входом разрешения блока управления. На (, 1 приведена функциональная схема интегратора;на фиг, 2 - временная диаграмма работы иитегратора. Интегратор содержит токозадающую цепь 1, операционный усилитель 2, блок 3 с переменным коэффициентом передачи 3, интегрирующий конденсатор 4, блок 5 управления. Выход операционного усилителя 2 CBSP- , зан с сигнальным входом блока 3 с переменным коэффициентом передачи (например, аттенюатором) и с сигнальным входом блока 5 управления, выходы которого подключены к управляющим входам блока 3 р Переменным коэффициентом передачи, выход которого через интегрирующий конденсатор 4 соединен с входом . операционного усилителя 2 и выходом токозадающей цепи 1. .БЛОК 5 управления содержит схему 6 сраШ1ения, источник 7 оперных, напряжений, сдвиговый регистр 8, генератор 9 тактовых импульсов. Вход схемы 6 сравнения связан с источником 7 опорных напряжений, а выходс входом сдвигового регистра 8, другой вход которого подключен к генератору 9 тактовых импульсов. Интегратор работает следуюцим образом. Одновременно с началом режима интегрирования (усреднения) (момент времени ip , фиг. 2), на управляющий вход блока 5 управления приходит импульс начальной установки, который блокирует сдвиг и устанавливает в нулевое состояние сдвиговый регистр 8, при этом на единичном входе его младшего разряда постоянно присутствует единица. Информация о состоянии каждого разряда регистра 8 с его выходов поступает на управляющие входы блока 3 с переменным коэффициентом передачи (аттенюатора). В результате чего коэффициент передачи блока 3 устанавливается максимальным и равен К , причем в режиме интегрирования (момент oтt(JДot ) коэффициент передачи блока 3 остается неизменным до прихода сигнала разрешения анализа на управляющий вход блока 5 управления. В момент времени Ь) процесс интегрирования (усреднения) заканчивается и интегратор переходит в режим хранения. К этому моменту времени напряжение на конденсаторе 4 достигает величины бр , а напряжение на вьйсоде усилителя 2 величины .Начальное значение постоянной времени интег5 9 ратора ьыбираегся т&ким, чтобы максимальная величина бд лежала в линейной области усилителя 2 и не превышала его динамического диапазон:а. Далее напряжение е с выхода усилителя 2 поступает на сигнальный вход блока 5 управления, т.е. на вход схемы б сравнения, на второй вход которого подается напряжение бц, с источ ника 7 опорных напряжений. Схема 6 сра& нения осуществляет сравнение по модулю напряжения ej, с напряжением б д-р ® работа схемы 6 сравнения описывается следующим выражением I, если leHe, Loi н.гр О, если1е ен,гр.,. гдeU(t) - напряжение на выходе схемы 6 сравнения. Если ej, лежит ниже нижней границы .ец,.р желаемого динамического циапазона работы (в котором обеспечивается тре буемая точность измерения), то сигнал запрета на Выходе схемы 6 сравнения отсутствует. Одновременно с началом режима хранения на другой управляющий вход блока 5 управления приходит сигнал разрешения анализа, в редуш тате чего с частотой следования генератора 9 тактовых импульсов осуществляется последовательное заполнение ешшицей разрядов в сдвиговом регистре 8 в направлении от младшего к старшему и соответственно происходит сТу пенчатое уменьшение коэффициента передачи блока 3 и он пршшмает значения Кл, К и т.д. При этом напряжение на выходе усилителя 2 будет ступенчато возрастать (фиг. 2). Если новое значение напряясения е на выходе усилителя 2 превысит 6 рр , то на выходе схемы б сравнения появляется сигнал запрета, который поступает на вхо сдвигового регистра 8, и сдвиг единицы в нем и, соответственно, изменение коэффициента передачи блока 3 (аттенюатора) прёкращается. При изменении коэффициента передачи блока 3 с К до К 2 или К напряжение на выходе блока 3 практически не изменится, так как оно определяется напряжением, до которого заряжён Кшденсатор 4. Напряжение на выходе усилителя будет равно1, , «, т.е, увеличится в - раз, что эквивалентно уменьшению постоянной времени интегратора в раз перед началом ин066тегрирова1П1я. В интересующем нас режиме Хранение дополнительное напряжение ошибки, возникающее за счет па цени л напряжения тока заряда конденсатора 4 на выходном сопротивлении блока 3, равно О, т.е. в этом режиме т еж заряда равен О (входным током ОУ пренебрегаем). В режиме интегрирования эту ошибку можно свести к минимуму соответствующим выбором аттенюатора (лока 3) с малым Вькодным сопротивлением. Таким образом, благодаря вьтолнению блока 3 с переменным коэффициентом передачи и введению блока управления появилась возможность изменять после интервала интегрирования постоя1П1ую времени, с которой происхорило 1штегрирование,что позволяет выбрать оптимальные постоягтые интегрирования при усреднении случайных параметров, вследствие чего точность повышается. Стоимость известных устройств с аналогичными точностными характеристиками на 200-300% выше. Формула изобретения 1. Интегратор, содержащий токоэадпющую цепь, подключенную к BXDJV операдиснного усилителя, выход которого явля ется выходом интегратора, и интегрирующий конденсатор, обкладка которого подключена к входу оперпцишного усилителя, отличающийся тем, что, с целью повыщекия точности интегрирования, в него введены блок-с переменным коэффициентом -передачи и. блок управления, вход которого подключен к выхооу операционного усилителя, а выход соешшси с управляющим входом блока с переменным коэфф1щиентом передачи, включенным межоу другой обкладкой интегрирующего конденсатора и выходом операционного усилителя. 2. Интегратор по п. I, о т л и ч а ю щ и и с я тем, что блок управления содержит схему сравнения, один из входов которой является первым входом блока управления, другие входы соединены с выходами источника опорных н апряжений, а выход подключен к инфЬрмадионному входу С1ШИГОВОГО регистра, тактирующий вход Которого соединен с генератором тактовых импульсов, установочный вход сдвигового регистра и ьход разрешения являются соответственно установочным входом и входом разрещения блока у)1равления.

79551068

Источники информации,2. Электроника, 1979, т, 52, Nf 15,

пртнятые во внимание при эксперпзес. 99.

I. Проектирование и применение опера

дионных усилителе, .Под ред. Дж. Грэ .з. Чесноков А. А. Решающие усилимв Дж. Тоби и Л. Хьюсмана. М./Мир, isтали. Л., Энергия, 1969, с. 21 (про1974, с. 233-239.готип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Амплитудно-фазовый анализатор гармоник периодических напряжений | 1985 |

|

SU1303950A2 |

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112375A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Анализатор импульсных моментовлиНЕйНыХ СиСТЕМ АВТОМАТичЕСКОгОРЕгулиРОВАНия | 1979 |

|

SU847283A1 |

| Устройство для счета движущихся объектов | 1985 |

|

SU1312623A1 |

| Устройство для измерения параметров аппаратов магнитной записи | 1988 |

|

SU1543456A1 |

| ФОТОПРИЕМНАЯ ЛИНЕЙКА | 2009 |

|

RU2419242C1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347028A1 |

| Аналоговый интегратор | 1983 |

|

SU1128271A1 |

| Устройство для оценки детонации в двигателе внутреннего сгорания | 1986 |

|

SU1397777A1 |

vcr.

АНАМЗ

(рие. 1

ei

ff

r I

C-O //pjSo, 0 Afy

- Нг

a.2

Авторы

Даты

1982-08-30—Публикация

1981-01-06—Подача