( КОМПАРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоустойчивый компаратор напряжения | 1981 |

|

SU993466A1 |

| Компаратор напряжений | 1978 |

|

SU902238A1 |

| Следящий многоустойчивый компаратор напряжений | 1974 |

|

SU660226A1 |

| Стробируемый формирователь с парафазными ттл-выходами | 1978 |

|

SU758502A1 |

| Триггер Шмитта | 1980 |

|

SU884087A1 |

| Компаратор | 1987 |

|

SU1448402A1 |

| Дифференциальный операционный усилитель | 1974 |

|

SU515251A1 |

| Многоустойчивый компаратор тока | 1983 |

|

SU1129583A1 |

| Преобразователь уровня сигналов | 1981 |

|

SU1011025A1 |

| Устройство сравнения | 1977 |

|

SU714291A1 |

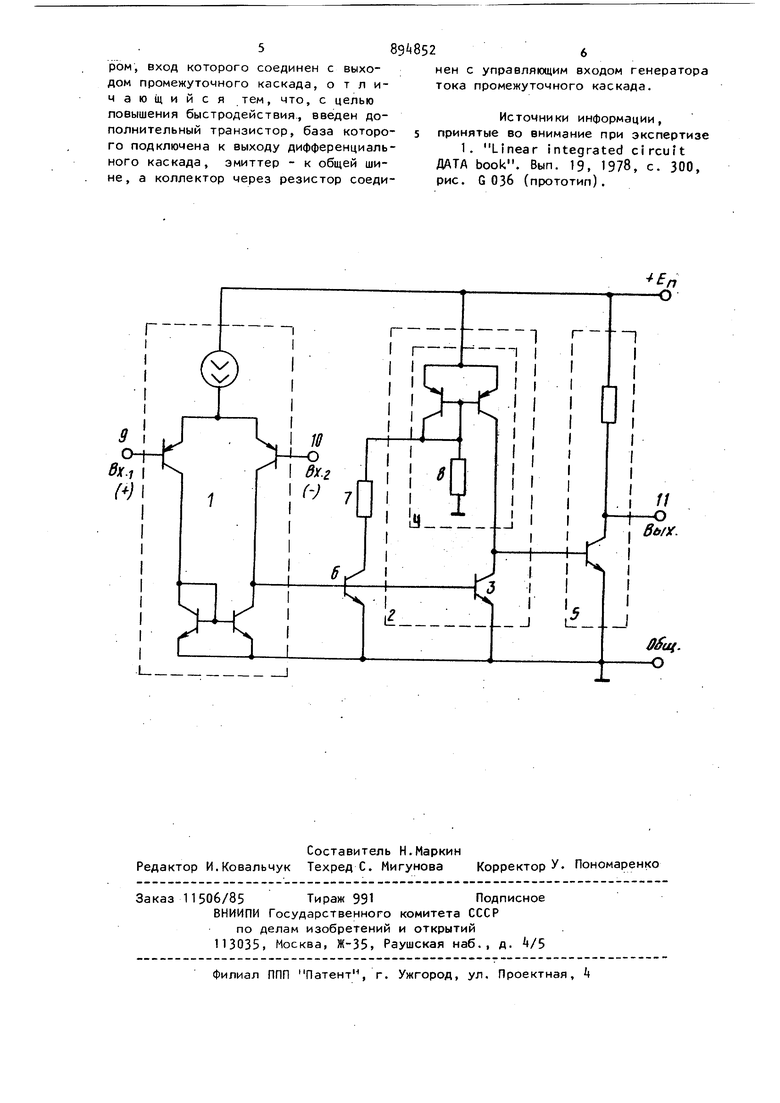

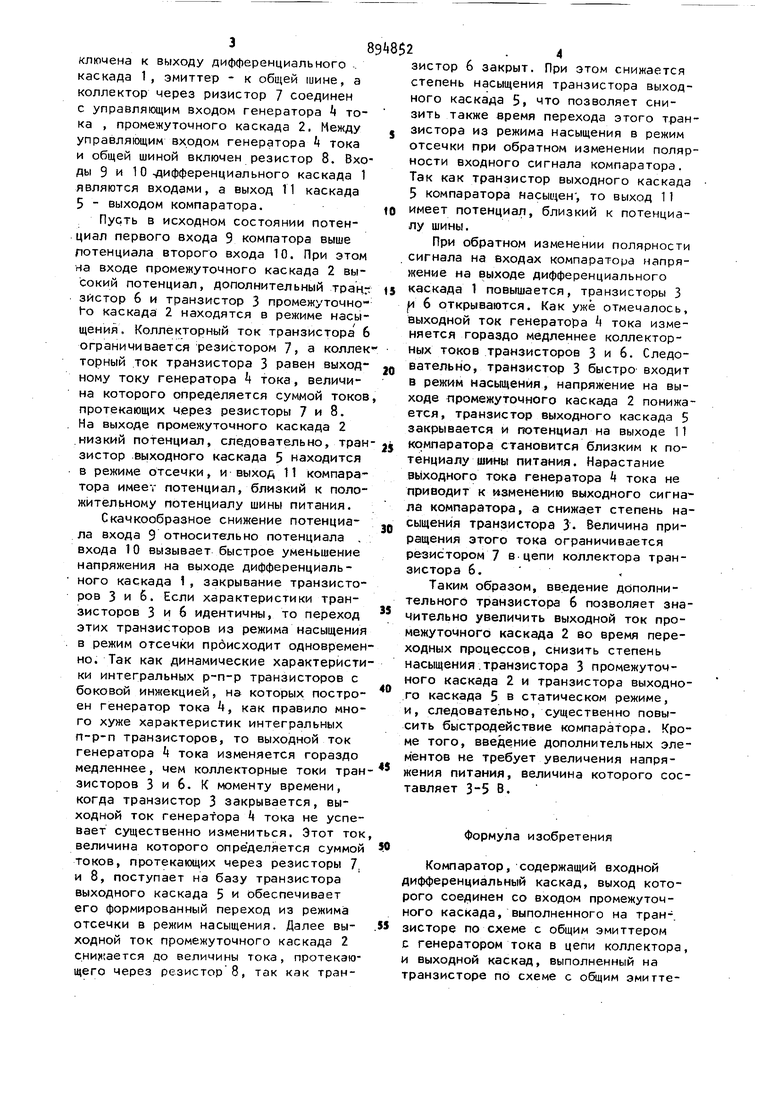

Изобретение относится к радиотехнике и электронике и может быть использовано в устройствах автоматики и вычислительной техники. Известны компараторы, содержащие входной дифференциальный каскад, выход которого соединен со входом промежуточного каскада, выполненного на транзисторе по схеме с общим эмиттером с генератором тока в цепи коллектора, и выходной каскад, выполненный на транзисторе по схеме с общим эмиттером , вход которого соединен с выходом промежуточного каскада 1. Недостаток таких компараторов низкое, быстродействие. Цель изобретения - повышение быстродействия. Для достижения поставленной цели в компаратор, содержащий входной дифференциальный- каскад , выход которого соединен со входом промежуточного кас када, выполненного на транзисторе по схеме с общим эмиттером с генератором тока в цепи коллектора, и выходной каскад, выполненный на транзисторе по схеме с общим эмиттером, вход которого соединен с выходом промежуточного каскада, введен дополнительный транзистор, база которого подключена к выходу дифференциального каскада, эмиттер - к общей шине, а коллектор через резистор соединен с управляющим входом генератора тока промежуточного каскада. На чертеже приведена принципиальная схема компаратора. Компаратор содержит входной дифференциальный каскад 1, выход которого соединен со входом промежуточного каскада 2, вьтолненного на транзисторе 3 по схеме с общим эмиттером с генератором k тока в цепи коллектора, выходной каскад 5, также выполненный на транзисторе по схеме с .общим эмиттером, вход которого соединен с выходом промежуточного каскада 2 , и дополнительный транзистор 6, база которого подк выходу дифференциального клюуена 1 , эмиттер - к общей шине, а каскада коллектор через ризистор 7 соединен с управляющим входом генератора тока , промежуточного каскада 2. Между управляющим входом генератора k тока и общей шиной включен резистор 8. Входы 9 и 10-дифференциального каскада 1 являются входами, а выход 11 каскада 5 - выходом компаратора. Пусть в исходном состоянии потенциал первого входа 9 компатора выше потенциала второго входа 10. При этом на входе промежуточного каскада 2 высокий потенциал, дополнительный транзИстор 6 и транзистор 3 промежуточно|-о каскада 2 находятся в режиме насыщения. Коллекторный ток транзистора 6 ограничивается резистором 7, а коллек торный ток транзистора 3 равен выходному току генератора 4 тока, величина которого определяется суммой токов протекающих через резисторы 7 и 8. На выходе промежуточного каскада 2 .низкий потенциал, следовательно, тран зистор вь1ходного каскада 5 находится в режиме отсечки, и выход 11 компаратора имеет потенциал, близкий к положительному потенциалу шины питания. Скачкообразное снижение потенциала входа 9 относительно потенциала . входа 10 вызывает быстрое уменьшение напряжения на выходе дифференциального каскада 1, закрывание транзисторов 3 и 6. Если характеристики транзисторов 3 и 6 идентичны, то переход этих транзисторов из режима насыщения в режим отсечки происходит одновремен но. Так как динамические характеристи ки интегральных р-п-р транзисторов с боковой инжекцией, на которых построен генератор тока 4, как правило много хуже характеристик интегральных п-р-п транзисторов, то выходной ток генератора тока изменяется гораздо медленнее, чем коллекторные токи тран зисторов 3 и 6. К моменту времени, когда транзистор 3 закрывается, выходной ток генератора тока не успевает существенно измениться. Этот ток величина которого определяется суммой токов, протекающих через резисторы 7. и 8, поступает на базу транзистора выходного каскада 5 и обеспечивает его формированный переход из режима отсечки в режим насыщения. Далее выходной ток промежуточного каскада 2 с.нин.ается до величины тока, протекающего через резистор 8, так как тран8 . 4 зистор 6 закрыт. При этом снижается степень насыщения транзистора выходного каскада 5, что позволяет снизить также еремя перехода этого транзистора из режима насыщения в режим отсечки при обратном изменении полярности входного сигнала компаратора. Так как транзистор выходного каскада 5 компаратора насыщен , то выход 11 имеет потенциал, близкий к потенциалу шины. При обратном изменении полярности сигнала на входах компаратора напряжение на выходе дифференциального каскада 1 повышается, транзисторы 3 6 открываются. Как уже отмечалось, выходной ток генератора тока изменяется гораздо медленнее коллекторных токов транзисторов 3 и 6. Следовательно, транзистор 3 быстро входит в режим насыщения, напряжение на выходе промежуточного каскада 2 понижается, транзистор выходного каскада 5 закрывается и потенциал на выходе 11 компаратора становится близким к потенциалу шины питания. Нарастание выходного тока генератора тока не приводит к изменению выходного сигнала компаратора, а снижает степень насыщения транзистора 3. Величина приращения этого тока ограничивается резистором 7 в цепи коллектора транзистора 6. Таким образом, введение дополнительного транзистора 6 позволяет значительно увеличить выходной ток промежуточного каскада 2 во время переходных процессов, снизить степень насыщения .транзистора 3 промежуточного каскада 2 и транзистора выходного каскада 5 в статическом режиме, и, следовательно, существенно повысить быстродействие компаратора. Кроме того, введение дополнительных элементов не требует увеличения напряжения питания, величина которого составляет 3-5 В. Формула изобретения Компаратор, содержащий входной дифференциальный каскад, выход которого соединен со входом промежуточного каскада, выполненного на тран-. зисторе по схеме с общим эмиттером с генератором тока в цепи коллектора, и выходной каскад, выполненный на транзисторе по схеме с общим эмиттером, вход которого соединен с выходом промежуточного каскада, о т л ичаюЩийся тем, что, с целью повышения быстродействия., введен дополнительный транзистор, база которого подключена к выходу дифференциального каскада, эмиттер - к общей шине, а коллектор через резистор соединен с управляющим входом генератора тока промежуточного каскада.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-12-30—Публикация

1980-03-03—Подача