Изобретение относится к импульсной технике и может быть использовано в компараторах напряжения, в выходных регистрах хранения, в частности в интегральных аналого-цифровых преобразователях.

Известно устройство, содержащее входной дифференциальньш каскад, выходы которого подключен к входам двух выходных ТТЛ каскадов.

Недостатком устройства является низкое быстродействие и большая потребляемая мощность.

Известен также ТЛЭС-ТТЛ преобразователь, содержап(ий входной дифференциапьньй переключатель тока на двух транзисторах, эмиттеры которых подключены к источнику тока, базы к входам устройства, и выходные ТТЛ каскады, эмиттеры нижних транзисторов которых подключены к общей шине, а коллекторы верхних транзисторов через резистор - к шине питания.

Недостатком такого преобразователя является низкое быстродействие и большая потребляемая мощность.

Цель изобретения - повышение быстродействия и уменьшение потребляемой мощности преобразователя.

Для достижения поставленной дели в преобразователе, содержащем входной дифференциальный переключатель тока на первом и втором транзисторах, эмиттеры которых подключены к генератору тока, базы - к входам устройства и выходной ТТЛ каскад, эмиттер нижнего транзистора которого подключен к общей шине, а коллектор верхнего транзистора - к шине питания, коллекторы первого и второго транзисторов подключены соответственно к эмиттерам третьего и четвертого транзисторов, базы которых подключены к общей шине, а коллекторы - соотв.етственно к базам верхнего и нижнего транзисторов выходного T17I.каскада, коллектор нижнего транзистора которого подключен к выходу и через диод к эмиттеру верхнего транзистора, база которого через резистор подключена к шине питания, базы - к источникам опорных напряжений, а эмиттеры соответственно через резистор, и непосредственно под1шючены к коллекторам вто рого и третьего транзисторов, а кроме того, введен управляющий дифференциальньм каскад, базы транзисторов которого подключены к стробирующим

входам устройства, эмиттеры - к генератору тока, а коллекторы - соответственно к эмиттерам транзисторов входного дифференциального переключателя тока и к эмиттерам транзисторов триггера с непосредственными коллекторно-базовыми связями, коллекторы транзисторов.которого подключены соответственно к коллекторам транзисторов входного дифференциального переключателя тока.

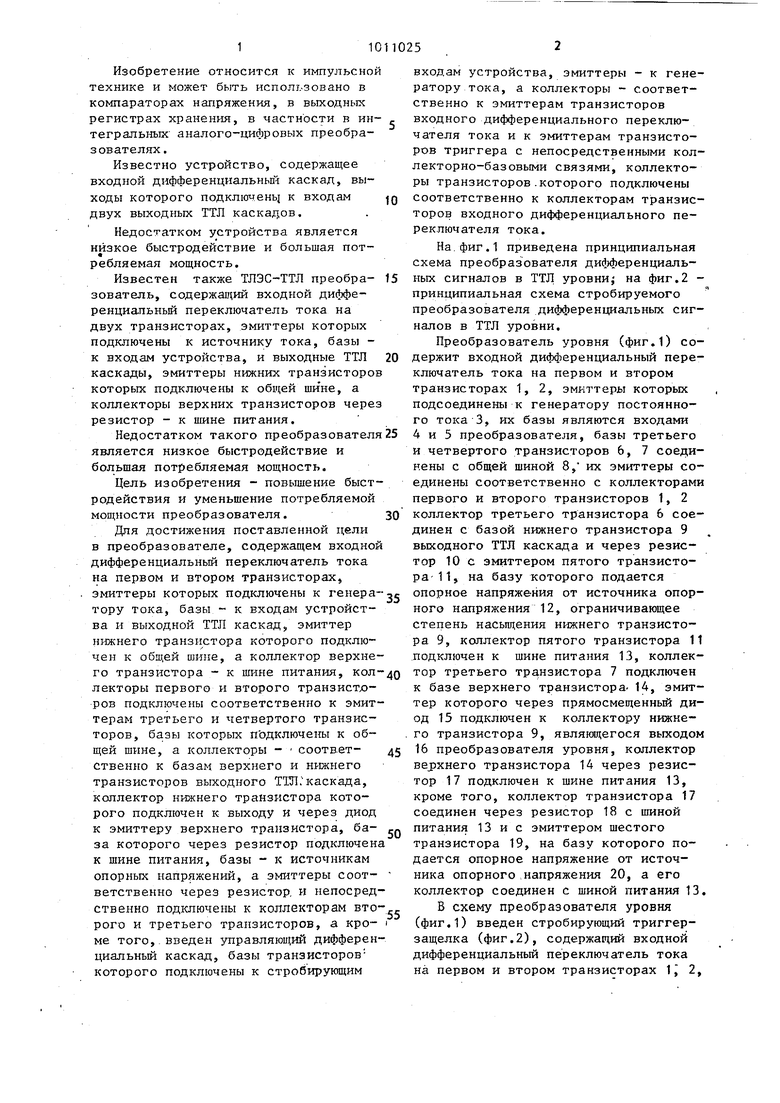

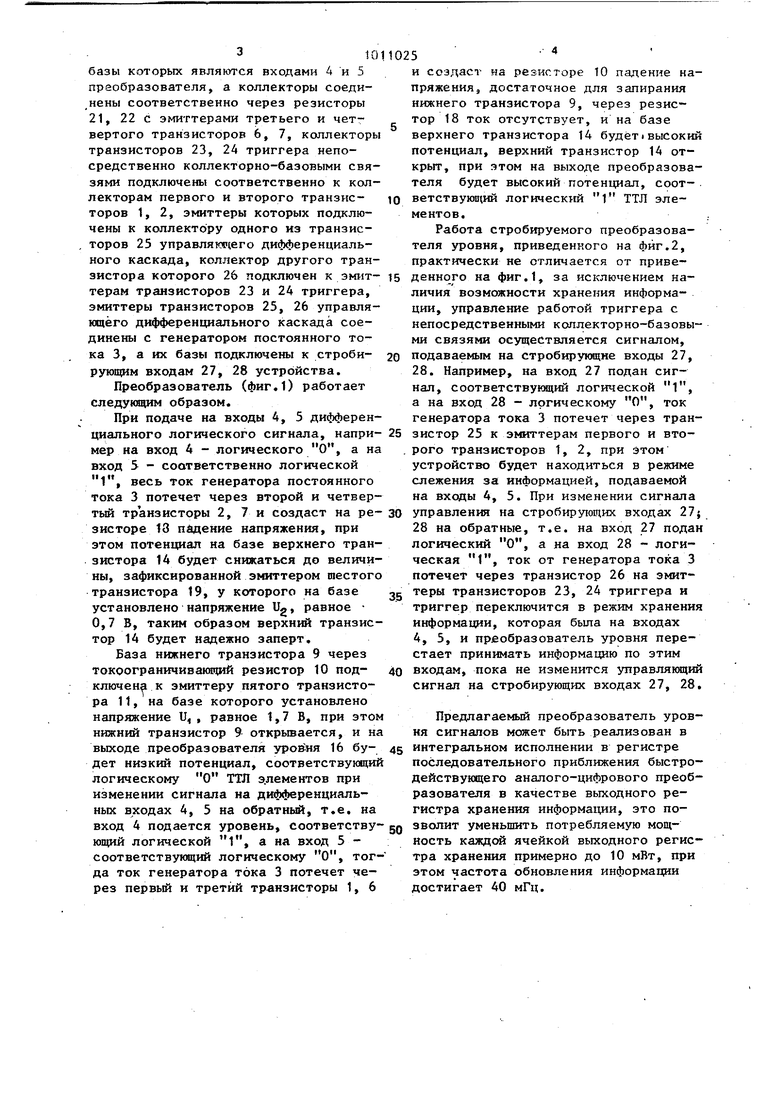

На.фиг.1 приведена принципиальная схема преобраз ователя дид)ференциальньгх сигналов в ТТЛ уровни; на фиг.2 принципиальная схема стробируемого преобразователя дифференциальных сигналов в ТТЛ уровни.

Преобразователь уровня (фиг.1) содержит входной дифференциальный переключатель тока на первом и втором транзисторах 1, 2, эмиттеры которых подсоединены к генератору постоянного тока 3, их базы являются входами 4 и 5 преобразователя, базы третьего и четвертого транзисторов 6, 7 соединены с общей шиной 8, их эмиттеры соединены соответственно с коллекторами первого и второго транзисторов 1, 2 коллектор третьего транзистора 6 соединен с базой нижнего транзистора 9 выходного ТТЛ каскада и через резистор 10 с эмиттером пятого транзистора- 11, на базу которого подается опорное напряжения от источника опорного напряжения 12, ограничивающее степень насыщения нижнего транзистора 9, коллектор пятого транзистора 11 подключен к шине питания 13, коллектор третьего транзистора 7 подключен к базе верхнего транзистора- 14, эмиттер которого через прямосмещенный диод 15 подключен к коллектору нижнего транзистора 9, являющегося выходом 16 преобразователя уровня, коллектор BejDXHero транзистора 14 через резистор 17 подключен к шине питания 13, кроме того, коллектор транзистора 17 соединен через резистор 18 с шиной питания 13 и с эмиттером шестого транзистора 19, на базу которого подается опорное напряжение от источника опорного .напряжения 20, а его коллектор соединен с шиной питания 13.

В схему преобразователя уровня (фиг.1) введен стробирующий триггерзащелка (фиг.2), содержащий входной дифференциальный переключатель тока на первом и втором транзисторах 1 2, 3to базы которых являются входами 4 и 5 преобразователя, а коллекторы соединены соответственно через резисторы 21, 22 с эмиттерами третьего и четвертого транзисторов 6, 7, коллекторы транзисторов 23, 24 триггера непосредственно коллекторно-базовыми связями подключены соответственно к коллекторам первого и второго транзисторов 1, 2, эмиттеры которых подключены к коллектору одного из транзисторов 25 управляюр1его дифференциального каскада, коллектор другого транзистора которого 26 подключен к эмиттерам транзисторов 23 и 24 триггера, эмиттеры транзисторов 25, 26 управляющего дифференциального каскада соединены с генератором постоянного тока 3, а их базы подключены к стробирующим входам 27, 28 устройства. Преобразователь (фиг,1) работает следующим образом. При подаче на входы 4, 5 дифференциального логического сигнала, например на вход 4 - логического О, а на вход 5 - соответственно логической 1, весь ток генератора постоянного тока 3 потечет через второй и четвертый транзисторы 2, 7 и создаст на резисторе 18 падение напряжения, при этом потенциал на базе верхнего транзистора 14 будет снижаться до величины, зафиксированной эмиттером шестого транзистора 19, у которого на базе установлено напряжение Ug, равное 0,7 В, таким образом верхний транзистор 14 будет надежно заперт. База нижнего транзистора 9 через токоограничивающий резистор 10 подключен к эмиттеру пятого транзистора 11, на базе которого установлено напряжение U, , равное 1,7В, при этом нижний транзистор 9 открьтается, и на выходе преобразователя уровия 16 будет низкий потенциал, соответствующий логическому О ТТЛ элементов при изменении сигнала на диф ренциальных входах 4, 5 на обратный, т.е. на вход 4 подается уровень, соответствующий логической 1, а на вход 5 соответствукмций логическому О, тогда ток генератора тока 3 потечет через первый и третий транзисторы 1, 6 5 и создаст на резисторе 10 падение напряжения, достаточное для запирания нижнего транзистора 9, через резис тор 18 ток отсутствует, и на базе верхнего транзистора 14 будёт высокий потенциал, верхний транзистор 14 открыт, при этом на выходе преобразователя будет высокий потенциал, соответствуюп1Ий логический 1 ТТЛ элементов. Работа стробируемого преобразователя уровня, приведенного на фиг.2, практически не отличается от приве- денного на фиг.1, за исключением наличия возмсшности хранения информа- ции, управление работой триггера с непосредственными каплекторно-базовыми связями осуществляется сигналом, подаваемым на стробирукицне входы 27, 28. Например, на вход 27 подан сигнал, соответствукиций логической 1, а на вход 28 - логическому О, ток генератора тока 3 потечет через транзистор 25 к эмиттерам первого и второго транзисторов 1, 2, при этом устройство будет находиться в режиме слежения за информацией, подаваемой на входы 4, 5. При изменении сигнала управления на стробирующих входах 27$ 28 на обратные, т.е. на вход 27 подан логический О, а на вход 28 - логическая 1, ток от генератора тока 3 потечет через транзистор 26 на эмиттеры транзисторов 23, 24 триггера и триггер переключится в режим хранения информации, которая была на входах 4, 5, и преобразователь уровня перестает принимать информацию по этим входам, пока не изменится управлякнций сигнал на стробирующих входах 27, 28. Предлагаемый преобразователь уровня сигналов может быть реализован в интегральном исполнении в регистре последовательного приближения быстродействующего аналого-цифрового преобразователя в качестве выходного регистра хранения информагщи, это позволит уменьшить потребляемую мощность ячейкой выходного регистра хранения примерно до 10 мВт, при этом частота обновления информации достигает 40 мГц.

ф1/г.1

6

47 22

21

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральная логическая схема | 1979 |

|

SU1001480A1 |

| Стробируемый формирователь с парафазными ттл-выходами | 1978 |

|

SU758502A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1350831A1 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| Преобразователь логических уровней | 1978 |

|

SU790327A1 |

| Преобразователь логических уровней | 1990 |

|

SU1812634A1 |

| Стабилизированный источник питания | 1981 |

|

SU993228A1 |

| Преобразователь логического уровня | 1986 |

|

SU1338054A1 |

1. ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ СИГНАЛОВ, содержавший входной дифференциальный переключатель тока на первом и втором транзисторах, эмиттеры которых подключены к генератору тока, базы - к входам устройства, и выходной ТТЛ каскад, эмиттер нижнего транзистора которого подключен к общей шине, а коллектор верхнего транзистора через резистор - к шине питания j отличающийся тем, что,- с целью повьшения быстродействия и уменьшения потребляемой мощности, коллекторы первого и второго транзисторов подключены соответственно к эмиттерам третьего и четвертого транзисторов, базы которых подключены к общей шине, а коллекторы - соответственно к базам верхнего и нижнего транзисторов выходного ТТЛ каскада, коллектор нижнего транзистора которого подключен к выходу и через диод к эмиттеру верхнего транзистора, база которого через резистор подключена к шине питания, коллекторы пятого и шестого транзисторов подключены к ши.не питания, базы - к источникам опорных напряжений, а эмиттеры соответственно через резистор и непосредственно подключены к коллекторам второго и третьего транзисторов. 2. Преобразователь по п.1, -о т л и ч а ющ и и с я тем, что, с целью его расширения функциональных возможностей, введен управляющий дифференциальный каскад, базы транзисторов которого подключены к стробируюсл щим входам устройства, эмиттеры - к генератору тока, а коллекторы - соответственно к эмиттерам транзисторов входного дифференциального переключателя тока и эмиттерам транзисторов триггера с непосредственными коллекторно-базовыми связями, коллекторы транзисторов которого подключены соответственно к коллекторам транзисторов входного дифференциального переключателя тока.

7 /70-Hil. вход

| 1972 |

|

SU411644A1 | |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Тлэс-ттл преобразователь | 1977 |

|

SU617844A1 |

Авторы

Даты

1988-11-15—Публикация

1981-01-09—Подача