(5) ПРЕОБРАЗОВАТЕЛЬ ФАЗА - ЧАСТОТА

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь активной мощностиВ КОличЕСТВО иМпульСОВ | 1979 |

|

SU845109A1 |

| Преобразователь сдвига фаз в цифровой код | 1978 |

|

SU781708A1 |

| Преобразователь аналоговых величин в код | 1979 |

|

SU924855A2 |

| Преобразователь аналоговых величин в код | 1978 |

|

SU764127A1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1984 |

|

SU1225014A1 |

| Преобразователь частоты в код | 1977 |

|

SU746922A1 |

| Способ аналого-цифрового преоб-РАзОВАНия и уСТРОйСТВО для ЕгООСущЕСТВлЕНия | 1979 |

|

SU839050A1 |

| Цифровой кондуктометр | 1986 |

|

SU1374144A1 |

| Устройство для импульсно-фазового управления @ -пульсным вентильным преобразователем | 1983 |

|

SU1156212A1 |

| Устройство для измерения мощности | 1990 |

|

SU1751685A1 |

t

Изобретение относится к цифровой преобразовательной технике и может найти применение в системах управления ( телемеханики и дистанционного контроля.

Известен преобразователь фаза-код, содержащий формирователи, логические схемы И, НЕ, ИЛИ, сумматор, реверсивный счетчик, генератор образцовой частоты, ключ и линию задержки l J.

j

Недостаток этого устройства -, работа только в режиме отслеживания угла сдвига фаз и узкий диапазон рабочих частот.

Наиболее близким по технической сущности к предлагаемому является преобразователь фаза-частота, содержащий соединенные последовательно генератор образцовой частоты, группу управляемых вентилей, счетчик и группу импульсно-потенциальных вентилей, формирователь и блок управления, две группы управляемых вентилей, сумматор, элемент задержки и логический, элемент ИЛИ 2j

Недостаток этого устройства - малое быстродействие, поскольку преобразование фазы в частоту осуществляется за время, равное нескольким периодам исследуемых сигналов, что ограничивает рабочий частотный диапазон.

Цель изобретения - повышение быстродействия преобразования фазы в частоту.

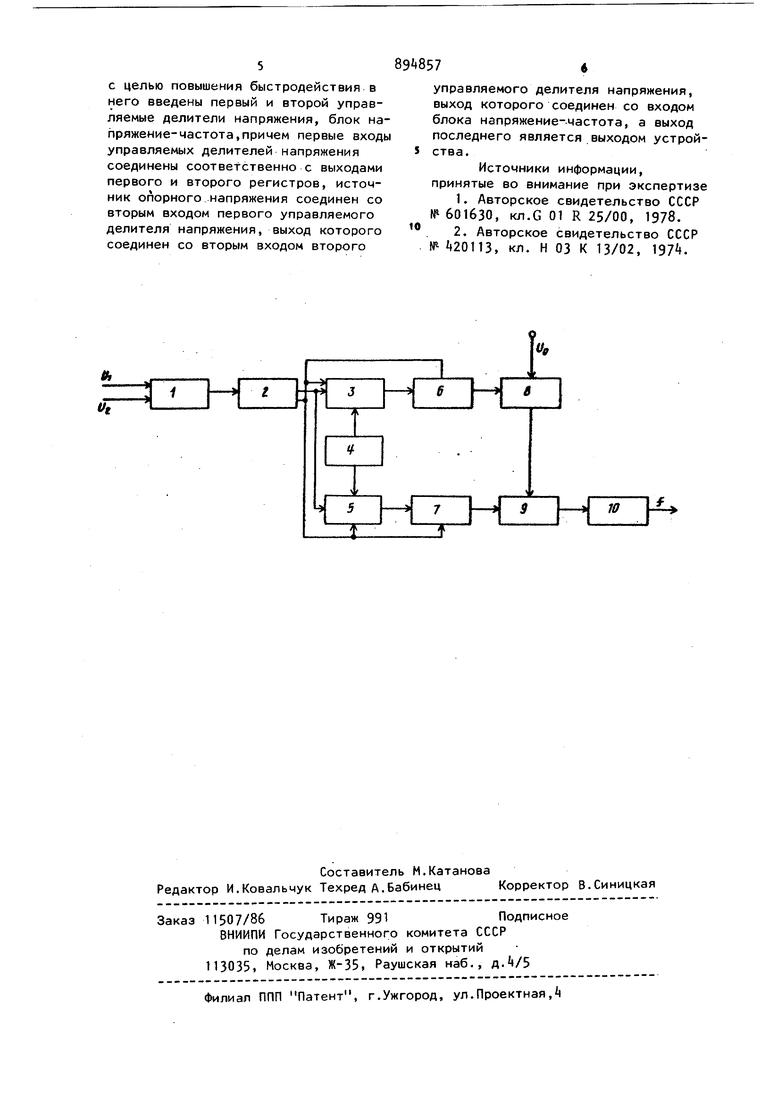

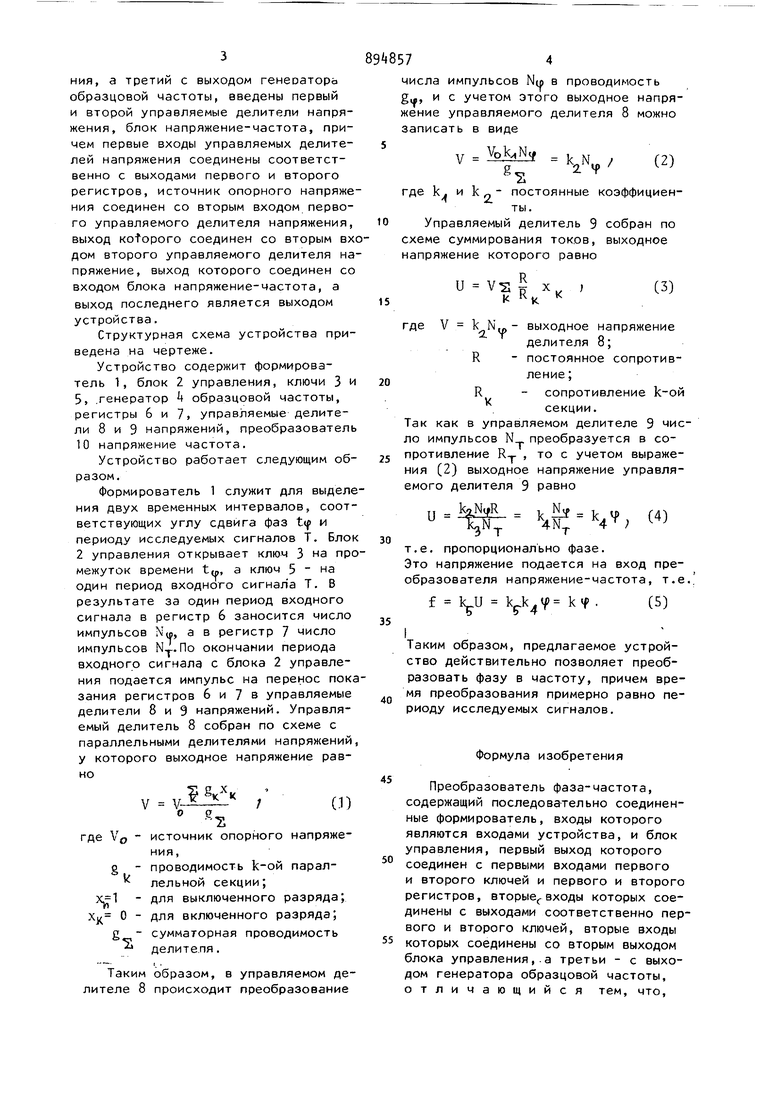

Эта цель достигается тем, что в устройство, содержащее последовательно соединенные формирователь, входы которого являются входами устройства, блок управления, первый выход которого соединен с первыми входами первого и второго ключей и первого и второго регистров, вторые входы которых соединены с выходами соответственно первого и второго ключей, вторые входы которых соединены со вторым выходом блока управления, а третий с выходом генеоаторь образцовой частоты, введены первый и второй управляемые делители напряжения, блок напряжение-частота, причем первые входы управляемых делителей напряжения соединены соответственно с выходами первого и второго регистров, источник опорного напряже ния соединен со вторым входом первого управляемого делителя напряжения выход Kofoporo соединен со вторым вх дом второго управляемого делителя на пряжение, выход которого соединен со входом блока напряжение-частота, а выход последнего является выходом устройства. Структурная схема устройства при ведена на чертеже. Устройство содержит формирователь 1, блок 2 управления, ключи 3 и 5, .генератор образцовой частоты, регистры 6 и 7, управляемые делители 8 и 9 напряжений, преобразовател 10 напряжение частота. Устройство работает следующим об разом. Формирователь 1 служит для выдел ния двух временных интервалов, соот ветствующих углу сдвига фаз t«f и периоду исследуемых сигналов Т. Бло 2 управления открывает ключ 3 на пр межуток времени t(p, а ключ 5 - на один период входного сигнала Т. В результате за один период входного сигнала в регистр 6 заносится число импульсов NW, а в регистр 7 число импульсов N.По окончании периода входного сигнала с блока 2 управления подается импульс на перенос пок зания регистров 6 и 7 в управляемые делители 8 и 9 напряжений. Управляемый делитель 8 собран по схеме с параллельными делителями напряжений у которого выходное напряжение равно где VQ - источник опорного напряжения, g - проводимость k-ой парал лельной секции; - для выключенного разряда; х О - для включенного разряда; g - сумматорная проводимость делителя. Таким образом, в управляемом делителе 8 происходит преобразование 74 числа импульсов Nip в проводимость g(«, и с учетом этого выходное напряение управляемого делителя 8 можно записать в виде V k,(2) где k. и k . - постоянные коэффициентУправляемый делитель 9 собран по схеме суммирования токов, выходное напряжение которого равно и v-a § где V - k N - выходное напряжение делителя 8; R - постоянное сопротивление;R - сопротивление k-ой секции. Так как в управляемом делителе 9 число импульсов N преобразуется в сопротивление R-j- , то с учетом выражения (2) выходное напряжение управляемого делителя 9 равно W,, W Т.е. пропорционально фазе. Это напряжение подается на вход преобразователя напряжение-частота, т.е., f . kf Таким образом, предлагаемое устройство действительно позволяет преобразовать фазу в частоту, причем время преобразования примерно равно периоду исследуемых сигналов. Формула изобретения Преобразователь фаза-частота, содержащий последовательно соединенные формирователь, входы которого являются входами устройства, и блок управления, первый выход которого соединен с первыми входами первого и второго ключей и первого и второго регистров, вторые входы которых соединены с выходами соответственно первого и второго ключей, вторые входы которых соединены со вторым выходом блока управления,.а третьи - с выходом генератора образцовой частоты, отличающийся тем, что.

с целью повышения быстродействия в него введены первый и второй управляемые делители напряжения, блок напряжение-частота, причем первые входы управляемых делителей напряжения соединены cooTBetcTBeHHo с выходами первого и второго регистров, источник огюрного напряжения соединен со вторым входом первого управляемого делителя напряжения, выход которого соединен со вторым входом второго

управляемого делителя напряжения, выход которого соединен со входом блока напряжение-частота, а выход последнего является выходом устройства.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-12-30—Публикация

1980-05-05—Подача