Изобретение относится к импульсной технике,в частности к 0-триггерам, построенным по ЭСЛ схемотехнике.

Известен D-триггер, построенный на трех RS-триггерах 1.

Известен также О-триггер, построенный по схеме M-S, содержащий ведущую часть, выполненную в виде D-триггера с управлением по yjpoBHro тактового сигнала, база информационного транзистора переключателя тока которого через согласователь логического уровня подключена к входу RS б устройства, ведомую часть, в состав которой входят переключатель тока, база ин Ъормациокного транзистора которого подключена к базе информационного транзистора переключателя тока ведущей части, два экшттерных повторителя с резистивными делителями в экшттерных цепях и бистабильная ячейка 21.

Общий; недостаток известных устройств - низкая надежность вследствие большойсложности при реализации по ЭСЛ схемотехнике.

Цель изобретения - повышение надежности устройства путем упрощения.

Для достижения поставленной цели в устройство, содерхсащее D-триггер с управлением по уровню тактового сигнала, база информационного транзистора переключателя тока которого через согласователь логи10ческого уровня подключена к входу RSC устройства и база информационного транзистора первого дополнительного переключателя тока, два эмиттерных повторителя с резистивныьш делителями в эмиттерных цепях вве15ден второй дополнительный переключатель тока, база информационного транзистора которого подключена к выходу первого эмиттерного повторителя, вхол которого подключен к

20 коллектору информационнот о транзистора первого дополнительного переключателя тока, коллектор опорного транзистора второго дополнительного переключателя тока через второй

25 эмиттерный повторитель подключен к базе дополнительного транзистора, коллектор и эмиттер которого подключен соответственно к коллектору и эмиттеру информационного транзис30тора переключателя тока D-триггера

с управлением по уровню тактового сигнала, выходы которого подключены к выходам устройства.

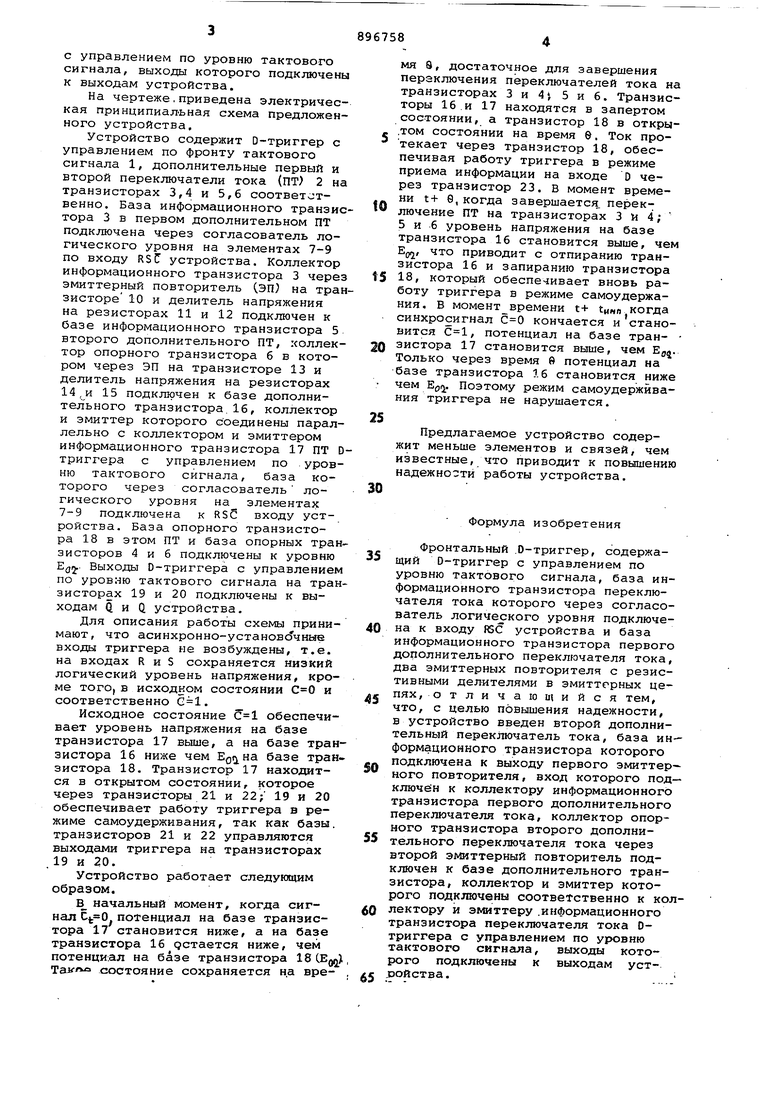

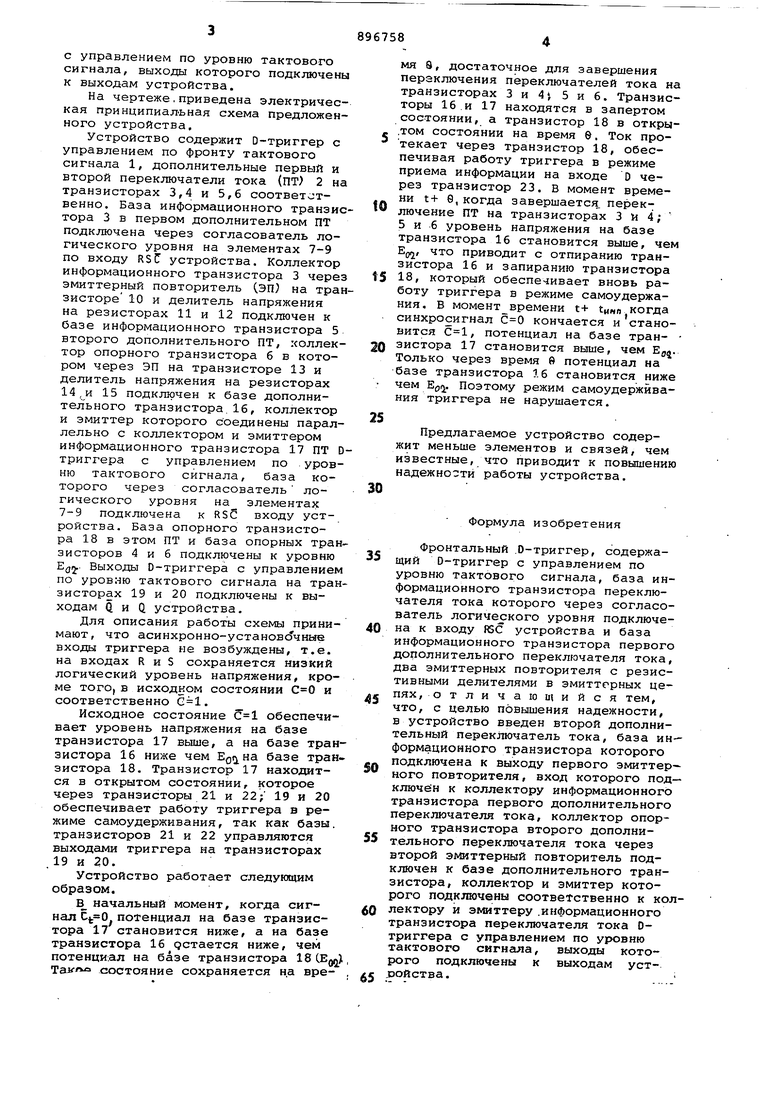

На чертеже.приведена электрическая принципиальная схема предложенного устройства.

Устройство содержит D-триггер с управлением по фронту тактового сигнала 1, дополнительные первый и второй переключатели тока (ПТ) 2 на транзисторах 3,4 и 5,6 соответственно. База информационного транзистора 3 в первом дополнительном ПТ подключена через согласователь логического уровня на элементах 7-9 по входу RSC устройства. Коллектор информационного транзистора 3 через эмиттерный повторитель (ЭП) на транзисторе 10 и делитель напряжения на резисторах 11 и 12 подключен к базе информационного транзистора 5 второго дополнительного ПТ, коллектор опорного транзистора 6 в котором через ЭП на транзисторе 13 и делитель напряжения на резисторах 14,и 15 подключен к базе дополнительного транзистора.16, коллектор и эмиттер которого соединены параллельно с коллектором и эмиттером информационного транзистора 17 ПТ Dтриггера с управлением по уровню тактового сигнала, база которого через согласователь логического уровня на элементах 7-9 подключена к RSC входу устройства. База опорного транзистора 18 в этом ПТ и база опорных транзисторов 4 и б подключены к уровню Ед.- Выходы D-триггера с управлением по уровню тактового сигнала на транзисторах 19 и 20 подключены к выходам Q и Q устройства.

Для описания работы схемы принимают, что асинхронно-установочные входы триггера не возбуждены, т.е. на входах R и S сохраняется низкий логический уровень напряжения, кроме того, в исходном состоянии и соответственно .

Исходное состояние обеспечивает уровень напряжения на базе транзистора 17 выше, а на базе транзистора 16 ниже чем Е(, базе транзистора 18. Транзистор 17 находится в открытом состоянии, которое через транзисторы 21 и 22; 19 и 20 обеспечивает работу триггера в режиме самоудерживания, так как базы. транзисторов 21 и 22 управляются выходами триггера на транзисторах . 19 и 20.

Устройство работает следующим образом.

В начальный момент, когда сигнал потенциал на базе транзистора 17 становится ниже, а на базе транзистора 16 дстается ниже, чем потенциал на базе транзистора 18 (Еу fQyno состояние сохраняется на время 9, достаточное для завершения переключения переключателей тока на транзисторах 3 и 4j 5 и 6. Транзисторы 16 и 17 находятся в запертом состоянии, а транзистор 18 в откры.том состоянии на время 6, Ток протекает через транзистор 18, обеспечивая работу триггера в режиме приема информации на входе О через транзистор 23. В момент времени t+ б, когда завершается, переключение ПТ на транзисторах 3 И 4; 5 и 6 уровень напряжения на базе транзистора 16 становится выше, чем Ер, что приводит с отпиранию транзистора 16 и запиранию транзистора 18, который обеспечивает вновь работу триггера в режиме самоудержания. В момент времени t+ 1иип когда синхросигнал кончается и становится , потенциал на базе тран- зистора 17 становится выше, чем Ед. Только через время и потенциал на базе транзистора 16 становится ниже чем , Поэтому режим самоудержйвания триггера не нарушается.

Предлагаемое устройство содержит меньше элементов и связей, чем известные, что приводит к повышению надежности работы устройства.

Формула изобретения

Фронтальный .D-триггер, содержащий D-триггер с управлением по уровню тактового сигнала, база информационного транзистора переключателя тока которого через согласователь логического уровня подключена к входу fiSC устройства и база информационного транзистора первого дополнительного переключателя тока, два эмиттерных повторителя с резистивными делителями в эмиттгрных цепях, отличаюши йся тем, что, с целью повышения надежности, в устройство введен второй дополнительный переключатель тока, база информационного транзистора которого подключена к выходу первого эмиттер кого повторителя, вход которого под ключен к коллектору информационного транзистора первого дополнительного переключателя тока коллектор опорного транзистора второго дополнительного переключателя тока через второй эмиттерный повторитель подключен к базе дополнительного транзистора, коллектор и эмиттер которого подключены соответственно к коллектору и эмиттеру .информационного транзистора переключателя тока Dтриггера с управлением по уровню тактового сигнала, выходы которого подключены к выходам устройства .

Источники информации. тринятые во внимание при экспертизе

1, Букреев И.Н. и др. Микроэлёктронные схекы цифровых устройств,

М., Сов., радио, 1975, с. 102, рис. 321.. .

2. William R . В 1 ood . J г . MECL system design handbook. Motorola Snc., 1971, .p.9, fig- 1,6(прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Троичный счетный триггер | 1979 |

|

SU864503A1 |

| Троичный фронтальный Д-триггер | 1980 |

|

SU917307A1 |

| Однофазный D-триггер | 1988 |

|

SU1647855A1 |

| Быстродействующий помехоустойчивыйлОгичЕСКий элЕМЕНТ и-или/ и-или-HE | 1978 |

|

SU849488A1 |

| НИЗКОВОЛЬТНЫЙ D-ТРИГГЕР С АСИНХРОННОЙ УСТАНОВКОЙ ЗНАЧЕНИЯ НА ОСНОВЕ ЭМИТТЕРНО-СВЯЗАННОЙ ЛОГИКИ | 2016 |

|

RU2699684C2 |

| Полный троичный сумматор | 1979 |

|

SU826342A1 |

| Согласующее устройство | 1977 |

|

SU660213A1 |

| Д-триггер типа М-S | 1986 |

|

SU1363449A1 |

| Логический пробник | 1983 |

|

SU1132268A1 |

| СИНХРОННАЯ ТРИГГЕРНАЯ ЯЧЕЙКА | 1997 |

|

RU2119716C1 |

Авторы

Даты

1982-01-07—Публикация

1979-07-24—Подача