ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области импульсной техники

УРОВЕНЬ ТЕХНИКИ

Из существующего уровня техники известно, что для осуществления фазовой автоподстройкой частоты необходимо применение программируемых делителей частоты, которые построены на основе D-триггеров с асинхронной установкой хранимого значения. Выполнение таких триггеров на основе эмиттерно-связанной логики позволяет получить высокую рабочую частоту. Известно схемотехническое решение D-триггера с асинхронным сбросом на основе эмиттерно-связанной логики, которое представляет собой двухступенчатую структуру на основе двух триггеров синхронизируемых по уровню, т.н. «защелок» с цепями сброса или принудительной установки хранимого значения. Защелки состоят из биполярных транзисторов, образующих вместе с цепями сброса или установки значения три уровня дифференциальных каскадов, которые определяют путь протекания тока в соответствии с логическими уровнями напряжений на базах транзисторов и определяют, соответственно, уровни напряжений на выходе триггера US 5122682 A, 16.06.1992. Недостатками данного технического решения являются: ограничение возможности применения схемы при однополярном напряжении питания ниже 5 В, обусловленное наличием трех уровней дифференциальных каскадов; высокое удельное энергопотребление ввиду наличия дополнительных цепей смещения логических уровней напряжения для соответствующих уровней дифференциальных каскадов, что приводит к дополнительной задержке сигнала при распространении в цепях смещения.

Наиболее близким к заявленному техническому решению является схема D-триггера с асинхронным сбросом и/или установкой значения выполненная на основе эмиттерно-связанной логики, которая представляет собой двухступенчатую структуру на основе двух триггеров «защелок» с цепями сброса и/или установкой хранимого значения, в которой использована одноуровневая схема US 7215170 B1, 8.05.2007. Реализация в схеме одного уровня дифференциальных каскадов обеспечивает активный режим работы транзисторов при типовом однополярном напряжении питания ниже 5 В вплоть до 1,8 В, также это позволяет исключить дополнительные цепи смещения логических уровней напряжений и связанные с ними недостатки. Недостатком данного решения является: избыточное количество используемых транзисторов в схеме; низкое входное сопротивление и высокая входная емкость вывода сброса и/или установки значения из-за одновременного подключения вывода к базам четырех транзисторов; низкое входное сопротивление и высокая входная емкость прямого и инверсного входов тактового сигнала из-за одновременного подключения каждого вывода к базам четырех транзисторов.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Задачей, на решение которой направлено заявляемое изобретение, является создание быстродействующих программируемых делителей частоты с низким энергопотреблением на основе эмиттерно-связанной логики.

Данная задача решается за счет того, что заявленный низковольтный D-триггер с асинхронным сбросом, характеризуется тем, что состоит из одного уровня дифференциальных каскадов и резисторов, образующих ведущий и ведомый триггеры, синхронизируемые по уровню, которые состоят из:

пары транзисторов с объединенными эмиттерами первого дифференциального каскада, усиливающих входной сигнал;

пары транзисторов с объединенными эмиттерами второго дифференциального каскада с положительной обратной связью, образованной соединением базы с коллектором противолежащего транзистора, позволяющих удерживать усиленное первым дифференциальным каскадом логическое значение;

трех резисторов, два из них подключены к объединенным коллекторам двух транзисторов по одному из первого и второго дифференциальных каскадов, при этом резисторы подключены к шине питания через третий резистор.

При этом объединенные эмиттеры транзисторов первого дифференциального каскада ведущего триггера подключены к объединенным эмиттерам транзисторов второго дифференциального каскада ведомого триггера; объединенные эмиттеры транзисторов второго дифференциального каскада ведущего триггера подключены к объединенным эмиттерам транзисторов первого дифференциального каскада ведомого триггера; источник постоянного тока I1 подключен к объединенным эмиттерам транзисторов первого дифференциального каскада ведущего триггера и второго дифференциального каскада ведомого триггера; источник постоянного тока I2 подключен к объединенным эмиттерам транзисторов второго дифференциального каскада ведущего триггера и первого дифференциального каскада ведомого триггера. Тактовый сигнал CLK подается на базу транзистора Т6, а инверсный тактовый сигнал  подается на базу транзистора Т7. Эмиттер транзистора Т6 подключен к объединенным эмиттерам транзисторов второго дифференциального каскада ведущего триггера и к объединенным эмиттерам транзисторов первого дифференциального каскада ведомого триггера; коллектор транзистора Т6 подключен к шине питания; эмиттер транзистора Т7 подключен к объединенным эмиттерам транзисторов первого дифференциального каскада ведущего триггера и к объединенным эмиттерам транзисторов второго дифференциального каскада ведомого триггера; коллектор транзистора Т7 подключен к шине питания. Сигнал установки значения SET подается на базы двух транзисторов Т5 и Т8. Эмиттер транзистора Т5 подключен к объединенным эмиттерам транзисторов второго дифференциального каскада ведущего триггера и к объединенным эмиттерам транзисторов первого дифференциального каскада ведомого триггера; коллектор транзистора Т5 подключен к инверсному выходу ведущего триггера

подается на базу транзистора Т7. Эмиттер транзистора Т6 подключен к объединенным эмиттерам транзисторов второго дифференциального каскада ведущего триггера и к объединенным эмиттерам транзисторов первого дифференциального каскада ведомого триггера; коллектор транзистора Т6 подключен к шине питания; эмиттер транзистора Т7 подключен к объединенным эмиттерам транзисторов первого дифференциального каскада ведущего триггера и к объединенным эмиттерам транзисторов второго дифференциального каскада ведомого триггера; коллектор транзистора Т7 подключен к шине питания. Сигнал установки значения SET подается на базы двух транзисторов Т5 и Т8. Эмиттер транзистора Т5 подключен к объединенным эмиттерам транзисторов второго дифференциального каскада ведущего триггера и к объединенным эмиттерам транзисторов первого дифференциального каскада ведомого триггера; коллектор транзистора Т5 подключен к инверсному выходу ведущего триггера  ; эмиттер транзистора Т8 подключен к объединенным эмиттерам транзисторов первого дифференциального каскада ведущего триггера и к объединенным эмиттерам транзисторов второго дифференциального каскада ведомого триггера; коллектор транзистора Т8 подключен к инверсному выходу ведомого триггера

; эмиттер транзистора Т8 подключен к объединенным эмиттерам транзисторов первого дифференциального каскада ведущего триггера и к объединенным эмиттерам транзисторов второго дифференциального каскада ведомого триггера; коллектор транзистора Т8 подключен к инверсному выходу ведомого триггера  .

.

Сигнал сброса RST может подаваться на базы двух транзисторов Т5 и Т8, при этом необходимо, чтобы: эмиттер транзистора Т5 подключен к объединенным эмиттерам транзисторов второго дифференциального каскада ведущего триггера и к объединенным эмиттерам транзисторов первого дифференциального каскада ведомого триггера; коллектор транзистора Т5 подключен к прямому выходу ведущего триггера Z; эмиттер транзистора Т8 подключен к объединенным эмиттерам транзисторов первого дифференциального каскада ведущего триггера и к объединенным эмиттерам транзисторов второго дифференциального каскада ведомого триггера; коллектор транзистора Т8 подключен к прямому выходу ведомого триггера Q.

Техническим результатом, обеспечиваемым приведенной совокупностью признаков, является обеспечение возможности применения схемы при напряжении питания ниже 5 В, исключение дополнительных цепей смещения логических уровней, снижение входной емкости вывода сброса RST или установки хранимого значения SET, снижение входной емкости прямого CLK и инверсного входа тактового сигнала  , снижение количества используемых транзисторов в схеме.

, снижение количества используемых транзисторов в схеме.

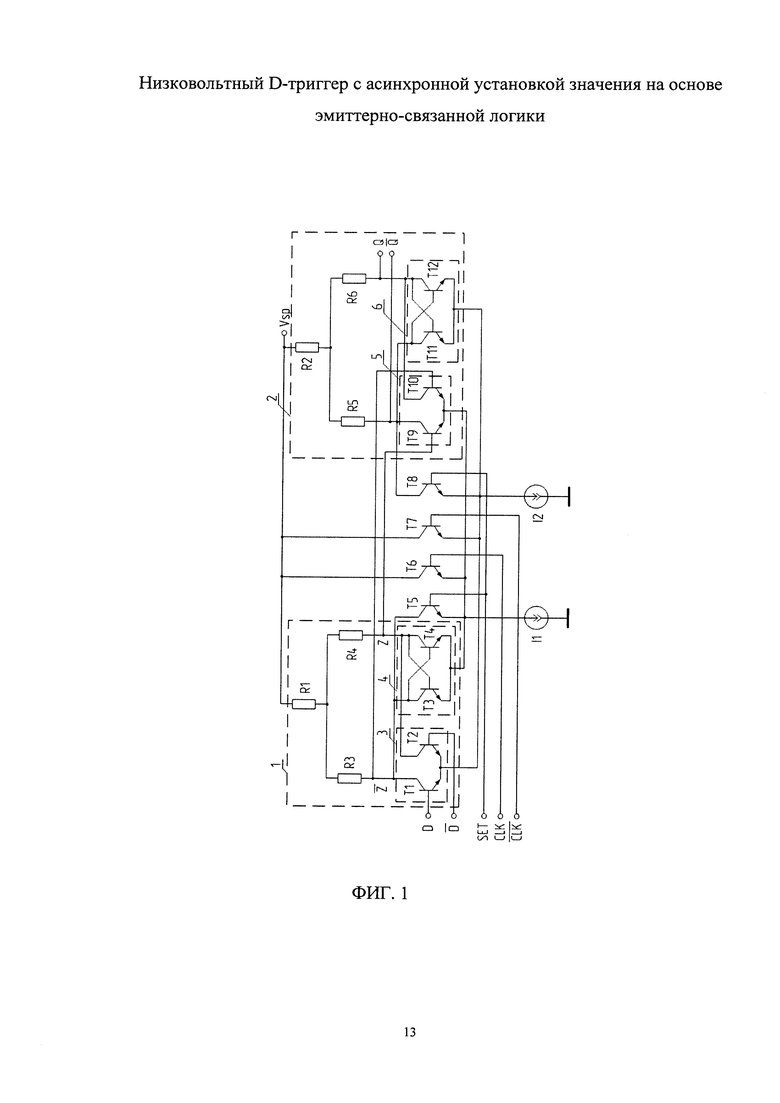

Сущность изобретения поясняется чертежами, на которых изображено:

На фиг. 1 - принципиальная электрическая схема низковольтного D-триггера с асинхронной установкой хранимого значения;

На фиг. 2 - принципиальная электрическая схема низковольтного D-триггера с асинхронным сбросом.

На фиг. 3 - блок-схема программируемого делителя частоты.

Низковольтный D-триггер с асинхронным сбросом, характеризующийся тем, что состоит из одного уровня дифференциальных каскадов 3, 4, 5, 6 и резисторов (R1, R2, R3, R4, R5, R6), образующие ведущий 1 и ведомый 2 триггеры, синхронизируемые по уровню, которые состоят из:

пары транзисторов Т1, Т2 (Т9, Т10) с объединенными эмиттерами первого дифференциального каскада 3(5), усиливающих входной сигнал;

пары транзисторов Т3, Т4 (T11, Т12) с объединенными эмиттерами второго дифференциального каскада 4(6) с положительной обратной связью, образованной соединением базы с коллектором противолежащего транзистора, позволяющих удерживать усиленное первым дифференциальным каскадом логическое значение;

трех резисторов R1, R3, R4 (R2, R5, R6), два из них R3, R4 (R5, R6) подключены к объединенным коллекторам двух транзисторов по одному из первого и второго дифференциальных каскадов, при этом резисторы подключены к шине питания через третий резистор R1 (R2).

При этом объединенные эмиттеры транзисторов первого дифференциального каскада 3 ведущего триггера 1 подключены к объединенным эмиттерам транзисторов второго дифференциального каскада 6 ведомого триггера 2; объединенные эмиттеры транзисторов второго дифференциального каскада 4 ведущего триггера 1 подключены к объединенным эмиттерам транзисторов первого дифференциального каскада 5 ведомого триггера 2; источник постоянного тока I1 подключен к объединенным эмиттерам транзисторов первого дифференциального каскада 3 ведущего триггера 1 и второго дифференциального каскада 6 ведомого триггера 2; источник постоянного тока I2 подключен к объединенным эмиттерам транзисторов второго дифференциального каскада 4 ведущего триггера 1 и первого дифференциального каскада 5 ведомого триггера 2. Тактовый сигнал CLK подается на базу транзистора Т6, а инверсный тактовый сигнал  подается на базу транзистора Т7. Эмиттер транзистора Т6 подключен к объединенным эмиттерам транзисторов второго дифференциального каскада 4 ведущего триггера 1 и к объединенным эмиттерам транзисторов первого дифференциального каскада 5 ведомого триггера 2; коллектор транзистора Т6 подключен к шине питания; эмиттер транзистора Т7 подключен к объединенным эмиттерам транзисторов первого дифференциального каскада 3 ведущего триггера 1 и к объединенным эмиттерам транзисторов второго дифференциального каскада 6 ведомого триггера 2; коллектор транзистора Т7 подключен к шине питания. Сигнал установки значения SET подается на базы двух транзисторов Т5 и Т8. Эмиттер транзистора Т5 подключен к объединенным эмиттерам транзисторов второго дифференциального каскада 4 ведущего триггера 1 и к объединенным эмиттерам транзисторов первого дифференциального каскада 5 ведомого триггера 2; коллектор транзистора Т5 подключен к инверсному выходу ведущего триггера

подается на базу транзистора Т7. Эмиттер транзистора Т6 подключен к объединенным эмиттерам транзисторов второго дифференциального каскада 4 ведущего триггера 1 и к объединенным эмиттерам транзисторов первого дифференциального каскада 5 ведомого триггера 2; коллектор транзистора Т6 подключен к шине питания; эмиттер транзистора Т7 подключен к объединенным эмиттерам транзисторов первого дифференциального каскада 3 ведущего триггера 1 и к объединенным эмиттерам транзисторов второго дифференциального каскада 6 ведомого триггера 2; коллектор транзистора Т7 подключен к шине питания. Сигнал установки значения SET подается на базы двух транзисторов Т5 и Т8. Эмиттер транзистора Т5 подключен к объединенным эмиттерам транзисторов второго дифференциального каскада 4 ведущего триггера 1 и к объединенным эмиттерам транзисторов первого дифференциального каскада 5 ведомого триггера 2; коллектор транзистора Т5 подключен к инверсному выходу ведущего триггера  ; эмиттер транзистора Т8 подключен к объединенным эмиттерам транзисторов первого дифференциального каскада 3 ведущего триггера 1 и к объединенным эмиттерам транзисторов второго дифференциального каскада 6 ведомого триггера 2; коллектор транзистора Т8 подключен к инверсному выходу ведомого триггера

; эмиттер транзистора Т8 подключен к объединенным эмиттерам транзисторов первого дифференциального каскада 3 ведущего триггера 1 и к объединенным эмиттерам транзисторов второго дифференциального каскада 6 ведомого триггера 2; коллектор транзистора Т8 подключен к инверсному выходу ведомого триггера  .

.

Сигнал сброса RST может подаваться на базы двух транзисторов Т5 и Т8, при этом необходимо, чтобы: эмиттер транзистора Т5 подключен к объединенным эмиттерам транзисторов второго дифференциального каскада 4 ведущего триггера 1 и к объединенным эмиттерам транзисторов первого дифференциального каскада 5 ведомого триггера 2; коллектор транзистора Т5 подключен к прямому выходу ведущего триггера Z; эмиттер транзистора Т8 подключен к объединенным эмиттерам транзисторов первого дифференциального каскада 3 ведущего триггера 1 и к объединенным эмиттерам транзисторов второго дифференциального каскада 6 ведомого триггера 2; коллектор транзистора Т8 подключен к прямому выходу ведомого триггера Q.

Работа устройства осуществляется следующим образом.

При поступлении парафазного синхроимпульса на входы CLK, обеспечивается отвод токов источников I1 и I2 на шину питания в обход активной части схемы за счет открытия одного из транзисторов Т6, Т7. Когда ток источника I1 шунтирован, ток источника 12 поровну делится между первым дифференциальным каскадом ведущего триггера и вторым дифференциальным каскадом ведомого триггера, затем при смене фазы синхроимпульса на 180 градусов происходит шунтирование тока источника I2 на шину питания, при этом ток источника I1 поровну делится между вторым дифференциальным каскадом ведущего триггера и первым дифференциальным каскадом ведомого триггера. Процесс захвата логического значения на дифференциальном входе D можно условно разделить на 3 этапа:

обеспечивается отвод токов источников I1 и I2 на шину питания в обход активной части схемы за счет открытия одного из транзисторов Т6, Т7. Когда ток источника I1 шунтирован, ток источника 12 поровну делится между первым дифференциальным каскадом ведущего триггера и вторым дифференциальным каскадом ведомого триггера, затем при смене фазы синхроимпульса на 180 градусов происходит шунтирование тока источника I2 на шину питания, при этом ток источника I1 поровну делится между вторым дифференциальным каскадом ведущего триггера и первым дифференциальным каскадом ведомого триггера. Процесс захвата логического значения на дифференциальном входе D можно условно разделить на 3 этапа:

1) На прямом входе тактового сигнала CLK установлен высокий логический уровень напряжения, на инверсном входе тактового сигнала  установлен низкий логический уровень напряжения, ток источника I1 шунтирован на шину питания, ток источника I2 поровну разделен между первым дифференциальным каскадом ведущего триггера и вторым дифференциальным каскадом ведомого триггера. Обеспечивается усиление значения, установленного на информационном входе для его последующего сохранения в ведущем триггере;

установлен низкий логический уровень напряжения, ток источника I1 шунтирован на шину питания, ток источника I2 поровну разделен между первым дифференциальным каскадом ведущего триггера и вторым дифференциальным каскадом ведомого триггера. Обеспечивается усиление значения, установленного на информационном входе для его последующего сохранения в ведущем триггере;

2) На прямом входе тактового сигнала CLK установлен низкий логический уровень напряжения, на инверсном входе тактового сигнала  установлен высокий логический уровень напряжения, ток источника I2 шунтирован на шину питания, ток источника I1 поровну разделен между вторым дифференциальным каскадом ведущего триггера и первым дифференциальным каскадом ведомого триггера. За счет положительной обратной связи во втором дифференциальном каскаде ведущего триггера обеспечивается удержание захваченного значения на этапе 1), а за счет первого дифференциального каскада ведомого триггера производится усиление хранящегося значения для последующего сохранения в ведомом триггере.

установлен высокий логический уровень напряжения, ток источника I2 шунтирован на шину питания, ток источника I1 поровну разделен между вторым дифференциальным каскадом ведущего триггера и первым дифференциальным каскадом ведомого триггера. За счет положительной обратной связи во втором дифференциальном каскаде ведущего триггера обеспечивается удержание захваченного значения на этапе 1), а за счет первого дифференциального каскада ведомого триггера производится усиление хранящегося значения для последующего сохранения в ведомом триггере.

3) На прямом входе тактового сигнала CLK установлен высокий логический уровень напряжения, на инверсном входе тактового сигнала  установлен низкий логический уровень напряжения, ток источника I1 шунтирован на шину питания, ток источника I2 поровну разделен между первым дифференциальным каскадом ведущего триггера и вторым дифференциальным каскадом ведомого триггера. Обеспечивается усиление значения, установленного на информационном входе, на данном этапе, для его последующего сохранения в ведущем триггере и за счет положительной обратной связи во втором дифференциальном каскаде ведомого триггера обеспечивается удержание значения захваченного на этапе 1).

установлен низкий логический уровень напряжения, ток источника I1 шунтирован на шину питания, ток источника I2 поровну разделен между первым дифференциальным каскадом ведущего триггера и вторым дифференциальным каскадом ведомого триггера. Обеспечивается усиление значения, установленного на информационном входе, на данном этапе, для его последующего сохранения в ведущем триггере и за счет положительной обратной связи во втором дифференциальном каскаде ведомого триггера обеспечивается удержание значения захваченного на этапе 1).

Описанные этапы непрерывно сменяют друг друга, пока происходит смена логических уровней на выводах CLK, в противофазе.

в противофазе.

При установлении на выводе SET высокого логического уровня напряжения, токи источников I1 и I2 шунтируются на шину питания через резисторы R1, R3 и R2, R5 соответственно, обеспечивая необходимое падение напряжения и установку логической единицы на выходах ведущего и ведомого триггеров. Так как эмиттеры транзисторов Т5, Т6, Т7, Т8 объединены, уровень высокого логического напряжения на выводе SET должен быть больше высокого логического уровня напряжения на выводах CLK,  не менее чем на 150 мВ для шунтирования основной части токов источников. При этом, вне зависимости от сигналов на остальных входах D-триггера, обеспечивается асинхронная установка высокого логического уровня напряжения на выходе.

не менее чем на 150 мВ для шунтирования основной части токов источников. При этом, вне зависимости от сигналов на остальных входах D-триггера, обеспечивается асинхронная установка высокого логического уровня напряжения на выходе.

Схема низковольтного D-триггера с асинхронной установкой хранимого значения выполнена на основе одного уровня биполярных дифференциальных каскадов, что обеспечивает возможность однополярного питания схемы напряжением ниже 5 В, при этом обеспечив активный режим работы транзисторов. Это связано с тем, что при снижении напряжения питания наступает момент, когда потенциал на коллекторе становится ниже потенциала базы, после чего транзистор начинает работать в режиме насыщения, поэтому для схем на основе эмиттерно-связанной логики справедливо соотношение Vsp>IR+NVbe+VI,

где Vsp - напряжение питания;

IR - падение напряжения на резисторах в цепи коллектора;

N - количество уровней биполярных дифференциальных каскадов;

Vbe - напряжение открытого р-n перехода база-эмиттер транзистора;

VI - минимально допустимое падение напряжения на источнике тока.

Из этого соотношения видно, что минимально допустимое напряжение питание, при котором обеспечивается активный режим работы транзисторов, достижимо только при N=1, т.е. при одном уровне биполярных дифференциальных каскадов.

Создание низковольтного D-триггера с асинхронным сбросом на основе эмиттерно-связанной логики обеспечивает максимальное быстродействие изделия за счет высокой граничной частоты биполярных транзисторов.

Таким образом, заявленная схема D-триггера с асинхронной установкой значения позволяет успешно создавать быстродействующие программируемые делители частоты с низким энергопотреблением на основе эмиттерно-связанной логики.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХТАКТНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2193273C2 |

| ДВУХТАКТНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ | 1996 |

|

RU2115223C1 |

| СИММЕТРИЧНЫЙ МУЛЬТИПЛЕКСОР НА КОМПЛЕМЕНТАРНЫХ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК (КМОП) ТРАНЗИСТОРАХ | 2018 |

|

RU2689820C1 |

| Источник опорного напряжения | 1974 |

|

SU536484A1 |

| Тактируемый д-триггер | 1979 |

|

SU794723A1 |

| УСТРОЙСТВО для ИЗМЕРЕНИЯ ДЕФОРМАЦИЙ И НАГРУЗОК | 1973 |

|

SU370500A1 |

| Преобразователь напряжения в длительность импульсов | 1990 |

|

SU1785071A1 |

| Преобразователь напряжения в код Грея | 1984 |

|

SU1182687A1 |

| Устройство для управления синхронизированным выключателем переменного тока | 1976 |

|

SU586510A1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ КМОП СУММАТОР | 2011 |

|

RU2454703C1 |

Изобретение относится к области импульсной техники. Технический результат заключается в возможности применения схемы при напряжении питания ниже 5 В, исключении дополнительных цепей смещения логических уравнений, снижении входной емкости вывода сброса RST или установки хранимого значения SET, снижении входной зависимости емкости прямого CLK и инверсного входа тактового сигнала CLK, снижении количества используемых транзисторов в схеме. Для этого предложен низковольтный D-триггер, который состоит из одного уровня дифференциальных каскадов и резисторов, образующих ведущий и ведомый триггеры, синхронизируемые по уровню. Ведущий и ведомый триггеры состоят из пары транзисторов с объединенными эмиттерами первого дифференциального каскада, усиливающих входной сигнал, пары транзисторов с объединенными эмиттерами второго дифференциального каскада с положительной обратной связью, образованной соединением базы с коллектором противолежащего транзистора, позволяющих удерживать усиленное первым дифференциальным каскадом логическое значение, и трех резисторов. 3 ил.

Низковольтный D-триггер с асинхронным сбросом, характеризующийся тем, что состоит из одного уровня дифференциальных каскадов и резисторов, образующих ведущий и ведомый триггеры, синхронизируемые по уровню, которые состоят из:

пары транзисторов с объединенными эмиттерами первого дифференциального каскада, усиливающих входной сигнал;

пары транзисторов с объединенными эмиттерами второго дифференциального каскада с положительной обратной связью, образованной соединением базы с коллектором противолежащего транзистора, позволяющих удерживать усиленное первым дифференциальным каскадом логическое значение;

трех резисторов, два из них подключены к объединенным коллекторам двух транзисторов по одному из первого и второго дифференциальных каскадов, при этом резисторы подключены к шине питания через третий резистор;

источника постоянного тока I1, подключенного к объединенным эмиттерам транзисторов второго дифференциального каскада ведущего триггера и объединенным эмиттерам транзисторов первого дифференциального каскада ведомого триггера;

источника постоянного тока I2, подключенного к объединенным эмиттерам транзисторов первого дифференциального каскада ведущего триггера и объединенным эмиттерам транзисторов второго дифференциального каскада ведомого триггера;

транзистора Т6, эмиттер которого подключен к объединенным эмиттерам транзисторов второго дифференциального каскада ведущего триггера и к объединенным эмиттерам транзисторов первого дифференциального каскада ведомого триггера, коллектор транзистора Т6 подключен к шине питания, а на базу подается тактовый сигнал CLK;

транзистора Т7, эмиттер которого подключен к объединенным эмиттерам транзисторов первого дифференциального каскада ведущего триггера и к объединенным эмиттерам транзисторов второго дифференциального каскада ведомого триггера, коллектор транзистора Т7 подключен к шине питания, а на базу подается инверсный тактовый сигнал  ;

;

транзистора Т5, эмиттер которого подключен к объединенным эмиттерам транзисторов второго дифференциального каскада ведущего триггера и к объединенным эмиттерам транзисторов первого дифференциального каскада ведомого триггера, коллектор транзистора Т5 подключен к инверсному выходу ведущего триггера  , а на базу транзистора Т5 подается сигнал установки значения SET или коллектор транзистора Т5 подключен к прямому выходу ведущего триггера Z, а на базу транзистора Т5 подается сигнал сброса RST;

, а на базу транзистора Т5 подается сигнал установки значения SET или коллектор транзистора Т5 подключен к прямому выходу ведущего триггера Z, а на базу транзистора Т5 подается сигнал сброса RST;

транзистора Т8, эмиттер которого подключен к объединенным эмиттерам транзисторов первого дифференциального каскада ведущего триггера и к объединенным эмиттерам транзисторов второго дифференциального каскада ведомого триггера, коллектор транзистора Т8 подключен к инверсному выходу ведомого триггера  , а на базу транзистора Т8 подается сигнал установки значения SET или коллектор транзистора Т8 подключен к прямому выходу ведомого триггера Q, а на базу транзистора Т8 подается сигнал сброса RST.

, а на базу транзистора Т8 подается сигнал установки значения SET или коллектор транзистора Т8 подключен к прямому выходу ведомого триггера Q, а на базу транзистора Т8 подается сигнал сброса RST.

| US 7215170 B1, 08.05.2007 | |||

| US 5122682 A1, 16.06.1992 | |||

| US 5850155 A1, 15.12.1998 | |||

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1980 |

|

SU852131A1 |

Авторы

Даты

2019-09-09—Публикация

2016-01-12—Подача