Изобретение относится к полупроводниковой микроэлектронике, в частности к D-триггерам ЭСЛ-типа по принципу M-S (главный - вспомогательный) и может быть использовано в интегральных схемах для построения блоков хранения и сдвига информации.

Цель изобретения - расширение функциональных возможностей устройства путем введения новых конструк- тивных признаков, обеспечивающих асинхронную установку D-триггера в единицу или в нуль.

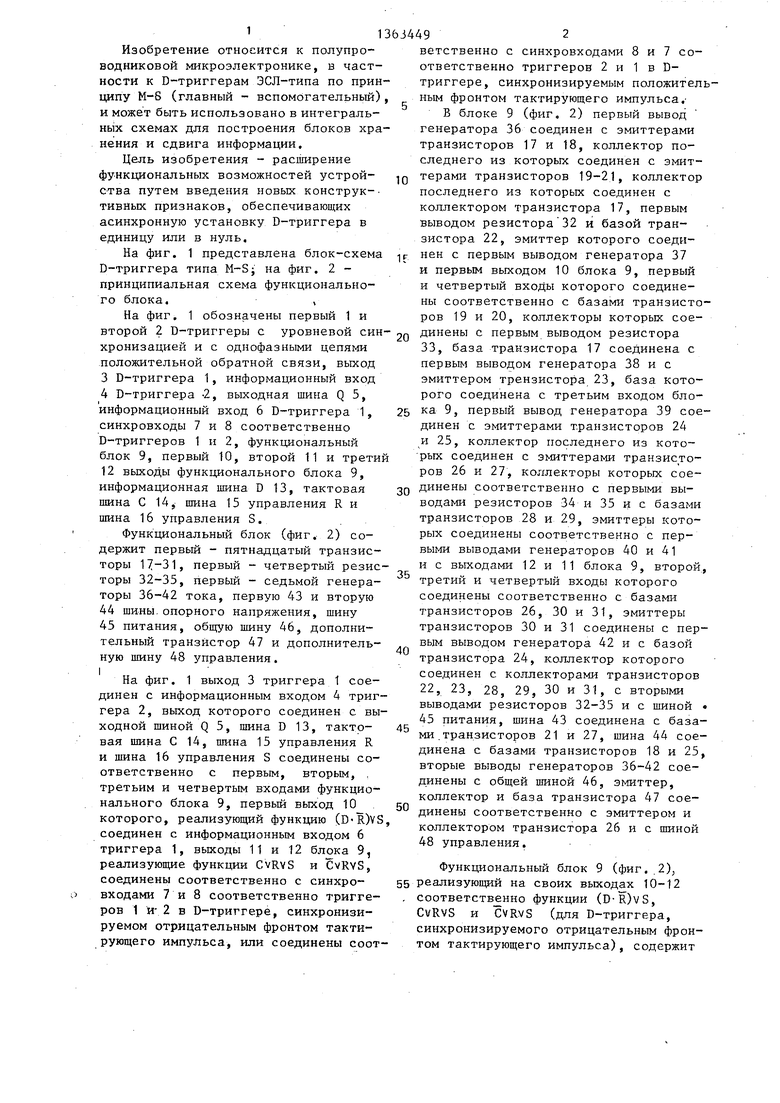

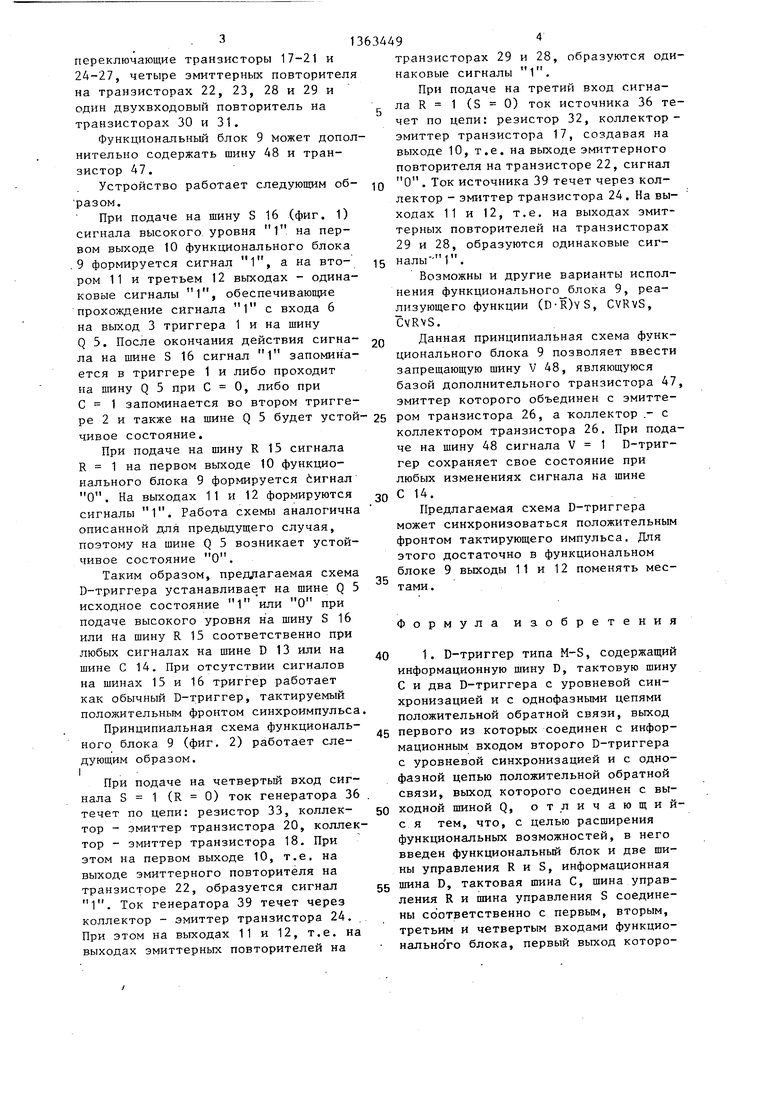

На фиг. 1 представлена блок-схема D-триггера типа M-S; на фиг. 2 - принципиальная схема функционального блока.,

На фиг. 1 обозначены первый 1 и второй 2 D-триггеры с уровневой синхронизацией и с однофазными цепями положительной обратной связи, выход

3D-триггера 1, информационный вход

4D-триггера -2, выходная шина Q 5, информационный вход 6 D-триггера 1, синхровходы 7 и 8 соответственно D-триггеров 1 и 2, функциональный блок 9, первый 10, второй 11 и трети 12 вькоды функционального блока 9, информационная шина D 13, тактовая шина С 14, шина 15 управления R и шина 16 управления S.

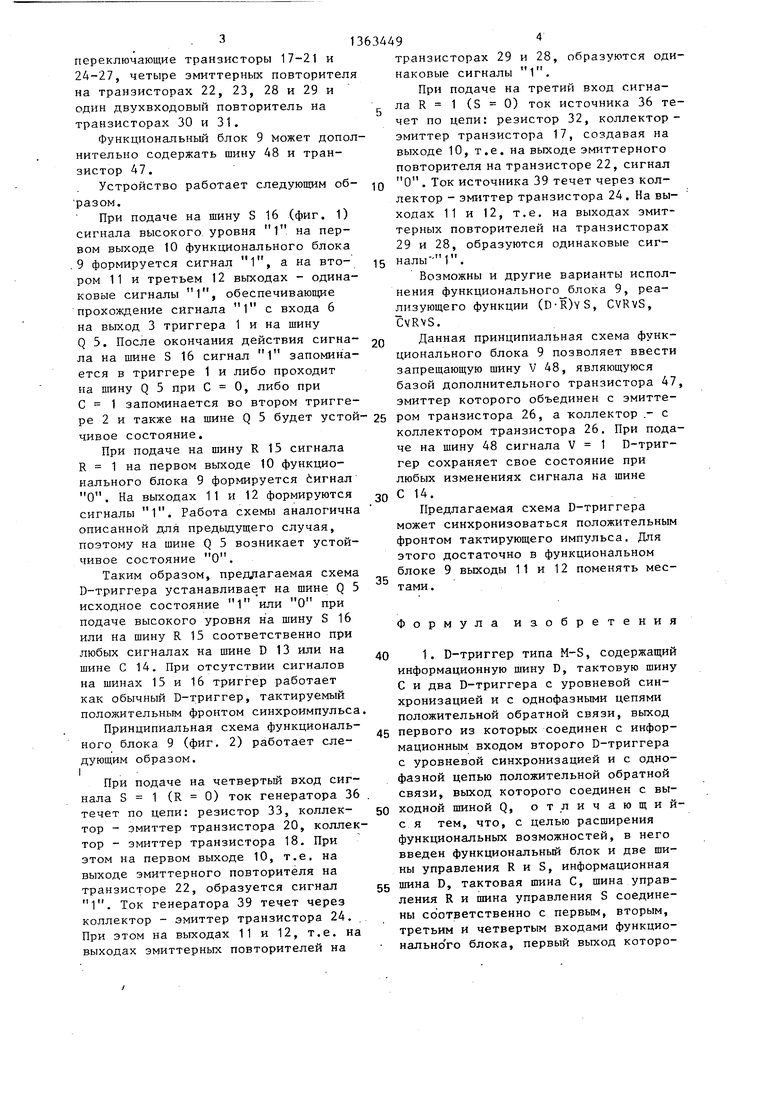

Функциональный блок (фиг. 2) содержит первый - пятнадцатый транзисторы 17-31, первый - четвертый резисторы 32-35, первьш - седьмой генераторы 36-42 тока, первую 43 и вторую

44шины.опорного напряжения, шину

45питания, общую шину 46, дополнительный транзистор 47 и дополнительную шину 48 управления.

На фиг. 1 выход 3 триггера 1 соединен с информационным входом 4 триггера 2, выход которого соединен с выходной шиной Q 5, шина D 13, тактовая шина С 14J шина 15 управления R и шина 16 управления S соединены соответственно с первым, вторым, , третьим и четвертым входами функционального блока 9, первый выход 10 которого, реализующий функцию (D R)VS соединен с информационным входом 6 триггера 1, выходы 11 и 12 блока 9, реализующие функции CvRvS и CvRYS, соединены соответственно с синхро- входами 7 и 8 соответственно триггеров 1 и- 2 в D-триггере, синхронизируемом отрицательным фронтом тактирующего импульса, или соединены соот

F

0

5

0

ветственно с синхровходами 8 и 7 соответственно триггеров 2 и 1 в D- триггере, синхронизируемым положительным фронтом тактирующего импульса.- В блоке 9 (фиг. 2) первый вывод генератора 36 соединен с эмиттерами транзисторов 17 и 18, коллектор последнего из которых соединен с эмиттерами транзисторов 19-21, коллектор последнего из которьк соединен с коллектором транзистора 17, первым выводом резистора 32 и базой транзистора 22, эмиттер которого соединен с первым выводом генератора 37 и первым выходом 10 блока 9, первый и четвертый входы которого соединены соответственно с базами транзисторов 19 и 20, коллекторы которых соединены с первым выводом резистора 33, база транзистора 17 соединена с первым выводом генератора 38 и с эмиттером трензистора 23, база которого соединена с третьим входом блока 9, первый вывод генератора 39 соединен с эмиттерами транзисторов 24 и 25, коллектор последнего из кото- рых соединен с эмиттерами транзисторов 26 и 27, коллекторы которых соединены соответственно с первыми выводами резисторов 34 и 35 и с базами транзисторов 28 и 29, эмиттеры которых соединены соответственно с первыми выводами генераторов 40 и 41 и с выходами 12 и 11 блока 9, второй, третий и четвертый входы которого соединены соответственно с базами транзисторов 26, 30 и 31, эмиттеры транзисторов 30 и 31 соединены с первым выводом генератора 42 и с базой транзистора 24, коллектор которого соединен с коллекторами транзисторов 22, 23, 28, 29, 30 и 31, с вторыми выводами резисторов 32-35 и с шиной 45 питания, шина 43 соединена с базами .транзисторов 21 и 27, шина 44 соединена с базами транзисторов 18 и 25, вторые выводы генераторов 36-42 соединены с общей шиной 46, эмиттер, коллектор и база транзистора 47 соединены соответственно с эмиттером и коллектором транзистора 26 и с шиной 48 управления.

Функциональный блок 9 (фиг..2), 5 реализующей на своих выходах 10-12 . соответственно функции (D-R)vS, CvRVS и CVRVS (для D-триггера, синхронизируемого отрицательным фронтом тактирующего импульса), содержит

5

0

5

0

5

10

1363449

переключающие транзисторы 17-21 и 24-27, четыре эмиттерных повторителя на транзисторах 22, 23, 28 и 29 и один двухвходовый повторитель на транзисторах 30 и 31.

Функциональный блок 9 Может дополнительно содержать шину 48 и транзистор 47.

Устройство работает следующим об- разом.

При подаче на шину S 16 (фиг. 1) сигнала высокого уровня 1 на первом выходе 10 функционального блока 9 формируется сигнал 1, а на вто- 15 ом 11 и третьем 12 выходах - одинаковые сигналы 1, обеспечивающие прохождение сигнала 1 с входа 6 на выход 3 триггера 1 и на шину Q 5. После окончания действия сигна- 20 а на шине S 16 сигнал 1 запоминается в триггере 1 и либо проходит на шину Q 5 при С О, либо при 1 запоминается во втором триггетрна

ла че эм вы по О ле хо те 29 на

не ли CV

ци за ба эм

ре 2 и также на шине Q 5 будет устой- 25 ром транзистора 26, а коллектор .- с

чивое состояние.

При подаче на шину R 15 сигнала R 1 на первом выходе 10 функционального блока 9 формируется Сигнал О. На выходах 11 и 12 формируются сигналы 1. Работа схемы аналогична описанной для предьщущего случая, поэтому на шине Q 5 возникает устойчивое состояние О.

Таким образом, предлагаемая схема D-триггера устанавливает на шине Q 5 исходное состояние 1 или О при подаче высокого уровня на шину S 16 или на шину R 15 соответственно при любых сигналах на шине D 13 или на шине С 14. При отсутствии сигналов на шинах 15 и 16 триггер работает как обычный D-триггер, тактируемый положительным фронтом синхроимпульса

Принципиальная схема функционального блока 9 (фиг, 2) работает следующим образом. I

При подаче на четвертый вход сигнала (R 0) ток генератора 36 течет по цепи: резистор 33, коллектор - эмиттер транзистора 20, коллектор - эмиттер транзистора 18. При этом на первом выходе 10, т.е. на выходе эмиттерного повторителя на транзисторе 22, образуется сигнал 1. Ток генератора 39 течет через коллектор - эмиттер транзистора 24. При этом на выходах 11 и 12, т.е. на выходах эмиттерных повторителей на

5

0

449

5 0

4

транзисторах 29 и 28, образуются одинаковые сигналы 1.

При подаче на третий вход сигнала R 1 () ток источника 36 течет по цепи: резистор 32, коллектор- эмиттер транзистора 17, создавая на выходе 10, т.е. на выходе эмиттерного повторителя на транзисторе 22, сигнал О . Ток источника 39 течет через коллектор - эмиттер транзистора 24. На выходах 11 и 12, т.е. на выходах эмиттерных повторителей на транзисторах 29 и 28, образуются одинаковые сиг- налы- Ч.

Возможны и другие варианты исполнения функционального блока 9, реализующего функции (D-R)YS, CVRVS, CVRVS.

Данная принципиальная схема функционального блока 9 позволяет ввести запрещающую шину V 48, являющуюся базой дополнительного транзистора 47, эмиттер которого объединен с эмиттеколлектором транзистора 26. При подаче на шину 48 сигнала V 1 D-триггер сохраняет свое состояние при любых изменениях сигнала на шине С 14.

Предлагаемая схема D-триггера может синхронизоваться положительным фронтом тактирующего импульса. Для этого достаточно в функциональном блоке 9 выходы 11 и 12 поменять мес

теми.

Формула изобретения

1. D-триггер типа M-S, содержащий информационную шину D, тактовую шину С и два D-триггера с уровневой синхронизацией и с однофазными цепями положительной обратной связи, выход

первого из которых соединен с информационным входом второго D-триггера с уровневой синхронизацией и с однофазной цепью положительной обратной связи, выход которого соединен с выходной шиной Q, отличающий- с я тем, что, с целью расширения функциональных возможностей, в него введен функциональный блок и две шины управления R и S, информационная

шина D, тактовая шина С, шина управления R и шина управления S соединены соответственно с первым, вторым, третьим и четвертым входами функцио- нально го блока, первый выход которого, реализующий функцию (D.R)vS, соединен с информационнь1м входом первого D-триггера с уровневой синхронизацией и с однофазной цепью положительной обратной связи, второй и третий вьцсоды функционального блока, реализующие функции соответственно CVRyS и CVRVS. (CVRVS и CVRVS), соединены соответственно с синхровходами пер - вого и второго D-триггеров с уровневой синхронизацией и с однофазными цепями положительной обратной связи.

2. Устройство по п. 1, отличающееся тем, что функциональный блок содержит семь генераторов тока, четыре резистора, две шины

25

опорного напряжения, пятнадцать тран- 20 нального блока, второй, третий и чет- зисторов, шину питания и общую шину, первый вывод первого генератора тока соединен с эмиттерами первого и второго транзисторов, коллектор последнего из которых соединен с эмиттерами третьего, четвертого и пятого транзисторов, коллектор последнего из которых соединен с коллектором первого транзистора, с первым выводом первого резистора и с базой шестого транзистора, эмиттер которого соединен с первым выводом второго генератора тока и с первым выходом функционального блока, первый и четвертый,входы которого соединены соответственно с базами третьего и четвертого Транзисторов, коллекторы которых соединены с первым выводом второго резистора, база первого транзис30

35

вертыи входы-которого соединены соответственно с базами десятого, четырнадцатого и пятнадцатого транзисторов, эмиттеры двух последних из которых соединены с первым выводом седьмого генератора тока и с базой восьмого транзистора, коллектор которого соединен с коллекторами шестого, седьмого, двенадцатого, тринадцатого, четырнадцатого, пятнадцатого транзисторов, с вторыми выводами всех резисторов и с шиной питания, первая шина опорного напряжения соединена с базами пятого и одиннадцатого транзисторов, вторая шина опорного напряжения соединена с базами второго и девятого транзисторов, вторые выводы всех генераторов тока соединены с общей шиной.

тора соединена с первым выводом третьего генератора тока и с эмитте- ром седьмого транзистора, база которого соединена с третьим входом функ-

ционального блока, первый вывод четвертого генератора тока соединен с эмиттерами восьмого и девятого транзисторов, коллектор последнего из которых соединен с эмиттерами десятого и одиннадцатого транзисторов, колдекторы которых соединены соответственно с первыми выводами третьего и четвертого резисторов и с базами двенадцатого и тринадцатого транзисторов, эмиттеры которых соединены соответственно с первыми выводами пятого и шестого генераторов тока и с третьим и вторым выходами функцио

нального блока, второй, третий и чет-

вертыи входы-которого соединены соответственно с базами десятого, четырнадцатого и пятнадцатого транзисторов, эмиттеры двух последних из которых соединены с первым выводом седьмого генератора тока и с базой восьмого транзистора, коллектор которого соединен с коллекторами шестого, седьмого, двенадцатого, тринадцатого, четырнадцатого, пятнадцатого транзисторов, с вторыми выводами всех резисторов и с шиной питания, первая шина опорного напряжения соединена с базами пятого и одиннадцатого транзисторов, вторая шина опорного напряжения соединена с базами второго и девятого транзисторов, вторые выводы всех генераторов тока соединены с общей шиной.

33

32

22 iO

Редактор А.Огар

Составитель Н.Ранов Техред М.Ходанич

Заказ 6378/52 Тираж 900Подписное

БНИИПИ Государственного комитета СССР

.по делам изобретений и открытий 113035, Москва, Ж-35, Раушск ая наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг. 2

Корректор Л.Пилипенко

| название | год | авторы | номер документа |

|---|---|---|---|

| Д-триггер с селектором на входе | 1989 |

|

SU1707741A1 |

| Однофазный D-триггер | 1988 |

|

SU1647855A1 |

| Д-триггер ЭСЛ - типа | 1989 |

|

SU1644368A1 |

| Близостный переключатель | 1988 |

|

SU1539855A1 |

| Многопортовое запоминающее устройство | 1990 |

|

SU1718270A1 |

| Компаратор напряжения | 1989 |

|

SU1653149A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1560987A1 |

| Логическая ячейка | 1985 |

|

SU1248056A1 |

| СИНХРОННЫЙ ГЕНЕРАТОР С ПРЕЦИЗИОННОЙ СИСТЕМОЙ УПРАВЛЕНИЯ | 2005 |

|

RU2295192C1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

Изобретение относится к полупроводниковой микроэлектронике и может быть использовано для построения, блоков хранения и сдвига информации. Цель изобретения - расширение функциональных возможностей устройства. D-триггер типа M-S содержит D-триг- геры 1 и 2 с уровневой синхронизацией и однофазными цепями положительной обратной связи и шины 13 и 14 - информационную D и тактовую С. Введение функционального блока 9 и шин 14 и 15 управления R и S обеспечивает асинхронную установку D-триггера в единицу или в нуль. В описании приведен пример реализации функционального блока 9. 1 з.п. ф-лы, 2 ил. (Л Фиг.1

| ECL Data book, Fairchild Camera and Instrument Corporation, California, 1977, p | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Troubridge Mattew Low-power high performance ECL gate arrays | |||

| Машина для разделения сыпучих материалов и размещения их в приемники | 0 |

|

SU82A1 |

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

| Насос | 1917 |

|

SU13A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

Авторы

Даты

1987-12-30—Публикация

1986-01-06—Подача