Изобретение относится к импульсной технике и может быть использовано в буферных регистрах памяти цифровых устройств автоматики и информационно-измерительных и вычислительных комплексов.

Цель изобретения - повышение надежности, достоверности записи информации и быстродействия и расширение функциональных возможностей.

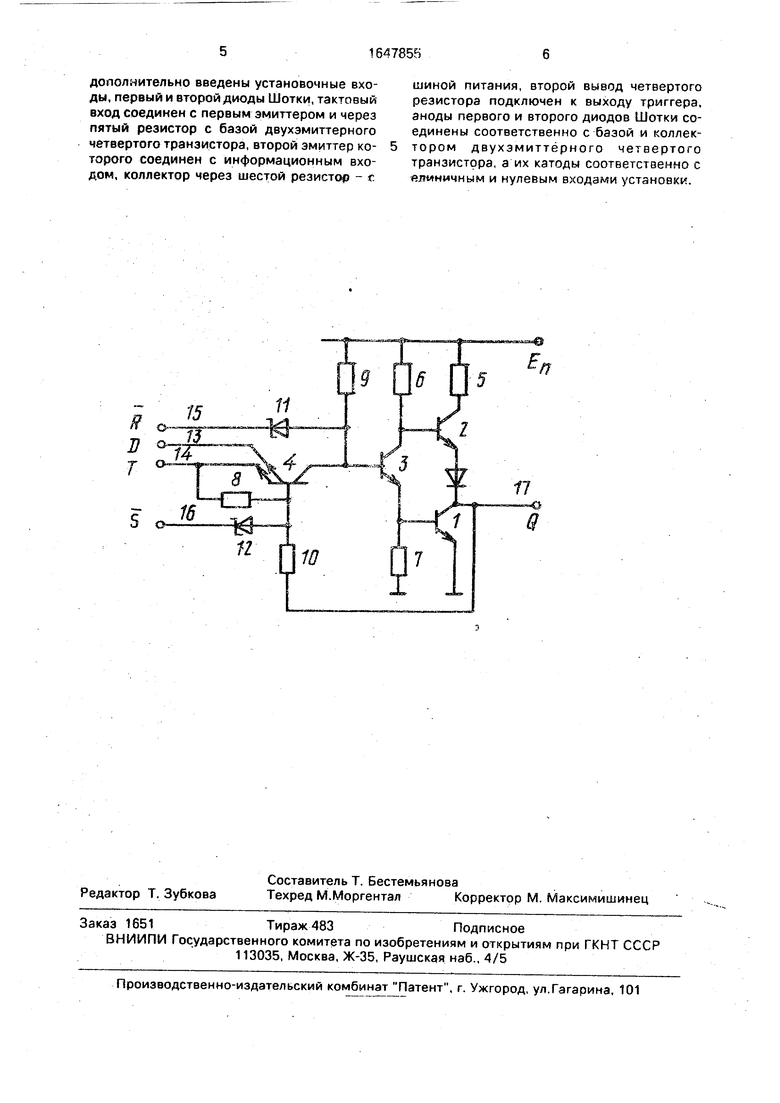

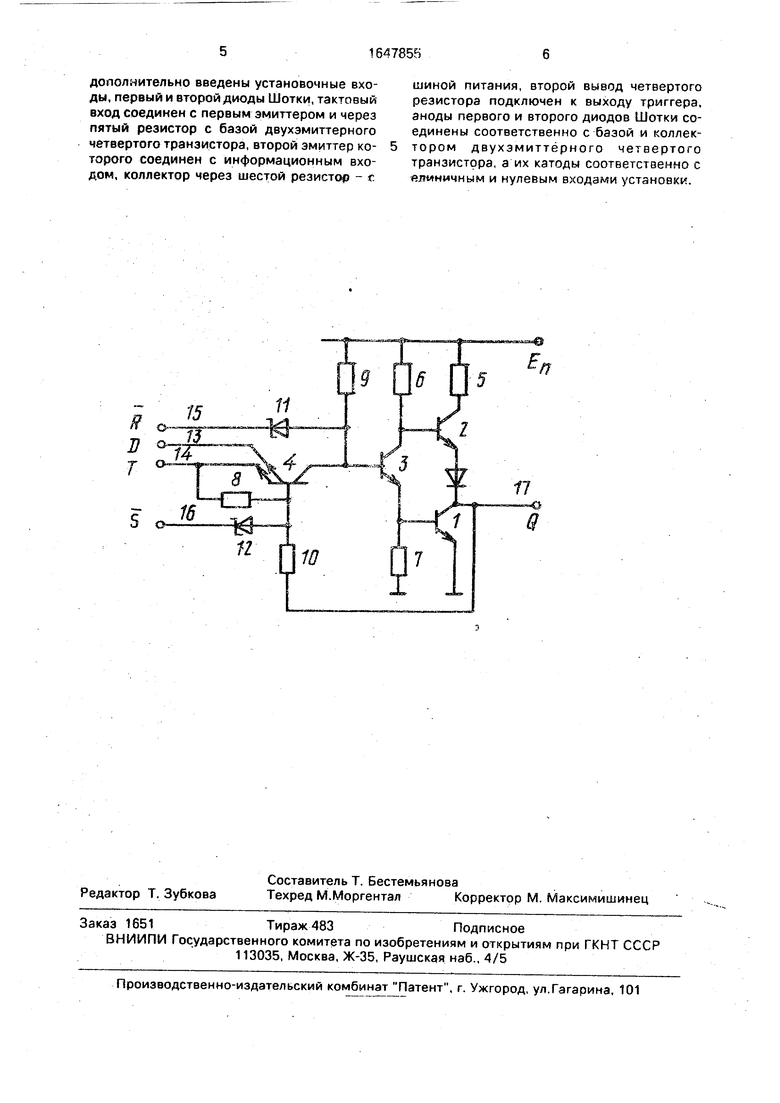

На чертеже показана схема предлагаемого однофазного D-триггера.

Устройство содержит инвертор на первом транзисторе 1, эмиттер которого соединен с общей шиной, коллектор через диод в прямом относительно источника питания включении - с эмиттером эмиттерного повторителя на втором транзисторе 2, база которого подключена к коллектору фазораз- делительного третьего транзистора 3, база которого соединена с коллектором двух- эмиттерного четвертого транзистора 4, коллектор второго транзистора 2 через первый резистор 5 соединен с шиной питания, к которой через третий резистор 6 подключена база второго транзистора 2, эмиттер фа- зоразделительного третьего транзистора 3 подключен к базе первого транзистора 1 и через второй резистор 7 - к общей шине, первый вывод пятого резистора 8 соединен с базой двухэмиттерного четвертого транзистора 4, коллектор которого через шестой резистор 9 соединен с шиной питания, а база - с первым выводом четвертого резистора 10, коллектор и база двухэмиттерного четвертого транзистора 4 соединены также с анодами второго 11 и первого 12 диодов Шотки соответственно, а его второй и первый эмиттеры - соответственно с информа- ционным 13 и тактовым 14 входами триггера, тактовый 14 вход соединен также с вторым выводом пятого резистора 8, нулевой 15 и единичный 16 входы триггера соединены с катодами соответственного второго 11 и первого 12 диодов, второй вывод четвертого резистора 10 соединен с выходом триггера 17.

Предлагаемый D-триггер работает следующим образом

сл

о

00

ел

СП

В исходном состоянии на тактовом ходе 14 присутствует нулевой потенциал Т 0) и в зависимости от состояния выхода 17 триггера по цепи обратной связи резитор 10 - переход база - первый эмиттер ранзистора 4 - вход 14 будет протекать или не протекать ток, задавая открытое или закрытое состояние транзистора 4.

Если на выходе 17 триггера - единичный потенциал (Q 1), то через указанный переход протекает базовый ток, транзистор 4 открыт и шунтирует базовую цепь фазо- разделительного транзистора 3, на коллекторе которого поддерживается высокий потенциал, поступающий через эмиттерный повторитель на транзисторе 2 на выход триггера. Если на выходе 17 триггера - нулевой потенциал (Q - 0), то транзистор 4 будет заперт по базе, а ток через резистор 9 потечет в базо-эмиттерные переходы транзисторов 3 и 2, которые отпираются, и на выходе триггера поддерживается поэтому нулевой потенциал, т.е. схема обладает трмггерными свойствами и при Т 0 сохраняет ранее поступившую информацию, а изменения ее на входе D не могут изменить состояние схемы и передаться на выход Q, что описывается логическим выражением

Qn + t QnT . (1)

Запись информации в триггер происходит при поступлении на тактовый вход 14 единичного потенциала Т 1, который запирает первый эмиттерный переход транзистора 4. Если при этом информационный сигнал на входе 13 имеет нулевое значение О 0, то через базовый резистор 8 и второй змиттерный переход будет протекать ток, открывающий транзистор 4, который шун- тирует базовую цепь транзистора 3. На коллекторе последнего формируется высокий (единичный) потенциал, поступающий через эмиттерный повторитель на транзисторе 2 на выход 17триггера (Q - 1)и генерирующий в цепи обратной связи ток, втекающий через резистор 10 в базу транзистора 4 и действующий согласно с током через резистор 8 от сигнала Т 1, т.е. сигнал обратной связи дублирует воздействие сигналов Т 1 и D О на транзистор4, поддерживая его в открытом состоянии.

Если информационный сигнал имеет единичное значение D 1 при Т 1, оба эмиттерных перехода транзистора 4 и он сам запираются, а ток через резистор 9 втекает в базо-эмиттерные переходы транзисторов 3 и 2, отрывая последние. На выходе 17 триггера устанавливается нулевой потенциал (Q 0), который по цепи обратной связи через резистор 10 дополнительно запирает транзистор 4 по базе, т.е. сигнал

обратной связи и в этом случае дублирует действие сигналов транзистор 4.

Поэтому по окончании единичного тактового сигнала с приходом его отрицательного фронта запирание первого эмиттерного перехода транзистора 4 и фиксирование записавшейся в триггер информации происходит с высокой надежностью

0 и практически мгновенно, без каких-либо переключений в цепи обратной связи (в отличие от известных триггеров), что повышает быстродействие.

Так как при Т 1 все изменения записываемой информации с входа D передаются на выход Q триггера в текущем (п + 1)-м такте с инверсией, то режиму записи соответствует логическое выражение Qn+1 Drn-iT. (2)

0 Тогда логическое уравнение предлагаемого триггера на основании (1) и (2) будет иметь вид

Qn+l - Dn+lT + QnT , где n - предыдущий такт.

5 Для установки триггера, в определенное состояние на входы 15 и 16 подается нулевой установочный уровень, при котором открывается соответствующий диод Шотки 11 или 12 и шунтируется базовая цепь транзи0 сторов 3 или 4t который закрывается, и на выходе 17 триггера устанавливается соответствующий потенциал Q 1 или 0 0. Диоды Шотки, имея порог открытия почти вдвое меньший, чем у транзисторов, надеж5 но обеспечивают возможность установки триггера в нужное состояние.

Формула изобретения Однофазный D-триггер, содержащий информационный и тактовый входы, выход,

0 инвертор на первом транзисторе, эмиттер которого соединен с общей шиной, коллектор - с выходом триггера, эмиттерный повторитель на втором транзисторе, коллектор которого через первый резистор

5 соединен с шиной питания, эмиттер через диод в прямом включении - с выходом триггера, базы первого и второго транзисторов соединены соответственно через второй и третий резисторы с общей шиной и шиной

0 питания, а также соответственно с эмиттером и коллектором фазоразделительного третьего транзистора, база которого соединена с коллектором двухэмиттерного четвертого транзистора, база которого

5 соединена с первым выводом четвертого резистора, пятый и шестой резисторы, отличающийся тем, что, с целью повышения надежности и достоверности записи информации, повышения быстродействия и расширения функциональных возможностей,

дополнительно введены установочные входы, первый и второй диоды Шотки, тактовый вход соединен с первым эмиттером и через пятый резистор с базой двухэмиттерного четвертого транзистора, второй эмиттер которого соединен с информационным входом, коллектор через шестой резистор - г

шиной питания, второй вывод четвертого резистора подключен к выходу триггера, аноды первого и второго диодов Шотки соединены соответственно с базой и коллектором двухэмиттерного четвертого транзистора, а их катоды соответственно с етшнмчным и нулевым входами установки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный Д(Т)-триггер | 1988 |

|

SU1561200A1 |

| Троичный счетный триггер | 1979 |

|

SU864503A1 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| Трехвходовой дешифратор | 1974 |

|

SU517155A1 |

| Синхронный @ -триггер | 1989 |

|

SU1684911A1 |

| Логический элемент | 1983 |

|

SU1138941A1 |

| Д-триггер | 1988 |

|

SU1562962A1 |

| Т-триггер (его варианты) | 1984 |

|

SU1226615A1 |

| Дешифратор | 1988 |

|

SU1658210A1 |

| Усилитель считывания | 1986 |

|

SU1368918A1 |

Изобретение относится к импупьсной технике и может использоваться в буферных регистрах памяти цифровых устройств автоматики. Целью изобретения является повышение надежности, достоверности записи информации и быстродействия и расширение функциональных возможностей. Устройство содержит инвертор на транзисторе 1, эмиттерный повторитель на транзисторе 2, фазоразделительный транзистор 3, двухэмиттерный транзистор 4, резисторы 5-10, Для достижения поставленной цели в устройство введены установочные входы 15, 16, диоды Шотки 11. 12 и новые функциональные связи. 1 ил.

Т

| @ -Триггер (его варианты) | 1984 |

|

SU1188861A1 |

| ФОРМА ДЛЯ БРИКЕТОВ | 1919 |

|

SU286A1 |

| ВСЕСС-.'ОаНАЯ^^АТ11йу-;-:::::;;'г-5-^[&ИЙЛИО гиНА [ | 0 |

|

SU378956A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-05-07—Публикация

1988-12-15—Подача