1

Изобретение относится к электро;технике,в частности к преобразователям напряжения для электронных часов и других аналогичных приборов с жидкокристаллическим индикатором.

Известен преобразователь напряжв:ния, содержащий схему умножения напряжения и КМДП-усилитель уровня с парафазным выходом. Схема умножения напряжения содержит два каскада для получения высокого напряжения,выходной МДП-транзистор, тип проводимости которого соответствует полярности преобразуемого напряжения, и выходной сглаживающий конденсатор. Каждый каскад для получения высокого напряжения содержит КМДП-инвертор, МДПтранзистор, тип проводимости которого соответствует полярности преобразуемого напряжения, и накопительный конденсатор СИ

Недостатком данного преобразователя напряжения является большой собственный ток потребления, что обусловлено особенностью известных схем КМДП-усилителей уровня с пара фазным выходом фронт переключения одного из выходов в состояние усиливаемого уровня потенциала запаздывает по отношению к cooTaeTCTjyMineму фронту переключения второго выхода. Это приводит к тому, что при переключении МДП-транзисторов схемы умножения напряжения имеют место паразитные состояния одновременной проводимости МДП-транзисторов, следствием чего является наличие паразитных токов между выходной и пита10ющими шинами преобразователя напряжения.

Наиболее близким по технической сущности к предлагаемому источнику питания .является преобразовательная

15 ячейка, содержащая каскад умножения напряжения, состоящий из накопитель ного конденсатора, подключенного к выходу первого КМДП-инвертора и точке соединения истока питающего и

20 стока выходного МДП-транзисторов с типом проводимости,соответствующим полярности преобразуемого напряжения, при зтом исток транзистора КМДПйнвертора с типом проводимости соот25ветствующим полярности преобразуемого напряжения и сток питающего МДП-транзистора соединены с источником напряжения, сток другого транзистора КМДП-инвертора обратного типа

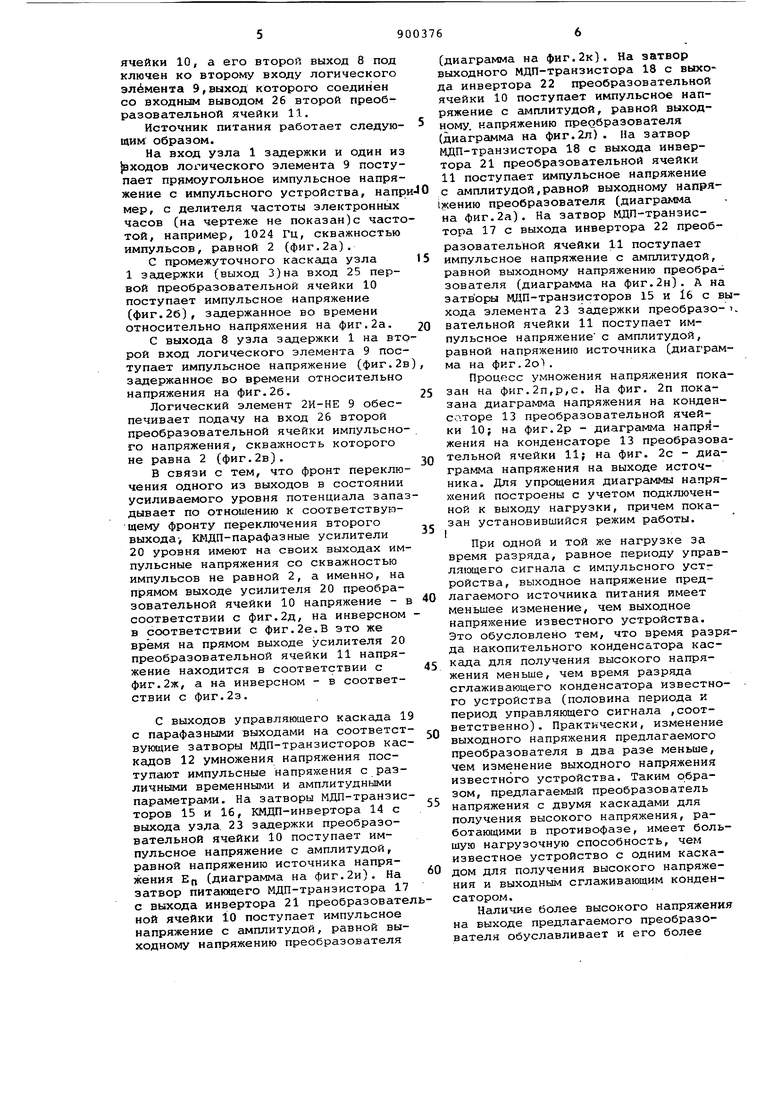

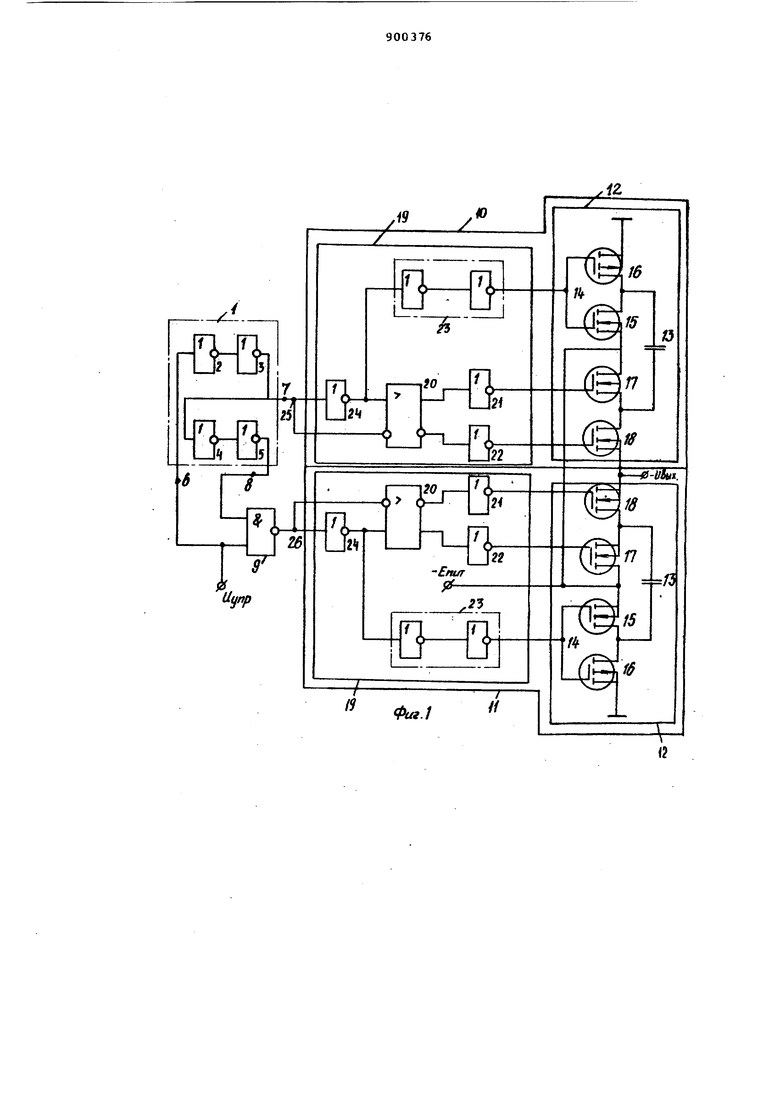

30 проводимости образует общий вывод ячейки, а исток выходного МДП-транзистора - выходной вывод, между кото рым включен выходной сглаживающий конденсатор, а также управляющий каскад, состоящий из парафазного уси лителя, прямой выход которого через второй КМДП-инвертор подключен к затвору питающего МДП-транзистора, а инверсный - через третий КМДП-инвертор - к затвору выходного МДПтранзистора, причем вход усилителя образует управляющий вход ячейки и через узел задержки связан со входо первого КМДП-инвертора 2. Однако известный преобразователь напряжения отличается низкой нагрузочной способностью, не удовлетворя щей жестким требованиям, предъявляемым к преобразователю напряжения при использовании его в электронных часах с мультиплексным управлением жидкокристаллического индикатора. Это приводит к тому,что уменьшается надежность жидкокристаллического индикатора,имеющего предельно допус тимую постоянную составляющую управ ляющего сигнала порядка 50 мВ. Низкая нагрузочная способность обуслав ливает низкий КПД,так как снижается полезная мощность преобразователя. Цель изобретения - повышение КПД и нагрузочной способности. Поставленная цель достигается те что в устройство,содержащее преобра зовательную ячейку с каскадом умножения напряжения, состоящим из нако пительного конденсатора, подключенного к выходу первого КМДП-инвертора и точке соединения истока питающего и стока выходного МДП-транзисторов с типом проводимости,соответствующим полярности преобразуемого напряжения, при этом исток транзистора КМДП-инвертора с типом- проводи мости, соответствующим полярности преобразуемого напряжения, и сток питающего НДП-транзистора подключен к входному выводу источника, сток другого транзистора КМДП-инвертора обратного типа проводимости образует общий вывод ячейки, а исток выходного МДП-транзистора - выходно вывод ячейки, а также управляющий каскад,состоящий из парафазного усилитеитя, прямой выход которого че рез второй КМДП-инвертор подключен i к затвору питающего МДП-транзистора каскада умножения, а инверсный - че рез третий КМДП-инверхор - к затвору выходного МДП-транзистора, приче вход усилителя образует входной вывод .ячейки, который через узел задержки связан со входом первого КМДП-инвертора, введены вторая аналогичная преобразовательная ячейка, дополнительный узел задержки и логи ческий элемент, при этом тактовый вход устройства соединен с одним из входов логического элемента и входом дополнительного узла задержки, первый выход которого подключен к входному выводу первой преобразовательной ячейки, а его второй выход ко второму входу логического элемента, выход которого соединен со входным выводом второй преобразовательной ячейки, а выходы преобразовательных ячеек объединены параллельно и образуют выходные выводы устройства. На фиг.1 приведена структурная схема источника питания; на фиг.2 диаграммы напряжений, описывакядие цикл работы устройства. Источник питания содержит дополнительный узел 1 задержки, состоящий из четного числа КМДП-инверторов 2,3,4,5 с входным выводом 6 и двумя выходными выводами 7 и 8, логический элемент 9 и две преобразовательные ячейки 10 и 11. Каждая из преобразовательных ячеек содержит каскад 12 умножения напряжения, состоящий из накопительного конденсатора 13, подключенного к выходу первого КМДП-инвертора 14 на МДП-транзисторах 15 и 16 разного типа проводимости и точке соединения истока питающего 17 и стока выходного 18 МДП-транзисторов с типом проводимости, соответствующим полярности преобразуемого напряжения. Исток транзистора 16 КМДП-инвертора 14 с типом проводимости, соответствующим полярности преобразуемого напряжения, и сток питакяцего МДП-транзистора 17 подключены к входному выводу источника . Сток транзистора 15 КМДПинвертора 14 обратного типа проводимости образует общий вывод ячейки Корпус, а исток выходного МДП-транзистора 18 выходной вывод ячейки Управляющий каскад 19 содержит парафазный усилитель 20 уровня, прямой выход которого через второй КМДП-инвертор 21 подключен к затвору питающего МДП-транзистора,а инверсный-через третий КМДП-инвертор 22 - к затвору выходного МДП-транзистора.Прямой вход усилителя уровня соединен через узел 23 задержки с входом первого КМДП-инвертора каскгща умножения и через управляющий КМДП-инвертор 24 инверсным входом усилителя уровня, при этом точка соединения последних образует входной вывод 25 первой преобразовательной ячейки и входной вывод 26 второй преобразовательной ячейки. Тактовый вход источника Иупр соединен с одним из входов логического элемента 9 и входным выводом дополнительного узла 1 задержки, первый выход 7 которого соединен с входным выводом 25 первой преобразовательной

ячейки 10, а его второй выход 8 под ключей ко второму входу логического элемента 9,выход которого соединен со входным выводом 26 второй преобразовательной ячейки 11,

Источник питания работает следующим образом.

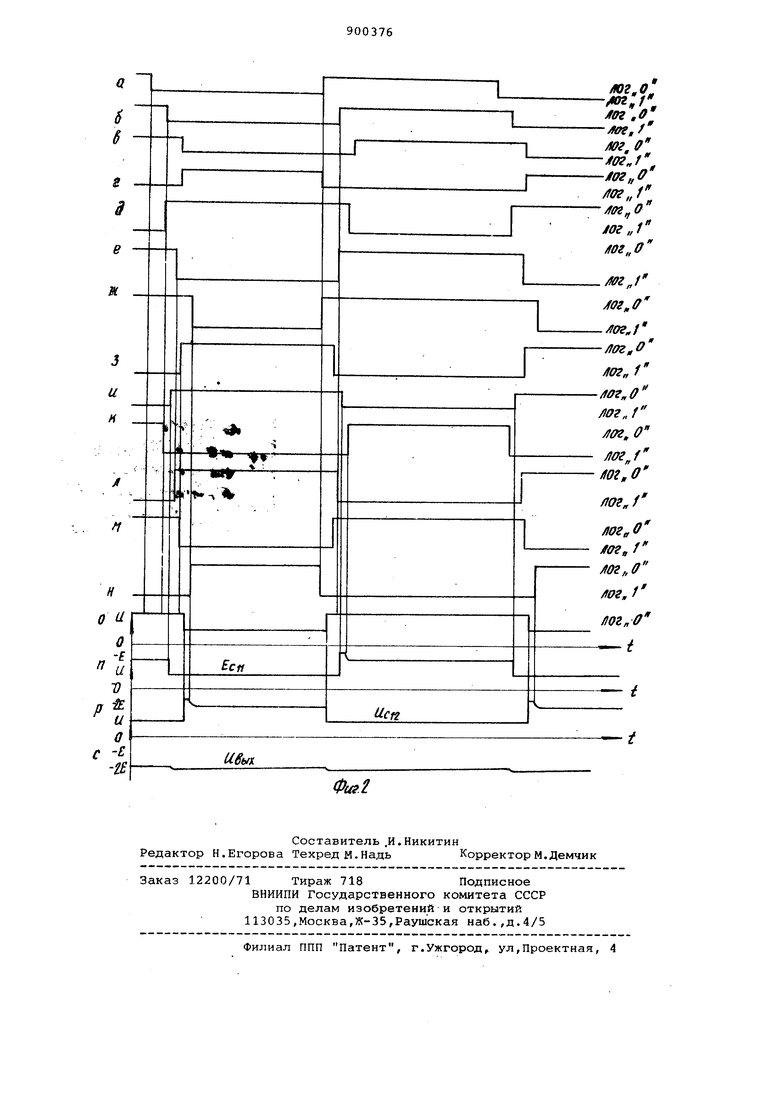

На вход узла 1 задержки и один из |входов логического элемента 9 поступает прямоугольное импульсное напряжение с импульсного устройства, напр мер, с делителя частоты электронных часов (на чертеже не показан)с частотой, например, 1024 Гц, скважностью импульсов, равной 2 (фиг.2а).

С промежуточного каскада узла 1 задержки (выход 3)на вход 25 первой преобразовательной ячейки 10 поступает импульсное напряжение (фиг.2б), задержанное во времени относительно напряжения на фиг.2а.

С выхода 8 узла задержки 1 на второй вход логического элемента 9 поступает импульсное напряжение (фиг.2в задержанное во времени относительно напряжения на фиг.26.

Логический элемент 2И-НЕ 9 обеспечивает подачу на вход 26 второй преобразовательной ячейки импульсного напряжения, скважность которого не равна 2 (фиг.2в).

В связи с тем, что фронт переключения одного из выходов в состоянии усиливаемого уровня потенциала запаздывает по отношению к соответствующему фронту переключения второго выхода-, КМДП-парафазные усилители 20 уровня имеют на своих выходах импульсные напряжения со скважностью импульсов не равной 2, а именно, на прямом выходе усилителя 20 преобразовательной ячейки 10 напряжение - в соответствии с фиг.2д, на инверсном в соответствии с фиг.2е.В это же время на прямом выходе усилителя 20 преобразовательной ячейки 11 напряжение находится в соответствии с фиг.2ж, а на инверсном - в соответствии с фиг.2з.

С выходов управляющего каскада 19 с парафазными выходами на соответствующие затворы МДП-транзисторов каскадов 12 умножения напряжения поступают импульсные напряжения с различными временными и амплитудными параметрами. На затворы МДП-транзисторов 15 и 16, КМДП-инвертора 14 с вьгхода узла 23 задержки преобразовательной ячейки 10 поступает импульсное напряжение с амплитудой, равной напряжению источника напряжения ЕП (диаграмма на фиг.2и). На затвор питающего МДП-транзистора 17 с выхода инвертора 21 преобразователной ячейки 10 поступает импульсное напряжение с амплитудой, равной выходному напряжению преобразователя

(диаграмма на фиг.2к). На затвор выходного МДП-транзистора 18 с выхода инвертора 22 преобразовательной ячейки 10 поступает импульсное напряжение с амплитудой, равной выходному, напряжению преобразователя (диагрс1мма на фиг.2л). Па затвор МДП-транзистора 18 с выхода инвертора 21 преобразовательной ячейки 11 поступает импульсное напряжение с амплитудой,равной выходному напря1жению преобразователя (диаграмма на фиг.2а). На затвор МДП-транзистора 17 с выхода инвертора 22 преобразовательной ячейки 11 поступает импульсное напряжение с амплитудой, равной выходному напряжению преобразователя (диаграмма на фиг.2н). А на затворы МЩП-транзисторов 15 и 16 с входа элемента 23 задержки преобразовательной ячейки 11 поступает импульсное напряжение с амплитудой, равной напряжению источника (диаграмма на фиг. 20 .

Процесс умножения напряжения показан на фиг.2п,р,с. На фиг. 2п показана диаграмма напряжения на конденсаторе 13 преобразовательной ячейки 10; на фиг.2р - диаграмма напряжения на конденсаторе 13 преобразовательной ячейки 11; на фиг. 2с - диаграмма напряжения на выходе источника. Для упрощения диаграммы напряжений построены с учетом подключенной к выходу нагрузки, причем показан установившийся режим работы. I

При одной и той же нагрузке за время разряда, равное периоду управля ощего сигнала с импульсного устг ройства, выходное напряжение предлагаемого источника питания имеет меньшее изменение, чем выходное напряжение известного устройства. Это обусловлено тем, что время разряда накопительного конденсатора каскада для получения высокого напряжения меньше, чем время разряда сглаживающего конденсатора известного устройства (половина периода и период управляющего сигнала ,соответственно) . Практически, изменение выходного напряжения предлагаемого преобразователя в два разе меньше, чем изменение выходного напряжения известного устройства. Таким образом, предлагаемый преобразователь напряжения с двумя каскадами для получения высокого напряжения, работающими в противофазе, имеет большую нагрузочную способность, чем известное устройство с одним каскадом для получения высокого напряжения и выходным сглаживающим конденсатором.

Наличие более высокого напряжения на выходе предлагаемого преобразователя обуславливает и его более высокий кпд, зависящий от величины мощности, отдаваемой в нагрузку, и в конечном итоге - от выходного напряжения при одинаковой нагрузке. Уменьшение изменения выходного напряжения повышает полезную моадность преобразователя, отдаваемую в нагрузку,что в свою очередь повышает КПД и нагрузочную способность преобразователя напряжения. Применение источника питания с повышенными КПД и нагрузочной способностью позволяет улучшить ряд характеристик электронных приборов с жидкокристаллическим индикатором, например, электронных часов, а имен но - повысить автономность работы, увеличить контрастность и повысить надежность индикатора, особенно при мультиплексном управлении последнег так как допустимая величина постоян ной составляющей сигналов управлени жидкокристаллическим индикатором не должна превышать 5 MB, что трудно обеспечить при питании схемы управления индикатором от известного уст ройства . Формула изобретения Источник питания, содержащий преобразовательную ячейку с тактовы входом и с каскадом умножения напря жения, состоящим из накопительного конденсатора, подключенного к выход первого КМДП-инвертора и точке соединения истока питающего и стока выходного МДП-транзисторов с типом проводимости, соответствующим поляр ности преобразуемого напряжения,при этом исток транзистора КМДП-инверто ра с типом проводимости, соответствующим полярности преобразуемого напряжения, и сток питающего МДПтранзистора подключены к входному выводу источника, исток другого транзистора КМДП-инвертора обратного типа проводимости образует общий вывод ячейки, а исток выходного МДПтцанзистора - выходной вывод ячейки, а также управляющим каскадом, состоящим из парафазного усилителя, прямой выход которого через второй КМДП-инвертор подключен к затвору питающего МДП-транзистора каскада умножения, а инверсный - через третий КМДП-инвертор - к затвору выходного МДП-транзистора, причем вход усилителя образует входной вывод ячейки, который через узел задержки связан со входом первого КМДП-инвертора, отличающийся тем, что, с целью повышения КПД и нагрузочной способности, введены вторая аналогичная преобразовательная ячейка, , дополнительный, узел задержки и логический элемент, причем тактовый вход источником соединен с одним из входов логического элемента и входом дополнительного узла задержки, первый выход которого подключен к входному выводу первой преобразовательной ячейки, а его второй выходко второму входу логического элемента, при этом выход последнего соединен со входньаи выводом второй преобразовательной ячейки,а выходы преобразовательных ячеек соединены параллельно и образуют выходные выводы источника. Источники информации, приянтые во внимание при экспертизе 1.Патент США 3975671, кл.Н 01 М 3/06, 1976. 2.Авторское свидетельство СССР № 771817, кл.Н 02 М 3/155, 29.06.79.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

| Электронные наручные часы | 1979 |

|

SU909661A1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2008 |

|

RU2349028C1 |

| Ключевой элемент | 1986 |

|

SU1406768A1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| Формирователь импульсов на МДП-транзисторах | 1988 |

|

SU1539995A1 |

| Преобразователь уровней сигналов на МДП-транзисторах | 1988 |

|

SU1538246A1 |

| Компаратор | 1989 |

|

SU1690184A1 |

| Формирователь импульсов с преобразованием уровней сигналов | 1985 |

|

SU1378030A1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

Авторы

Даты

1982-01-23—Публикация

1980-04-17—Подача