Изобретение относится к электронной технике, в частности к преобразователям напряжения для электронных наручных часов с жидкокристаллическим индикатором.

Известен преобразователь напряжения 1, представляющий собой схему умножения напряжения, управляемую генератором прямоугольных импульсов. Схема умножения напряжения включает три накопите-аьных элемента для получения дополнительных напряжений, каждый из которых состоит из двух полевых транзисторов одного типа проводимости и накопительного конденсатора, причем последний включен между истоком одного и стоком другого транзисторов. Каждый накопительный элемент подключен параллельно к источнику напряжения. Затворы полевых транзисторов накопительных элементов инверсно соединены с выходом генератора прямоугольных импульсов.

Схема умножения напряжения имеет еще четыре полевых транзистора того же типа проводимости, что и полевые транзисторы накопительных элементов, и выходной сглаживающий конденсатор. Эти четыре транзистора включены в схеме таким образом, что образуют последовательную цепь источ2

ника напряжения и трех накопительных конденсаторов, подключенную параллельно к выходному сглаживающему конденсатору и нагрузке. Затворы четырех полевых транзисторов соединены с выходом генератора g прямоугольных импульсов.

Под воздействием импульсного сигнала с генератора происходит периодическое переключение (открывание и закрывание) полевых транзисторов схе.мы умножения напряжения.

Когда открыты полевые транзисторы накопительных элементов, происходит заряд накопительных конденсаторов от источника напряжения. В следующий момент времени закрываются транзисторы накопительных элементов, и открываются другие четыре

15 транзистора, при этом происходит последовательное соединение источника и трех заряженных накопительных конденсаторов, вследствие чего и достигается усиление напряжения приблизительно в четыре раза по 20 сравнению с напряжением источника на выходном сглаживающем конденсаторе, т.е. на выходе преобразователя напряжения.

Недостатком данного преобразователя напряжения является использование полевых транзисторов одинакового типа проводимости, что эквивалентно использованию источника питания с напряжением, уменьшенным на величину порогового напряжения транзисторов, а это приводит к значительному снижению коэффициента преобразования напряжения. Указанный недостаток отсутствует в преобразователе напряжения 2, содержащем схему умножения напряжения, усилитель уровня с парафазным выходом и ручной включатель. Схема умножения напряжения представляет собой схему утроения, содержит два каскада для получения дополнительных напряжений, равных приблизительно напряжению источника питания, выходной МДП-транзистор, тип проводимости которого соответствует полярности преобразуемого напряжения, и выходной сглаживающий конденсатор. Каждый каскад для получения дополнительного напряжения содержит КМДП-инвертор, МДП-транзистор, тип проводимости которого соответствует полярности преобразуемого напряжения, и накопительный конденсатор, включенный между выходом КМДП-инвертора и истоком МДПтранзистора. Истоки МДП-транзисторов КМДП-инверторов с типом проводимости, противоположным полярности преобразуемого напряжения, соединены с общей шиной «земля. Исток МДП-транзистора с типом проводимости, соответствующим полярности преобразуемого напряжения КМДПинвертора первого каскада для получения дополнительного напряжения, и стоки МДПтранзисторов обоих каскадов соединены с источником напряжения, .другой электрод которого соединен с общей шиной «земля. Исток МДП-транзистора с типом проводи мости, соответствующим полярности преобразуемого напряжения КМДП-инвертора второго каскада для получения дополнительного напряжения, соединен с истоком МДПтранзистора первого каскада, а исток МДПтранзистора второго каскада соединен со стоком выходного МДП-транзистора, исток которого соединен с одной обкладкой выходного сглаживающего конденсатора, другая обкладка которого соединена с общей шиной «земля. Затвор выходного МДПтранзистора и входы КМДП-инверторов обоих каскадов для получения дополнительного напряжения соединены с прямым выходом усилителя уровня, а затворы МДП-транзисторов обоих каскадов- с инверсным выходом. Шина питания усилителя уровня соединена с истоком выходного МДП-транзистора, служащего выходом преобразователя напряжения. Между выходом преобразователя и источником напряжения включен ручной включатель, служащий для подачи напряжения источника питания на выход преобразователя, что необходимо для обеспечения работоспособности схемы умножения напряжения в щироком диапазоне пороговых напряжений, при пороговых напряжениях МДП-транзисторов, превышающих разность между напряжением питания и напряжением прямого смещения диффузионных областей МДП-транзисторов. При работе преобразователя напряжения на вход усилителя уровня с парафазным выходом поступает импульсное напряжение прямоугольной формы с делителя частоты электронных часов, а усиленные по амплитуде импульсы напряжения с выходов усилителя уровня, поступая на затворы МДП-транзисторов схемы умножения напряжения, управляют переключением этих транзисторов. Когда открыты МДП-транзисторы с типом проводимости, противоположным полярности преобразуемого напряжения, КМДПинверторов, и МДП-транзисторы обоих каскадов и закрыты МДП-транзисторы с типом проводимости, соответствующим полярности преобразуемого напряжения КМДПинверторов обоих каскадов, и выходной МДП-транзистор, происходит заряд обоих накопительных конденсаторов от источника напряжения. В следующлй момент времени, при переключении названных групп транзисторов, происходит последовательное соединение источника и заряженных накопительных конденсаторов обоих каскадов и параллельное подключение этой цепи к выходному сглаживающему конденсатору, который, заряжаясь, обеспечивает постоянное напряжение на выходе преобразователя, равное приблизительно устроенному напряжению источника питания. Описанный преобразователь напряжения имеет следующие недостатки: 1. Сложную конструкцию, что обусловлено наличием ручного включателя, изолированного от общей щины; в результате усложняется конструкция электронных наручных часов, корпус которых соединен с общей шиной «земля электронной схемы устройства. 2. Большой ток потребления при частоте управления свыше 0,5-1 кГц, что необходимо для повышения нагрузочной способности преобразователя или уменьшения номиналов (а следовательно, и габаритных размеров) конденсаторов. Наличие большого тока потребления обусловлено особенностью известных схем КМДП-усилителей уровня с парафазным выходом: фронт переключения одного из выходов в состояние усиливаемого уровня потенциала запаздывает по отношению к соответствующему фронту переключения второго выхода. Это приводит к тому, что при переключении МДП-транзисторов схемы умножения напряжения имеют место паразитные состояния одновременной проводимости МДП-транзисторов, следствием чего является наличие паразитных токов между выходной и питающей, выходной и общей шинами преобразователя.

Цель изобретения - упрощение конструкции преобразователя путем исключения ручного включателя, обеспечение работоспособности устройства в широком диапазоне пороговых напряжений и снижение тока потребления путем устранения состояния одновременной проводимости МДП-транзисторов схемы умножения, включенных между питающей и выходной, выходной и общей шинами преобразователя.

Эта цель достигается тем, что в преобразователь напряжения дополнительно введены два КМДП-инвертора, и линия задержки. Линия задержки состоит из четного числа КМДП-инверторов, соединенных последовательно. Прямой выход усилителя уровня через один КМДП-инвертор соединен с затвором выходного МДП-транзистора, а инверсный - через второй КМДП-инвертор соединен с затвором МДП-транзистора каскада для получения дополнительного напряжения. Вход линии задержки инверсно соединен с входом усилителя уровня, а ее выход - с входом КМДП-инвертора каскада для получения дополнительного напряжеки.ч. Питание линии задержки осуществляется постоянным напряжением источника питания, а питание двух КМДП-инверторов - постоянным выходным напряжением преобразователя.

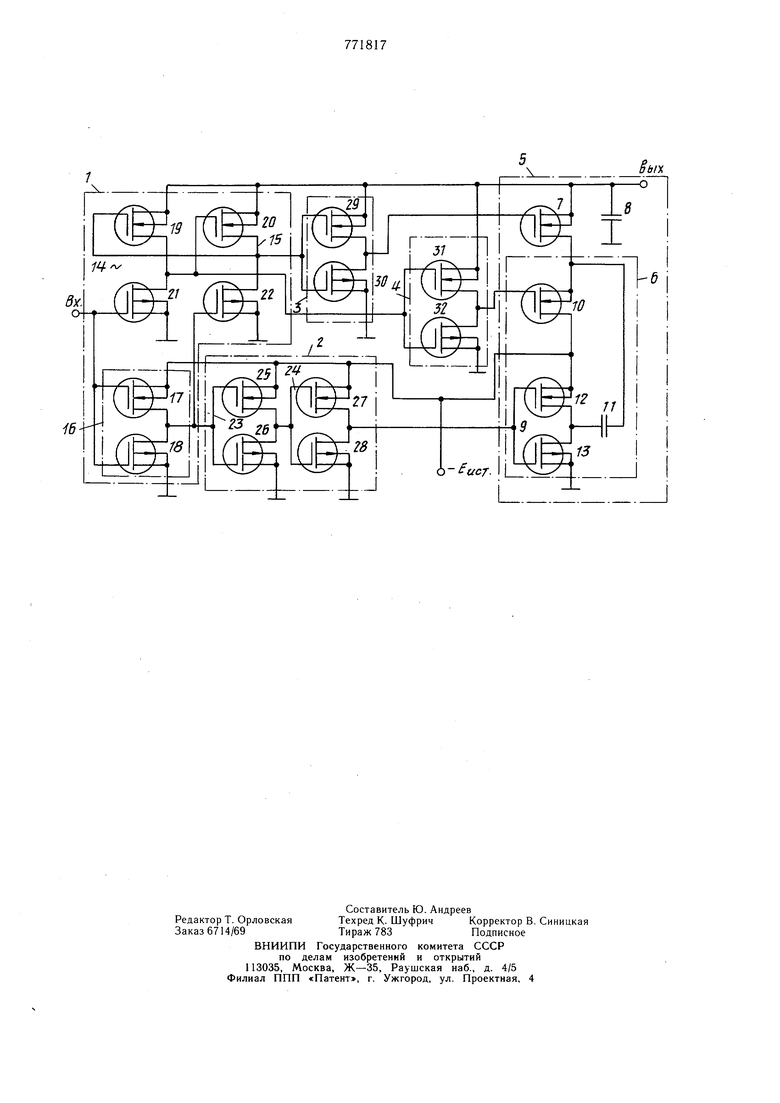

Схема предложенного преобразователя приведена на чертеже.

Преобразователь напряжения для электронных наручных часов состоит из усилителя уровня 1 с парафазным выходом, линия задержки 2, двух КМДП-инверторов 3, 4 и схемы 5 умножения напряжения.

Схема 5 умножения напряжения служит для преобразования (усиления) напряжения источника, которое необходимо для питания нагрузки, например жидкокристаллического индикатора электронных наручных часов.

Усилитель уровня 1 служит для усиления импульсов напряжения, необходимых для управления переключением МДП-транзисторов схемы умножения напряжения.

Линия задержки 2 и инверторы 3, 4 служат для формирования необходимых фронтов управляющих импульсов схемы умножения напряжения, исключающих паразитные состояния одновременной проводимости МДП-транзисторов, включенных между питающей и выходной, выходной и общей шинами схемы 5 умножения.

Вход линии задержки 2 инверсно соединен с входом усилителя уровня 1, прямой выход которого соединен с входом КМДПинвертора 3. Инверсный выход усилителя уровня 1 соединен со входом КМДП-инвертора 4.

Схема 5 умножения включает каскад 6 для получения дополнительного напряжения, выходной п-канальный МДП-транзистор 7 и выходной сглаживающий конденсатор 8. Каскад 6 состоит из КМДП-инвертора 9, N-канального МДП-транзистора 10 и накопительного конденсатора 11. Одна обкладка конденсатора 11 соединена с выходом КМДП-инвертора 9, а другая - с истоком МДП-транзистора 10 и стоком выходного МДП-транзистора 7. КМДП-инвертор 9 состоит из N-канального МДП-транзижтора 12 и р-канального МДП-транзистора 13, стоки которых соединены между собой и служат выходом инвертора 9, сток МДП-транзистора 10 и исток МДП-транзистора 12 соединены с общей шиной «земля.

Затвор выходного МДП-транзистора 7 соединен с выходом КМДП-инвертора 3, затвор МДП-транзистора 10 - с выходом КМДП-инвертора 4. Вход КМДП-инвертора 9, т.е. затворы МДП-транзисторов12, 13, соединен с выходом линии задержки 2.

Усилитель уровня 1 состоит из двух комплементарных пар 14, 15 и управляющего КМДП-инвертора 16, включающего N-канальный 17 и р-канальный 18 МДП-транзисторы. Комплементарные пары 14 и 15 состоят соответственно из N-канальных 19, 20 и р-канальных 21, 22 МДП-транзисторов. Стоки МДП-транзисторов 19, 21, служащие инверсным выходом усилителя уровня 1, соединены с затвором МДП-транзистора 20, а стоки МДП-транзисторов 20, 22, служащие прямым выходом усилителя 1, соединены с затвором МДП-транзистора 19. Затворы МДП-транзисторов 17, 18, служащие входом КМДП-инвертора 16, соединены с затвором МДП-транзистора 21, являющимся входом усилителя уровня 1, а стоки транзисторов 17, 18 (выход инвертора 16) соединены с затвором МДП-транзистора 22. Истоки МДП-транзисторов 18, 21, 22 соединены с общей шиной «земля. Шина питания усилителя уровня 1(истоки транзисторов 19, 20) соединена с выходом преобразователя, т.е. истоком выходного МДП-транзистора 7 схемы 5, а исток МДП-транзистора 17 с отрицательным электродом источника напряжения.

Линия задержки 2 состоит из двух КМДП-инверторов 23,24. Инвертор 23 включает N-канальный 25 и р-канальный 26 МДПтранзисторы, стоки которых соединены между собой и служит выходом инвертора 23, соединенные затворы - входом. Инвертор 24включает N-канальный 27 и р-канальный 28 МДП-транзисторы, затворы которых соединены между собой и служат входом инвертора 24, а соединенные стоки - его выходом, соединённые со входом инвертора 9, т.е. с затворами МДП-транзнсторов 12, 13. Выход инвертора 23 соединен со входом инвертора 24. Инверсное соединение входа линии задержки 2 - входа инвертора 23 осуществляется соединением входа линии задержки 2 с выходом управляющего КМДПинвертора 16, вход которого соединен со входом усилителя уровня 1. Истоки транзисторов 25, 27 соединены с отрицательным

электродом источника питания, и истоки транзисторов 26, 28 - с общей шиной «земля.

КМДП-инвертор 3 состоит из N-канального 29 и р-канального 30 МДП-транзисторов, затворы которых соединены с прямым выходом усилителя уровня 1, а стоки - с затвором выходного МДП-транзистора 7 схемы умножения 5.

КМДП-инвертор 4 состоит из N-канального 31 и р-канального 32 МДП-транзисторов, затворы которых соединены с инверсным выходом усилителя 1, а стоки - с затвором МДП-транзистора 10 схемы 5.

Истоки МДП-транзисторов 29, 31 соединены с выходом преобразователя напряжения, а истоки МДП-транзисторов 30, 32 - с общей шиной «земля.

На вход усилителя уровня 1 поступает прямоугольное импульсное напряжение с делителя частоты электронных наручных часов (не показан), например, с частотой 1024 Гц, скважностью 2. Усиленные по амплитуде импульсы с выходов усилителя 1 поступают на входы КМДП-инверторов 3, 4. Параметры МДП-транзисторов 29-32 выбраны такими, что импульсные сигналы с выходов инверторов 3, 4 имеют скважность импульсов, не равную 2.

Одновременно сигнал со входа усилителя уровня 1 через управляющий инвертор 16 поступает на выход линии задержки 2. Импульсные сигналы, поступающие с выходов линии задержки 2, КМДП-инверторов 3, 4 на затворы соответственно МДП-транзисторов 7, 10, 12 и 13 схемы 5, ис}-слючэ;от паразитные состояния одновременной проводимости транзисторов 7 и 10, 12 и 13, тем самым обеспечивая отсутствие паразк Hjwx токов между питающей и выходной, выходной и общей шинами преобразователя напряжения, что снижаетобщий ток потребления последнего.

При поступлении на вход усилителя уровня 1 уровня логического «О поочередно происходит закрывание выходного МДПтранзистора 7, открыбание МДП-транзистора 13 и закрывание МДП-транзистора 12, открывание МДП-транзистора 9. При таком состоянии транзисторов 7, 10, 12, 13 происходит заряд накопительного конденсатора 11 до напряжения, приблизительно равного напряжению источника питания.

В следующий момент времени, при поступлении на вход усилителя уровня 1 логической «1 (соответствует «-Ё) поочередно происходит закрывание МДП-транзистора 10, открывание МДП-транзистора 12 и закрывание МДП-транзистора 13, открывание МДП-транзистора 7. При этом обеспечивается последовательное соединение источника питания и заряженного конденсатора 11 и параллельное подключение данной цепи к выходному сглаживающему конденсатору 8 и нагрузке (не показана). Зарядившись приблизительно до удвоенного напряжения источника, конденсатор 8 обеспечивает питание нагрузки в следующий такт работы, когда процесс повторяется.

Формула изобретения

Преобразователь напряжения преимущественно для электронных наручных часов, содержащий, усилитель уровня с парафазным выходом и схему умножения напряжения, имеющую каскад для получения дополнительного напряжения, выходной МДП-транзистор, тип проводимости которого соответствует полярности преобразуемого напряжения, и выходной сглаживающий конденсатор, причем каскад включает КМДП-инвертор, МДП-транзистор, тип проводимости которого соответствует полярности преобразуемого напряжения, и накопительный конденсатор, включенный между выходом КМДП-инвертора и истоком МДПтранзистора, который соединен со стоком выходного МДП-транзистора, а сток МДПтранзистора и исток МДП-транзистооа с типом проводимости, соответствующие полярности преобразуемого напряжения КМДП инвертора соединены с источником напряжения, другой электрод которого соединен с общей щиной «земля исток выходного МДП транзистора соединен с выходным сглаживающим конденсатором, другая обкладка которого и исток МДП-транзистора с типом проводимости, противоположным полярности преобразуемого напряжения, КМДП-инвертора, соединены с общей щиной «земля, а шина питания усилителя уровня соединена с истоком выходного МДП-транзистора, служащего выходом преобразователя, отличающийся тем, что, с целью упрощения конструкции и снижения тока потребления, преобразователь напряжения дополнительно снабжен двумя КМДП-инверторами и лкнней задержки, образованной из четного числа КМДП-инверторов, включенных последовательно, причем прямой выход усилит.еля уровня через один дополнительный КМДПинвертор соединен с затвором выходного МДП-транзистора, инверсный выход усилителя уровня через другой дополнительный КМДП-инвертор соединен с затвором МДПтранзистора каскада для получения дополнительного напряжения, вход линии задержки инверсно соединен со входом усилителя уровня, а ее выход - со входом КМДП-инвертора каскада для получения дополнительного напряжения, шина питания линии задержки подсоединена к источнику напряжения, а шина питания дополнительных КМДП-инверторов - к выходу преобразователя.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3824477, кл. Н 02 N 7/00, 1974.

2.Патент США № 3975671. кл. Н 02 М 3/06, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Источник питания | 1980 |

|

SU900376A1 |

| Электронные наручные часы | 1979 |

|

SU909661A1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| Формирователь импульсов | 1980 |

|

SU911692A1 |

| Формирователь парафазных импульсов | 1981 |

|

SU984013A1 |

| Ключевой элемент | 1986 |

|

SU1406768A1 |

| Компаратор | 1989 |

|

SU1690184A1 |

| Устройство автоматического смещения | 1981 |

|

SU995673A1 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

Авторы

Даты

1980-10-15—Публикация

1978-11-21—Подача