( МАТРИЧНЫЙ КОММУТАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1981 |

|

SU1014147A1 |

| Кольцевой счетчик | 1983 |

|

SU1095417A1 |

| Стабилизатор напряжения | 1987 |

|

SU1509852A1 |

| СИСТЕМА ЗАЖИГАНИЯ С НАКОПЛЕНИЕМ ЭНЕРГИИ НА КОНДЕНСАТОРЕ | 1992 |

|

RU2020259C1 |

| Электронный коммутатор | 1977 |

|

SU692087A1 |

| Ячейка памяти | 1974 |

|

SU1327185A1 |

| Многостабильный триггер | 1986 |

|

SU1309263A1 |

| Устройство для защиты переключающего транзистора | 1983 |

|

SU1124412A1 |

| УСТРОЙСТВО СИГНАЛИЗАЦИИ О СОСТОЯНИИ ПИРОПАТРОНА | 1995 |

|

RU2093895C1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1972 |

|

SU434481A1 |

Изобретение относится к импульсной технике и может быть использовано для создания коммутаторов с матричной организацией цепей управления.

Известны матричные коммутаторы с постоянной памятью в каждой ячейке, содержащие в каждой ячейке тиристор, последовательно с которым включена нагрузка, первые и вторые координатные шины, шину питания, общую шину и источник смещения 1.

Недостаток указанных матричных коммутаторов заключается в том, что для выбора требуемых ячеек в нем используется зависимость переключательных характеристик тиристоров от величины анодного напряжения, которая является слабо выраженной, что делает вероятность неправильной выборки ячеек весьма значительной.

Известен матричный коммутатор, содержащий в каждой ячейке тиристор, имеющий первый и второй катоды, и

резистор, включенный последовательно с тиристором, и диод, первый .вывод которого соединен с управляющим электродом тиристора, а таюхе первые, вторые и третьи координатные шины, шину питания и общую шину, первые, вторые и третьи ключевые элементы, входы которых являются первыми, вторыми и третьими координатными входами коммутатора, и резисторы, причем первые координатные шины соединены с вторыми выводами диодов, вторые координатные шины соединены с вторыми катодами тиристоров, а третьи координатные шины через третьи ключевые элементы соединены с шиной питания, кроме того, указанное устройство содержит источник смещения, полярность которого противоположна полярности основного источника питания 2.

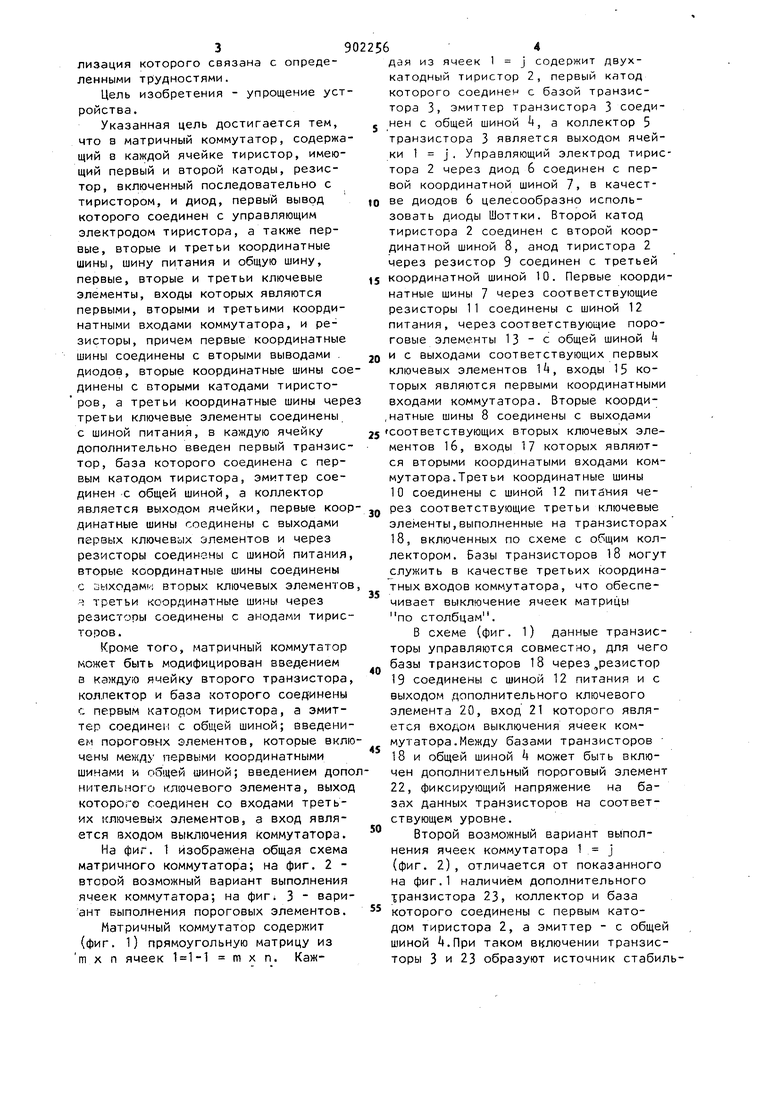

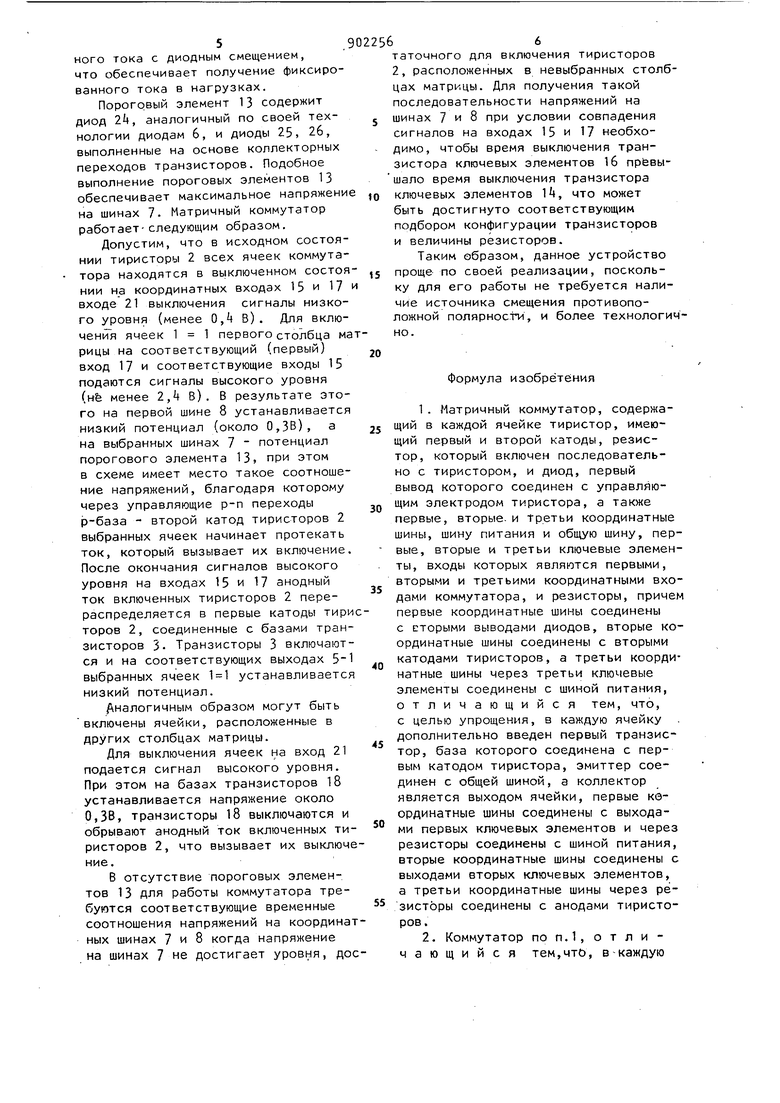

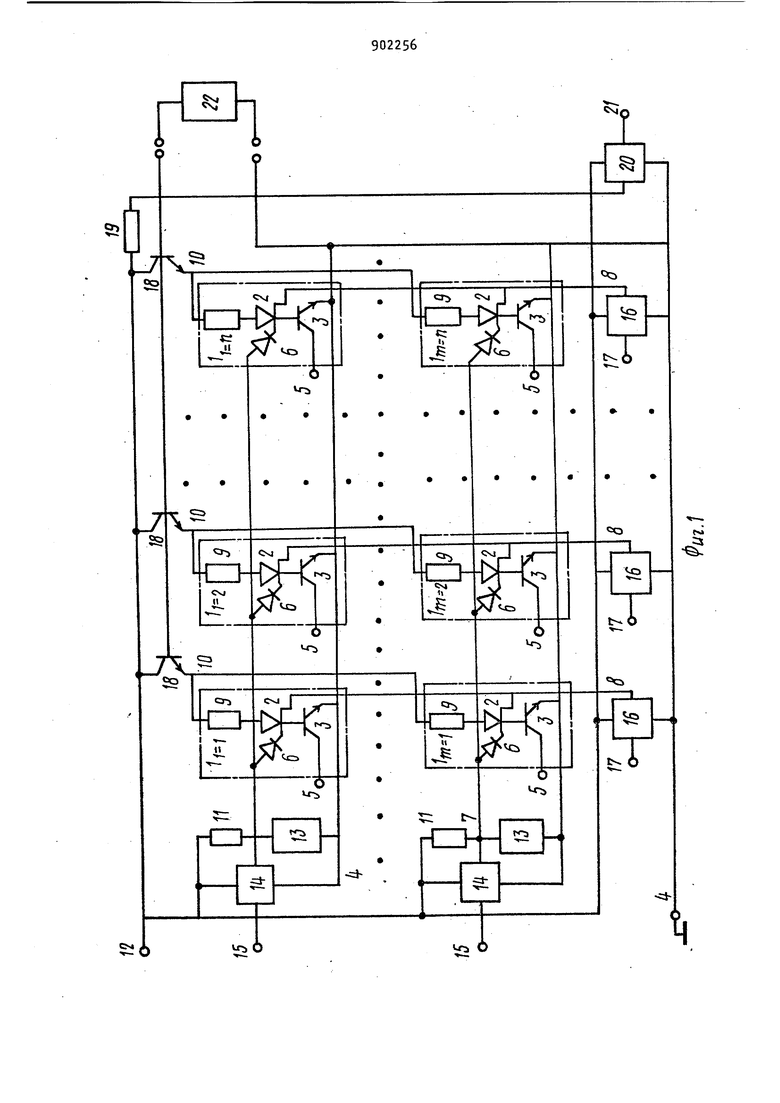

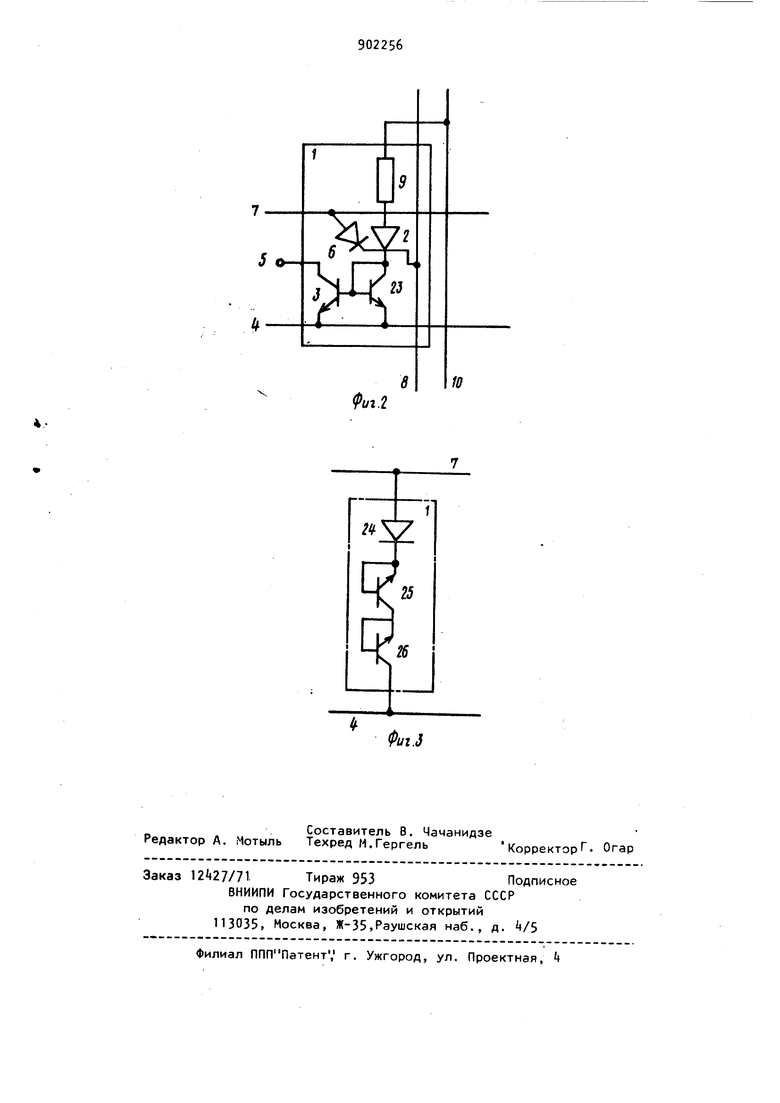

Недостаток данного коммутатора состоит в наличии источника смещения противоположной полярности, peaлизация которого связана с определенными трудностями. Цель изобретения - упрощение уст ройства. Указанная цель достигается тем, что в матричный коммутатор, содержа щий в каждой ячейке тиристор, имеющий первый и второй катоды, резистор, включенный последовательно с тиристором, и диод, первый вывод которого соединен с управляющим электродом тиристора, а также первые, вторые и третьи координатные шины, шину питания и общую шину, первые, вторые и третьи ключевые элементы, входы которых являются первыми, вторыми и третьими координатными входами коммутатора, и резисторы, причем первые координатные шины соединены с вторыми выводами . диодов, вторые координатные шины со динены с вторыми катодами тиристоров, а третьи координатные шины чер третьи ключевые элементы соединены с шиной питания, в каждую ячейку дополнительно введен первый транзис тор, база которого соединена с первым катодом тиристора, эмиттер соединен с общей шиной, а коллектор является выходом ячейки, первые коо динатные шины соединены с выходами первых ключевых элементов и через резисторы соединены с шиной питания вторые координатные шины соединены с ыходамм вторых ключевых элементо --; третьи координатные шины через резисторы соединены с анодами тирис торов. Кроме того, матричный коммутатор может быть модифицирован введением в каждую ячейку второго транзистора коллектор и база которого соединены с первым катодом тиристора, а эмиттер соединен с общей шиной; введени ем пороговых элементов, которые вкл чены между первыми координатными шинами и общей шиной; введением доп нительного ключевого элемента, выхо которого соединен со входами третьих 1слгачевь х элементов, а вход является входом выключения коммутатора. На фиг. 1 изображена общая схема матричного коммутатора; на фиг. 2 второй возможный вариант выполнения ячеек коммутатора; на фиг; 3 вари ант выполнения пороговых элементов. Матричный коммутатор содержит (фиг. 1) прямоугольную матрицу из т X п ячеек m х п. Каждая из ячеек i j содержит двухкатодный тиристор 2, первый катод которого соединен с базой транзистора 3, эмиттер транзистора 3 соединен с общей шиной k, а коллектор 5 транзистора 3 является выходом ячейки 1 j. Управляющий электрод тиристора 2 через диод 6 соединен с первой координатной шиной 7, в качестве диодов 6 целесообразно использовать диоды Шоттки. Второй катод тиристора 2 соединен с второй координатной шиной 8, анод тиристора 2 через резистор 9 соединен с третьей координатной шиной 10. Первые координатные шины 7 через соответствующие резисторы 11 соединены с шиной 12 питания, через соответствующие пороговые элементы 13 с общей шиной 4 и с выходами соответствующих первых ключевых элементов 1, входы 15 которых являются первыми координатными входами коммутатора. Вторые координатные шины 8 соединены с выходами соответствующих вторых ключевых элементов 16, входы 17 которых являются вторыми координатыми входами коммутатора. Третьи координатные шины 10 соединены с шиной 12 питймия через соответствующие третьи ключевые элементы,выполненные на транзисторах 18, включенных по схеме с общим коллектором. Базы транзисторов 18 могут служить в качестве третьих координатных входов коммутатора, что обеспечивает выключение ячеек матрицы по столбцам. В схеме (фиг. 1) данные транзисторы управляются совместно, для чего базы транзисторов 18 через,резистор 19 соединены с шиной 12 питания и с выходом дополнительного ключевого элемента 20, вход 21 которого является входом выключения ячеек коммутатора. Между базами транзисторов 18 и общей шиной k может быть включен дополнительный пороговый элемент 22, фиксирующий напряжение на базах данных транзисторов на соответствующем уровне. Второй возможный вариант выполнения ячеек коммутатора 1 j (фиг. 2), отличается от показанного на фиг.1 наличием дополнительного транзистора 23, коллектор и база которого соединены с первым катодом тиристора 2, а эмиттер - с общей шиной 4.При таком включении транзисторы 3 и 23 образуют источник стабильного тока с диодным смещением, что обеспечивает получение фиксированного тока в нагрузках.

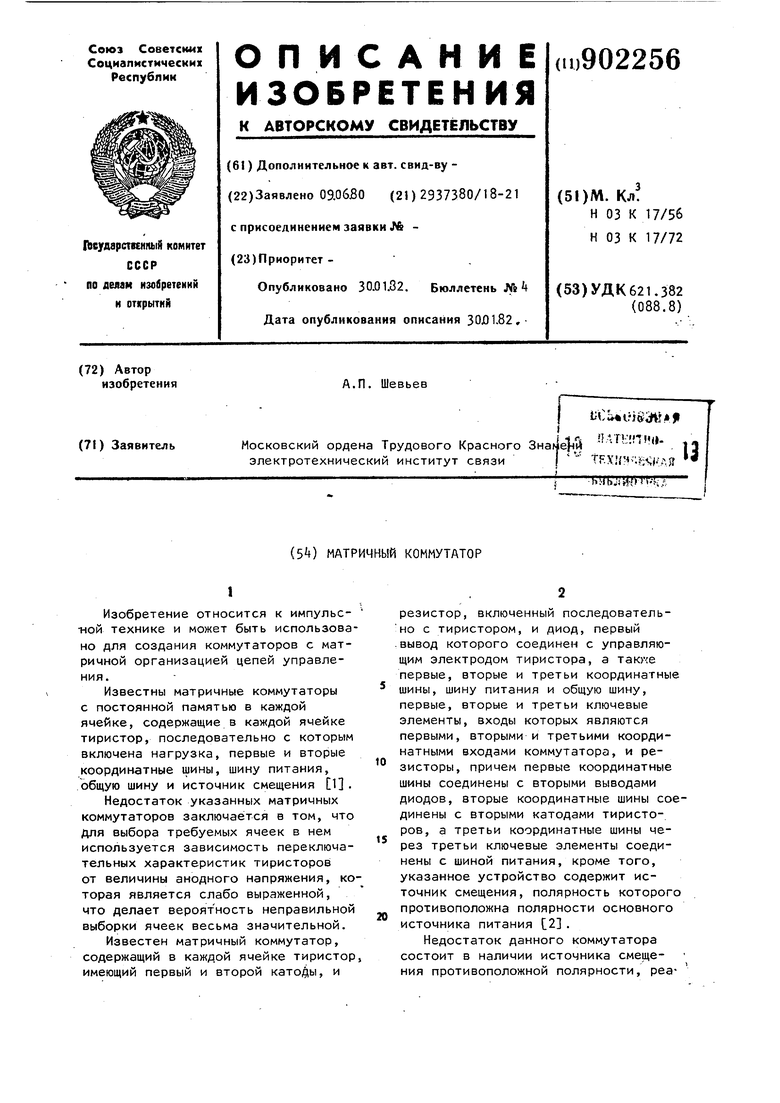

Пороговый элемент 13 содержит диод 2k, аналогичный по своей технологии диодам 6, и диоды 25, 26, выполненные на основе коллекторных переходов транзисторов. Подобное выполнение пороговых элементов 13 обеспечивает максимальное напряжени на шинах 7. Матричный коммутатор работает-следующим образом.

Допустим, что в исходном состоянии тиристоры 2 всех ячеек коммутатора находятся в выключенном состоянии на координатных входах 15 и 17 входе 21 выключения сигналы низкого уровня (менее О, В) . Для включения ячеек 1 1 первого столбца марицы на соответствующий (первый) вход 17 и соответствующие входы 15 подаются сигналы высокого уровня (не менее 2,4 В) . В результате этого на первой шине 8 устанавливается низкий потенциал (около 0,ЗВ), а на выбранных шинах 7 - потенциал порогового элемента 13, при этом в схеме имеет место такое соотношение напряжений, благодаря которому через управляющие р-п переходы р-база - второй катод тиристоров 2 выбранных ячеек начинает протекать ток, который вызывает их включение. После окончания сигналов высокого уровня на входах 15 и 17 анодный ток включенных тиристоров 2 перераспределяется в первые катоды тириторов 2, соединенные с базами транзисторов 3- Транзисторы 3 включаются и на соответствующих выходах 5-1 выбранных ячеек устанавливается низкий потенциал.

/ налогичным образом могут быть включены ячейки, расположенные в других столбцах матрицы.

Для выключения ячеек на вход 21 подается сигнал высокого уровня. При этом на базах транзисторов 18 устанавливается напряжение около 0,3В, транзисторы 18 выключаются и обрывают анодный ток включенных тиристоров 2, что вызывает их выключение.

В отсутствие пороговых элементов 13 для работы коммутатора требуются соответствующие временные соотношения напряжений на координатных шинах 7 и 8 когда напряжение на шинах 7 не достигает уровня, достаточного для включения тиристоров 2, расположенных в невыбранных столбцах матрицы. Для получения такой последовательности напряжений на шинах 7 и 8 при условии совпадения сигналов на входах 15 и 17 необходимо, чтобы время выключения транзистора ключевых элементов 16 превышало время выключения транзистора ключевых элементов 1А, что может быть достигнуто соответствующим подбором конфигурации транзисторов и величины резисторов.

Таким образом, данное устройство проще по своей реализации, поскольку для его работы не требуется наличие источника смещения противоположной nonRpHoctM, и более технологично.

Формула изобретения

ячейку дополнительно введен второй транзистор, коллектор и база которого соединены с первым катодом тиристора, а эмиттер соединен с общей шиной .

k. Коммутатор по п.1, о т л и чающийся тем, что дополнительно введен ключевой элемент, выход которого соединен со входами третьих ключевых элементов, а вход является входом выключения коммутатора.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-01-30—Публикация

1980-06-09—Подача