1

Изобретение относится к интегральной схемотехнике и может быть применено для построения запоминающего устройства ЭВМ.

Известны матричные накопители, выполненные на двухкатодных тиристорах со словарноразрядной организацией, в которых тиристоры объединены одним из катодов шинами словарного считывания, а другим - шинами разрядного считывания. Рассасывание накопленных носителей из баз транзисторов разрядного считывания осуществляется благодаря использованию резистора, шунтирующего переход база-эмиттер транзистора.

Запись информации в ячейку памяти известного накопителя осуществляется через транзистор записи, база которого через согласующий резистор подсоединена к словарной шине записи, а эмиттер подключен к разрядной щине.

Однако наличие резистора рассасывания, шунтирующего переход база-эмиттер транзистора считывания, определяет большую мощность хранения. Кроме того, построение многоразрядных ЗУ невозможно без ухудшения параметров быстродействия по записи при согласовании с логическими уровнями стандартных ИС.

Цель изобретения - уменьшить мощность хранения и улучшить эксплуатационные характеристики накопителя.

Для этого в предлагаемом матричном накопителе к словарным щинам считывания подсоединены базы развязывающих эмиттерных повторителей импульсного смещения, к соединенным эмиттерам которых подключен анод диода, к катоду которого подключены резистор, соединенный с отрицательной шиной питания, и катоды п диодов рассасывания, аноды которых соединены с базами разрядных

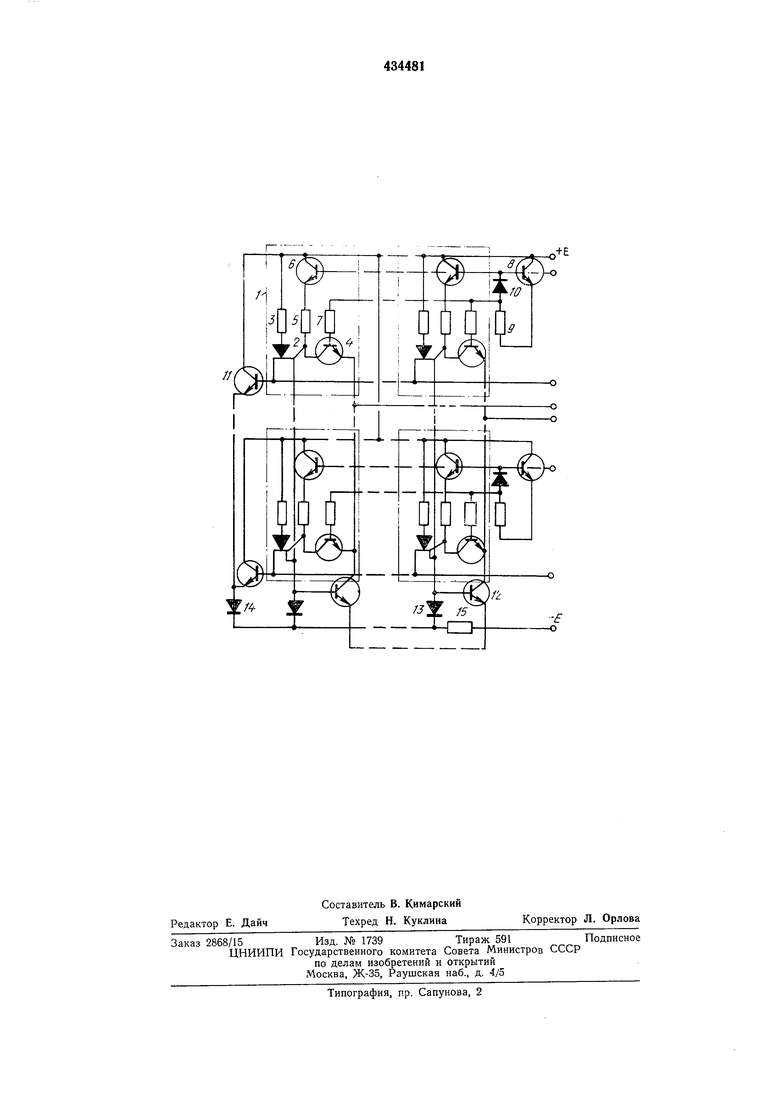

транзисторов считывания; база первого транзистора записи ячеек через согласующий резистор подключена к аноду общего для строки диода рассасывания и через резистор нагрузки - к эмиттеру общего для строки транзистора записи «О, база которого соединена с катодом диода рассасывания и подключена к словарной шине записи, а коллектор которого соединен с коллекторами вторых транзисторов записи ячеек и с коллекторами эмиттерных повторителей импульсного смещения, подключенными к положительной шине питания. На чертеже приведена схема матричного накопителя.

Накопитель состоит из /г ячеек памяти и

элементов, общих для строки, столбца и накопителя. Собственно ячейка 1 памяти содержит двухкатодный тиристор 2, анодный резистор 3, первый транзистор 4 записи, согласующий резистор 5, второй транзистор 6 записи

и согласующий резистор 7.

Общими для строки являются транзистор записи «О 8, согласующий резистор 9, диод 10 рассасывания, эмиттерный повторитель 11 импульспого смещения.

Общими для столбца являются транзистор 12 разрядного считывания и диод 13 рассасывания.

Общими для накопителя являются диод 14 и резистор 15.

Матричный накопитель работает следующим образом.

В режиме хранения записанной информации на словарных щинах записи и считывания поддерживают напряжение уровня логического «О, на разрядных щинах-логической «1.

При записи на выбранную шину словарной записи подают напряжение уровня логической «1, чем обеспечивают возможность отпирания тиристора 2 (запись «1) током через согласующий резистор 5 при условии, что переход база-эмиттер транзистора 4 закрыт напряжением уровня логической «1 со стороны разрядной шины.

При наличии на разрядной шине напряжения уровня логического «О транзистор 4 насыщается и шунтирует переход Р - база- катод тиристора 2, закрывая последний, что соответствует записи «О в ячейку памяти 1.

Диод 10 обеспечивает быстрое восстановление закрытого состояния транзистора 4 при окончании импульса словарной записи за счет смещения, действующего со стороны разрядной шины.

При считывании на выбранную шину словарного считывания подают напряжение уровня логической «1, при этом на резисторе 15 через эмиттерный повторитель 11 и диод 14, формируется положительный импульс, обеспечивающий отсечку тока хранения через диоды 13 в момент считывания.

В открытых тиристорах 2 строки ток, определяемый резистором 3, с катодов, объединенных словарной шиной считывания, перебрасывается в катоды, подключенные к базам транзисторов 12, формируя на разрядных шинах, соответствующих ячейкам 1 с записаппой «1, папряжепие уровня логического «О.

После окончания импульса считывания ток в открытых тиристорах 2 перебрасывается на

катоды, объединенные шиной словарного считывания.

Транзисторы 12, соответствующие ячейкам 1 с записанной «1, закрываются, так как при отсутствии считывания цепь рассасывания через диоды 13 и низкоомный резистор 15 открыта.

Предмет изобретения

Матричный накопитель, содержащий в каждой ячейке двухкатодный тиристор, причем один из катодов тиристора подключен к слоВарной шине считывания, другой - к базе разрядного транзистора считывания, коллектор которого соединен с разрядной шиной и с эмиттерами первых транзисторов записи ячеек столбца, причем в каждой ячейке памяти коллектор первого транзистора записи соединен со вторым катодом тиристора и через резистор - с эмиттером второго транзистора записи, база которого соединена со словарной шиной записи, анод тиристора через

резистор подключен к шине первого источника напряжения, отличающийся тем, что, с целью уменьшения потребляемой мощности и улучшения эксплуатационных характеристик, в нем к словарным шинам считывания

подсоединены базы развязывающих эмиттерных повторителей импульсного смещения, к эмиттерам которых подключены аноды диодов, к катодам которых подключены катоды п диодов рассасывания, аноды которых подключены к базе разрядного транзистора считывания, катоды диодов рассасывания подключены через резистор к шине второго источника напряжения; база цервого транзистора записи через согласующий резистор подключены к аноду общего для строки диода рассасывания и через резистор нагрузки - к эмиттеру эмиттерного повторителя записи «О - общего для строки, катод диода рассасывания подключен к словарной щине записи

«1 и к базе транзистора эмиттерного повторителя записи «О, коллектор которого соединен с первой шиной источника напряжения, которая подключена также к коллекторам вторых транзисторов записи ячеек.

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1111204A1 |

| Формирователь уровня считывания | 1984 |

|

SU1244718A1 |

| Параметрический источник опорного напряжения для запоминающего устройства | 1989 |

|

SU1647647A1 |

| Оперативное запоминающее устройство | 1979 |

|

SU903972A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

Даты

1974-06-30—Публикация

1972-06-30—Подача