11327185

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах.

Целью изобретения является увеличение быстродействия.

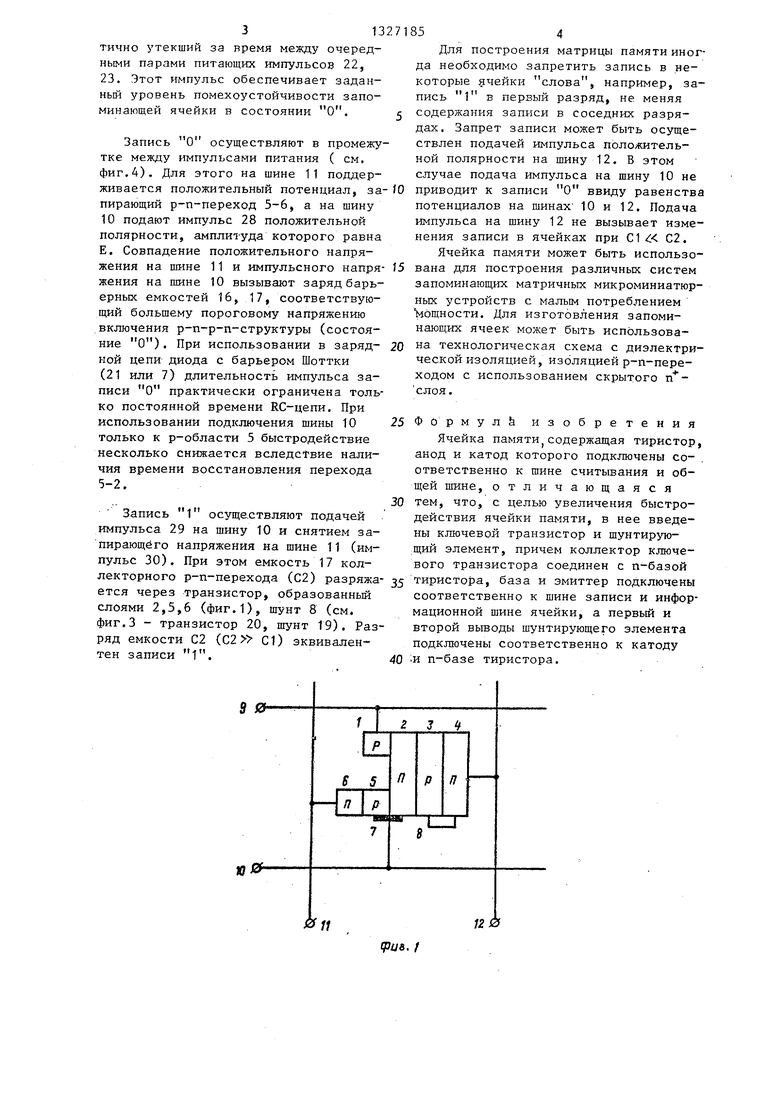

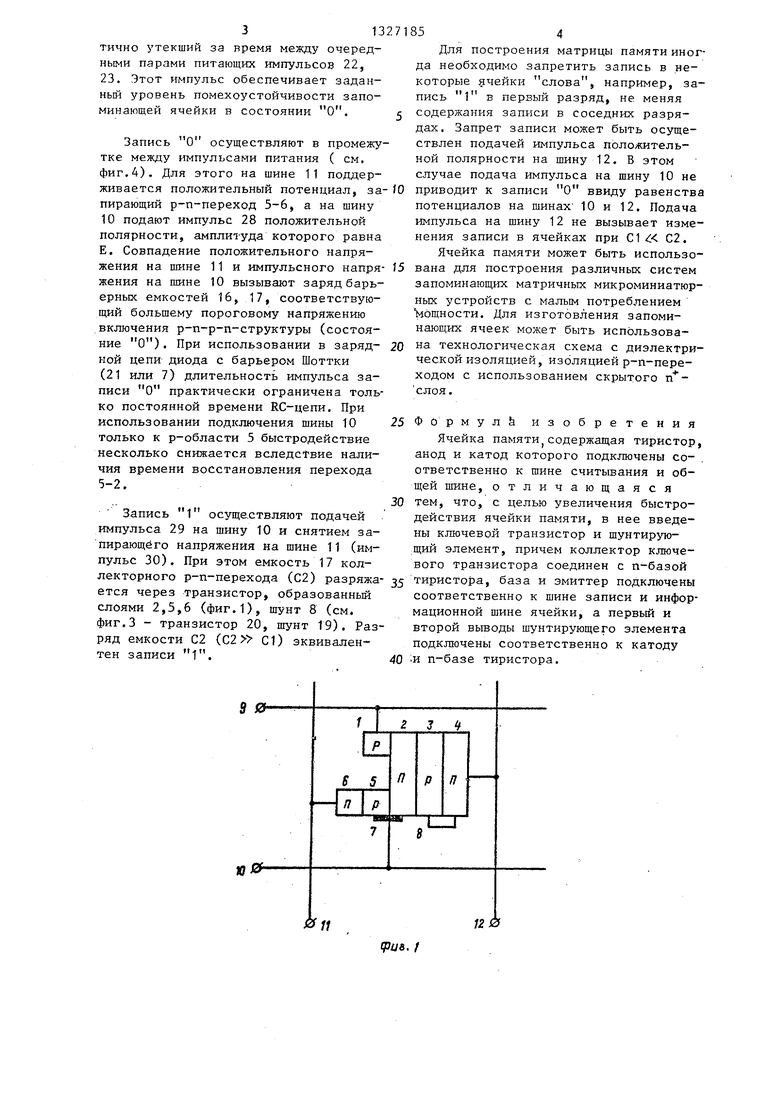

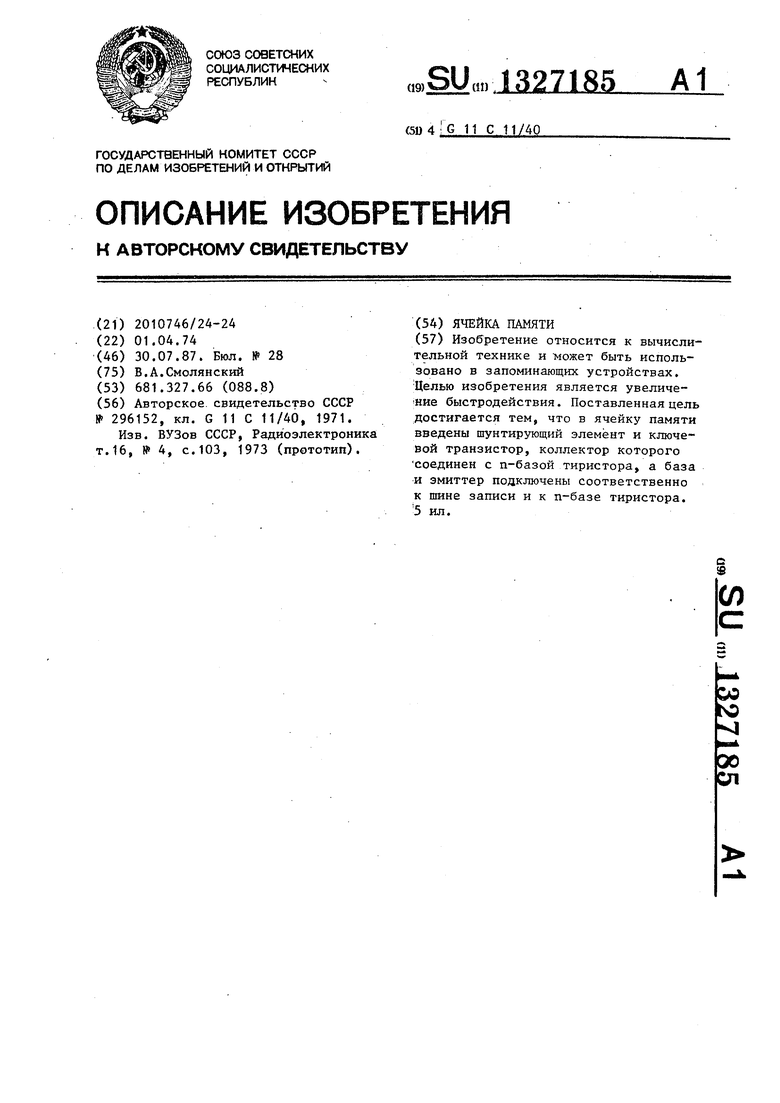

На фиг.1 показана принципиальная

g

за

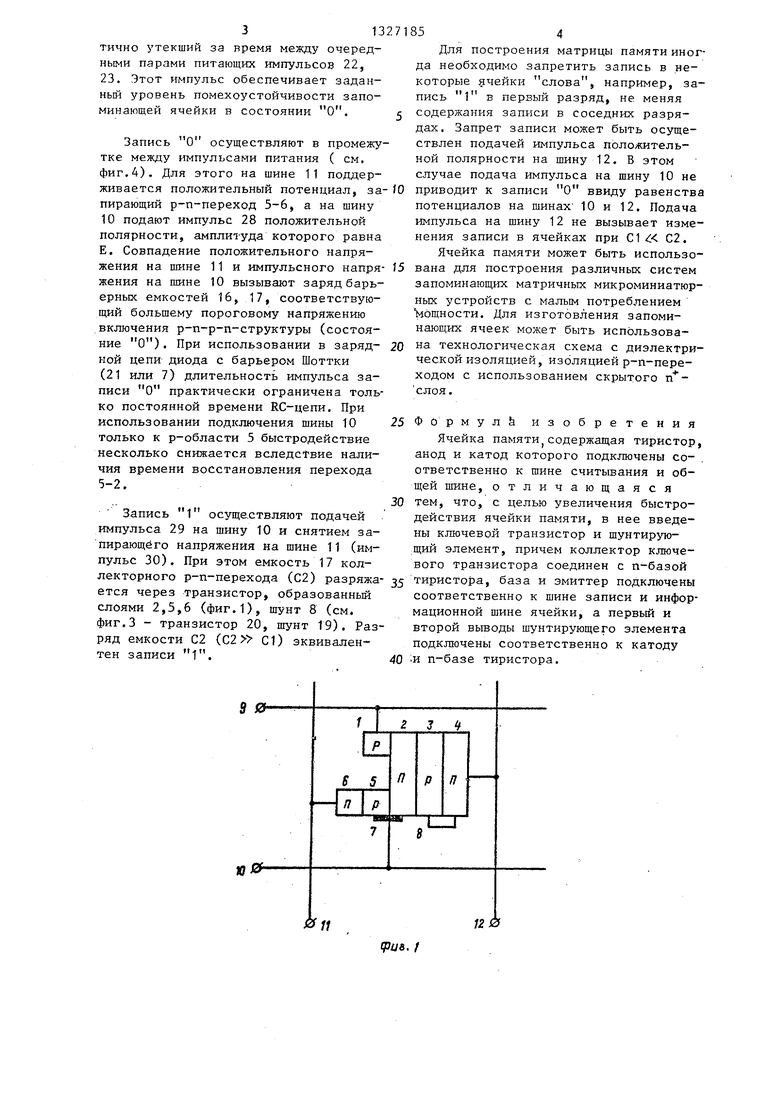

схема ячейки, на фиг. 2 - конструкция областей ячейки на фиг.З - эквивалентная схема ячейкиJ на фиг.4 - диаграммы управляющих и питающих импулсов; на фиг.З - зависимость импульсного напряжения включения ячейки (по аноду) от амплитуды импульса питания подаваемого на дополнительную р-об- ласть.

Ячейка памяти содержит р-область

1р-п-р-п-структуры (анод), п-базу

2р-п-р-п-структуры, 3р-п-р-п- структуры, п -эмиттер 4 (катод) р-п-р-п-структуры, базу 5 ключевого. транзистораj эмиттер 6 ключевого транзистора, диод 7 с барьером Шоттки, шунтирующий элемент 8, шины 9 и 10 считывания и записи, информациошгую

и общую щины 11 и 12, скрытьш п -сло 13, р-п-р- ип-р-п-транзисторы 14 и 15, емкости 16 и 17 (С1 и С2), емкость 18 . (СЗ) р-п-р-п-структуры, шунт 19 (14- 19 - элементы эквивалентной схемы р-п-р-п-структуры), п-р-п-транзистор 20, диод 21 с барьером Шоттки.

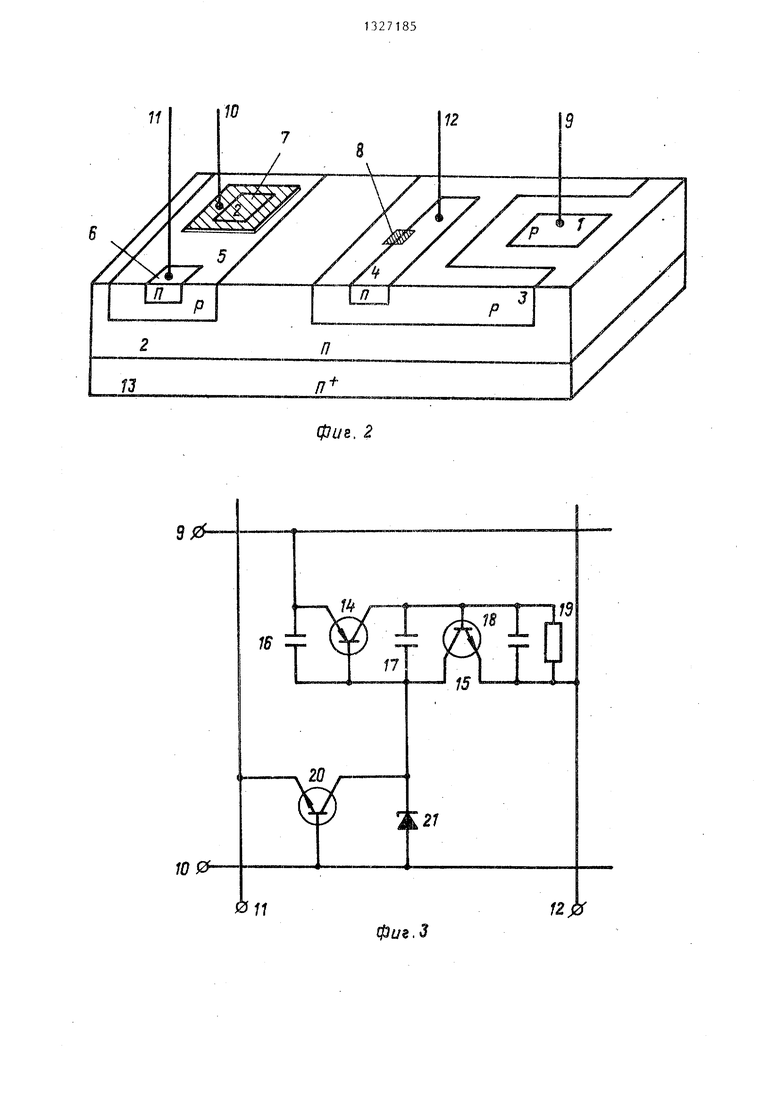

На фиг.4 приняты следующие обозначения: 22 - первый импульс питания, 23 - второй импульс питания, 24, 25- импульсы питания, проходящие на шину 12 (при состоянии ячейки 1), 26 и 27 - импульсы считывания, 28 - импульс записи состояния О, 29 - ко- ординатный импульс записи 1 (по горизонтальной шине), 30 - координатный импульс записи 1 (по вертикальной шине), 31-33 - импульсы помех, возникающие на шине 12 при записи или при считывании О, 34 - импульс считывания 1 на шине 12.

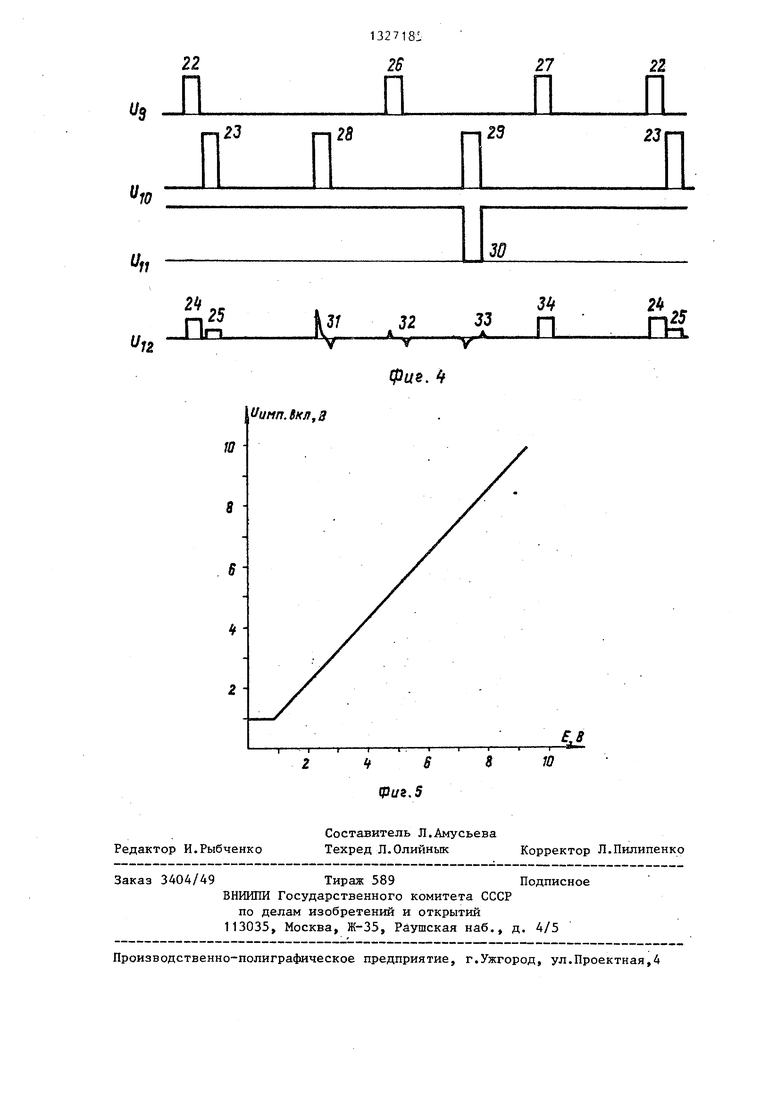

р-п-р-п-Структуры с двумя тонкими базами обладают зависимостью импульсного напряжения включения от величины амплитуды импульса, заряжающего барьерные емкости структуры. Эта зависимость для структуры, показанной на фиг.1 и 2

, может быть выражена формулой и(2-ь §i)+E(1+

и

имп. бкл

С2

С2

),(1)

где и - пороговое напряжение отпиу 2

рания р-п-перехода (,5B);

С1,С2 - барьерные емкости р-п-р-п- структуры; . Е - амплитуда зарядного импульса.

Зависимость (1) при С1 « С2 показана на фиг.5,,

Импульсное питание запоминающей ячейки осуществляют периодически

следующими с частотой примерно 10 - 10 Гц импульсами положительной полярности (22,23) с длительностью порядка 10 -10 с, причем импульс 22 подают на шину 9 (анод р-п-р-п-структуры), а импульс 23, следующий, непосредственно за импульсом 22, подают на шину 10. Нагрузочное сопротивление должно быть включено в цепь шины 12. Запоминающая ячейка может находиться в состоянии 1 (малое пороговое напряжение включения) и в состоянии О (большое пороговое напряжение включения).

В состоянии 1 импульс 22 включает р-п-р-п-структуру (1-4), а импульс 23 экстрагирует возникающий в ее базах заряд неосновных носителей через п-р-переход (2,3) и частично через п-р-переход (1,2). Ток обратного рассасывания следует ограничить нагрузочным сопротивлением в цепи шины 10.

Заряд, экстрагируемый импульсом 23, ограничивают таким образом, чтобы к концу импульса емкости 16, 17 (01,02) еще не начали заряжаться. Такое ограничение может быть достигнуто как ограничением тока обратного рас3540 45

gg

55

сасывания, так и ограничением длительности импульса 23. Так как после окончания, действия импульса 23 емкости 16, 17 не заряжены, очередной импульс 22 в соответствии с формулой (1) включает. р-п-р-п-структуру 1-4 и состояние 1 сохраняется,

В состоянии О импульс 22 не включает р-п-р-п-структуру ввиду того, что амплитуда напряжения включения больше амплитуды импульса 22. Например, если амплитуда импульса 22 рав- на 2В, а амплитуда импульса 23 равна ЗВ, то в соответствии с (1), пренебрегая некоторым разрядом 16, 17 вследствие утечек (см. фиг.5) импульсное напряжение включения близко к ЗВ и импульс 22 не включает р-п-р-п-структуру. Импульс 23, следующий непосредственно за импульсом 22, возобновляет заряд емкостей 16, 17 (С1,С2), час313

тично утекший за время между очеред- ньпчи парами питающих импульсов 22, 23. Этот импульс обеспечивает заданный уровень помехоустойчивости запоминающей ячейки в состоянии О.

Запись О осуществляют в промежутке между импульсами питания ( см, фиг.4). Для этого на шине 11 поддерживается положительный потенциал, запирающий р-п-переход 5-6, а на шину 10 подают импульс 28 положительной полярности, амплитуда которого равна Е. Совпадение положительного напряжения на шине 11 и импульсного напря- жения на пшне 10 вызывают заряд барьерных емкостей 16, 17, соответствующий большему пороговому напряжению включения p-ti-p-n-структуры (состояние О). При использовании в заряд- ной цепи диода с барьером Шоттки (21 или 7) длительность импульса записи О практически ограничена только постоянной времени RC-цепи. При использовании подключения шины 10 только к р-области 5 быстродействие несколько снижается вследствие наличия времени восстановления перехода 5-2.

Запись 1 осуществляют подачей импульса 29 на шину 10 и снятием запирающего напряжения на шине 11 (импульс 30). При этом емкость 17 коллекторного р-п-перехода (С2) разряжа- ется через транзистор, образованньш слоями 2,5,6 (фиг.1), шунт 8 (см. фиг.З - транзистор 20, шунт 19). Разряд емкости С2 (С2 С1) эквивалентен записи t

О 5 0 5

0

5

0

854

Для построения матрицы памяти иногда необходимо запретить запись в некоторые ячейки слова, например, запись 1 в первый разряд, не меняя содержания записи в соседних разрядах. Запрет записи может быть осуществлен подачей импульса положительной полярности на шину 12. В этом случае подача импульса на шину 10 не приводит к записи О ввиду равенства потенциалов на шинах 10 и 12. Подача импульса на шину 12 не вызывает изменения записи в ячейках при С1 ; С2.

Ячейка памяти может быть использована для построения различных систем запоминающих матричных микроминиатюрных устройств с малым потреблением мощности. Для изготовления запоминающих ячеек может быть использована технологическая схема с диэлектрической изоляцией, изоляцией р-п-пере- ходом с использованием скрытого слоя.

Формуле изобретения Ячейка памяти содержащая тиристор, анод и катод которого подключены соответственно к шине считывания и общей шине, отличающаяся тем, что, с целью увеличения быстродействия ячейки памяти, в нее введены ключевой транзистор и шунтир то- щий элемент, причем коллектор ключевого транзистора соединен с п-базой тиристора, база и эмиттер подключены соответственно к шине записи и информационной шине ячейки, а первый и второй выводы шунтирующего элемента подключены соответственно к катоду ;и п-базе тиристора.

. 2

Т т Т ПР Т

Т

Т,

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для регистра сдвига | 1974 |

|

SU1327186A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1972 |

|

SU434481A1 |

| СЧЕТНОЕ УСТРОЙСТВО, СОХРАНЯЮЩЕЕ ИНФОРМАЦИЮ ПРИ ПЕРЕРЫВАХ ПИТАНИЯ | 1969 |

|

SU250998A1 |

| Динамический элемент памяти | 1978 |

|

SU763966A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Матричный накопитель | 1984 |

|

SU1403096A1 |

| Многостабильный элемент памяти | 1983 |

|

SU1200340A1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах. Целью изобретения является увеличе- ние быстродействия. Поставленная цель достигается тем, что в ячейку памяти введены шунтирующий элемент и ключевой транзистор, коллектор которого соединен с п-базой тиристора, а база и эмиттер подключены соответственно к шине записи и к п-базе тиристора. 5 ил.

2Q

21

011

120

фи9.3

Фиё. 4

ицмп.

10

Ю

Редактор И.Рыбченко

Составитель Л.Амусьева

Техред Л.Олийнык Корректор Л.Пилипенко

Заказ 3404/49Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| ЗАПОМИНАЮЩАЯ ЯЧЕЙКА | 0 |

|

SU296152A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Изв | |||

| ВУЗов СССР, Радиоэлектроника т.16, № 4, с.103, 1973 (прототип). | |||

Авторы

Даты

1987-07-30—Публикация

1974-04-01—Подача