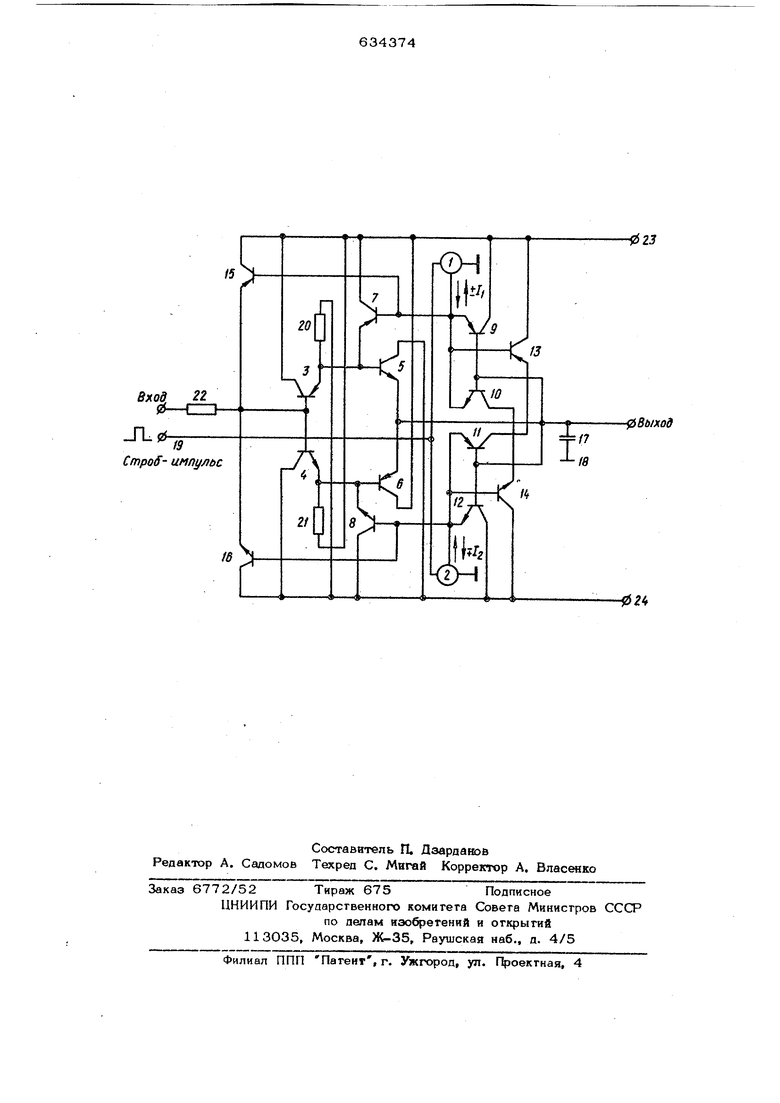

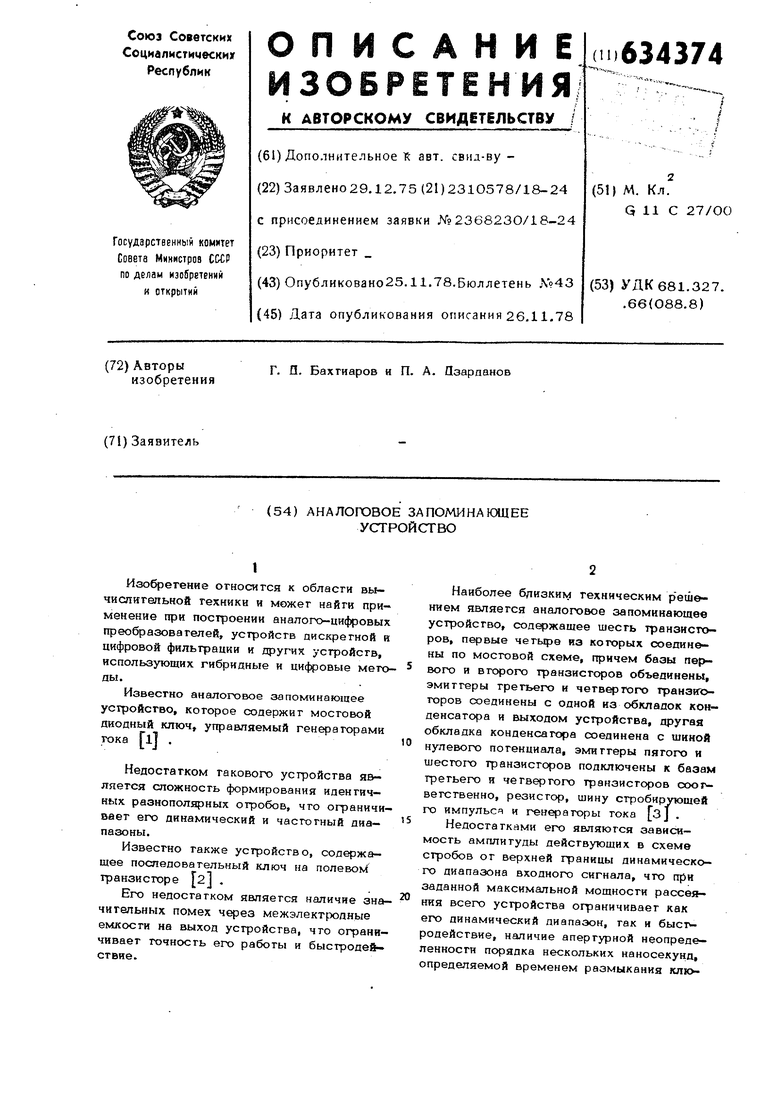

чвйых транзисторов, ограниченная точность в режиме хранения, однополярность схемы и невысокое входное сопротивление, определяемое используемыми на входе резисторами. Цепь изобретения - увеличение точности и быстродействия устройства. Поставленная цель достигается тем, что оно дополнительно содержит восемь, транзисторов, базы седьмого, восьмого, певятого и десятого транзисторов подключены к одной из обкладок конденсатора, базы пятого и шестого транзисторов соответчзтвенно соединены с эмиттерами седьмого и восьмого, девятого и десятого с базами одиннадцатого и двенадцатого тран зисторов и с выходами генераторов тока, эмигтеры одиннадцатого и двенадцатого транзисторов подключены соответственно к коллекторам девятого и восьмого транзистор в, входы генераторов тока соединены с шнной стробирующего импульса, коллектор тринадцатого транзистора и кол лектор четырнадцатого транзистора соединены соответственно с отрицательной и положительной шинами питания, эмиттеры тринадцатого и четырнадцатого транзисторов соединены с базами первого и второго транзисторов и через резистор - со входом устройства, база тринадцатого тра зистора соединена с эмиттером восьмого транзистора, а база четырнадцатого транзистора соединена с эмиттером девятого транзистора. Сущность изобретения поясняется чер- тежом, на котором изображена электриче екая схема устройства. Устройство содержит генераторы тока 1 и 2, транзисторы 3,4,5 и б, образук щие эмиттерный повторитель, транзисторы 7-16, причем транзисторы 7,9,10,13 и 15 образуют одно из плеч управления, а транзисторы 8,11,12,14 и 16 - друго плечо управления, конденсатор 17, при этом пары транзисторов разного типа про водимости 9-10 и 11-12 представляют собой двухсторонние ограничители напряж ния относительно напряжения на конденсаторе 17, а транзисторы 7 и 8 предназна чены для коммутации режимов работы уст ройства, которое также содержит шину ну левого потенциала 18, шину стробирующе го импульса 19, резисторы 20,21 и 22, положительную 23 и отрицательную 24 ш ны питания. Устройство работает следующим образом и имеет два режима работы. В перво а них оно представляет собой буферное стройство, имеющее высокое входное к алое выходное сопротивление . При этом напряжение, действующее на его входе, ОРслеживается на конденсаторе 17, являюемся его выходом. Во втором режиме устройство выполняет функцию разомкнутого ключа, при этом на конденсаторе 17 сохраняется то напряжение, которое было на нем в момент переключения из первого ежима во второй. Указанные режимы работы устройства определяются потенциалом, поступающим на шину стробирующего импульса 19. При наличии на этой шине разрешающего потенциала генератор тока 1 выдает втекающий в эмиттер транзистора 9 ток +У , а генератор тока 2 - вытекающий из эмиттера транзистора 12 ток -yg , поэтому транзисторы 9 и 12 открыты. При этом транзисторы 3,4 и 5,6 будут открыты, а транзисторы 7,8,10,11,13 т 16 полностью закрыты. Эмиттерный повторитель на транзисторах 3,4,5 и 6 в этом режиме замкнут на конденсатор 17 и поэтому напряжение на нем отслеживает входное напряжение. При подаче на шину стробирующего импульса 19 запрещающего потенциала происходит синхронное изменение полярности токов генераторов 1 и 2 без изменения их величины. При этом транзисторы 9 и ,12 запираются, а-транзисторы 10 и 11 открываются. Потенциал в тчэчке связи эмиттеров транзисторов 9 и Ю падает приблизительно на 1,4 вольта, а в точке связи эмиттеров транзисторов 11 и 12 он возрастает в то же время приблизи тельно на 1,4 вольта. Величина этих перепадов, действующих синхронно, вполне достаточна для очень быстрого запирания всех четырех транзисторов эмиттерного повторителя (на транзисторах 3,4,5 и 6), что и приводит к невозможности дальнейшего изменения заряда на конденсаторе 17. В то же время напряжения в коллекторных цепях транзисторов 10 и 11 ока, зывается привязанным к напряжению на конденсаторе 17, через открытые транзисторы 14 и 13 которые используются как плавающие источники питания, повторяющие напряжение на конденсаторе 17. Последнее обстоятельство стабилизирует величину базовых токов 10 и 11, являющихся токами утечки конденсатора 17, и, следовательно, появляется возможность компенсации этого тока утечки. Кроме того, в этом режиме оказывается замкнутым конгур, состоящий из транзисторов 10, 11, 15 и 16. Тем самым напряжение с конденсатора 17 подается на резистор 22. Образующийся при этом делитель напряжения, состоящий из резистора 22 и входного сопротивления контура, позволяет в коэффициент деления делителя раз уменьшить погрешность, определяемую пролетанием входного мгновенного значения сигнала. Поскольку размыкание эмиттерного пов торителя осуществляется путем замыкания эмиттерных токов транзисторов 3 и 4, а также базовых токов транзисторов 5 и 6 в эмиттерные цепи отпирающихся транзисторов 7 и 8 соответственно, управляемых в свою очередь небольшими и быстрыми перепадами напряжения, прикладываемыми к их базам, то время размыкания, опреде :ляемое в основном временем, необходимы :для рассасывания накопленных неосновных носителей в базах транзисторов 5 и 6, окаэывается весьма незначительным. Это обеспечивает апертурную неопределенность порядка 1 НС. Полная симме трия схемы усгройсгва относительно нулевого уровня обеспечивает работу от бипол5фных вход- ных сигналов. Предложенное устройство обеспечивает технические характеристики при небольших мощностях рассеивания, что делает возмож ным его производство методами гибридной и интегральной технологии и обуславливает высокую технико-экономическую эффек- гивность применения. Ф о изобретения Аналоговое запоминающее устройство, соцержащее шесть транзисторов, первые четыре из которых соединены по мостовой схемв) причем базы первого и второго транзисторов объединены, эмиттеры третье го и четвертого транзистсфов соединены с одной из обкладок конденсатора и выходом устройства, другая обкладка конденсатора соединена с шиной нулевого потенциала, эмиттеры пятого и шестого транзисторов подключены к базам третьего и четвертого гранзнсторов соответственно, резистор, шину стробирующего импульса и генератоаы тока, отличающееся тем, ч то с целью увеличения точности и быстро деист- ВИЯ, оно дополнительно содержит восемь транзисторов, базы, седьмого, восьмого, девятого и десятого транзисторов подключены к одной из обкладок конденсатора, базы пятого и шестого транзисторов соэтветственно соединены с эмиттером седьмого и восьмого, девятого и десятого, с базами одиннадцатого и двенадцатого транзисторов и с выходами генераторов тока, эмиттеры одиннадцатого и двенадцатогое фанзисторов подключены соответственно к коллекторам девятого и восьмого транзисторов, входы ген аторов тока соединены с шиной стробируюшего импульса, . коллектор тринадцатого транзистора и коллектор четырнадцатого транзистора;соединены соответственно с отрицательной и положительной шинами питания, эмиттер тринадцатого и четь надцатого транзисторов соединены с базами первого и второго транзисторов и через резистор - со входом устройства, база тринадцатого . транзистора соединена с эмитт ом восьмого транзистора, а база четырнадцатого транзистора .соедкнена-с эмитт ом девятого транзистора. Источники информации, принятые во вниманне при экспертизе: 1.IEEE Tt-ans.on Circuit Theory, 1964, V. CT-11, NO 3, p. 38Й-396. 2. Приборы и техника эксперимента, 1972, № а, стр. 1О7-1О9. 3.Авторское свидетельство СССР NO 484637, кл. Н ОЗ К 13/02, 17,02.73

5хо5 22 0-СИ}

SL0(9 CmpoS- импульс

02J

0 Вы ход

1йг4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для интегрирования произведения двух сигналов | 1984 |

|

SU1211764A1 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| Программируемый приемник сигналов для коммутационных сред | 1988 |

|

SU1718236A1 |

| УСТРОЙСТВО С ОТРИЦАТЕЛЬНЫМ СОПРОТИВЛЕНИЕМ | 2000 |

|

RU2175165C1 |

| РЕЛЕ ПРОМЕЖУТОЧНОЕ (ВАРИАНТЫ) | 2004 |

|

RU2263366C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ СИЛОВЫМ ТРАНЗИСТОРНЫМ КЛЮЧОМ | 1991 |

|

RU2012982C1 |

| ГЕНЕРАТОР ХАОТИЧЕСКИХ КОЛЕБАНИЙ | 2009 |

|

RU2416144C1 |

| Входное устройство схемы сравнения токов | 1989 |

|

SU1626360A1 |

| Формирователь импульсов управления | 1987 |

|

SU1522387A2 |

| Устройство задержки | 1989 |

|

SU1793535A1 |

Авторы

Даты

1978-11-25—Публикация

1975-12-29—Подача