(54) ПОСТОЯННОЕ ЗАПОМИНАКХиНЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU645203A1 |

| Запоминающее устройство с коррекцией программы | 1986 |

|

SU1347097A1 |

| УСТРОЙСТВО для ВЫБОРКИ ИНФОРМАЦИИ из постоянного ТРАНСФОРМАТОРНОГО ЗАПОМИНАЮЩЕГО | 1973 |

|

SU377868A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1287234A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU623236A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU280547A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ СИГНАЛЬНОГО ЗАРЯДА С МАТРИЧНОГО ПЗИ-ФОТОПРИЕМНИКА | 2007 |

|

RU2341850C1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU332502A1 |

| Постоянное запоминающее устройство трансформаторного типа | 1972 |

|

SU576610A1 |

1

Изобретение относится к автоматике и вычислтгельной технике, в частнсхл-и запоминающим устройствам трансформаторного типа.

Известно запоминающее устройство, которое содержит трансформаторные элементы памяти, прошитые числовыми шинами, вентили считывания, регистр числа, блок стробирования и формщзователи тока выборки. Шина считывания каждого элемента памяти соединена одним концом с вентилем считывания (элемент И-НЕ), а другим - с обшей шиной корпус Ц .

Недостатком известного устройства является значительный ток выборки, необходимый для выборки в шине считывания трансфер матерного элемента памяти сигнала, достаточного, чтобы сработал вентиль считывания. Кроме того, при считывании большого количества единиц или нулей происходит генерация помех по цепи питания вследствие одновременного открывания вентилей считывания. Подключение одного конца выходной обмотки

элементов памяти к обшей шине ухудшает соотношение сигнал/помеха на входе вентилей считывания.

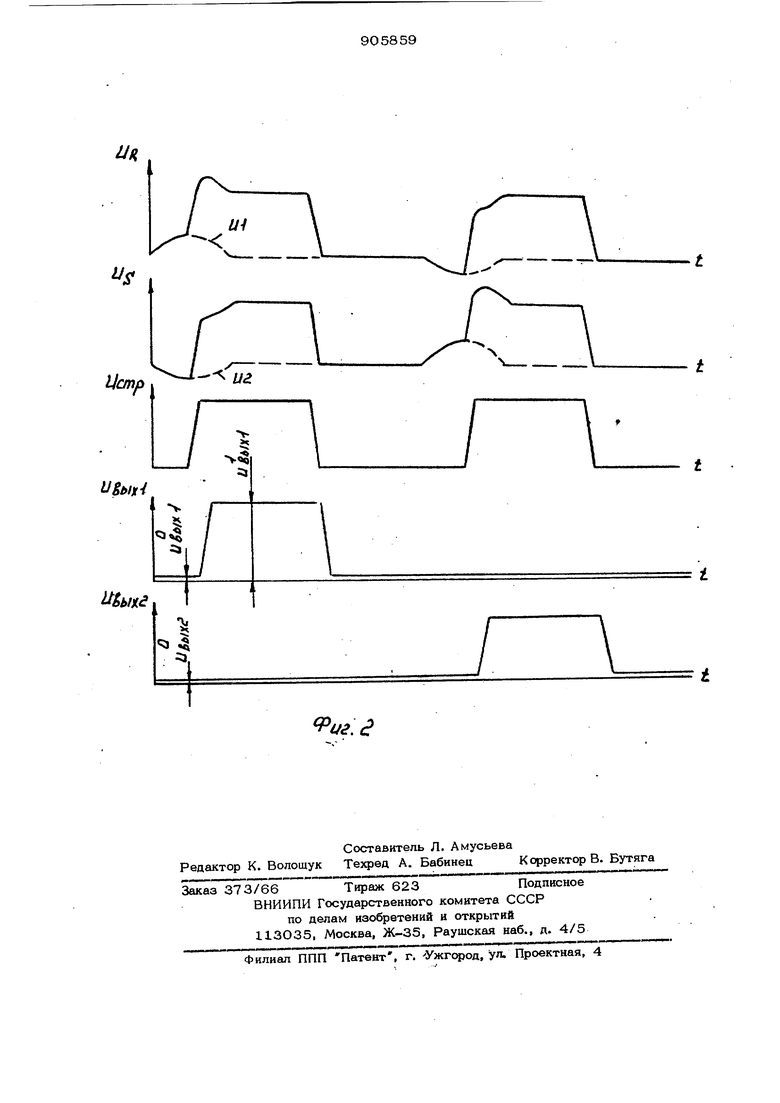

Наиболее близким по технической суш- ности и достигаемому результату к предлагаемому изобретению является запоминаюшее устройство, содержашее трансформаторные элементы памяти, прошитые числовыми шинами и соединенные с фор10мирователями тока выборки, регистр, соединенный с трансформаторными элементами памяти и блоком стробирования. Шина считывания каждого элемент памяти соединена одним выводом с входом

5 усилителя считывания соответствующего разряда регистра, а вторым выводом к обшей шине. Регистр известного устройства состоит из усилителей считывания и RS -триггеров, собранных на, элемен20тах И-ИЛИ-НЕ. Выход каждого усилите- ля считывания соединен с одним входом И соответствуюшего элементы И-ИЛИ-НЕ RS -триггера, а другой вход И этого элемента соединен с блоком стробирова- ния 2. Недостатком известного устройства является сложность регистра и недостаточная надежность работы запоминающего устройства. Так как мощность считываемых сигналов недостаточна для срабатывания логических элементов, то необходимы усилители считывания, что усложняет устройство. Подключение одно го конца шины считывания трансформатор ных элементов памяти к общей шине уху шает соотнощение сигнал/помеха на входе усилителей, а одновременное срабатывание усилителей при считывании единиц или нулей вызывает генерацию помех по цепи питания, что снижает надежность работы запоминающего устройства. Цель изобретения - ущ)ощение устройства и повышение надежности его работы Поставленная цель достигается тем, что в постоянном запоминающем устройстве, содержащем накопитель, трансформаторные элементы памяти которого г эошиты числовыми шинами и шинами считывания, подключенными соответствен но к выходам формирователей тока выборки н к входам каждого разряда регист ра, и блок стробирования, средние точки шин считывания трансфс маторных элементов памяти накопителя подключены к выходу блока С1роб1фования. Кроме того, каждый регистра содержит элементы НЕ и RS -триггер, установочные входы, которого являются входами регистра, а выходы RS - григг з соединены с соответствующими входами элементов НЕ, выходы являются выходами регистра. На фиг. 1 приведена структурная схема хфедлагаемого устройства; на фиг. 2 временная диаграмма работы регистра. Устройство содержит трансформаторные элементы памяти 1, прошитые числовыми шинами 2, соединенными с фармирователями тока выборки 3, регистр 4, каждый разряд которого соединен с щиНОЙ считывания 5 соответствующего тран сфсрматорного элемента памяти 1 и блок сгробирования 6. Каждый разряд регистра с держит RS -триггер 7, построенный на двух элементах И-НЕ 8, и два элемента НЕ 9, между устайовочными входами RS -триггера 7 включена шина считывания 5 трансфсрматсрного элемента памяти 1, средняя точка Ю шины считывания 5 соединены с блоком стробирования 6 и каждый элемент И-НЕ 8 соединен с элементом НЕ 9. Устройство работает следующим образом. В исходном состоянии с выхода блока стробирования 6 потенциал уровня логического нуля через среднюю точку Ю иГины считывания 5 поступает на Установочные входы RS -триггера 7. При этом на выходах 9 и Э В .риггера 7 сохраняются потенциалы логической единицы, а на выходах элементов НЕ 9 потенциалы логического нуля Ug,yy УА-а(см. фиг. 2). Ток, протекающий от форм1фователей тока выборки 3 по одному из числовых 1ФОВОдов 2, возбуждает на выходах шины считывания 5 трансф€фмат ного элемента памяти 1 раанопопярные сигналы Ц и и , например на входе R RS -триггера 7 положительный, а на входе S этого триггера - отрицательный. Сразу после подачи от блока С1ро6ироваН1Ш 6 в среднюю точку Ю шины считывания 5 импульса UCTP I R S -триггер 7 переходит в активное состояние и усиливает разность сигналов и и Uj . В результате однонаправленного регенеративного процесса переключения R& -триггера 7 на его выходе © устанавливается потенциал логического нуля, а на выходе элемента НЕ 9, соединенного с RS -триггером 7, уровень логической единицы Ugyx/j Состояние RS -триггера 7 определяется фазой сигналов Ц и U на входах R и S в момент подачи стробирующего импульса UCTP и сохраняется в течение его длительности. В идеальном случае увеличение заряда на одном из входов RS триггера 7, когда он находится в активном состоянии, и уменьшение заряда на другом его входе на бесконечно малую величину вызывает переключение RS триггера 7 в заранее известное состояние. В реальной схеме количество заряда, которое необходимо внести для переключения RS -триггера 7 в нужное со- стояние, определяется неидентичностью электрических параметров логически}С элементов И-НЕ 8. Чем больше отличаются электрические пераметры логических элементов И-НЕ 8, тем меньше чувствительность RS -триггера 7. Кроме того, на скорость регенеративного гфоцесса и чувствительность RS-триггера 7 влийет разброс емкостей выходных шин триггера и неидентичность параметров нагрузки. 59О Чтобы ксключить влияние нагрузки н моитажных соединений на процесс переключения R -триггера 7 и устранить генерацию помех по цепи питания при оановремеилом считывании единиц или нулей, каждый выход в и 0 RS -триггера 7 соединен с соответствующим элементом НЕ 9. При включении однс.о из элемен тов И-НЕ 8 соединенный с ним элементЙЕ 9 выключается, поэтому ток, погребляемый регистром при считывании инф(Ч)мации, не изменяется, тем самым устраняется генерация помех по цепям питания. Таким образом, совмещение в одной схеме чувствительного усилителя и триггера уменьшает количество оборудования и упрощает запоминающее устройство. Включение шины считывания 5 каждого трансформаторного элемента памяти между входами R и S триггера 7 и соединение средней точки 10 шины считывания 5 с блоком стробирования 6 ослабляет действие синфазных помех, а соединение каждого выхода Rb -триггера 7 с эле мен том НЕ 9 устраняет генерацию помех по цепям питания, вследствие этого повышается надежность работы щ едлагаемого запоминающего устройства по сравнению с известным. В регистре 4 целесообразно использовать логические элементы, физически размещенные в одном на общем кристалле. Вследствие того, что интегральные логические элементы, расположенные на общем кристал ле, изготовлены в едином технологическом цикле, параметры их иде1Ггичны с вы сокой степенью точности. В настоящее время для хранения констант, табличных функций и 1фограмм используется известное запоминающее устройство Б Ои 2О48-33 ПР3.061.ООО ТО, рае аботанное в СССР для ЕС-ЮЗЗ ЭВМ. Ово имеет плотность информации ЗО бит/см. Для того, чтобы считанная информация записалась в регистр известного устройства, величина считанного cifraana должна превышать 2 В. В отличие от базового образца, предлагаемое техническое реше596кие позволяет повысить плотность информации за счет угфощення регистра, снизить требование к величине считанного сигнала вследствие возросшей чувствительности последнего и повысить надежность запоминающего устройства благода ря уменьшению генерации помех по цепям питания. Макет запоминающего устройства имеет плотность информации 50 бит/см. Чувствительность RS -триггеров регистра, собранного по схеме фиг. 1 на микросхемах 133 серии 133 ЛАЗ, как показали измерения, - 10 ... 2О мВ, что на два выше 4yBCTBKTe;vbHocTK гфиемной части регистра базового образца. Формула изобретения 1. Постоянное запоминающее устройство, содержащее накопитель, трансфс маторные элементы памяти которого прошиты числовыми шинами а шинамя считывания, подключенными соответст векно к выходам формирователей тока выборки и к входам каждого разряда регистра, к блок стробирования, отличающееся тем, что, с целью упрощения устройства и повышения его надежности, средние точки шин считывания трансформаторных элементов памяти накопителя подкпючеиы к выходу блока стробирования. 2. Устройство по п. 1, отличающее с я тем, что, кажлилй ра;фяд регистра содержит элементы НЕ и RS триггер, установочиые входы которого являются входами регистра, а выходы RS -триггера соединены с соответствующими входами элемеотов НЕ, выходы котсрых являются выходами регистра. Источники инфqpмaaии, щ инятые во внимание горя экспертизе 1.Электроника 1967, №19, . 27. 2.ЭВМ ЕС-ЮЗЗ, ПРЗ.О61,ООО ТО (прототип).

us,-/

ие. г

Авторы

Даты

1982-02-15—Публикация

1979-06-29—Подача