Изобретение относится к вычислительной технике и может быть использовано дЛя создания постоянных запоминающих устройств с возможностью , коррекции записанных данных.

Целью изобретения является расширение области применения устройства за счет использования в устройстве блоков полупостоянной памяти с различным временем выборки.

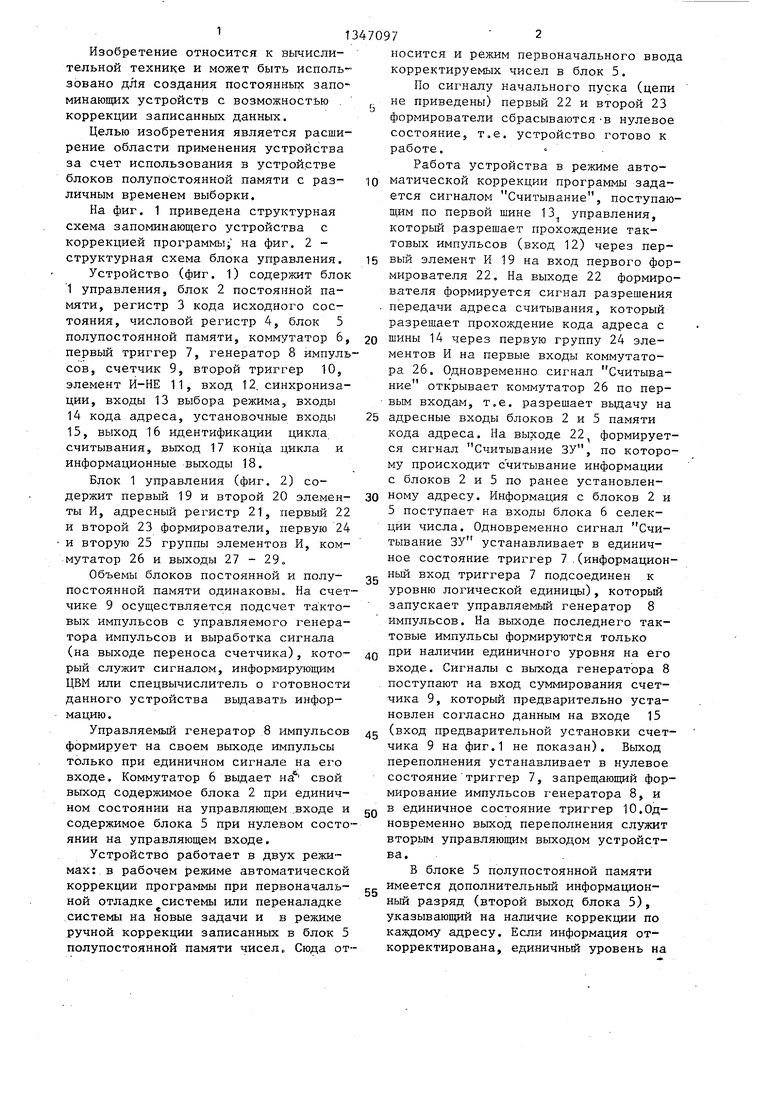

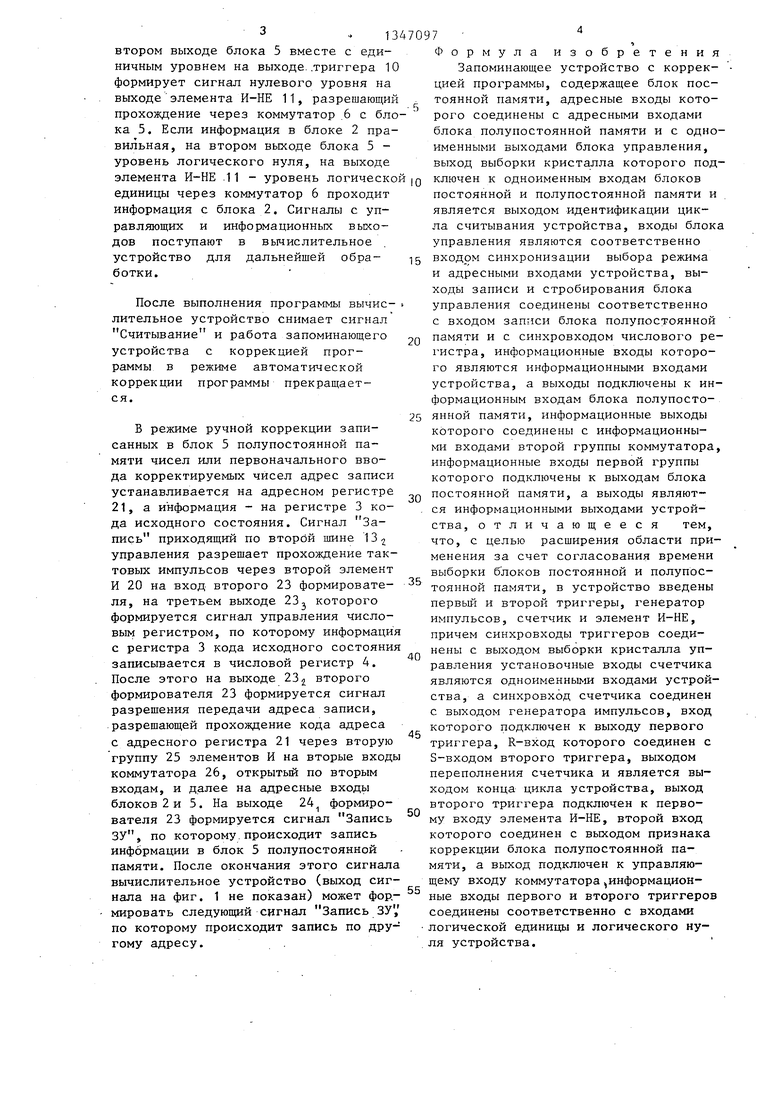

На фиг. 1 приведена структурная схема запоминающего устройства с коррекцией программыj на фиг, 2 - структурная схема блока управления.

Устройство (фиг. 1) содержит блок 1 управления, блок 2 постоянной памяти, регистр 3 кода исходного состояния, числовой регистр 4, блок 5 полупостоянной памяти, коммутатор 6, первый триггер 7, генератор 8 импульсов, счетчик 9, второй триггер 10, элемент И-НЕ 11, вход 12, синхронизации, входы 13 выбора режима входы 14 кода адреса, установочные входы 15, выход 16 идентификации ьщкла считывания, выход 17 конца цикла и информационные выходы 18.

Блок 1 управления (фиг. 2) содержит первый 19 и второй 20 элементы И, адресный регистр 21, первый 22 и второй 23 формирователи, первую 24 и вторую 25 группы элементов И, коммутатор 26 и выходы 27 - 29 о

Объемы блоков постоянной и полупостоянной памяти одинаковы На счетчике 9 осуществляется подсчет тактовых импульсов с управляемого генератора импульсов и выработка сигнала (на выходе переноса счетчика), который служит сигналом, информирующим ЦВМ или спецвычислитель о готовности данного устройства выдавать информацию .

Управляемый генератор 8 импульсов формирует на своем выходе импульсы только при единичном сигнале на его входе. Коммутатор 6 выдает на свой выход содержимое блока 2 при единичном состоянии на управляющем .входе и содержимое блока 5 при нулевом состоянии на управляющем входе.

Устройство работает в двух режимах: в рабочем ;режиме автоматической коррекции программы при первоначальной отладке системы или переналадке системы на новые задачи и в режиме ручной коррекции записанных в блок 5 полупостоянной памяти чисел. Сюда от0

5

0

носится и режим первоначального ввода корректируемых чисел в блок 5.

По сигналу начального пуска (цепи не приведены) первый 22 и второй 23 формирователи сбрасываются-в нулевое состояние, т.е. устройство готово к работе.

Работа устройства в режиме автоматической коррекции программы задается сигналом Считывание, поступающим по первой шине 13 управления, который разрешает прохождение тактовых импульсов (вход 12) через первый элемент И 19 на вход первого формирователя 22, На выходе 22 формирователя формируется сигнал разрешения передачи адреса считывания, который разрешает прохождение кода адреса с шины 14 через первую группу 24 элементов И на первые входы коммутатора 26. Одновременно сигнал Считывание открывает коммутатор 26 по пер- вым входам, т.е. разрешает выдачу на

5 адресные входы блоков 2 и 5 памяти кода адреса. На выходе 22 формируется сигнал Считывание ЗУ, по которому происходит считывание информации с блоков 2 и 5 по ранее установлен0 ному адресу. Информация с блоков 2 и 5 поступает на входы блока 6 селекции числа. Одновременно сигнал Считывание ЗУ устанавливает в единичное состояние триггер 7 . (информационный вход триггера 7 подсоединен к уровню логической единицы), который запускает управляемый генератор 8 импульсов. На выходе последнего тактовые импульсы формируются только при наличии единичного уровня на его входе. Сигналы с выхода генератора 8 , поступают на вход суммирования счетчика 9, который предварительно установлен согласно данным на входе 15

с (вход предварительной установки счетчика 9 на фиг,1 не показан). Выход переполнения устанавливает в нулевое состояние триггер 7, запрещающий формирование импульсов генератора 8, и в единичное состояние триггер 10.Одновременно выход переполнения служит вторым управляющим выходом устройства.

В блоке 5 полупостоянной памяти имеется дополнительный информационный разряд (второй выход блока 5), указывающий на наличие коррекции по каждому адресу. Ecsm информация откорректирована, единичный уровень на

5

0

0

5

втором выходе блока 5 вместе с единичным уровнем на выходе, .триггера 10 формирует сигнал нулевого уровня на выходе элемента И-НЕ 11, разрешающий прохождение через коммутатор .6 с блока 5. Если информация в блоке 2 правильная, на втором выходе блока 5 - уровень логического нуля, на выходе элемента И-НЕ .11 - уровень логической единицы через коммутатор 6 проходит информация с блока 2. Сигналы с управляющих и информационных выходов поступают в вычислительное устройство для дальнейшей обработки.

После выполнения программы вычис- i лительное устройство снимает сигнал Считывание и работа запоминающего устройства с коррекцией программы в режиме автоматической коррекции программы прекращается.

В режиме ручной коррекции записанных в блок 5 полупостоянной памяти чисел или первоначального ввода корректируемых чисел адрес записи устанавливается на адресном регистре 21, а информация - на регистре 3 кода исходного состояния. Сигнал Запись приходящий по второй шине 13 управления разрешает прохождение тактовых импульсов через второй элемент И 20 на вход второго 23 формирователя, на третьем выходе 23 которого формируется сигнал управления числовым регистром, по которому информация с регистра 3 кода исходного состояния записывается в числовой регистр 4. После этого на выходе 23 второго формирователя 23 формируется сигнал разрешения передачи адреса записи, разрешающей прохождение кода адреса с адресного регистра 21 через вторую группу 25 элементов И на вторые входы коммутатора 26, открытьй по вторым входам, и далее на адресные входы блоков 2 и 5. На выходе 24 формирователя 23 формируется сигнал Запись ЗУ, по которому.происходит запись информации в блок 5 полупостоянной памяти. После окончания этого сигнала вычислительное устройство (выход сиг10

15

20

Формула изобретения Запоминающее устройство с коррекцией программы, содержащее блок постоянной памяти, адресные входы которого соединены с адресными входами блока полупостоянной памяти и с одноименными выходами блока управления, выход выборки кристалла которого подключен к одноименньм входам блоков постоянной и полупостоянной памяти и является выходом идентификации цикла считывания устройства, входы блока управления являются соответственно входом синхронизации выбора режима и адресными входами устройства, выходы записи и стробирования блока управления соединены соответственно с входом записи блока полупостоянной памяти и с синхровходом числового регистра, информационные входы которого являются информационными входами устройства, а выходы подключены к информационным входам блока полупосто- 25 янной памяти, информационные выходы которого соединены с информационными входами второй группы коммутатора, информационные входы первой группы которого подключены к выходам блока постоянной памяти, а выходы являются информационными выходами устройства, отличающееся тем, что, с целью расширения области применения за счет согласования времени выборки блоков постоянной и полупостоянной памяти, в устройство введены первый и второй триггеры, генератор импульсов, счетчик и элемент И-НЕ, причем синхровходы триггеров соединены с выходом выборки кристалла управления установочные входы счетчика являются одноименными входами устройства, а синхровход счетчика соединен с выходом генератора импульсов, вход которого подключен к выходу первого триггера, R-вход которого соединен с S-входом второго триггера, выходом переполнения счетчика и является выходом конца цикла устройства, выход второго триггера подключен к первому входу элемента И-НЕ, второй вход которого соединен с выходом признака коррекции блока полупостоянной памяти, а выход подключен к управляющему входу коммутатора информацион30

35

40

45

50

нала на фиг. 1 не показан) может фор,- ные входы первого и второго триггеров мировать следующий сигнал Запись ЗУ , соединены соответственно с входами

логической единицы и логического нуля устройства.

по которому происходит запись по другому адресу. .

0

5

0

Формула изобретения Запоминающее устройство с коррекцией программы, содержащее блок постоянной памяти, адресные входы которого соединены с адресными входами блока полупостоянной памяти и с одноименными выходами блока управления, выход выборки кристалла которого подключен к одноименньм входам блоков постоянной и полупостоянной памяти и является выходом идентификации цикла считывания устройства, входы блока управления являются соответственно входом синхронизации выбора режима и адресными входами устройства, выходы записи и стробирования блока управления соединены соответственно с входом записи блока полупостоянной памяти и с синхровходом числового регистра, информационные входы которого являются информационными входами устройства, а выходы подключены к информационным входам блока полупосто- 5 янной памяти, информационные выходы которого соединены с информационными входами второй группы коммутатора, информационные входы первой группы которого подключены к выходам блока постоянной памяти, а выходы являются информационными выходами устройства, отличающееся тем, что, с целью расширения области применения за счет согласования времени выборки блоков постоянной и полупостоянной памяти, в устройство введены первый и второй триггеры, генератор импульсов, счетчик и элемент И-НЕ, причем синхровходы триггеров соединены с выходом выборки кристалла управления установочные входы счетчика являются одноименными входами устройства, а синхровход счетчика соединен с выходом генератора импульсов, вход которого подключен к выходу первого триггера, R-вход которого соединен с S-входом второго триггера, выходом переполнения счетчика и является выходом конца цикла устройства, выход второго триггера подключен к первому входу элемента И-НЕ, второй вход которого соединен с выходом признака коррекции блока полупостоянной памяти, а выход подключен к управляющему входу коммутатора информацион0

5

0

5

0

ные входы первого и второго триггеров соединены соответственно с входами

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки информации | 1986 |

|

SU1322256A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Запоминающее устройство с коррекцией программы | 1984 |

|

SU1246140A1 |

| Запоминающее устройство | 1979 |

|

SU826423A1 |

| Запоминающее устройство с коррекцией информации | 1984 |

|

SU1259339A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1456996A1 |

| Запоминающее устройство с кор-РЕКциЕй пРОгРАММы | 1979 |

|

SU809400A1 |

| Устройство для отображения информации | 1988 |

|

SU1566404A1 |

| УСТРОЙСТВО ДЛЯ СОКРАЩЕНИЯ ИЗБЫТОЧНОСТИ ИЗМЕРИТЕЛЬНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2007760C1 |

Изобретение относится к вычислительной технике и может быть использовано при создании постоянньрс запоминающих устройств с возможностью коррекции записанных данных. Целью изобретения является расширение области применения устройства за счет согласования времени выборки блоков постоянной и полупостоянной памяти. Устройство содержит блок управления, блоки постоянной и полупостоянной памяти, числовой регистр, коммутатор, первый и второй триггеры, генератор импульсов, счетчик, элемент И-НЕ. В устройстве обеспечивается согласование времени выборки блоков постоянной и полупостоянной памяти путем начальной установки счетчика, задающего время цикла устройства, соответствующее более медленному времени выборки блока полупостоянной памяти. 2 ил. (Л 00 4;: О со sj

| Запоминающее устройство с кор-РЕКциЕй пРОгРАММы | 1979 |

|

SU809400A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с коррекцией программы | 1984 |

|

SU1246140A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-10-23—Публикация

1986-04-29—Подача