(54) ЦИФРОВОЙ ДЕСЯТИЧНЫЙ ИЗМЕРИТЕЛЬ СРЕДНЕЙ ЧАСТОТЫ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель средней частоты | 1977 |

|

SU705360A1 |

| Цифровой измеритель средней частоты | 1980 |

|

SU920555A2 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Датчик угловой скорости | 1985 |

|

SU1296949A1 |

| Устройство для измерения относительного изменения напряжения | 1989 |

|

SU1718133A1 |

| Реверсивный счетчик | 1981 |

|

SU982201A1 |

| Устройство для измерения разности частот импульсов | 1978 |

|

SU728492A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Электропривод | 1987 |

|

SU1476584A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

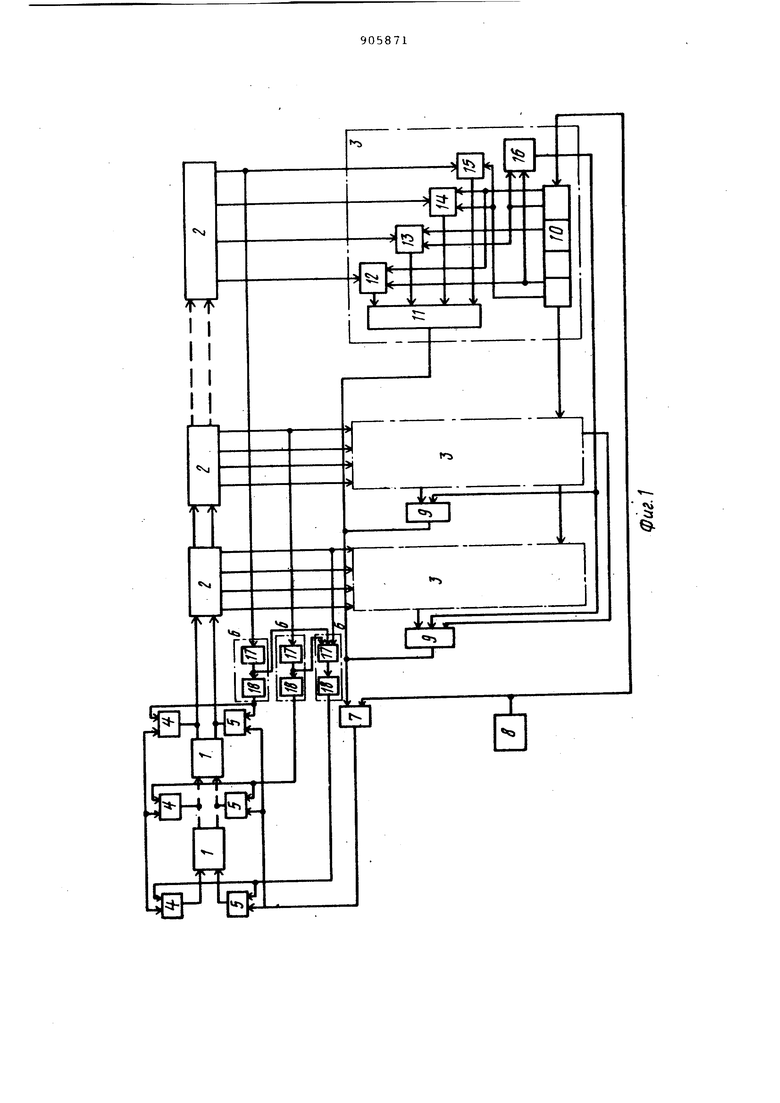

Изобретение относится к иэмерител ,ной технике и может быть использовано при регистрации импульсов с детек торов ионизирующих излучений. Известен цифровой десятичный изме ритель частоты, содержащий счетчик измеряемой частоты и цепочку делителей частоты, входы которых через вен тили соединены соответственно со входным формирователем и с генератором калибровочной частоты, а выходы с индикаторным табло и с первыми вхо дами вентилей управления, вторые вхо ды которых соединены с матричным кодовым дешифратором, соединенным со счетчиком концов эталонных интервалов времени, вход которого соединен с выходами вентилей управления и с триггером поиска конца счета, выход которого через триггер управления счета соединен с вентилями счетчика и калибровочной частоты 1. Однако это устройство обладает значительной систематической погрешностью и недостаточным быстродейств ием. Наиболее близким по технической сущности к предложенному является цифровой десятичный измеритель скорости счета, содержащий две последовательно соединенные группы из - предварительных реверсивных счетчиков и wi основных десятичных реверсивных счетчиков, выходы которых подключены к разрядным входам т преобразователей, тактовые четырехразрядные счетчики каждого из которых соединены последовательно друг с другом, а счетный вход первого из них соединен с выходом .тактового генератора 2. Недостатком известного устройства является значительная систематическая погрешность измерения, возникающая при динамических изменениях частоты и обусловленная большим временем измерения. Кроме того, входная частота индицируется с некоторой задержкой относительно процесса измерения. Цель изобретения - повышение точности измерения. Поставленная цель достигается тем, что в цифровой десятичный измеритель средней частоты импульсов, содержащий две последовательно соединенные группы из t предварительных реверсивных счетчиков и m основных десятичных реверсивных счетчиков, выходы которых подключены к разрядным входам m преобразователей, тактовые четырехразрядные счетчики каждого из которых соединены последовательно друг с дру гом, а счетный вход первого из них соединен с выходом тактового генератора введены К. блоков обратной связи R пар элементов совпадений, (m-i) бло ков управления и тактирующий элемент И, при этом выходы элементов совпаде ,ния с первой по (R-l)-yro и последней -4-ой пары соединены с входами -1 пред варительных реверсивных счетчиков и первого основного десятичного реверсивного счетчика соответственно, пер вые входы в каждой паре элементов Iсовпадения соединены между собой и подключены к прямому выходу соответствующего блока обратной связи, инверсный выход каждого из ко-торых сое динен с первыми входами всех блоков обратной связи, вторые входы которых соединены с выходами старших разрядо соответствующих основных десятичных реверсивных счетгчиков, вторые входы -ft пар элементов совпадения подключены к входной шине устройства и к выходу тактирующего элемента И; первый вход которого соединен с выходом так тового генератора, а второй вход под ключен к управляющим выходуV -го пре образователя и к выходам () блоко управления, первые входы каждого из которых соединены с управляющими выходами соответствующих преобразователей, вторые входы соединены межДу собой и подключены к дополнительному выходу преобразователя, а треть входы блоков управления соединены с дополнительными выходами { «-D-ro преобразователя. Причем, преобразователь содержит четыре элемента И, первые входы кото рых являются разрядными входами прео ,разователя, второй вход первого элемента И соединен с выходом четвертого разряда четырехразрядного-тактового счетчика и с первым входом ijio о го элемента И, третий вход первого элемента И соединен с вторым входом третьего элемента И и с выходом первого разряда четырехразрядного тактового счетчика, второй вход второго элемента И соединен с вторым входом пятого элемента И и с инверсным выхо дом первого разряда четырехразрядного тактового счетчика, выход которого является дополнительным выходом преобразователя, третий вход второго И соединен с выходом второго разряда четырехразрядного тактового счетчика, третий вход третьего элемента И соединен с вторым входом четвертого элемента И и с инверсным выходом четвертого разряда четырехразрядного тактового счетчика, а выходы всех четырех элементов И подклю чены к входам блока сборки, выход ко торого является управляющим выходом преобразователя. При этом блок обратной связи содержит элемент совпадения, выход которого является инверсным выходом блока обратной связи и соединен с входом инвертора, выход которого является прямым выходом блока обратной связи. На фиг. 1 представлена схема цифрового десятичного измерителя средней частоты импульсов; на фиг, 2 временные диаграммы преобразователя I (управляющий выход) при десяти различных кодах основного десятичного реверсивного счетчика. Устройство содержит последователь но соединенные группы из I предварительн лх реверсивных счетчиков 1 и « основных десятичных реверсивных счетчиков 2, преобразователя 3, -k пар элементов 4 и 5 совпадения, блоки 6 , обратной связи, тактирующий элемент 7 И, тактовый генератор 8, блок 9 управления, четырехразрядные тактовые счетчики 10, блок 11 сборки, элементы 12-16 И. Блок 6 обратной связи содержит элемент 17 совпадения,,выход которого является инверсным выходом блока 6 обратной связи и соединен с выходом инвертора 18, выход которого является прямым выходом блока б обратной связи. Устройство работает следующим образом. В исходном состоянии входные импульсы поступают на вторые входы элементов 4. Элементы 4 и 5 по первым входам управляются потенциалами блоков б. Каждый блок б по одному входу управляется потенциалом четвертого разряда соответствующего основного десятичного реверсивного счетчика 2, а по другим входам - потенциалами инверсных выходов блоков б более старших разрядов. Логическая едини«а четвертого разряда любого основного десятичного реверсивного счетчика 2 (что соответствует десятичным числам 8,9) вырабатывает разрешающий потенциал на прямом выходе соответствующего блока б, который управляет соответствующей парой элементов 4 и 5. Одновременно с этим на инверсном выходе данного блока б появляется запрещающий потенциал для всех блоков б, которые управляют прохождением входных сигналов к младшим основным десятичным реверсивным счетчикам 2. При этом открывается путь для суммирующих входных импульсов и вычитающих импульсов с выхода тактирующего элемента 7 через соответствующую пару элементов 4,5 на выходы предварительных реверсивных счетчиков 1 или основного десятичного реверсивного счетчика 2 младшего разряда. Коды каждого основного десятичного реверсивного счетчика 2 поступают на входы соответствующего преобразователя 3, где происходит их сравнение с кодами тактового четырехразрядного счетчика 10. На временной диаграмме (фиг. 1) видно, что на каждое значение кода основного десятичного реверсивного счетчика 2 преобразователь 3 вырабатывает последовательность импульсов с переменной скважностью и длительностью, прямо зависящей от кода реве сивного счетчика 2. Так, например, число 7 преобразуется в импульсную последовательность, в которой доля положительных импульсов (фиг. 2) рав на 7 входным тактам. Импульсы с управляющего выхода каждого преобраз ,вателя 3 поступают на соответствующий блок 9, на другие входы которого подаются импульсы с дополнительных выходов старших преобразователей 3. Импульсы с дополнительного выхода преобразователя 3 являются разрешающими для всех управляющих блоков 9 преобразователей 3. Так как длительность этого сигнала на втором(третьем и т.д.) входе более младшего упра ляющего блока 9 в десять раз меньше периода, то вклад более младшего пре образователя 3 тоже в десять раз -меньше. Таким образом, -1 преобразо ватель 3 дает вклад в суммарный импульс по второму входу тактирующей схемы И и десять раз меньше, чем более старший 1 преобразователь 3. В тактирующем элементе 7 происходит стробировка суммарной импульсной последовательности со всех преобразова телей 3, и средняя частота импульсов на выходе тактирующего элемента 7 равна входной частоте импульсов. Сле довательно, На входах сложения и вычитания десятичных счетчиков 1 или 2 частоты равны, а на основном десятич ном реверсивном счетчике 2 будет код прямо пропорциональный входной часто Увеличение точности измерения обе печивается следующим образом. Блоки обратной связи автоматически следят за величиной (порядком) измеряемой частоты. При этом, если входная частота имеет мaлqje значение то количество функционирующих предва рительных реверсивных счетчиков 1 увеличивается. При увеличении входной частоты число функционирующих о предварительных реверсивных счетчиков 1 уменьшается. Относительная величина среднеквадратичной погрешност определяется по формуле , С - постоянная времени измерителя;п - значение входной частоты. Подставив в это выражение значения п и Т где N, N3- соответственно емкости предварительного и основного десятичных реверсивных счетчиков; п - частота тактового генератора;N - код измеряемой частоты, снимаемый с основного реверсивного счетчика, получим V2N-N (3) Сравнительный анализ технических характеристик известного и данного измерителя, у которых число предварительных и основных десятичньох реверсивных счетчиков соответственно равно - 2 и з, показал, что при одноразовом измерении динамически изменяющейся входной частоты величина случайной погрешности для известного составляет согласно формуле (3) величину: 2.1оОО 2,2%, а для данного устройства величину 5Г 1 0,22%, 2-100- 1000 т.е. в десять раз меньшую. Формула изобретения 1. Цифровой десятичный измеритель средней частоты импульсов, содержащий две последовательно соед иненные группы из - предварительных реверсивных счетчиков и m основных десятичных реверсивных счетчиков, выходы которых подключены к разрядным входам м преобразователей, тактовые четырехразрядные счетчики каждого из которых соединены последовательно один с другим, а счетный вход первого из них соединен с выходом тактового генератора, отличающийся тем, что, с целью повышения точности измерения, в него введены Л блоков обратной связи,k пар элементов совпадений, (M-I) блоков управления и тактирую-. щий элемент И, при этом выходыэлементов совпадения с первой по (Л-1)ую и последней k-ой пары соединены с входами предварительных реверсивных счетчиков и первого основного десятичного реверсивного счетчика соответственно, первые входы в каждой паре элементов совпадения соединены между собой и подключены к прямому выходу соответствующего блока обратной связи, инверсный выход каждого из которых соединен с первыми входами всех блоков обратной связи, вторые входы которых соединены с выходё1ми старших разрядов соответствующих основных десятичных реверсивных счетчиков, вторые входы Л пар элементов совпсщения подключены к входной шине устройства и к выходу тактирующего элемента И, первый вход которого соединен с выходом тактового генератора а второй вход подключен к управляющему выходу ivi-ro преобразователя и к выходам ) блоков управления, первые входы каждого из которых соединевы с управляющими выходами соответствующих преобразователей, вторые входы соединены между собой и подключены к дополнительному выходу i-го преобразователя, а третьи входы блоков управления соединены с .дополнительными выходами (ю-1)-го преобразователя. 2. Измеритель по п. 1, отличающийся тем, что преобразова тель содержит четыре элемента И, первые входы которых являются разрядными входами преобразователя, второй вход первого элемента И соединен с выходом четвертого разряда четырехразрядного тактового счетчика и с первым входом пятого элемента И, тре тий вход первого элемента И соединен с вторым входом третьего элемента И и с выходом первого разряда четырехразрядного тактового счетчика, второ вход второго -элемента И соединен с вторым входом пятого элемента И и с инверсным выходом первого разряда четырехразрядного тактового счетчика, выход которого является дополнительным выходом преобразователя, третий вход второго элемента И соединен с выходом второго разряда четырехразрядного тактового счетчика, третий вход третьего элемента И соединен с вторым входом четвертого элемента И и с инверсным выходом четвертого разряда четырехразрядного тактового счетчика, а выходы всех четырех элементов И подключены к входам блока сборки, выход которого является управляющим выходом преобразователя. 3. Измеритель по п. 1 и 2, отличающийся тем, что блок обратной связи содержит элемент совпадения, выход которого является инверсным выходом блока обратной связи и соединен с входом инвертора, выход которого является прямым выходом блока обратной связи. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 194185, кл. G 01 R 23/10. 2.Nuclear Instruments and met- hods 34, 1965, с. 106.

I

I

f .J 5

фиг2

W

8

Авторы

Даты

1982-02-15—Публикация

1979-12-10—Подача