Ъ

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Электропривод | 1985 |

|

SU1275726A1 |

| Система регулирования скорости | 1984 |

|

SU1229727A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Цифровой импульсный электропривод постоянного тока | 1988 |

|

SU1552323A1 |

| Цифровая система регулирования частоты вращения двигателя постоянного тока | 1986 |

|

SU1386959A1 |

| Цифровой электропривод | 1982 |

|

SU1050077A1 |

| Цифровой демодулятор сигналов с фазово-импульсной модуляцией | 1985 |

|

SU1379939A1 |

| Устройство для настройки и поверки импульсной электроразведочной аппаратуры | 1984 |

|

SU1241177A1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

Изобретение относится к электротехнике и может быть использовано для управления электродвигателями постоянного тока. Целью изобретения является повышение качества регулирования. Устройство содержит схему 5 синхронизации, два реверсивных счетчика 20, 21 и регистр 22 с первой и второй группами информационных входов, подключенных к выходам соответственно первого и второго реверсивных счетчиков 20, 21. Выход регистра 22 подключены к цифровому регулирующему блоку 23. Повышение качества регулирования обеспечивается за счет раздельной обработки информации, содержащейся в старших и младших разрядах регистра 22. 1 з.п. ф-лы, 2 ил.

Шиг.1

Изобретение относится к электротехнике и может быть использовано в электроприводах с цифровым управлением.

Целью изобретения является повышение качества регулирования.

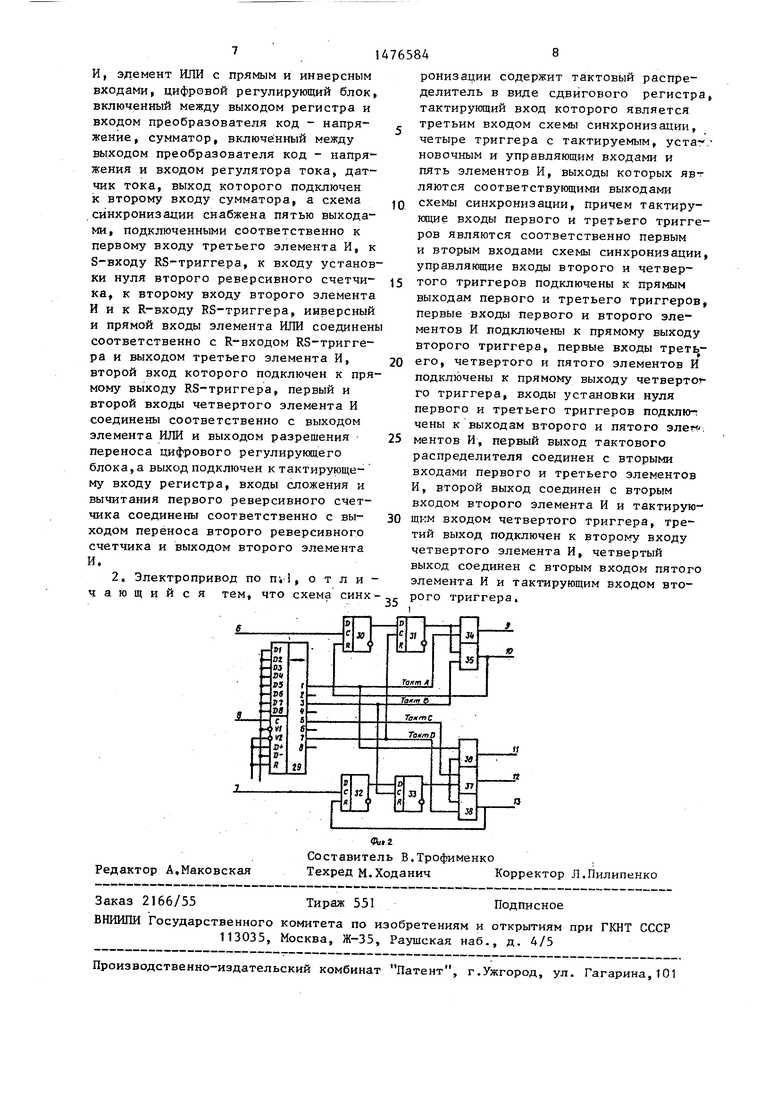

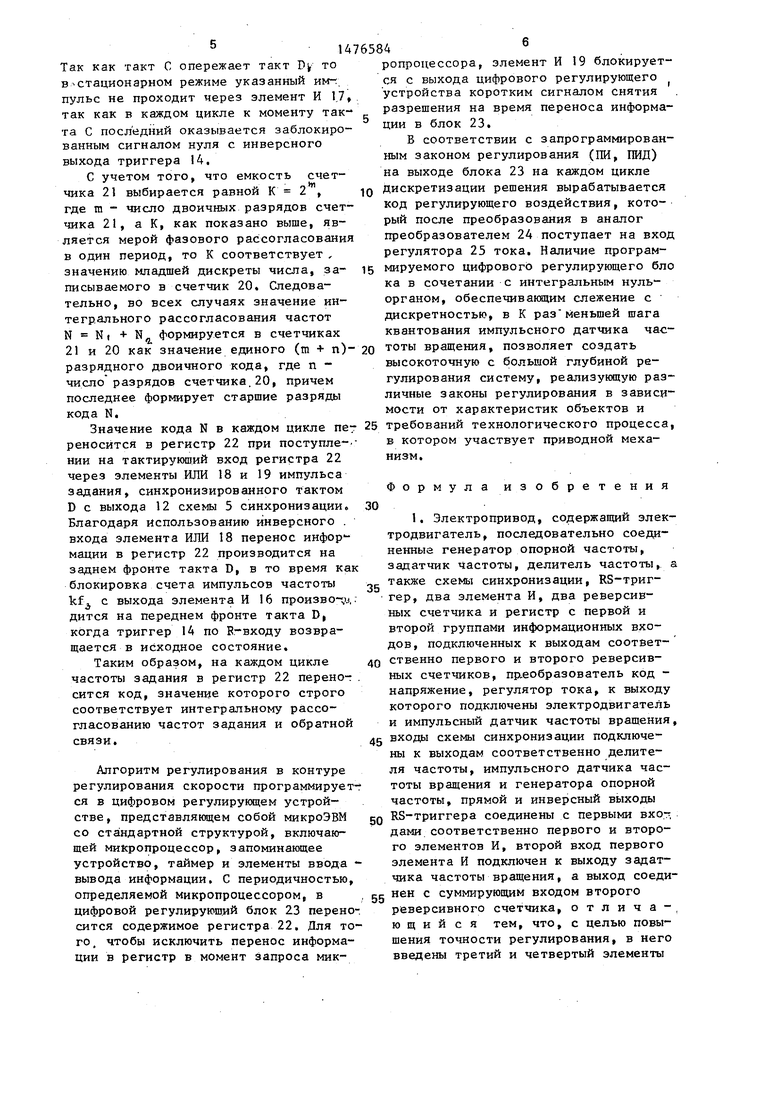

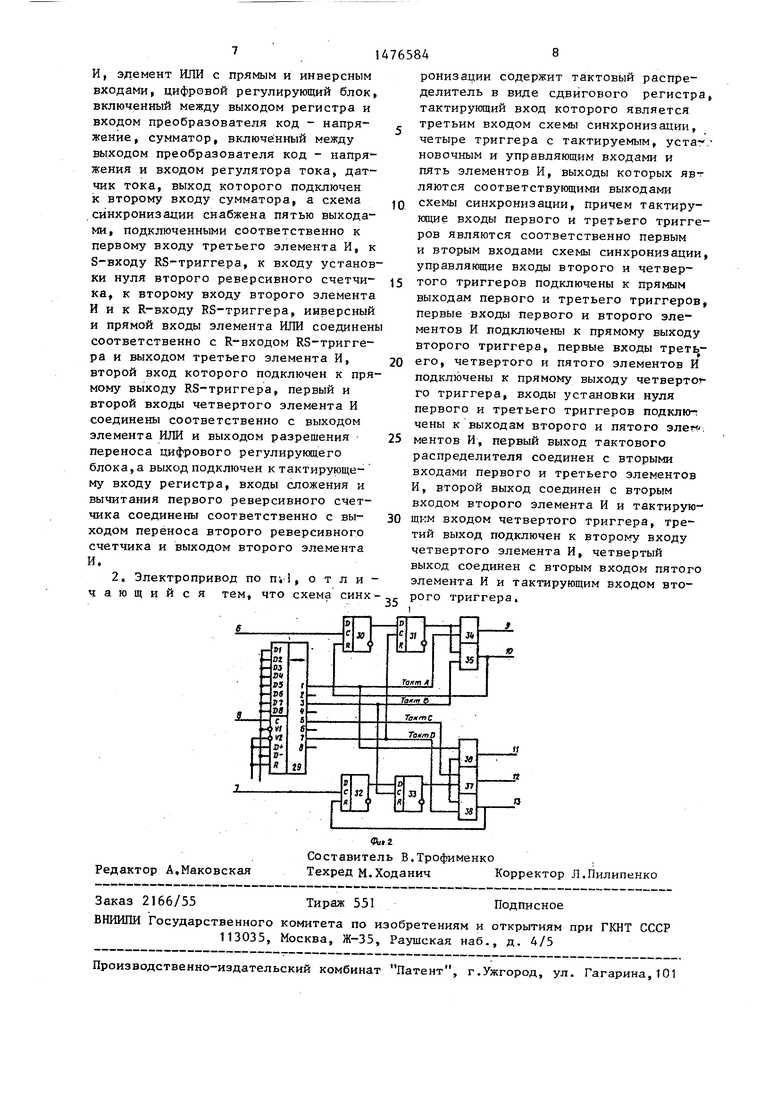

На фиг,1 приведена схема электропривода; на фиг.2 - схема синхронизации.

Электропривод содержит электродвигатель 1, последовательно соединенные генератор 2 опорной частоты, задатчик 3 частоты вращения, делитель 4 частоты, схему 5 синхронизации с тремя входами 6 - 8 и пятью выходами 9 - 13, RS-триггер 14, три элемента И 15 - 17, первые входы которых соединены с выходами RS-триггера 14, элемент ИЛИ 18 с прямым и инверсным входами, соединенными соответственно с выходом первой схемы И 15 и первым выходом 9 схемы 5 синхронизации, четвертый элемент И 19, первый вход

которого подключен к выходу элемента 25 задания f, пропорциональная коду ИЛИ 18, реверсивные счетчики 20 и

21,регистр 22 с первой и второй группой информационных входов и так-f тирующим выходом, цифровой регулирующий блок 23, информационный вход которого соединен с выходом регистра

22,а выход разрешения переноса подключен к второму входу четвертого элемента И 19, преобразователь 24

задания N3, поступающему на вход управления задатчика 3 частоты вращения, и частота обратной связи f. , формируемой импульсным датчиком 28 30 частоты вращения. Функция схемы 5 синхронизации заключается в том, чтобы осуществить временную привязку

импульсов сравниваемых частот f3 и f , фазовые соотношения между которы

код - напряжение, регулятор 25 тока, 35ми могут быть произвольными, к такти -

датчик 26 тока, сумматор 27, импульс-рующим импульсным последовательностям

ный датчик 28 частоты вращения, при-(такты А, В, С и D) производных от

чем вход преобразователя 24 код -частоты генератора 2. напряжение соединен с информационным Такты А, В, С и D формируются с

выходом цифрового регулирующего блока допомощью времяимпульсного распредели23, а выход подключен к первому вхо-теля 29, выполненного на 8-разрядном

ду сумматора 27, второй вход которого соединен с выходом датчика 26 тока, а выход подключен к входу регулятора 25 тока, выходом связанного с электродвигателем 1.

Схема 5 синхронизации содержит тактовый распределитель 29 в виде сдвигового регистра, четыре триггера 30 - 33, пять элементов И 34 - 38, выходы которых являются соответствую-, щими выходами 9-13 схемы 5 синхронизации, первым, вторым и третьим входами (6, 7 и 8) которой являются

сдвиговом регистре, на тактирующий вход 8 которого подана опорная частота Ј0 с выхода генератора 2. Частота 4ц тактирующих импульсных последовательностей на каждом из его выходов составляет при этом f0/8, временная раздвижка импульсов соседних тактов в каждом цикле составляет 2Т0, где Т0 - период опорной частоты, Триггеры 30 и 32 схемы 5 синхронизации служат элементами памяти и фиксируют факт поступления импульсов сравниваемых частот по входам 6 и 7. При

50

тактирующие входы соответственно пер-55 пост111161 1 1 импульса входной частоты вого 30 и третьего 32 триггеров и триггер 30 (32) включает схему перетактового распределителя 29. Тактовые носа информации на триггере 31 (33) выходы распределителя 29 подключены и элементах И ,34, 35 (36, 37, 38), соответственно к входам элементов И разрешая управление по входу D триг34, 36, к входу элемента И 35 и тактирующему входу триггера 33, к входу элемента И 37, к входу элемента И 38

и тактирующему входу триггера 31. Выход триггера 31 связан с входами эле ментов И 34, 35, а выход триггера 33 - с входами элементов И 36 - 38. Электропривод работает следующим

образом.

Электропривод является двухконтур- ной системой подчиненного регулирования частоты вращения двигателя 1 постоянного тока. Внутренний контур

регулирования тока якоря двигателя выполнен аналоговым на основе регулятора 25 тока, включающего тиристор- ный или транзисторный преобразователь мощности, с отрицательной обратной связью по току якоря двигателя от датчика 26 тока. Внешний контур регулирования частоты вращения выполнен цифровым. На входы 6 и 7 схемы 5 синхронизации поступают частота

задания f, пропорциональная коду

задания N3, поступающему на вход управления задатчика 3 частоты вращения, и частота обратной связи f. , формируемой импульсным датчиком 28 частоты вращения. Функция схемы 5 синхронизации заключается в том, чтобы осуществить временную привязку

импульсов сравниваемых частот f3 и f , фазовые соотношения между которы

сдвиговом регистре, на тактирующий вход 8 которого подана опорная частота Ј0 с выхода генератора 2. Частота тактирующих импульсных последовательностей на каждом из его выходов составляет при этом f0/8, временная раздвижка импульсов соседних тактов в каждом цикле составляет 2Т0, где Т0 - период опорной частоты, Триггеры 30 и 32 схемы 5 синхронизации служат элементами памяти и фиксируют факт поступления импульсов сравниваемых частот по входам 6 и 7. При

гера 32 (33). Схема 5 синхронизации работает по трехтактной схеме так, что, например, импульс такта D (В) опрашивает состояние триггера 31 г (33), а импульсы тактов А и В (С и D) формируют импульсы на выходы 9 и 10 (12 и 13) схемы 5 синхронизации, обеспечивая таким образом их жесткую временную раздвижку. Выходной им- ю пульс по R-входу возвращает в исход - ное состояние триггеры 30 (32), после чего очередной импульс такта D (В) возвращает в исходное состояние триггер 31 (33) по С-входу, 15 так как в это время на входе D последнего -уже имеет место уровень логического О. Чтобы исключить возникновение существенных возмущений от девиации фазовых сдвигов импуль- 20 сов f и foc, вызываемых принудительной временной привязкой, уровень тактирующих частот выбирается значительно выше максимально возможного уровня частот f, и foc . 25

В стационарном режиме при равенстве частот задания и обратной связи импульсы этих частот, синхронизированных соответственно тактами В и D с выходом 10 и 13 схемы синхрониза- 30 ции, поочередно поступают на устанет- вочные входы RS-триггера 14 и переключают его с частотой F5 foc , При этом скважность следования прямоугольных импульсов на выходах триг- ,5 гера 14 постоянна и определяется установившимся фазовым сдвигом между мпульсами обеих входных последовательностей.

40

На второй вход элемента И 16,

управляемого сигналом с прямого выхода триггера 14, поступает выходная частота задатчика 3, равная kfj,,rfle k - коэффициент деления делителя 4 .с частоты. В указанном режиме на выходе элемента И 16 в каждом цикле переключения триггера 14 формируется па-, кет импульсов частоты kfj, поступающих на счетный вход счетчика 21. Обнуление счетчика 21 по входу R про-50 изводится каждым импульсом частоты обратной связи, синхронизированным тактом А, Таким образом, в каждом цикле в интервале времени между тактами D и А в счетчике хранится код , значение которого пропорционально времени нахождения триггера 14 в состоянии 1, т.е. фазовому сдвигу

между импульсами f, и fpc в стационарном режиме. При этом очевидно, что значение кода N« может лежать в пределах от 0 до k, для определенн го фазового сдвига импульсов частот f э и foc постоянно и не зависит от их абсолютного значения, а значит, и от значения частоты вращения. С учетом переходных процессов и динамических режимов регулятор частоты вращения не обеспечит нормальную работу с нуль-органом, фиксирующим фазовые рассогласования только в пределах одного периода сравниваемых частот. Необходим интегратор, который может фиксировать интегральное фазовое рассогласование частот, превышающее один период (или 2fr). В электроприводе цифровой интегратор состоит из двух счетчиков 20 (работает в реверсивном режиме) и 21 (работает только в режиме прямого счета). Выход переноса Р+ счетчика 21 связан с входом сложения счетчика 20, вход вычитания последнего связан с выходом элемента И 17, который управляется с инверсного входа триггера 14. На информационт ный вход элемента И 17 поступают с выхода 11 схемы 5 синхронизации импульсы частоты обратной связи, синхронизированные тактом С. Емкость счетчика 21 выбирается равной К. С учетом этого при фазовом рассогласовании, превышающем один период частоты задания, счетчик 21 переполняется и по цепи переноса в счетчик 20 записывается число целых периодов ошибки

N,

Последнее имеет место в переходных режимах.

При разгоне двигателя с нуля в мо менты, когда импульсы цепи обратной связи еще отсутствуют, импульсы переноса информации в регистр 22 синхронизируются тактом А с выхода 9 схемы 5 синхронизации и поступают через элемент И 15 на вход элемента И 18 при нахождении триггера 14 в состоянии 1.

При изменении кода задания в сторону замедления частоты вращения на счетный вход вычитания счетчика 20 начинают поступать через элемент И 17, минуя триггер 14, импульсы обратной связи, синхронизированные тактом С. Последнее происходит в случае поступления подряд двух и более импульсов частоты обратной связи при отсутствии импульсов частоты задания.

Так как такт С опережает такт Т то в стационарном режиме указанный импульс не проходит через элемент И 17, так как в каждом цикле к моменту такта С последний оказывается заблокированным сигналом нуля с инверсного выхода триггера 14.

С учетом того, что емкость счетчика 21 выбирается равной К 2 , где m - число двоичных разрядов счетчика 21, а К, как показано выше, является мерой фазового рассогласования в один период, то К соответствует „ значению младшей дискреты числа, записываемого в счетчик 20. Следовательно, во всех случаях значение интегрального рассогласования частот N NI + N Формируется в счетчиках

ропроцессора, элемент И 19 блокируется с выхода цифрового регулирующего ( устройства коротким сигналом снятия разрешения на время переноса информа5 ции в блок 23.

В соответствии с запрограммированным законом регулирования (ПИ, ПИД) на выходе блока 23 на каждом цикле

10 дискретизации решения вырабатывается код регулирующего воздействия, который после преобразования в аналог преобразователем 24 поступает на вход регулятора 25 тока. Наличие програм15 мируемого цифрового регулирующего бло ка в сочетании с интегральным нуль- органом, обеспечивающим слежение с дискретностью, в К раз меньшей шага квантования импульсного датчика час21 и 20 как значение единого (т + п)- 20 ТОТЫ вращения, позволяет создать разрядного двоичного кода, где п - число разрядов счетчика.20, причем последнее формирует старшие разряды кода N.

высокоточную с большой глубиной регулирования систему, реализующую различные законы регулирования в зависи- мости от характеристик объектов и Значение кода N в каждом цикле пег 25 требований технологического процесса,

в котором участвует приводной механизм.

Формула изобретения

Таким образом, на каждом цикле частоты задания в регистр 22 перенот сится код, значение которого строго соответствует интегральному рассогласованию частот задания и обратной связи.

Алгоритм регулирования в контуре регулирования скорости программируется в цифровом регулирующем устройстве, представляющем собой микроэвм со стандартной структурой, включающей микропроцессор, запоминающее устройство, таймер и элементы ввода - вывода информации. С периодичностью, определяемой микропроцессором, в цифровой регулирующий блок 23 переносится содержимое регистра 22. Для того , чтобы исключить перенос информации в регистр в момент запроса мик30

40

35„

гер, два элемента И, два реверсивных счетчика и регистр с первой и второй группами информационных входов, подключенных к выходам соответственно первого и второго реверсивных счетчиков, преобразователь код - напряжение, регулятор тока, к выходу которого подключены электродвигатель и импульсный датчик частоты вращения, 45 входы схемы синхронизации подключены к выходам соответственно делителя частоты, импульсного датчика частоты вращения и генератора опорной частоты, прямой и инверсный выходы RS-триггера соединены с первыми вхо- дами соответственно первого и второго элементов И, второй вход первого элемента И подключен к выходу задат- чика частоты вращения, а выход соединен с суммирующим входом второго реверсивного счетчика, о т л и ч а -, ю щ и и с я тем, что, с целью повышения точности регулирования, в него введены третий и четвертый элементы

50

55

ропроцессора, элемент И 19 блокируется с выхода цифрового регулирующего ( устройства коротким сигналом снятия разрешения на время переноса информации в блок 23.

В соответствии с запрограммированным законом регулирования (ПИ, ПИД) на выходе блока 23 на каждом цикле

дискретизации решения вырабатывается код регулирующего воздействия, который после преобразования в аналог преобразователем 24 поступает на вход регулятора 25 тока. Наличие программируемого цифрового регулирующего бло ка в сочетании с интегральным нуль- органом, обеспечивающим слежение с дискретностью, в К раз меньшей шага квантования импульсного датчика час1. Электропривод, содержащий электродвигатель, последовательно соединенные генератор опорной частоты, задатчик частоты, делитель частоты, а также схемы синхронизации, RS-триг0

5„

гер, два элемента И, два реверсивных счетчика и регистр с первой и второй группами информационных входов, подключенных к выходам соответственно первого и второго реверсивных счетчиков, преобразователь код - напряжение, регулятор тока, к выходу которого подключены электродвигатель и импульсный датчик частоты вращения, 5 входы схемы синхронизации подключены к выходам соответственно делителя частоты, импульсного датчика частоты вращения и генератора опорной частоты, прямой и инверсный выходы RS-триггера соединены с первыми вхо- дами соответственно первого и второго элементов И, второй вход первого элемента И подключен к выходу задат- чика частоты вращения, а выход соединен с суммирующим входом второго реверсивного счетчика, о т л и ч а -, ю щ и и с я тем, что, с целью повышения точности регулирования, в него введены третий и четвертый элементы

0

5

7

И, элемент ИЛИ с прямым и инверсным входами, цифровой регулирующий блок, включенный между выходом регистра и входом преобразователя код - напряжение , сумматор, включенный между выходом преобразователя код - напряжения и входом регулятора тока, датчик тока, выход которого подключен к второму входу сумматора, а схема синхронизации снабжена пятью выходами, подключенными соответственно к первому входу третьего элемента И, к S-входу RS-триггера, к входу установки нуля второго реверсивного счетчика, к второму входу второго элемента И и к R-входу RS-триггера, инверсный и прямой входы элемента ИЛИ соединен соответственно с R-входом RS-триггера и выходом третьего элемента И, второй вход которого подключен к прямому выходу RS-триггера, первый и второй входы четвертого элемента И соединены соответственно с выходом элемента ИЛИ и выходом разрешения переноса цифрового регулирующего блока,а выход подключен к тактирующему входу регистра, входы сложения и вычитания первого реверсивного счетчика соединены соответственно с выходом переноса второго реверсивного счетчика и выходом второго элемента И.

8

0

5

ронизации содержит тактовый распределитель в виде сдвигового регистра, тактирующий вход которого является третьим входом схемы синхронизации, четыре триггера с тактируемым, уста- - новочным и управляющим входами и пять элементов И, выходы которых являются соответствующими выходами схемы синхронизации, причем тактирующие входы первого и третьего триггеров являются соответственно первым и вторым входами схемы синхронизации, управляющие входы второго и четвертого триггеров подключены к прямым выходам первого и третьего триггеров, первые входы первого и второго элементов И подключены к прямому выходу второго триггера, первые входы третьего, четвертого и пятого элементов И подключены к прямому выходу четвертого триггера, входы установки нуля первого и третьего триггеров подключены к выходам второго и пятого эле«

5 ментов И, первый выход тактового распределителя соединен с вторыми входами первого и третьего элементов И, второй выход соединен с вторым входом второго элемента И и тактирую0 щкм входом четвертого триггера, третий выход подключен к второму входу четвертого элемента И, четвертый выход соединен с вторым входом пятого элемента И и тактирующим входом второго триггера.

0

5

| Цифровой регулятор | 1982 |

|

SU1013907A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Электропривод | 1985 |

|

SU1275726A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1989-04-30—Публикация

1987-05-19—Подача