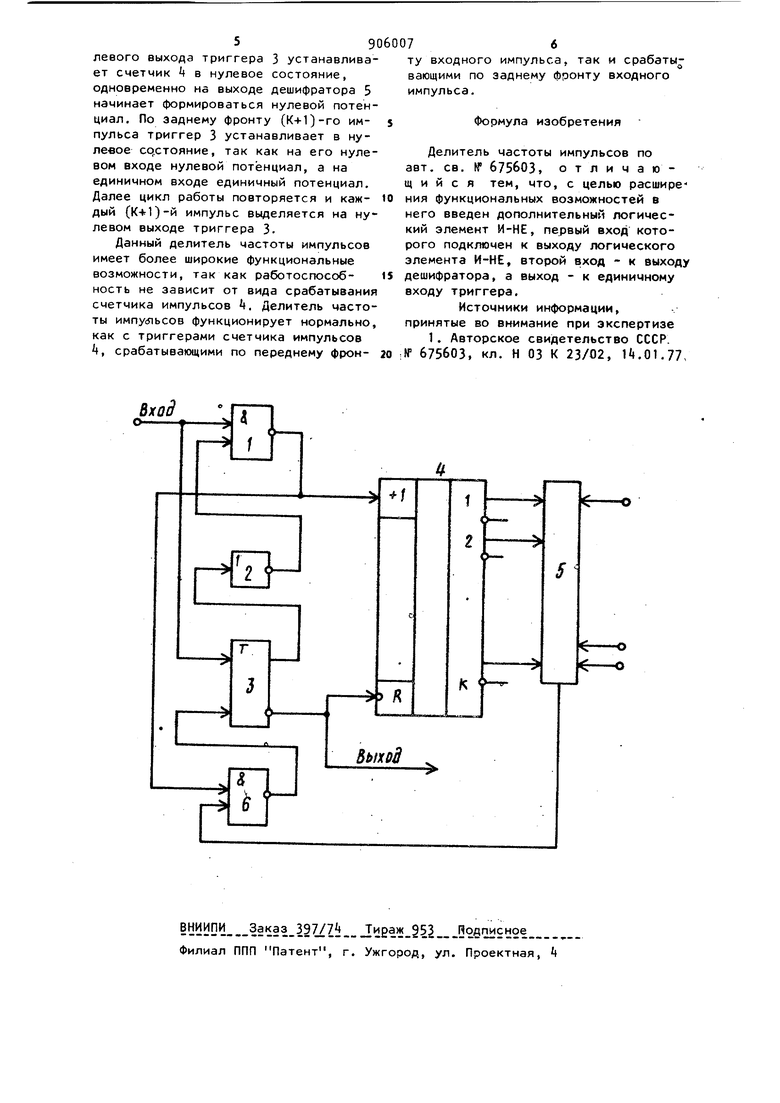

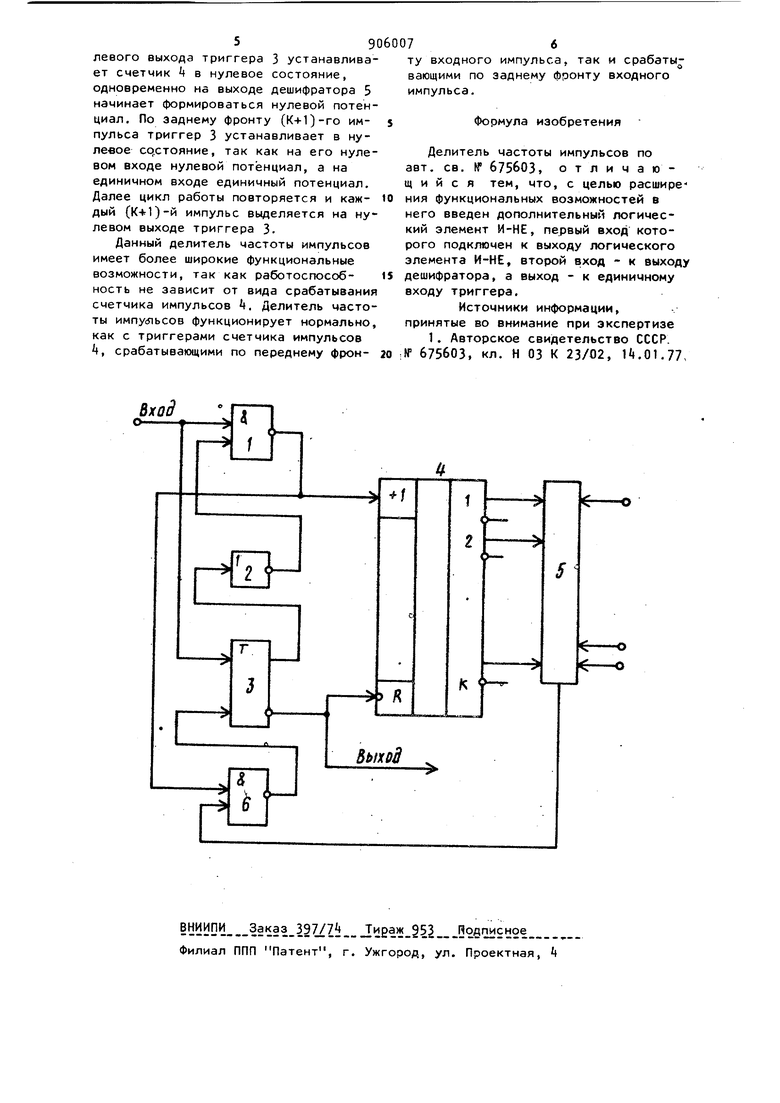

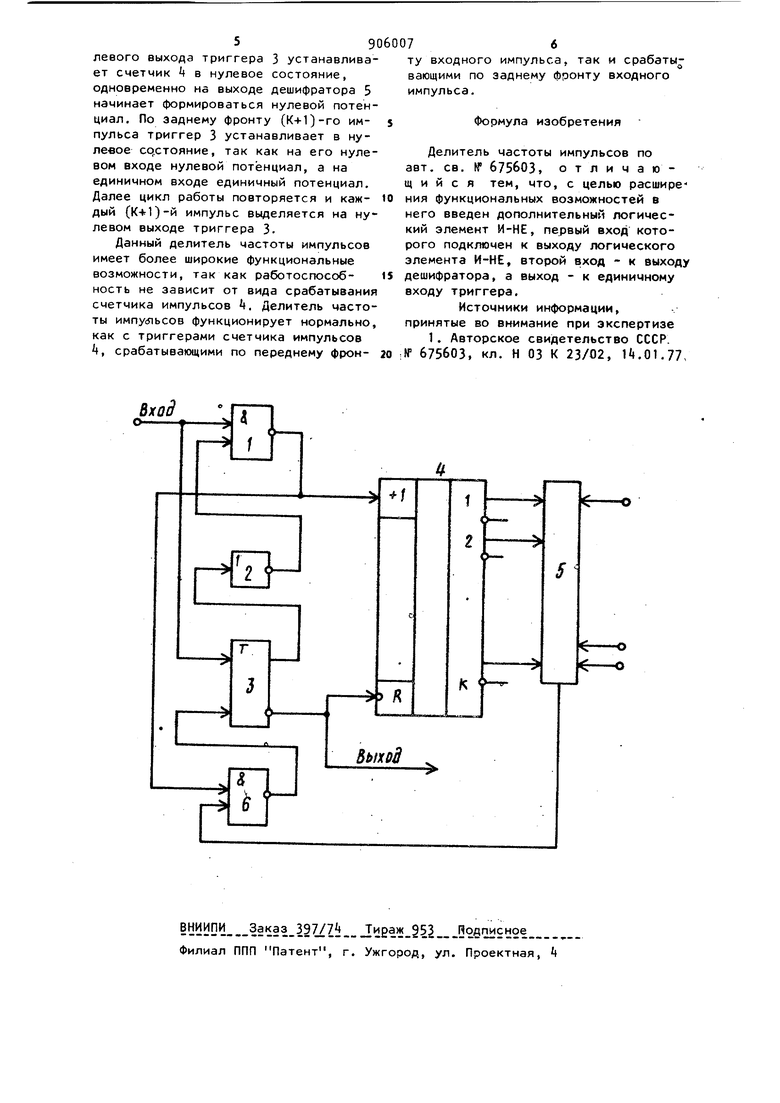

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники. По основному авт. св. W б75бОЗ известен делитель частоты импульсов, содержащий элемент И-НЕ, один вход которого соединен с входной шиной, второй вход которого через элемент НЕ соединен с единичный выходом триггера, а выход соединен с входом счет чика импульсов, выходы разрядов которого соединены с соответствующими входами дешифратора, другие входы ко торого соединены с шинами управляющих сигналов, а нулевой выход триггера соединен с входом сброса счетчика импульсов и выходной шиной делителя, при этом выход дешифратора соединен с единичным входом триггера, нулевой вход которого подключен к входной ши не П. Недостаток известного устройства ограниченные функциональные возможности, так как устройство работает толь КО В том случае, если счетчик импуль сов срабатывает по заднему фронту входного импульса. Цель изобретения - расширение функциональных возможностей. Цель достигается тем, что в делитель частоты импульсов, содержащий логический элемент И-НЕ, один вход которого соединен с входной шиной, второй вход которого через логический элемент НЕ соединен с единичным выходом триггера, а выход соединен с входом счетчика импульсов, выходы разрядов которого соединены с соответствующими входами дешифратора, другие входы которого соединены с шинами управляющих сигналов, а нулевой выход триггера соединен с входом сброса счетчика импульсов и выходной шиной делителя и нулевой вход триггера подключен к входной шине, введен дополнительный логический элемент И-НЕ, первый вход которого подключен к выходу логического элемента И-НЕ, 390 второй вход - к выходу дешифратора, а выход - к единичному входу триггера. На чертеже представлена структурная схема устройства. Устройство содержит логический элемент 1 И-НЕ, логический элемент 2 НЕ, RS триггер 3, счетчик k импульсов, дешифратор 5, дополнительный логический элемент 6 И-НЕ. Делитель частоты импульсов работает следующим образом. Счетчик Ц увеличивает свое содержимое на единицу по заднему фронту входного положительного импульса. В исходном состоянии счетчик k в нулевом состоянии, а триггер 3 устанавливается в нулевое состояние ну левым потенциалом входного сигнала, при этом на шине сброса счетчика единичный потенциал, на единичном вы ходе триггера 3 - нулевой потенциал, который поддерживает на выходе элеме та 2 единичный, разрешающий прохождение входных импульсов на вход счет чика потенциал. На входы дешифратора 5 подерется прямой код управления коэффициентом деления на единицу меньший, чем требуемый коэффициент деления частоты импульсов. Дешифратор 5 осу1чествляет сравнение кода управления коэффициентом с содержимым счетчика k. При равенстве кодов на выходе дешифратора 5 формир ётся единичный потенциал, а в случае неравенства кодов на выходе дешифратора 5 присутствует нулевой потенциал. Таким образом, каждый входной импульс, прошедший через элемент t, по заднему фронту положительного входно го импульса увеличивает содержимое счетчика на единицу и по заднему фронту входного импульса подтверждается нулевое состояние триггера 3. Пех.е прихода k-ro входного импульса по его заднему фронту содержи юе счетчика становится равным коду управления коэффициентом деления К. При этом на выходе дешифратора 5 фор мируется единичный потенциал, который поступает на второй вход элемента 6 , на первом входе которого это время - высокий потенциал, поступающий с выхода элемента 1, Передний фронт отрицательного сигнала с выхода элемента 6 устанавливает на единичном выходе триггера 3 высокий потенциал, а на нулевом выходе триггера 3 также высокий потенциал, поддерживаемый нулевым потенциалом паузы между К и (К+1) входными импульсами. Следующий, (К+1)-й входной импульс не проходит на вход счетчика , так как на втором входе элемент 1 присутствует нулевой потенциал с выхода элемента 2 во время действия (K+l)го входного импульса. По переднему фронту (К+1)-гс входного импульса триггер 3 устанавливается в единичное состояние, так как на его нулевом входе нулевой потенциал, а на единичном входе единичный потенциал. По заднему фронту (К4-1)-го импульса триггер 3 устанавливается в нулевое состояние. Состояние всех элементов устройства совпадает с исходным. Дапеё цикл работы повторяется. Счетчик k увеличивает свое содержимое на единицу по переднему фронту входного положительного импульса. Каждый входной импульс, прошедший через элемент 1 по переднему фронту положительного входного импульса, увеличивает содержимое счеучика на единицу и по заднему фронту входного импульса подтверждает нулевое состо яние триггера 3. По переднему фронту К-го входного импульса содержимое счетчика k становится равным коду управления коэффициентом деления К. При этом на выходе дешифратора 5 образуется высокий потенциал. Только по заднему фронту К-го импульса на выходе элемента 6 начинает формироваться нулевой потенциал, так как на обоих входах элемента 6 присутствуют высокие потенциалы. Передний фронт отрицательного сигнала с выхода элемента 6 устанавливает на единичном выходе триггера 3 высокий потенциал, а на нулевом выходе триггера 3 также высокий потенциал, поддерживаемый нулевым потенциалом паузы между К и (К+1)-ы« входными мпульсами. Следующий (К+1)-й входной импульс не проходит на вход счетчика , так как на втором входе элемента 1 присутствует нулевой потенциал с выхода элемента 2 во время действия (К+1)-го входного импульса. По переднему фронту ()-го входного импульса триггер 3 устанавливается в единичное состояние, так как на его цходе нулевой потенциал, а на единичном входе единичный потенциал. Нулевой сигнал с нулевого выхода триггера 3 устанавливает счетчик t в нулевое состояние, одновременно на выходе дешифратора 5 начинает формироваться нулевой потенциал. По заднему фронту (К+1)-го импульса триггер 3 устанавливает в нулевое со стояние, так как на его нулевом входе нулевой потенциал, а на единичном входе единичный потенциал. Далее цикл работы повторяется и каждый (К+1)-й импульс выделяется на нулевом выходе триггера 3. Данный делитель частоты импульсов имеет более широкие функциональные возможности, так как работоспособность не зависит от вида срабатывания счетчика импульсов . Делитель частоты импу яьсов функционирует нормально как с триггерами счетчика импульсов Ц, срабатывающими по переднему фрон97 ту входного импульса, так и срабатывающими по заднему фронту входного импульса. Формула изобретения Делитель частоты импульсов по авт. св. № 675603, отличающийся тем, что, с целью расширения функциональных возможностей в него введен дополнительный логический элемент И-НЕ, первый вход которого подключен к выходу логического элемента И-НЕ, второй вход - к выходу дешифратора, а выход - к единичному входу триггера. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР. ;№ 675603, кл. Н 03 К 23/02, И.01.77,

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты импульсов | 1977 |

|

SU675603A1 |

| Формирователь трапецеидальных импульсов | 1982 |

|

SU1077045A1 |

| Делитель частоты с переменным коэффициентом деления | 1990 |

|

SU1721824A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU875642A1 |

| Устройство для определения автокорреляционной функции | 1984 |

|

SU1363254A1 |

| Удлинитель импульсов | 1978 |

|

SU744944A1 |

| Устройство для определения положения числа на числовой оси | 1984 |

|

SU1231497A1 |

| Логический пробник | 1986 |

|

SU1352420A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU970632A1 |

| Распределитель импульсов | 1978 |

|

SU771873A1 |

Вхй

Авторы

Даты

1982-02-15—Публикация

1980-05-20—Подача