(54) ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСрВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов | 1982 |

|

SU1045400A1 |

| Делитель частоты импульсов | 1980 |

|

SU906007A2 |

| Устройство для управления шаговым двигателем с дроблением шага | 1982 |

|

SU1061230A1 |

| Управляемый делитель частоты | 1984 |

|

SU1238234A1 |

| Делитель частоты следования импульсов | 1978 |

|

SU764135A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU884152A1 |

| Формирователь трапецеидальных импульсов | 1982 |

|

SU1077045A1 |

| Делитель частоты | 1983 |

|

SU1112571A1 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2175167C1 |

| Устройство для формирования импульсных последовательностей | 1988 |

|

SU1596438A1 |

- -J Изобретение относится к импульсной технике. Известен делитель частоты импульсов, содержащий генератор импульсов, подключенный на вход счетчика импульсов С общей шиной: обнуления, выполненного. на триггерах, выходы каждого йз которых соеринены с триггерами разрядными входами дешифратора скважности, другие разрядные входы управления которого соединены с вьпсодами блока упра ления, допрлнител 5эный триггер с рйэде- льными входами и , ко торого подключены к точкам соедйнёшя входов дешифратора скважности С триггер ными разрядными входами в разрядвь1Мй входамиуправления при этом взмхОгзУь дешифратора скважности подключены к одному из раздельных входов Дополни ельного дешифратора, а выводы дополнительного дешифратора к другому раз дельному входу дополнительного триггера и. обшей- шине обнуления счетчика вд. однако ЭТОТ делитель обладает недостаточным быстродействием. . Наиболее близким по технической сущности к изобретению является делитель частот1з1, содержащий логический элемент И-НБ, один вход которого соединен с входной шиной, второй вход которого через логический элемент НЕ средйнен с единичным выходом триггера, а выход соединен с входом счетчика импульсов, выходы разрядов которого соединены с соответствующими входами дешифратора, другие входы которого coeflia- нень с дайнами упр)авляющих сигналов, а нулевой выход триггера соединен с входом сброса счетчика и выходной шиной делителя . Недостатком делителя является его сложность. Целью, изобретения - упрощение делителя, Это достигается тем, в делителе частоты, содержащем логический элемент И«41Е, ОДИН вход которого сое-

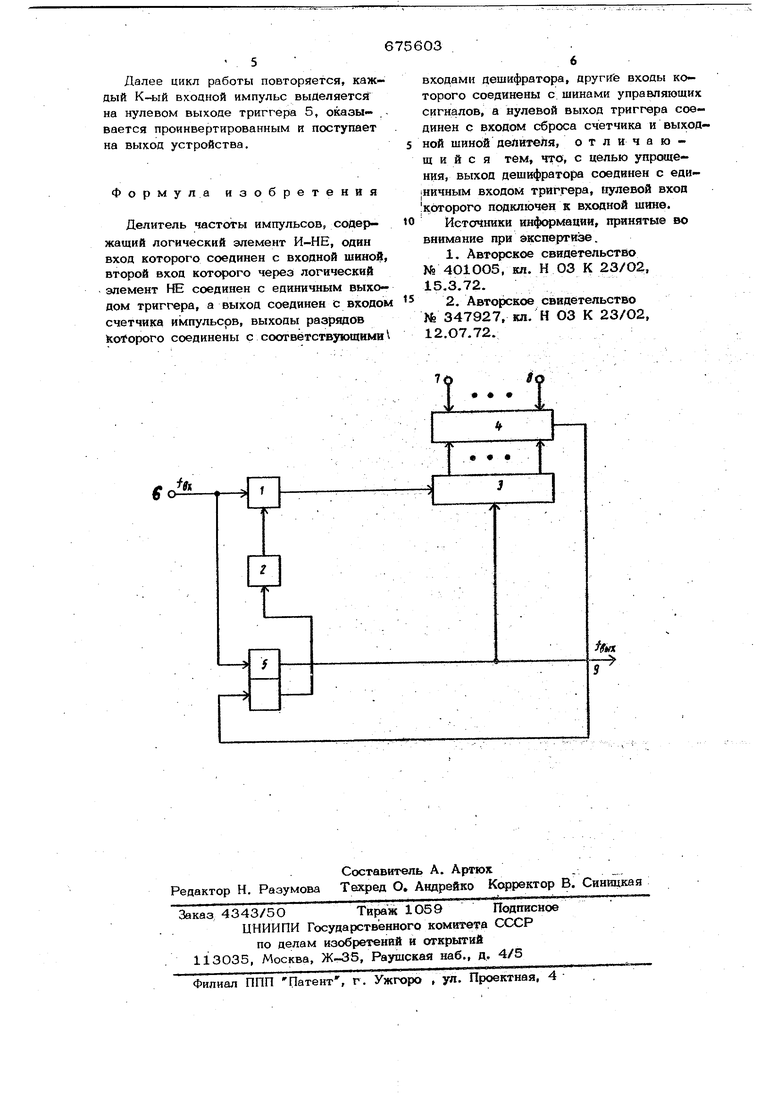

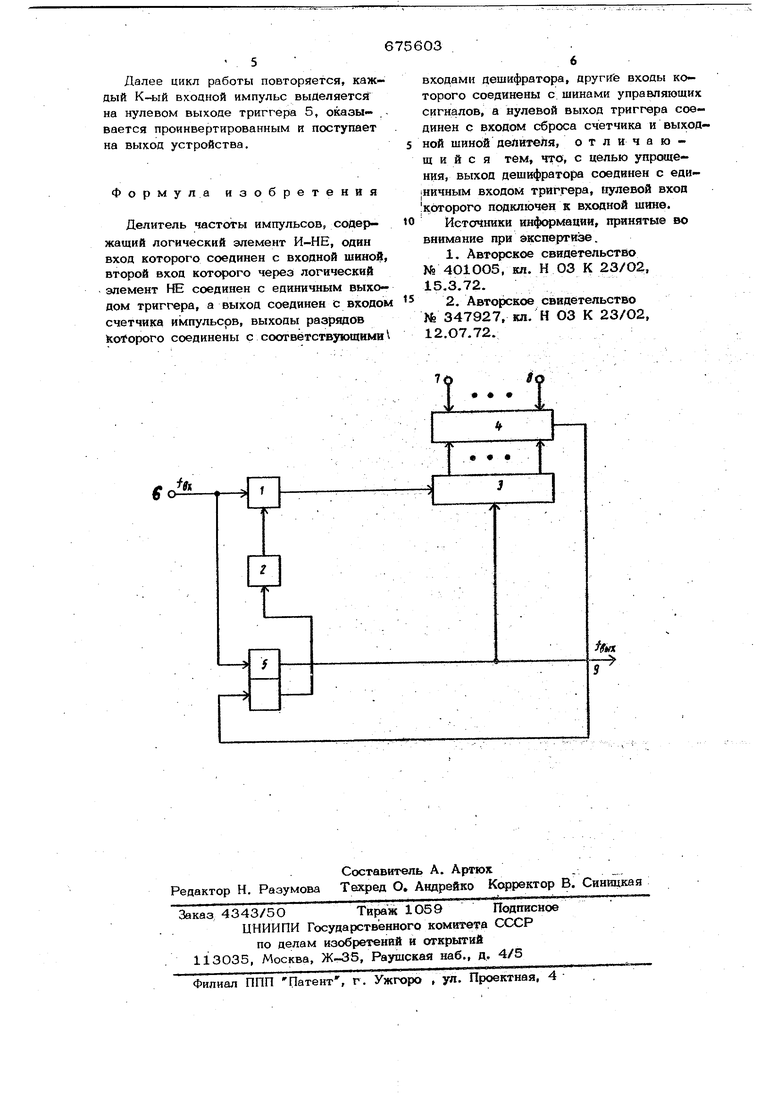

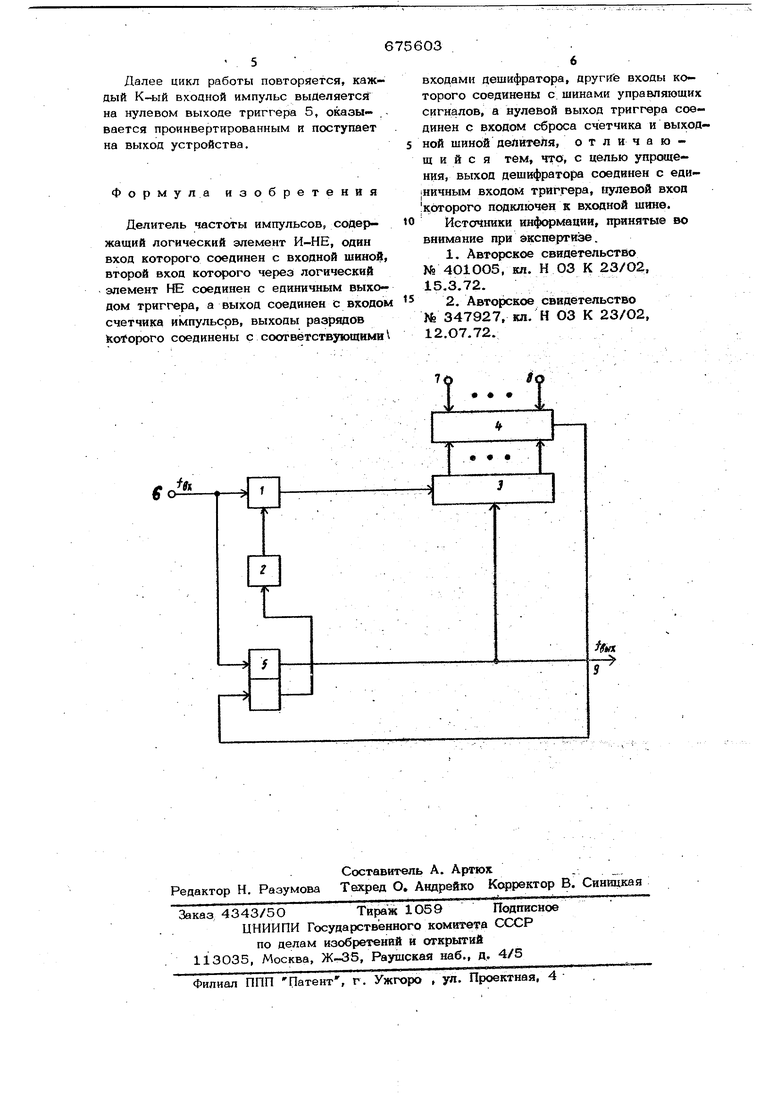

675603 аинен с входной шиной, второй вход которого через логический элемент НЕ lioe fieftt; едЙ1ГиВДё11Й Ж1х6дом рй гге-; ра, а выхбд соединен с входом счетчика импульсов, выходы разр Ргдбв которого соединены с соответствующими входами дешифрато эа, другие вкоды которого соединены с шинами управляющих сигналов, а нулевой выход триггера соединен с входом сброса счетчика и выходной шиной делителя, выход дешифратора соедине;н с единичным входом триггера, нулевой вход которого под:й1ючен к входной шине. На чертеже дана структурная электри ческая схема йелителя. Он содержит логический элемент И-НЕ 1, логический элемент НЕ 2,j:4eT чйк импульсов 3,, дешифратор 47Триг- г-ёр 5. Входной сигнал подан на входную шину 6, на шины 7, 8 подан сигнал управл ния, выходной сигнал снимается с выходной шины 9. Принцип работы делителя заключается в следующем. Рассмотрим работу; делителя для коэф фициента деления К равного 15 в десятичной системесчисления (К - ISjQ ), при этом разрядность бчетчика импульсов 3 равна четырем. В исходном состоянии на счетчик 3 записывается код (10ОО), а триггер 5 устанавливается в нулевое состояние нуле вйм потенциал ом входного сигнала, при этом на шине сброса счётчика импульсов 3 будет присутствовать бездействующий единичный потенциал, а на вхо де .логического элемента И-ЛЕ 1 с помощью логического элемента ,НЕ 2 единичный потенциал, разрешающий прохождение положительных (единичного уровня) импульсов входной частоты { I g I ) на счетный Вход счетчика импуль сов 3. На шины управления 7, 8 подает ся прямой код управления коэффициентом деления (К - ISjp - lillg), Дешифра тор 4 осуществляет сравнение кода управления коэ4)фициента деления с кодом счетчика. При равенстве ко дов на выходе дешифратора 4 возникает нулевой потенциал, а в случае неравенства кодов на вь1ходе дешифратора 4 присутствует единичный потенциал. Каждый импульс входной частоты ( { rf), прошедший логический элемент И-НЕ 1, по заднему фронту увеличивает код счетчика импульсов 3 на единицу. По заднему фронту импульса подтверж- дается нулевое состояние триггера 5 нулевым потенциалом паузы между положительными импульсами входной частоты. После прихода (К -1)-го импульса о его заднему фронту код смотчика импульов 3 станет равным коду управления коэффииента деления К, так как исходноа состояние счетчика импульсов задается рав- ным 1000. Приэтомна выходе дешифратора 4 фо рмируется нулевой потенциал, передний фронт которого устанавливает на единичном выходе триггера 5 единичный потенциал. На выходе логи- . ческого элемента И-НЕ 1 возникает нулевой потенциал, запрещаюший прохождение импульсов входной частоты на счетный вход счетчика импульсов 3. На нулевом выходе триггера 5 будет присутствовать единичный потенциал, поддерживаемый нулевым потенциалом паузы между (К - 1) -ым и импульсами входной частоты. Следующий К-й импульс не проходит на счетный вход счетчика импульсов 3, Потому, что логич:еский элемент И-НЕ 1 заблокирован. По переднему фронту К-го импульса триггер 5 установится в единичное состояние, так как на его нулевом входе возникает бездействующий единичный потенциал тела импульса, а на единичном входе присутствует нулевой потенциал с выхода дешифратора 4. Сигнал нулевого потенциала с нулевого выхода Триггера 5 по шине сбрсса записывает в счетчике импульсов 3 код 1ООО. При этом возникает неравенство кода управления коэффициента деления и кода счетчика 3 и на вь1ходе дешифратора 4 формируется единичный потен- циал. По заднему фронту К-го импульса триггер 5 устанавливается в нулевое состояние, так как на его нулевом входе возникает нулевой потенциал паузы между К-ыми (К + 1)-ым импульсами входной частоты, а на единичном Bjfoae присутсТвует бездействующий единичный потенциал с выхода дешифра- тора 4. При этом логический элемент И-НЕ 1 деблокируется. , Таким образом триггер 5 находится в в единичном состоянии в течении времени .действия К-го импульса и на его нулевом входе формируется отрицательный (нулевого уровня) импульс, длительность которого равна длительности импульсов входной частоты.

Далее цикл работы повторяется, каждый К-ый входной импульс выделяется на нулевом выходе триггера 5, окаэы вается проинвертированным и поступает на выход устройства.

Формула изобретения

Делитель частоты импульсов, содержащий логический элемент И-НЕ, один вход которого соединен с входной шиной, второй вход которого через логически|Я1 элемент НЕ соединен с единичным выходом триггера, а выход соединен с входом счетчика импульсов, выходы разрядов kotoporo соединены с соответствующими

.ft

входами дешифратора, другие входы которого соединены с шинами управляющих сигналов, а нулевой выход триггера соединен с входом сброса счетчика и выходной шиной деПитейя, отличающийся тем, что, с целью упрощения, выход дешифратора соединен с еди;ничным входом триггера, нулевой вход I которого подключен к входной шине.

Источники информации, принятые во внимание при эксперти;зе.

«

fftOi

Авторы

Даты

1979-07-25—Публикация

1977-01-14—Подача