1

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных и информационно-измерительных устройствах и системах для вычисления или формирования функций синуса и косинуса .

Известно устройство, обеспечивающее кусочно-ступенчатую аппроксимацию воспроизводимой функции. Устройство характеризуется сравнительно простой реализацией и высоким быстродействием 1 .

Недостатком известного устройства является очень низкая точность.

Наиболее близким по технической сущности к предлагаемому является устройство,, содержащее входной регистр, разделенный на группу старших и первую и вторую подгруппы младших разрядов, три блока памяти, два блока умножения,, сумматор и выходной регистр, при этом выходы группы старших разрядов входного регистра соединены с адресными входами первого и второго блоков памяти, выходы первой подгруппы младших разрядов входного регистра соединены с адресными входами третьего блока памяти, информационные выходы которого подсоединены к первым входам второго блока умножения, вторые входы которого соединены с информационными выходами первого блока памяти, а выходы - со вторыми входами сумматора, первые входы которого подсоединены к выходам первого блока умножения, соединенного первыми входами с информационными выходами второго блока памяти, а вторыми - с выходами первой и второй подгруппы младших разрядов входного регистра, выходы сумматора соединены со входами выходного регистра устройства.

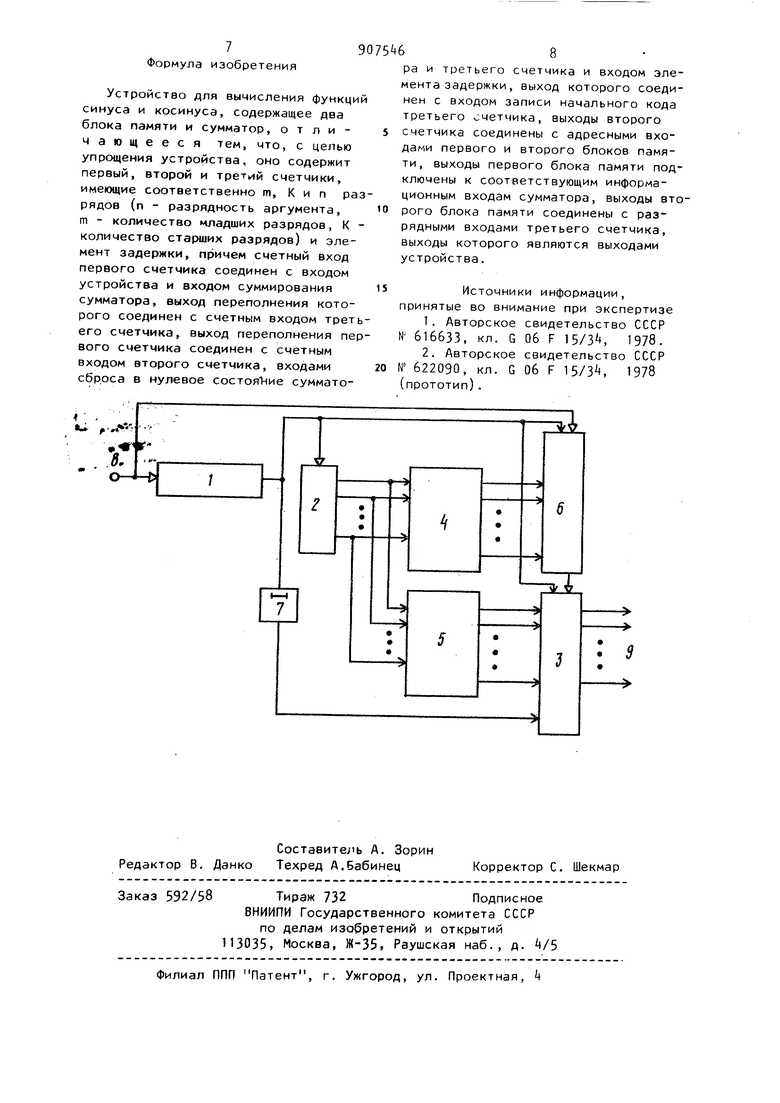

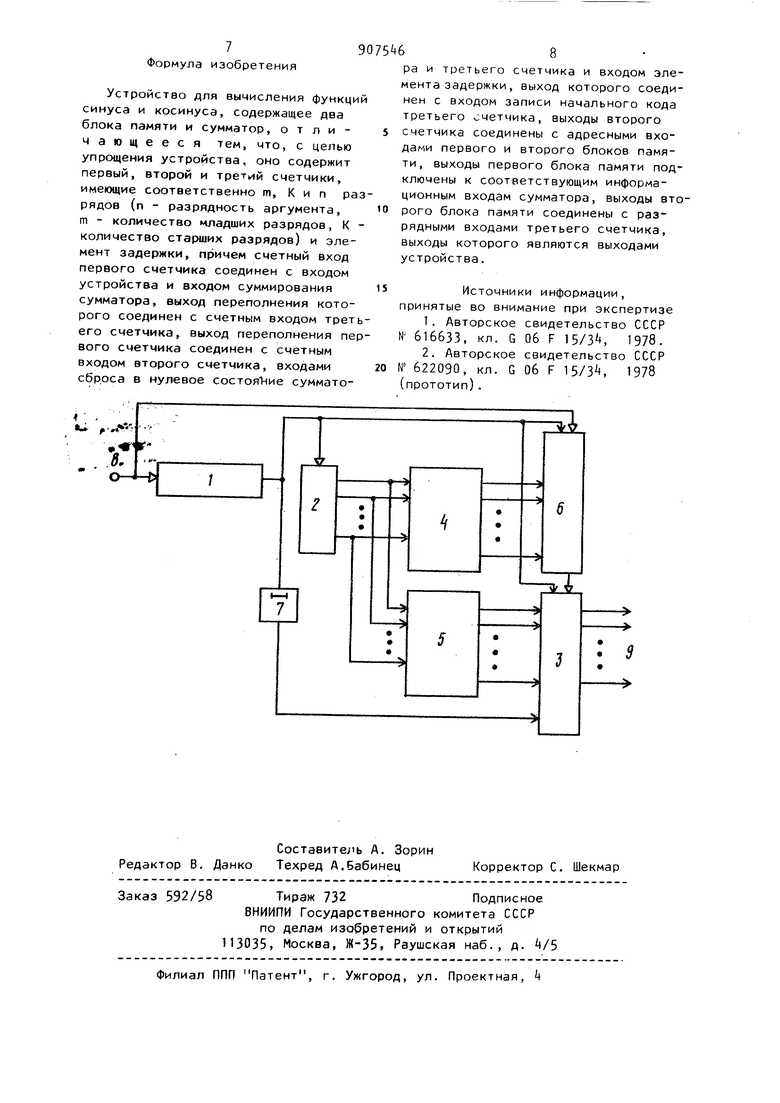

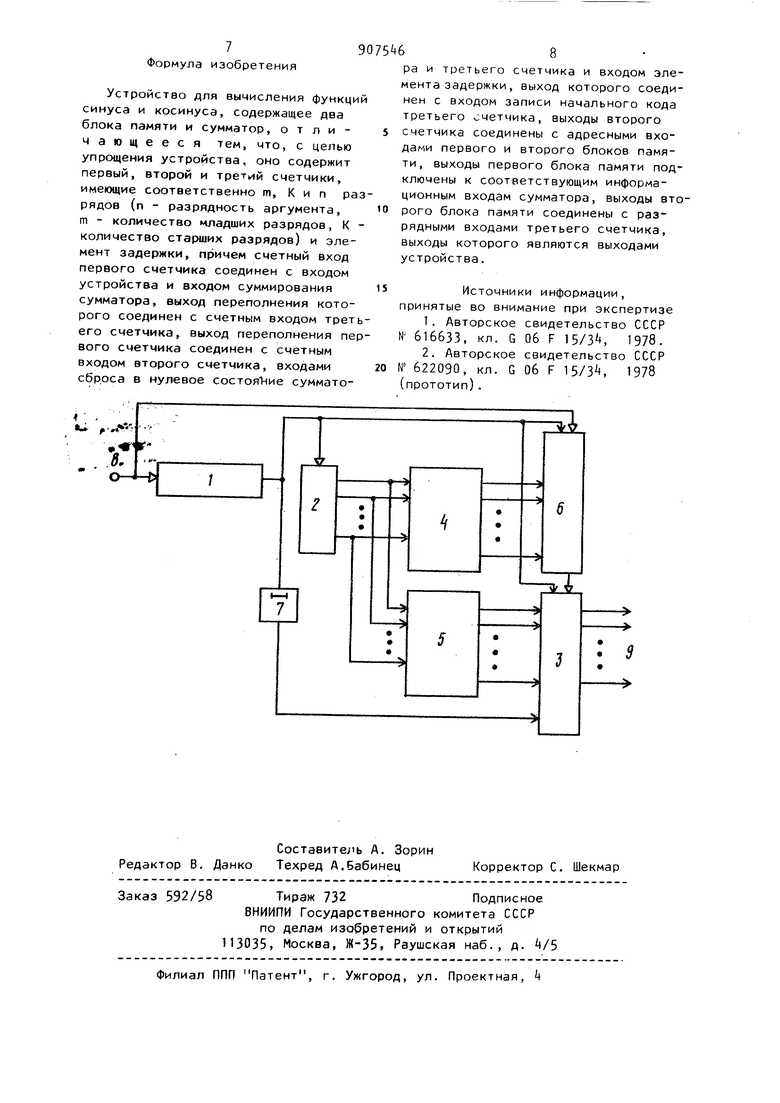

В данном устройстве двоично-кодированный аргумент х представляется в виде X Xjj+ux, где XQ - содержимое группы старших, а й содержимое группы младших разрядов. В свою очередь Дх представляется в виде , где Дх и uxj - содержи мое первой и второй подгрупп младших разрядов соответственно. В основу алгоритма работы устрой ства положены соотношения S inx sinxp- cosAx + + cos; - sinux COSX COSXQ- СОЗДХ -sinxosinux; .которые при некоторых достаточно ма лых значениях Дх могут быть заменен приближенными равенствами S inx sinXj со5Дх/(+Лх-cosXf, (2 COSX COSX СОЗЛХ -Д. х- sinxQ. Если обозначить п - общее число разрядов аргумента, К - число стар ших разрядов. С- число разрядов в первой подгруппе младших разрядов, то методическая погрешность замены вь;;1ажений (1) на выражения (2) не . превышает значения (2v2kte/ +±2 Варьируя значениями К и Р при задан ном п можно вывести данную погрешность за пределы разрядной сетки. |Так, например, при задании аргумент X, изменяющегося в пределах О 1,0 рад., в качестве К и следует взять соответственно: для п 8 К ,дляп 12 k и Е 2, для п 1б , и т.д. При вычислении функции sinx в первом и втором блоках памяти хра нятся значения S I nxQ и вычислении cosx - значения cosx (-sinXp) соответственно. В третьем блоке памяти в обоих случаях записываются значения cosAxf . Суммарный объем памяти равен 2 информа ционных слоев, содержащих не менее п разрядов 2. Недостатком данного устройства является его сложность, обусловленная наличием трех блоков памяти и двух блоков умножения с большим чис лом многоразрядных информационных связей. Если для построения блоков умножения использовать традиционные многотактные схемотехнические решения на основе регистров сдвига и су маторов, то помимо достаточно больш аппаратурных затрат это приводит к заметному снижению быстродействия устройства. В принципе вычисление м жет быть осуществлено и без существенных временных задержек, если в 4 качестве блоков умножения использовать матричные или табличные умножители. Но такое решение даже при малых п требует очень больших аппаратурных затрат, которые при больших п увеличиваются в такой степени, что техническая реализация такого рода умножителей в настоящее время является практически нецелесообразной. Цель изобретения - упрощение конструкции устройства. Поставленная цель достигается тем, что устройство, содержащее два блока памяти и сумматор, содержит первый, второй и третий счетчики, имеющие соответственно т, К и п разрядов (п разрядность аргумента, m - количество младших разрядов, К - количество старших разрядов) и элемент задержки, причем счетный вход первого счетчика соединен с входом устройства и входом суммирования сумматора, выход переполнения которого соединен с счетным входом третьего счетчика, выход переполнения первого счетчика соединен с счетным входом второго счетчика, входами сброса в нулевое состояние сумматора и третьего счет- чика и входом элемента задержки, выход которого соединен с входом записи начального кода третьего счетчика, выходы второго счетчика соединены с адресными входами первого и второго блоков памяти, выходы первого блока памяти подключены к соответствующим информационным входам сумматора, выходы второго блока памяти соединены с разрядными входами третьего счетчика, выходы которого являются выходами устройства. На чертеже представлена структурная схема устройства. Устройство содержит счетчики 1, 2 и 3, имеющие соответственно т, К и п разрядов, блоки k и S памяти, п-разрядный накапливающий сумматор 6, элемент 7 задержки, вход 8 и выходы 9В основу алгоритма работы устройства положены следующие соображения. Если аргумент х, выраженный в радианах, представить в виде , то, как. это уже отмечалось, справедивы равенства (1) и (1 ). При малых U.X С05ДХ« 1 (3) sinAxfiux,(3 ) и равенства (1) и (Т) могут быть записаны в виде si пх ;s inxpf cosx.ux, (4) cosx icosxp-si nxQ-ux- (Ц Как показывает анализ, при коди ровании аргумента х в диапазоне О 1,0 рад. п-раз ядным кодом или в диапазоне О - (п+1)-разрядным кодом абсолютная погрешность обеих приближенных равенств 3) и (З ) становится меньше , т.е. уходит за пределы разрядной сетки, при взятии в качестве Л.х m - младших разрядов аргумента. При этом для вычисления фуикци синуса и косинуса вместо соот ношений (1) и (1) могут быть исполь зованы соотношения (k) и (Ц ) . Если результат вычислений также представляется п-разрядным кодом и при этом необходимо обеспечить результирующую погрешность, не превышающую погрешности дискретности, то значения sinxp и cosx, используемые при вычислении, должны содержать не менее п разрядов. Эти значения можно хранить в блоках памяти, управ ляемых по адресным входам кодом XQ. Число разрядов К, отводимых для кодирования XQ, равно Л при работе в диапазоне 0-1,0 рад или ( 1) при работе в диапазоне О - - . Информационная емкость каждого из блоков па мяти составляет в общем случае или 2 п-раз рядных слов соответственно. Устройство работает следующим образом. При вычислении функции синуса в исходном положении все разряды счетчиков 1 , 2 и 3 и накапливающего сумматора 6 устанавливаются в нулевое состояние. Счетчик 3 работает на сло жение. При вычислении функции косинуса все разряды счетчиков 1 и 2 и накапливающего сумматора 6 устанавливаются в нулевое, а все разрядь счетчика 3 в единичное состояние. Счетчик 3 работает на вычитание. При вычислении функции синуса в блоках k и 5 памяти хранятся значения cosx и slnXfj соответственно, а при вычислении функции косинуса - наоборот. Аргумент X в числоимпульсном коде подается на вход 8 устройства и далее на счетный вход счетчика 1 и так тирующий вход суммирования накапливающего сумматора 6. Последний нарастающим итогом суммирует коды, сни маемые с выходов блока 4 памяти. Сигналы переполнения сумматора 6 поступают на счетный вход счетчика 3. При каждом переполнении т-разрядного счетчика 1, осуществляющего подсчет дх, к содержимому К-разрядного счетчика 2, формирующего очередные значения , добавляется единица-, п-разрядные сумматор 6 и счетчик 3 сбрасываются в нулевое состояние, а через некоторое время, зависящее от динамических характеристик счетчиков 2 и 3 и блока 5 памяти и определяемое элементом 7 задержки, в счетчик 3 заносится п-разрядный код очередного значения выходного слова блока 5 памяти. Тем самым в соответствии со структурой выражений () и (k.) в счетчике 3 формируются п-разрядные значения sinx или COSX соответственно. Для перехода от вычисления функции синуса к вычислению функции косинуса достаточно изменить исходное состояние и направление счета счетчика 3, а также поменять местзми блоки 4 и 5 памяти. Суммарный информационный объем блоков памяти устройства при вычислении функций синуса и косинуса в диапазоне аргумента 0-1,0 рад. и разрядности п, равной 8, 12 и 16 составляет соответственно 256, 1536 и 8192 бит. В предлагаемом устройстве, в отличие от .известного, за счет применения более простого алгоритма вычислений и использования числоимпульсной формы представления аргумента вместо трех блоков памяти содержатся только два и исключены два блока умножения двоично-кодированных чисел. Это существенно упрощает структуру устройства и сокращает аппаратурные затраты, а также позволяет осуществлять вычисление в темпе поступления входной информации. Последнее свойство открывает широкие возможности применения предлагаемого устройства для преобразования в реальном времени число- и частотноимпульсной информации, имеющей широкое распространение в информационноизмерительной и вычислительной технике, а также позволяет использовать его для построения цифровых функциональных генераторов соответствующих функций.

7 Формула изобретения

Устройство для вычисления функций синуса и косинуса, содержащее два блока памяти и сумматор, о т л и чающееся тем, что, с целью упрощения устройства, оно содержит первый, второй и третий счетчики, имеющие соответственно т, К и п разрядов (п - разрядность аргумента, m - количество младших разрядов, К количество старших разрядов) и элемент задержки, причем счетный вход первого сметчика соединен с входом устройства и входом суммирования сумматора, выход переполнения которого соединен с счетным входом третьего счетчика, выход переполнения первого счетчика соединен с счетным входом второго счетчика, входами сброса в нулевое состояТчие сумматоf .

«U- , д,

O-MS

8

ра и третьего счетчика и входом элемента задержки , выход которого соединен с входом записи начального кода третьего счетчика, выходы второго счетчика соединены с адресными входами первого и второго блоков памяти, выходы первого блока памяти подключены к соответствующим информационным входам сумматора, выходы второго блока памяти соединены с разрядными входами третьего счетчика, выходы которого являются выходами устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР W 616633, кл. G 06 F 15/3, 1978.

2.Авторское свидетельство СССР N 622090, кл. G 06 F ТЗ/З, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1262486A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1339555A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1388855A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Устройство для воспроизведения тригонометрических функций синуса и косинуса | 1989 |

|

SU1661800A1 |

| Устройство для вычисления спектра уолша функций синуса и косинуса | 1979 |

|

SU864291A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Устройство для вычисления функций синуса и косинуса | 1984 |

|

SU1205140A1 |

| Устройство для вычисления тригонометрических функций | 1987 |

|

SU1427362A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

Авторы

Даты

1982-02-23—Публикация

1980-07-24—Подача