ю

11А

Изобретение относится к вьгчисли- тельной технике и может быть использовано в специализированных вычислителях, обладающих высоким быстродействием и высокой достоверностью результатов.

Цель изобретения - повышение достоверности результата за счет самоисправления единичных сбоев шины вход- кого аргумента и повьппение быстродействия за счет уменьшения числа итерации.

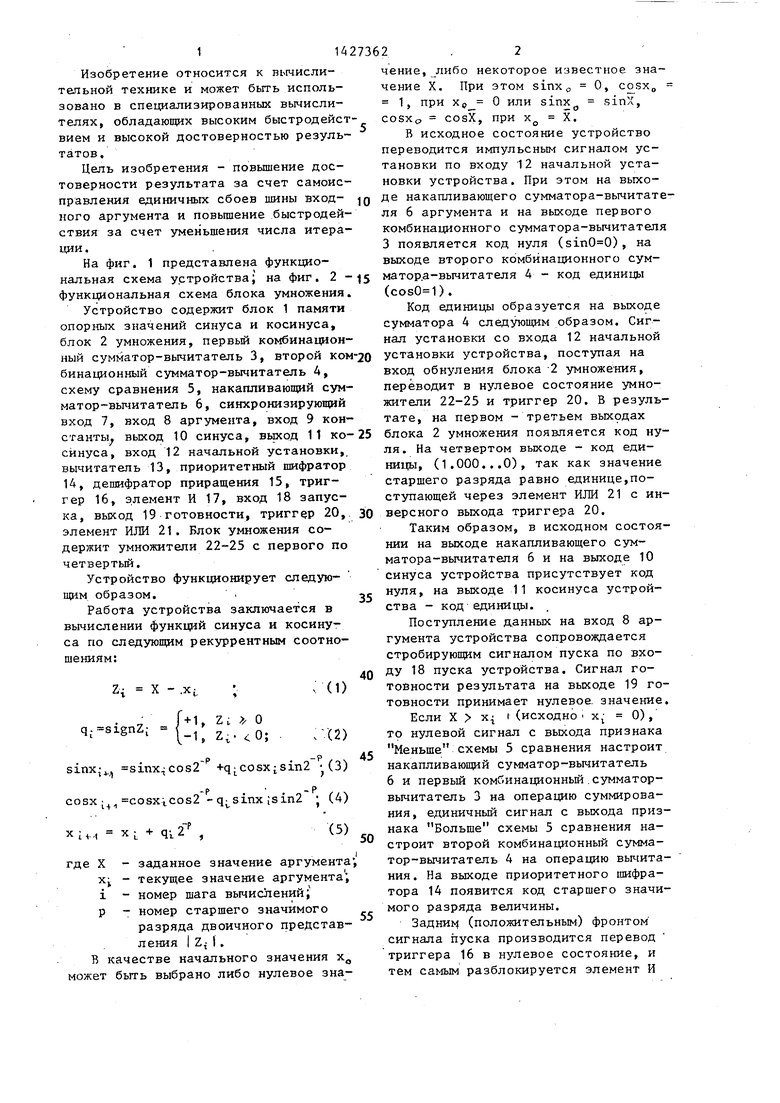

На фиг. 1 представлена функцио

чение, либо некоторое известное значение X. При этом sinXo О,

1, при Хр О или sinx sinX, cosxo cosX, при Хд X.

В исходное состояние устройство переводится импульсным сигналом установки по входу 12 начальной установки устройства. При этом на выходе накапливающего сумматора-вычитате- ля 6 аргумента и на выходе первого комбинационного сумматора-вычитателя 3 появляется код нуля (), на выходе второго комбинационного сум

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1339555A1 |

| Синусно-косинусный кодовый преобразователь | 1972 |

|

SU464006A1 |

| Цифровой генератор гармонических функций | 1983 |

|

SU1164686A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Устройство для вычисления функций синуса и косинуса | 1980 |

|

SU907546A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1388855A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях, обладающих высоким быстродействием и высокой достоверностью результатов. Целью изобретения является повышение достоверности результата за счет самоисправления единичных сбоев аргумента и повьшение быстродействия за счет уменьшения числа итераций. Устройство содержит блок 1 памяти опорных значений синуса и косинуса, блок 2 умножения, первый комбинационный сумматор-вычитатель 3, второй комбинационный сумматор-вычитатель 4, схему сравнения 5, накапливающий сумматор-вычитатель 6, синхронизирующий вход 7, вход 8 аргумента, вход 9 константы, выход 10 синуса, выход 11 косинуса, вход. 12 начальной установки, вычитатель 13, приоритетный шифратор 14, дешифратор приращения 15, триггер 16, элемент И 17, вход 18 запуска, вькод 19 готовности, триггер 20, элемент ИЛИ 21. 2 ил. «е (/)

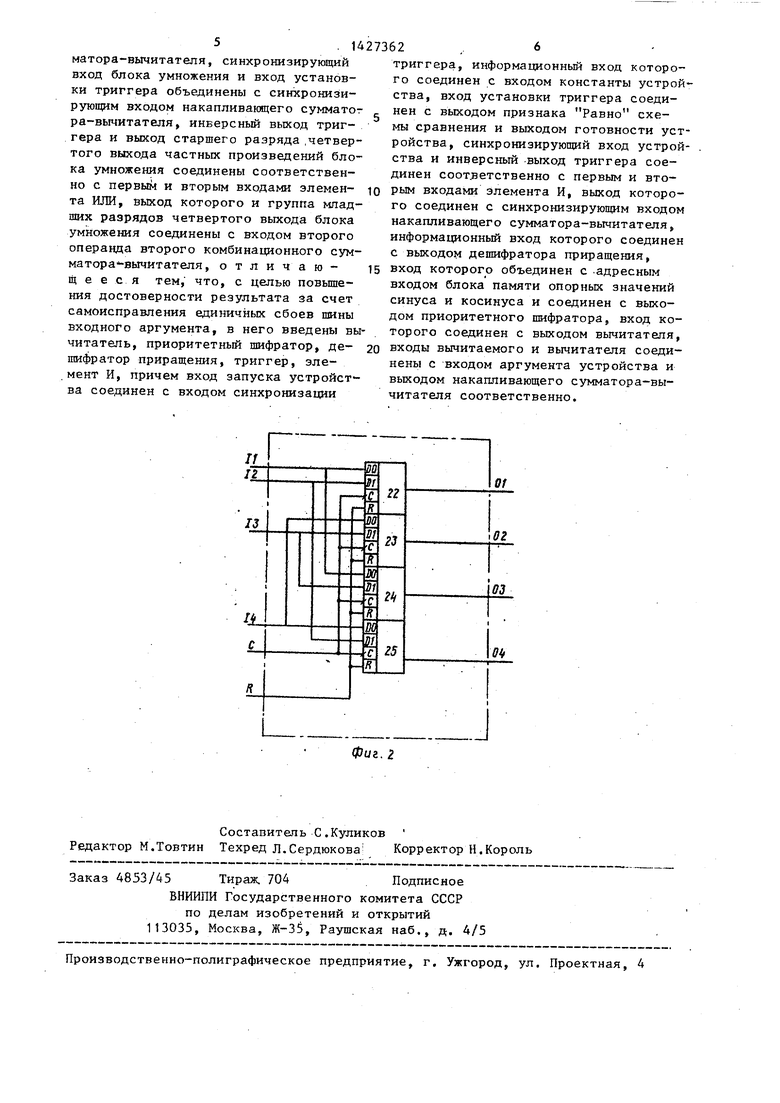

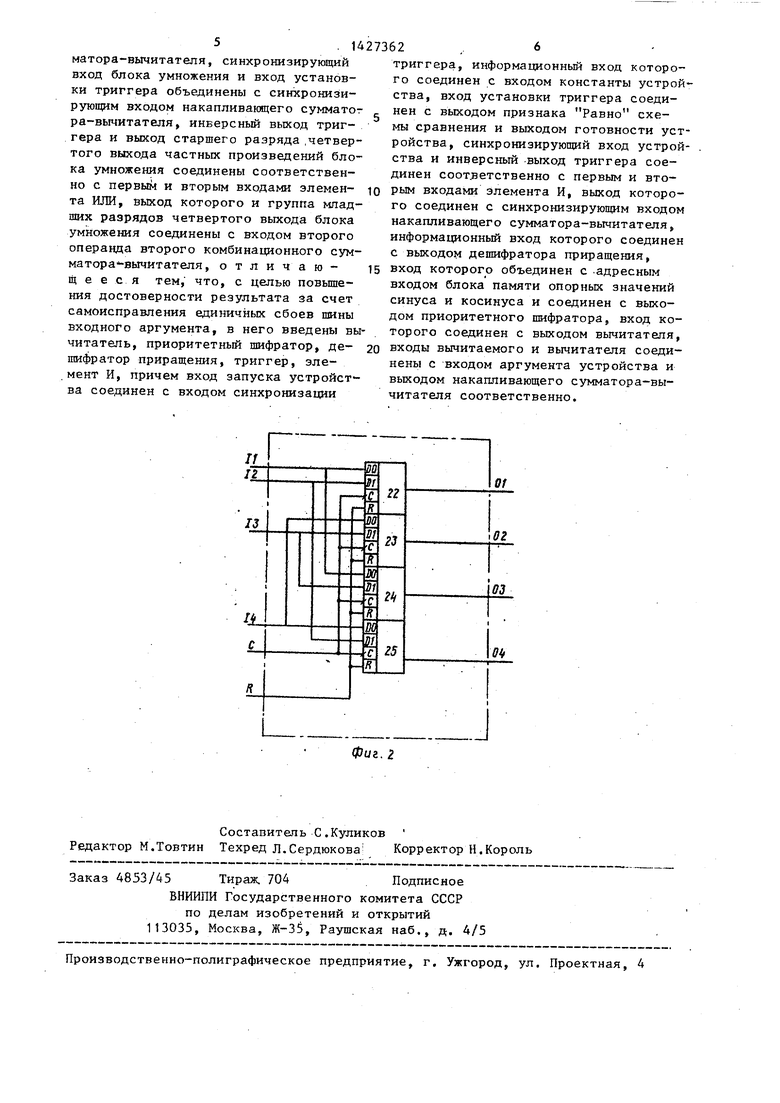

нальная схема устройства; на фиг. 2 матора-вычитателя 4 - код единип)

функциональная схема блока умножения. Устройство содержит блок 1 памяти onopiaix значений синуса и косинуса, блок 2 умножения, первый комбинацией-

ный сумматор-вычитатель 3, второй ком-20 установки устройства, поступая на бинационный сумматор-вычитатель 4, схему сравнения 5, накапливающий сум- матор-вьмитатель 6, синхронизирующий вход 7, вход 8 аргумента, вход 9 кон- станты выход 10 синуса, выход 11 ко-25 синуса, вход 12 начальной установки,. вычитатель 13, приоритетный шифратор 14, дешифратор приращения 15, триггер 16, элемент И 17, вход 18 запуска, выход 19 готовности, триггер 20,. элемент ИЛИ 21. Блок умножения содержит умножители 22-25 с первого по четвертый.

Устройство функционирует следующим образом.

Работа устройства закпю(чается в вычислении функций синуса и косинуса по следующим рекуррентным соотношениям:

30

35

вход обнуления блока-2 умноже ния, переводит в нулевое состояние умно жители 22-25 и триггер 20. В резул тате, на первом - третьем выходах блока 2 умножения появляется код н ля. На четвертом выходе - код единицы, (1.000...0), так как значени старшего разряда равно единице,поступающей через элемент ИЛИ 21 с и версного выхода триггера 20.

Таким образом, в исходном состо нии на выходе накапливающего сумматора-вычитателя 6 и на выходе 10 синуса устройства присутствует код нуля, на выходе 11 косинуса устрой ства - код единицы.

Поступление данных на вход 8 ар гумента устройства сопровождается стробирующим сигналом пуска по вхо ду 18 пуска устройства. Сигнал готовности результата на выходе 19 г товности принимает нулевое, значени

Zi X ,Х;

(1)

-1,

Zc Z:

/ О 0;

. - (2)

,-р

р

sinx|,, sinx cos2 +q; cosxisin2 ,(3)

-р - р

COSX- cosxicos2 - ;sin2 j (4)

t ,

X + q-, 2

rP

(5)

где X - заданное значение аргумента; Xj - текущее значение аргумента ; номер шага вычислений;

1

Р

номер старшего значимого разряда двоичного представления I Z{ i.

В качестве начального значения х может быть выбрано либо нулевое зна().

Код единицы образуется на выходе сумматора 4 следуюш 1м образом. Сигнал установки со входа 12 начальной

установки устройства, поступая на

вход обнуления блока-2 умноже ния, переводит в нулевое состояние умножители 22-25 и триггер 20. В результате, на первом - третьем выходах блока 2 умножения появляется код нуля. На четвертом выходе - код единицы, (1.000...0), так как значение старшего разряда равно единице,поступающей через элемент ИЛИ 21 с инверсного выхода триггера 20.

Таким образом, в исходном состоянии на выходе накапливающего сумматора-вычитателя 6 и на выходе 10 синуса устройства присутствует код нуля, на выходе 11 косинуса устройства - код единицы.

Поступление данных на вход 8 аргумента устройства сопровождается стробирующим сигналом пуска по входу 18 пуска устройства. Сигнал готовности результата на выходе 19 готовности принимает нулевое, значение.

Если X x.i t (исходно I х{ 0),

то нулевой сигнал с выхода признака Меньше схемы 5 сравнения настроит накапливающий сумматор-вычитатель 6 и первый комбинационный.сумматор- вычитатель 3 на операцию суммирования, единичный сигнал с выхода признака Больше схемы 3 сравнения настроит второй комбинационный сумматор-вычитатель 4 на операцию вычитания. На выходе приоритетного шифратора 14 появится код старшего значимого разряда величины.

Задним (положительным) фронтом сигнала пуска производится перевод триггера 16 в нулевое состояние, и тем самым разблокируется элемент И

17 для пропускания импульсов с син- хронизируютего входа 7 устройства. По фронту каждого тактового импульса осуществляется увеличение (уменьшение) содержимого накапливающего сумматора-вычитателя 6 на вели р

чину 2 , где р - номер старшего значимого разряда величины. Одновременно осуществляется вычисление значе- НИИ sinx и по соотношениям (3), (4) с помощью блока 2 умножения и комбинационных сумматоров 3.4.

После очередного тактового импуль- 15 приведший к искажению входного аргуса в накапливающем сумматоре-вычкта- теле 6 появится код, совпадающий со значением аргумента. В этом случае проявляющийся единичный сигнал на выходе признака Равно схемы 5 срав- 20 нения установит триггер 16 в единичное состояние, блокируя тем самым элемент И 17 дпя прохождения тактовых импульсов с синхронизирующего входа 7 устройства. Данный единичный сигнал поступает также на выход 19 готовности устройства, свидетельствуя об окончании вычислительного процесса. Вычисленные значения sinX и cosX находятся на выходах 10, 11 устройства соответственно.

25

30

В ряде случаев необходимо вычислять значение функций синуса и косинуса для некоторого набора аргументов, являющихся близкими одно другому числами, т.е. необходимо организовать работу устройства в динамическом резкиме для малых приращений аргумента. В этом случае сигнал установки на вход 12 устройства не выдается. В накапливающем сумматоре-вы- читателе 6 содержится предьщущее значение аргумента, на выходах 10,

11 устройства присутствуют вычислен- 45 ого комбинационного сумматора-вычитателя, первый и второй выходы памяти опорных значений синуса и косинуса и выход второго комбинационного сумматора-вычитателя соединены с

и запуска устройства оно будет функ- 50 входами операндов блока- умножения с

первого по четвертый соответственно, первый и второй выходы частных произведений блока умножения соединены с входами соответственно первого и

будет появляться код старшего значи- gg второго операндов первого комбинационного сумматора-вычитателя, третий выход частных произведений блока умножения соединен с входом первого операнда второго комбинационного сумные значения функций синуса и косинуса для этого аргумента.. Прсле поступления на вход 8 аргумента устройства нового значения аргумента X

ционировать также, как было рассмотрено выше, за исключением того, что на выходе приоритетного шифратора 14 в каждом такте работы устройства

мого разряда числа Z JX -Х|, а не числа х . При значениях Х и X, близких одно другому такой режим работы устройства позволяет существенно

уменьшить время вычисления функций синуса и косинуса.

При наличии единичных сбоев на входе аргумента значение аргумента X может измениться. На следующем шаге

изменится и значение sinx , (cosx ) -f -- -.

на величину 2 ние X.

отслеживая изменеТак как к началу очередного такта значение восстановится, то на этом шаге восстановится и прежнее значение xj . Таким образом единичньй сбой,

ментаг не повлечет в общем случае искажения результата вычислений.

Формула изобретения

Устройство для вычисления тригонометрических функций, содержащее блок памяти опорных значений синуса и косинуса, два комбинационных сумматора5 вычитателя, схему сравнения, накапливаюший сумматор-вычитатель, блок ум- . ножения, триггер и элемент HIBi, причем входы первого и второго операндов схемы сравнения соединены с входом

0 аргумента устройства и выходом накапливающего сумматора-вычитателя соответственно, выход признака еньше схемы сравнения соединен с входами выбора режима накапливающего суммаg тора-вычитателя и первого комбинационного сумматора-вычитателя, вход вьЛгора режима второго комбинационного сумматор а-вычитателя соединен с выходом признака Больше схемы срав0 нения, вход начальной установки устройства соединен с входом сброса накапливающего сумматора-вычитателя, . входом обнуления блока умножения и с входом сброса триггера, вькод перматора-вычитателя, синхронизирующий вход блока умножения и вход установки триггера объединены с синхронизирующим входом накапливающего сумматог ра-вычитателя, инверсный выход триггера и выход старшего разряда .четвертого выхода частных произведений блока умножения соединены соответственно с первым и вторым входами злемен- та ИЛИ, выход которого и группа младших разрядов четвертого выхода блока умножения соединены с входом второго операнда второго комбинационного сум- матора -вычитателя, отличаю- щ е е с я тем, что, с целью повьше- ния достоверности результата за счет самоисправления единичных сбоев шины входного аргумента, в него введены вы читатель, приоритетный шифратор, де- шифратор прираш;ения, триггер, зле- мент И, причем вход запуска устройст ва соединен с входом синхронизации

триггера, информационный вход которого соединен с входом константы устройства, вход установки триггера соединен с выходом признака Равно схемы сравнения и выходом готовности устройства, синхронизирующий вход устройства и инверсный выход триггера соединен соот.ветственно с первым и вторым входами элемента И, выход которого соединен с синхронизирующим входом накапливающего сумматора-вычитателя, информационный вход которого соединен с выходом дешифратора приращения, вход которого объединен с адресным входом блока памяти опорных значений синуса и косинуса и соединен с выходом приоритетного шифратора, вход которого соединен с выходом вычитателя, входы вычитаемого и вычитателя соединены с входом аргумента устройства и выходом накапливающего сумматора-вычитателя соответственно.

Фиг. 2

| Устройство для вычисления функций синуса и косинуса | 1983 |

|

SU1140116A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отображения объем-НОй иНфОРМАции HA эКРАНЕ элЕКТРОН-НОлучЕВОй ТРубКи | 1979 |

|

SU832552A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-30—Публикация

1987-03-27—Подача