1339

ретения - расширение функциональных возможностей преобразователя за счет определения значений функций sinX и cosX в интервале 0-360 , В си- нусно-косинусньш преобразователь, содержащий регистр 2 прямого кода, регистр 11 нуля, элемент ИЛИ 6, сумматоры 10 и 12, регистр 13, группу 14 элементов И, блок 9 синхронизации, сумматор 4 дополнительного кода и блок 5 памяти, дополнительно введены (п+2)-й и (п+3)-й разряды регистра 2 прямого кода, преобразователь 1 углового перемещения в код, блок 7 вычисления знака, сумматор 8 по модулю два и преобразователь 3 прямого кода в обратный. В результате анализа (п+)-го и (п+3)-го разрядов

1

Изобретение относится к вычислительной технике и может быть использовано в цифроаналоговых вычислительных устройствах, например в навигационных вычислительных устройствах,

работающих с датчиками, в которых угл вьщаются в цифровом коде с преобразователей любого типа, например, фотоэлектрических преобразователей.

Цель изобретения - расширение функциональных возможностей преобразователя за счет определения значений функций sinX и cosX в интервале от О до 360°..

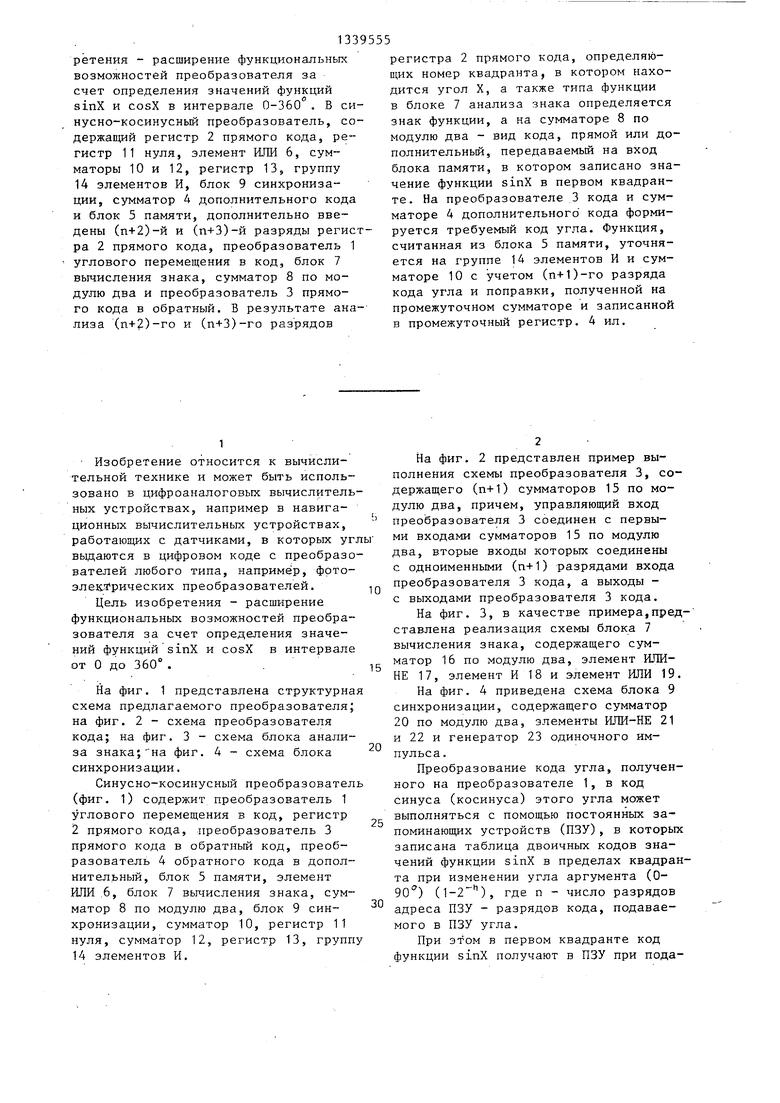

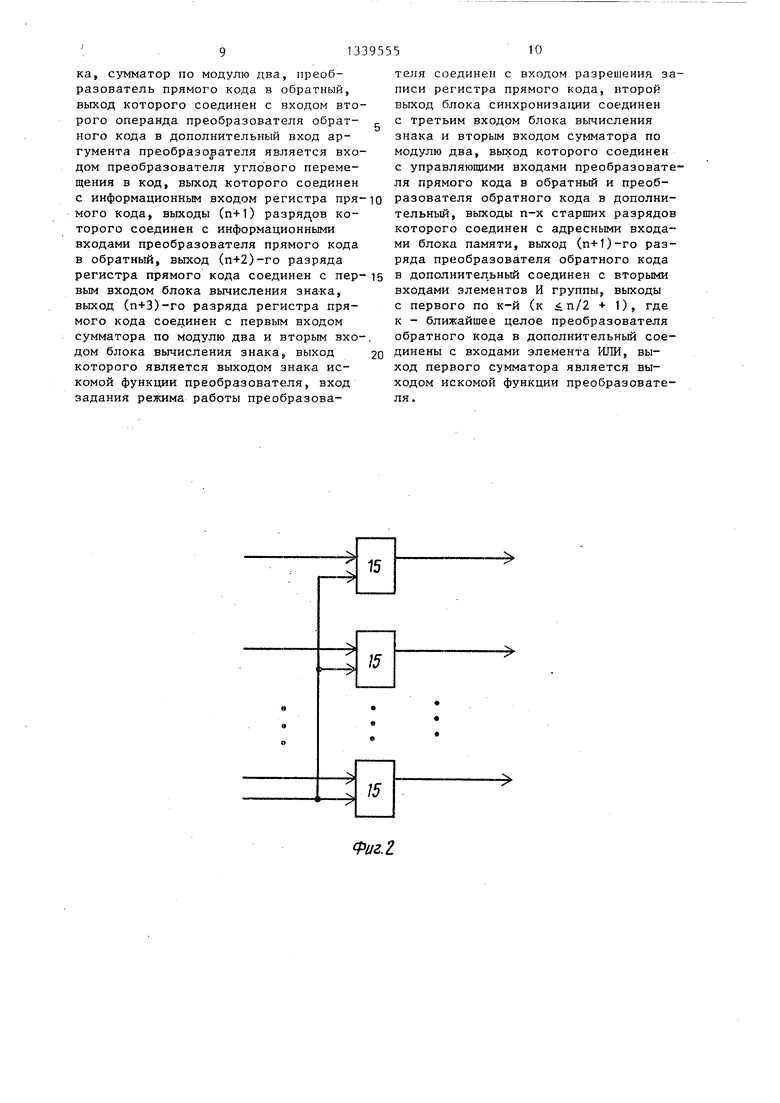

На фиг. 1 представлена структурная схема предлагаемого преобразователя; на фиг. 2 - схема преобразователя кода; на фиг. 3 - схема блока анализа знака; на фиг. 4 - схема блока синхронизации.

Синусно-косинусный преобразователь (фиг. 1) содержит преобразователь 1 углового перемещения в код, регистр 2 прямого кода, преобразователь 3 прямого кода в обратный код, преобразователь 4 обратного кода в дополнительный, блок 5 памяти, элемент ИЛИ .6, блок 7 вычисления знака, сумматор 8 по модулю два, блок 9 син- хронизации, сумматор 10, регистр 11 нуля, сумматор 12, регистр 13, группу 14 элементов И.

регистра 2 прямого кода, определяю- п;их номер квадранта, в котором находится угол X, а также типа функции в блоке 7 анализа знака определяется знак функции, а на сумматоре 8 по модулю два - вид кода, прямой или дополнительный, передаваемый на вход блока памяти, в котором записано значение функции sinX в первом квадранте. На преобразователе 3 кода и сумматоре 4 дополнительного кода формируется требуемый код угла. Функция, считанная из блока 5 памяти, уточняется на группе 14 элементов И и сумматоре 10 с учетом (п+1)-го разряда кода угла и поправки, полученной на промежуточном сумматоре и записанной в промежуточный регистр. 4 ил.

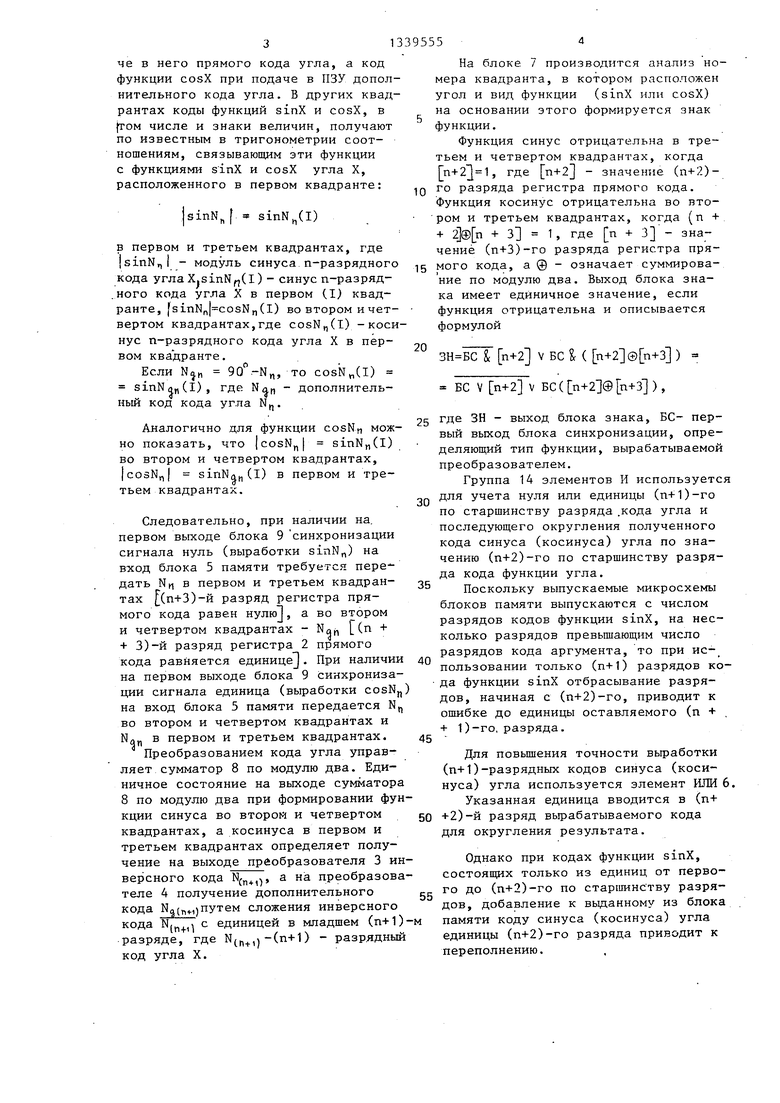

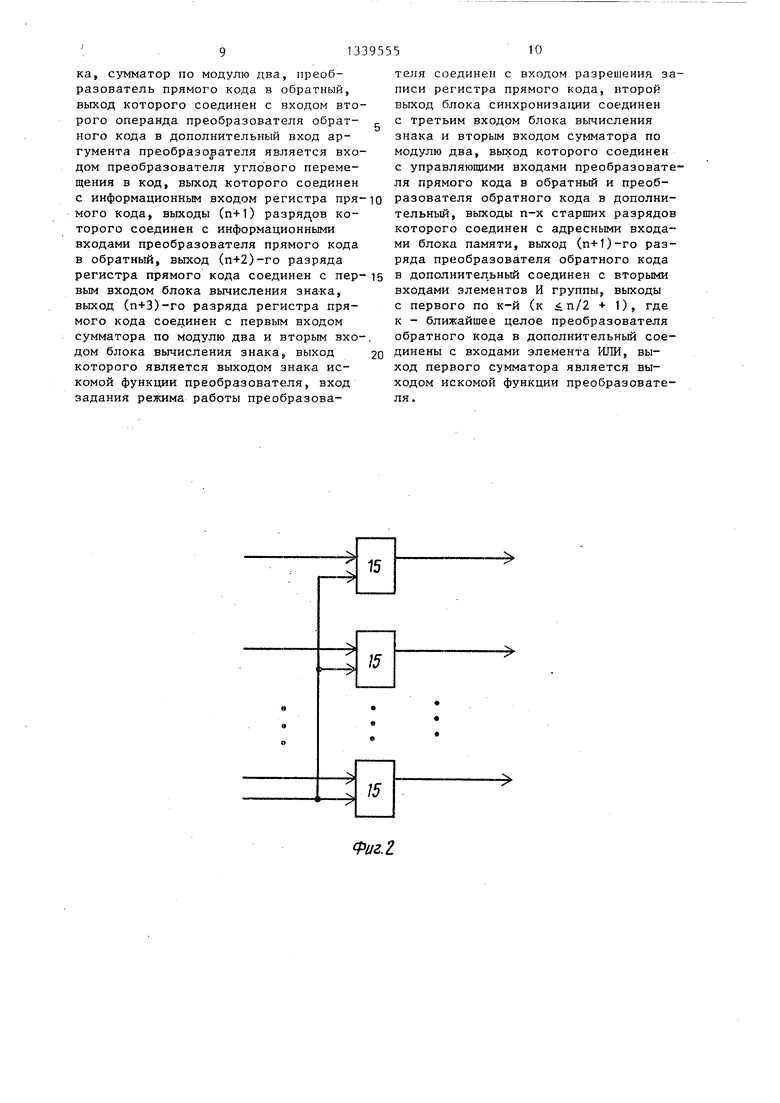

На фиг. 2 представлен пример выполнения схемы преобразователя 3, содержащего (п+1) сумматоров 15 по модулю два, причем, управляющий вход преобразователя 3 соединен с первыми входами сумматоров 15 по модулю два, вторые входы которых соединены с одноименными (п+1) разрядами входа преобразователя 3 кода, а выходы - с выходами преобразователя 3 кода.

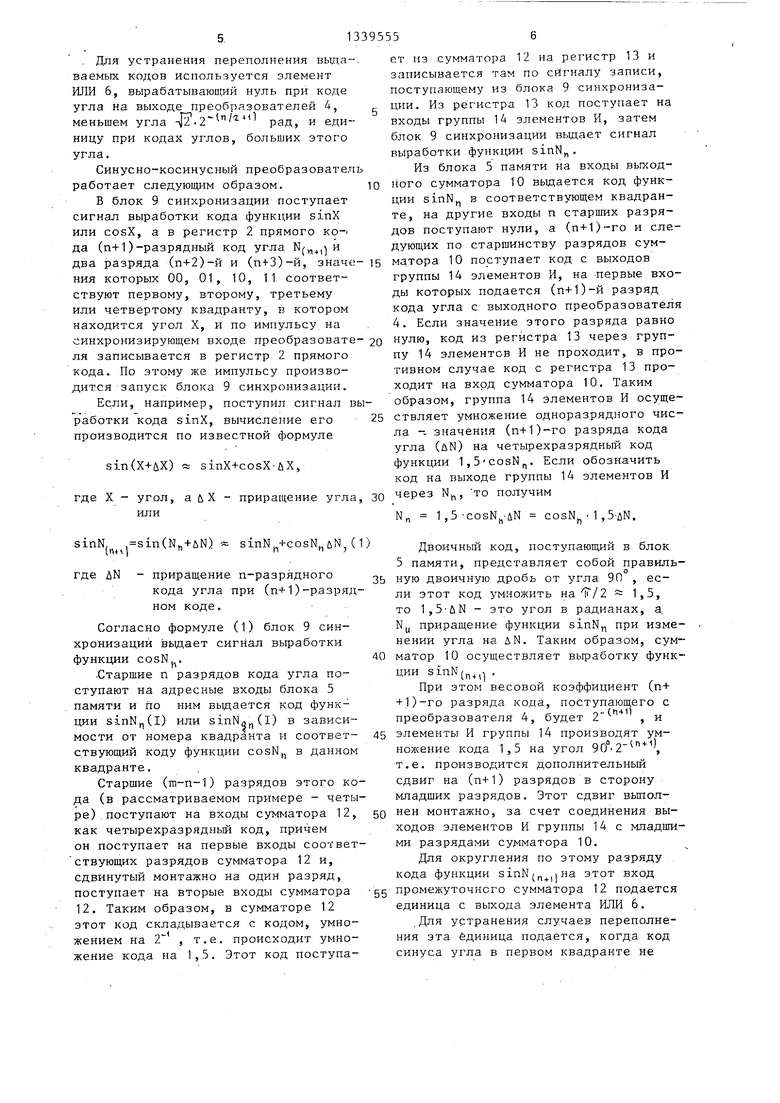

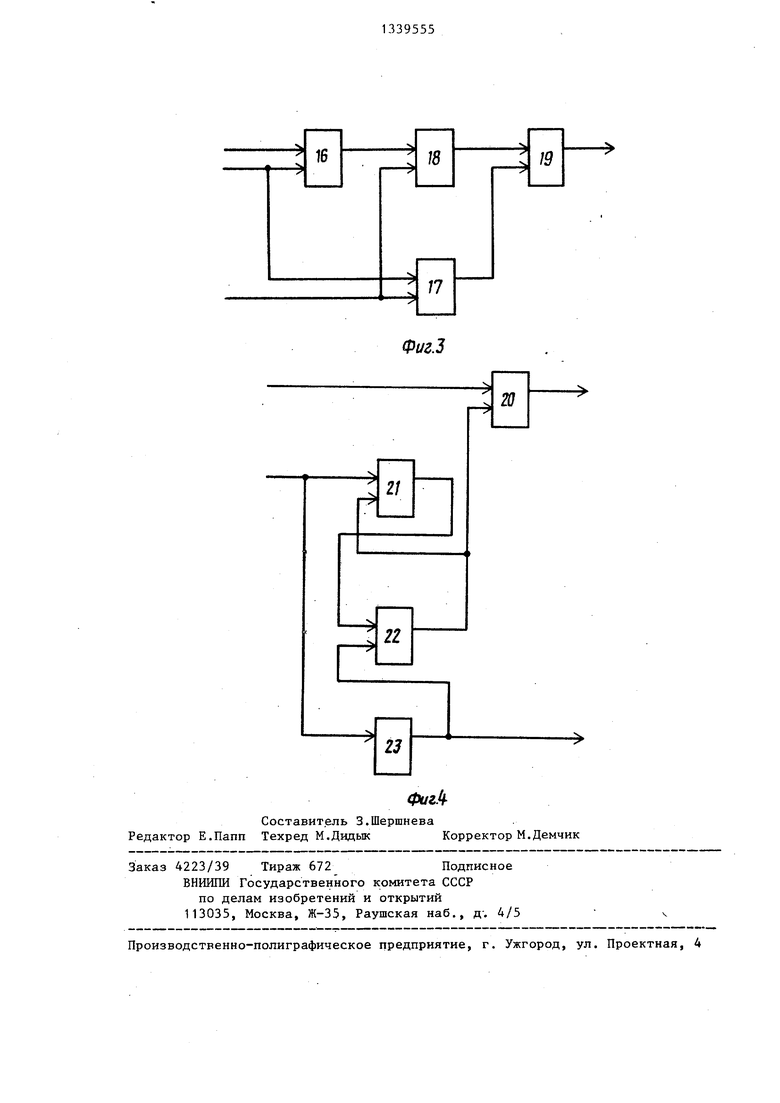

На фиг. 3, в качестве примера,представлена реализация схемы блока 7 вычисления знака, содержащего сумматор 16 по модулю два, элемент ИЛИ- НЕ 17, элемент И 18 и элемент ИЛИ 19.

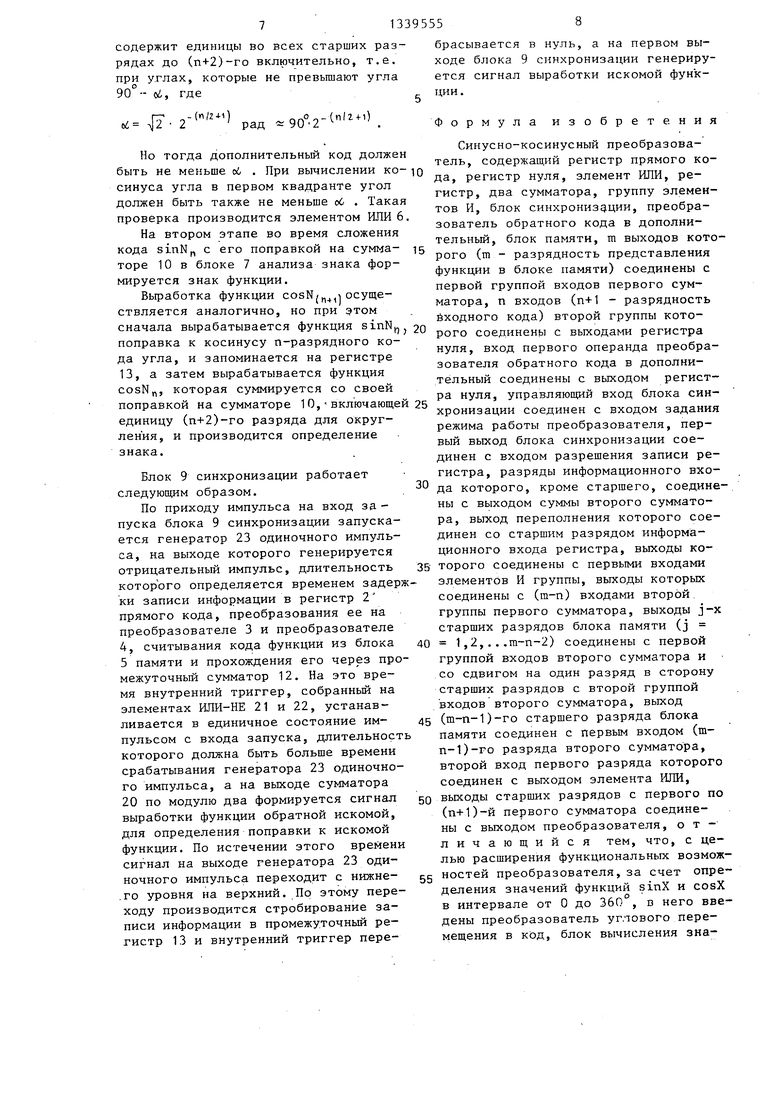

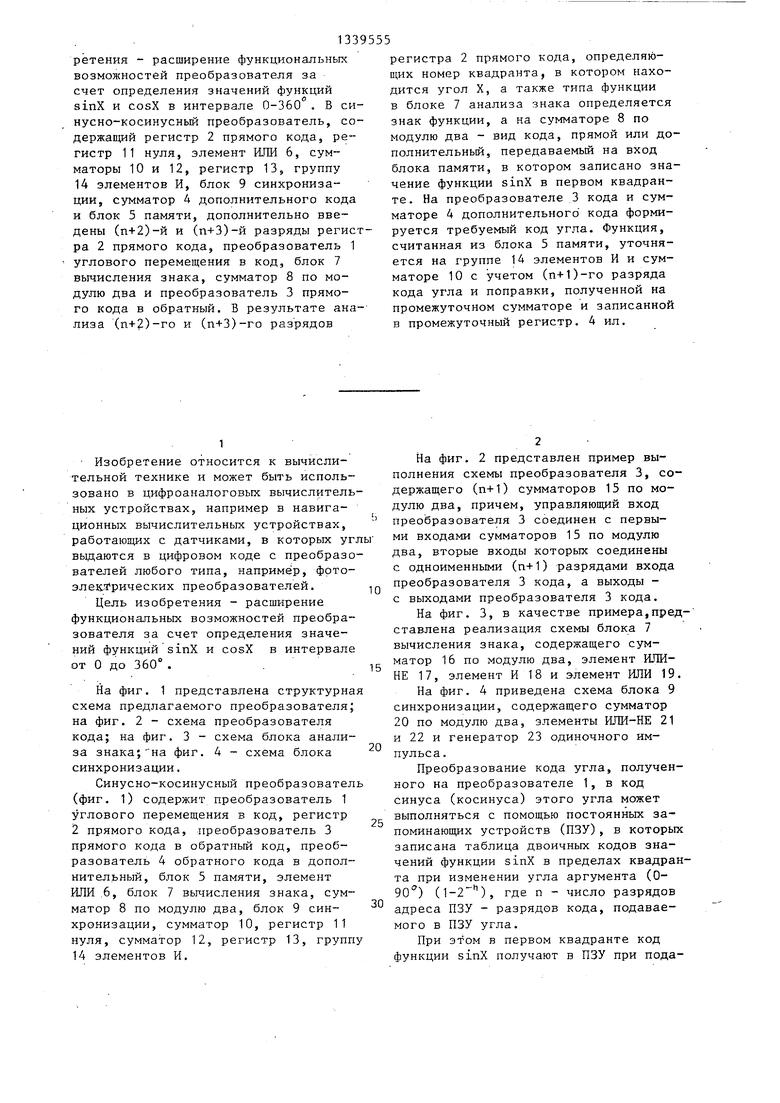

На фиг. 4 приведена схема блока 9 синхронизации, содержащего сумматор 20 по модулю два, элементы ИЛИ-НЕ 21 и 22 и генератор 23 одиночного импульса.

Преобразование кода угла, полученного на преобразователе 1, в код синуса (косинуса) этого угла может выполняться с помощью постоянных запоминающих устройств (ПЗУ), в которых записана таблица двоичных кодов значений функции sinX в пределах квадранта при изменении угла аргумента (0- 90) (1-2), где п - число разрядов адреса ПЗУ - разрядов кода, подаваемого в ПЗУ угла.

При этом в первом квадранте код функции sinX получают в ПЗУ при подаче в него прямого кода угла, а код функции cosX при подаче в ПЗУ дополнительного кода угла. В других квадрантах коды функций sinX и cosX, в JTOM числе и знаки величин, получают по известным в тригонометрии соотношениям, связывающим эти функции с функциями sinX и cosX угла X, расположенного в первом квадранте:

jsinN )

в первом и третьем квадрантах, где - модуль синуса п-разрядного кода yrnaX sinNf(l ) - синус п-разряд- .ного кода угла X в первом (I) квадранте, fsinNn| cosN(I) во втором ичет- вертом квадрантах,где cosN(l) - косинус п-разрядного кода угла X в пёр- вом квадранте.

Если , 90.-Н„, то cosN(I) sinNon(I), где Na,, дополнительный код кода угла N,.

Аналогично для функции cosN, мож- но показать, что |cosN | ) во втором и четвертом квадрантах, ICOSN I siriNflfjd) в первом и третьем квадрантах.

.

Следовательно, при наличии на. первом выходе блока 9 синхронизации сигнала нуль (выработки sinN) на вход блока 5 памяти требуется дать в первом и третьем квадран- тах (п+3)-й разряд регистра прямого кода равен нулю, а во втором и четвертом квадрантах - NQJ, (п + + 3)-й разряд регистра 2 прямого кода равняется единице. При наличии на первом выходе блока 9 синхронизации сигнала единица (выработки cosN на вход блока 5 памяти передается N во втором и четвертом квадрантах и Ng в первом и третьем квадрантах.

Преобразованием кода угла управляет сумматор 8 по модулю два. Единичное состояние на выходе сумматора 8 по модулю два при формировании функции синуса во второй и четвертом квадрантах, а косинуса в первом и третьем квадрантах определяет получение на выходе преобразователя 3 инверсного кода Nfn+,, а на преобразователе 4 получение дополнительного кода NO(nti)путем сложения инверсного кода N,, с единицей в младшем (п+1) разряде, где N(,j-(n+1) - разрядный код угла X.

0

п

На блоке 7 производится анализ номера квадранта, в котором расположен угол и вид функции (sinX или cosX) на основании этого формируется знак функции.

Функция синус отрицательна в третьем и четвертом квадрантах, когда , где п+2 - значение (п+2)- го разряда регистра прямого кода. Функция косинус отрицательна во вто- ром и третьем квадрантах, когда (п + + + З 1 , где п + значение (п+3)-го разряда регистра прямого кода, а @ - означает суммирова- ние по модулю два. Выход блока знака имеет единичное значение, если функция отрицательна и описывается формулой

& п+2 V БС ( ( )

ЕС V п+2 V БС( ),

где ЗН - выход блока знака, БС- первый выход блока синхронизации, определяющий тип функции, вырабатываемой преобразователем.

Группа 14 элементов И используетс для учета нуля или единицы (п+1)-го по старшинству разряда .кода угла и последующего округления полученного кода синуса (косинуса) угла по значению (п+2)-го по старшинству разряда кода функции угла.

Поскольку выпускаемые микросхемы блоков памяти выпускаются с числом разрядов кодов функции sinX, на несколько разрядов превьш1ающим число разрядов кода аргумента, то при ис- пользовании только (п+1) разрядов кода функции sinX отбрасывание разрядов, начиная с (п+2)-го, приводит к ошибке до единицы оставляемого (п + + 1)-го, разряда.

Для повьш1ения точности вьфаботки (п+1)-разрядных кодов синуса (косинуса) угла используется элемент ИЛИ

Указанная единица вводится в (п+ +2)-и разряд вырабатываемого кода для округления результата.

Однако при кодах функции sinX, состоящих только из единиц от первого до (п+2)-го по старшинству разрядов, добавление к выданному из блока памяти коду синуса (косинуса) угла единицы (п+2)-го разряда приводит к переполнению.

. Для устранения переполнения выда-. ваемых кодов используется элемент ИЛИ 6, вырабатывающий нуль при коде угла на выходе преобразователей 4, меньшем угла рад, и единицу при кодах углов, больших этого угла.

Синусно-косинусный преобразователь работает следующим образом.

В блок 9 синхронизации поступает сигнал выработки кода функции sinX или cosX, а в регистр 2 прямого KO-I да (п+1)-разрядный код угла N, и

10

ет из сумматора 12 на регистр 13 и записывается там по сигналу записи, поступающему из блока 9 синхронизации. Из регистра 13 код поступает на входы группы 1 элементов И, затем блок 9 синхронизации выдает сигнал выработки функции sinN.

Из блока 5 памяти на входы выходного сумматора 10 вьщается код функции sinN в соответствующем квадранте, на другие входы п старших разрядов поступают нули, а (п+1)-го и следующих по старшинству разрядов сумдва разряда (п+2)-й и (п+3)-й, значе- 15 матора 10 поступает код с выходов ния которых 00, 01, 10, 11 соответствуют первому, второму, третьему или четвертому квадранту, в котором находится угол X, и по импульсу на синхронизирующем входе преобразовате- 20 нулю, код из регистра 13 через групгруппы 14 элементов И, на первые входы которых подается (п+1)-и разряд кода угла с выходного преобразователя 4. Если значение этого разряда равно

ля записывается в регистр 2 прямого кода. По этому же импульсу производится запуск блока 9 синхронизации.

Если, например, поступил сигнал выработки кода sinX, вычисление его производится по известной формуле

sin(X+uX) sinX+cosX uX,

где X - угол, а л X - приращение угла, или

sinN sin() « slnN| +cosN uN (

где

( AN

- приращение n-разрядного кода угла при (п+1)-разрядном коде.

Согласно формуле (1) блок 9 синхронизации вьщает сигнал выработки функции cosN,.

Старшие п разрядов кода угла поступают на адресные входы блока 5 памяти и по ним вьщается код функции sinN(I) или sinNfli d) в зависимости от номера квадранта и соответствующий коду функции cosN в данном квадранте.

Старшие (т-п-1) разрядов этого кода (в рассматриваемом примере - четыре) . поступают на входы сумматора 12, как четырехразрядный код, причем он поступает на первые входы соответ- ствующих разрядов сумматора 12 и, сдвинутый монтажно на один разряд, поступает на вторые входы сумматора 12. Таким образом, в сумматоре 12 этот код складывается с кодом, умножением на 2 , т.е. происходит умножение кода на 1,5. Этот код поступа

ет из сумматора 12 на регистр 13 и записывается там по сигналу записи, поступающему из блока 9 синхронизации. Из регистра 13 код поступает на входы группы 1 элементов И, затем блок 9 синхронизации выдает сигнал выработки функции sinN.

Из блока 5 памяти на входы выходного сумматора 10 вьщается код функции sinN в соответствующем квадранте, на другие входы п старших разрядов поступают нули, а (п+1)-го и следующих по старшинству разрядов сумматора 10 поступает код с выходов нулю, код из регистра 13 через групгруппы 14 элементов И, на первые входы которых подается (п+1)-и разряд кода угла с выходного преобразователя 4. Если значение этого разряда равно

5

0

пу 14 элементов И не проходит, в противном случае код с регистра 13 проходит на вход сумматора 10. Таким образом, группа 14 элементов И осуществляет умножение одноразрядного числа -- значения (п+1)-го разряда кода угла (лН) на четырехразрядный код функции 1,5 cosN. Если обозначить код на выходе группы 14 элементов И через N, то получим

М„ 1,5-cosNi AN cosN 1 ,5-iN.

Двоичный код, поступающий в блок 5 памяти, представляет собой правиль5 ную двоичную дробь от угла 90 , если этот код умножить на /2 1,5, то 1,5 bN - это угол в радианах, а, NU приращение функции sinN при изменении угла на AN. Таким образом, сум0 матор 10 осуществляет вьфаботку функции sinN(,, .

При этом весовой коэффициент (п+ +1)-го разряда кода, поступающего с преобразователя 4, будет , и

5 элементы И группы 14 производят ум- ноясение кода 1,5 на угол , т.е. производится дополнительный сдвиг на (п+1) разрядов в сторону младщих разрядов. Этот сдвиг вьшол0 нен монтажно, за счет соединения выходов элементов И группы 14 с младшими разрядами сумматора 10.

Для округления по этому разряду . кода функции sinN,Ha этот вход

5 промежуточного сумматора 12 подается единица с выхода элемента ИЛИ 6.

.Для устранения случаев переполнения эта единица подается, когда код синуса угла в первом квадранте не

содержит единицы во всех старших разрядах до (п+2)-го включительно, т.е. при углах, которые не превышают угла 90°-- oi, где

42 2- рад -90°.

Но тогда дополнительный код долже быть не меньше об . При вычислении ко синуса угла в первом квадранте угол должен быть также не меньше об . Така проверка производится элементом ИЛИ 6

На втором этапе во время сложения кода sinN с его поправкой на сумма- торе 10 в блоке 7 анализа знака формируется знак функции.

Вьфаботка функции cosN осуществляется аналогично, но при этом сначала вырабатывается функция sinNf, поправка к косинусу п-разрядного кода угла, и запоминается на регистре 13, а затем вырабатывается функция cosN, которая суммируется со своей поправкой на сумматоре 10,включающе единицу (п+2)-го разряда для округления, и производится определение знака.

Блок 9 синхронизации работает следующим образом.

По приходу импульса на вход запуска блока 9 синхронизации запускается генератор 23 одиночного импульса, на выходе которого генерируется отрицательный импульс, длительность которого определяется временем задержки записи информации в регистр 2 прямого кода, преобразования ее на преобразователе 3 и преобразователе 4, считывания кода функции из блока 5 памяти и прохождения его через промежуточный сумматор 12. На это время внутренний триггер, собранный на элементах ИЛИ-НЕ 21 и 22, устанавливается в единичное состояние им- пульсом с входа запуска, длительност которого должна быть больше времени срабатывания генератора 23 одиночного импульса, а на выходе сумматора 20 по модулю два формируется сигнал выработки функции обратной искомой, для определения поправки к искомой функции. По истечении этого времени сигнал на выходе генератора 23 одиночного импульса переходит с нижне- .го уровня на верхний. По этому переходу производится стробирование записи информации в промежуточный регистр 13 и внутренний триггер перебрасывается в нуль, а на первом выходе блока 9 синхронизации генерируется сигнал выработки искомой функции .

Формула изобретения

Синусно-косинусный преобразователь, содержащий регистр прямого кода, регистр нуля, элемент ИЛИ, регистр, два сумматора, группу элементов И, блок синхронизации, преобразователь обратного кода в дополнительный, блок памяти, m выходов которого (т - разрядность представления функции в блоке памяти) соединены с первой группой входов первого сумматора, п входов (п+1 - разрядность йходного кода) второй группы которого соединены с выходами регистра нуля, вход первого операнда преобразователя обратного кода в дополнительный соединены с выходом регистра нуля, управляющий вход блока синхронизации соединен с входом задания режима работы преобразователя, первый выход блока синхронизации соединен с входом разрешения записи регистра, разряды информационного входа которого, кроме старшего, соединены с выходом суммы второго сумматора, выход переполнения которого соединен со старшим разрядом информационного входа регистра, выходы которого соединены с первыми входами элементов И группы, выходы которых соединены с (m-n) входами второй группы первого сумматора, выходы j-x старших разрядов блока памяти (j 1,2,...m-n-2) соединены с первой группой входов второго сумматора и со сдвигом на один разряд в сторону старших разрядов с второй группой входов второго сумматора, выход (m-n-l)-ro старшего разряда блока памяти соединен с первым входом (т- п-1)-го разряда второго сумматора, второй вход первого разряда которого соединен с выходом элемента ИЛИ, выходы старших разрядов с первого по (п+1)-й первого сумматора соединены с выходом преобразователя, отличающийся тем, что, с целью расширения функциональных возможностей преобразователя, за счет определения значений функций sinX и cosX в интервале от О до 360 , в него введены преобразователь углового перемещения в код, блок вычисления знака, сумматор по модулю два, преобразователь прямого кода в обратный, выход которого соединен с входом вто рого операнда преобразователя обратного кода в дополнительный вход аргумента преобразователя является вхо дом преобразователя углового перемещения в код, выход которого соединен с информационным входом регистра пря мого кода, выходы (п+1) разрядов которого соединен с информационнь га входами преобразователя прямого кода в обратный, выход (п+2)-го разряда регистра прямого кода соединен с пер вьш входом блока вычисления зна-ка, выход (п+3)-го разряда регистра прямого кода соединен с первым входом сумматора по модулю два и вторым вхо дом блока вычисления знака„ выход которого является выходом знака искомой функции преобразователя, вход задания режима работы преобразователя соединен с входом, разреи ения записи регистра прямого кода, второй выход блока синхронизации соединен с третьим входом блока вычисления знака и вторым входом сумматора по модулю два, выход которого соединен с управляющими входами преобразователя прямого кода в обратный и преоб- 10 разователя обратного кода в дополнительный, выходы п-х старших разрядов которого соединен с адресными входами блока памяти, выход (п+1)-го разряда преобразователя обратного кода

15 в дополнительный соединен с вторыми входами элементов И группы, выходы с первого по к-й (к п/2 + 1), где к - ближайшее целое преобразователя обратного кода в дополнительный сое2Q динены с входами элемента ИЛИ, выход первого сумматора является выходом искомой функции преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синусно-косинусный преобразователь | 1986 |

|

SU1388855A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1280698A1 |

| Устройство для вычисления функций @ и @ | 1980 |

|

SU978146A1 |

| Цифроаналоговая следящая система | 1988 |

|

SU1697055A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1061136A1 |

| Цифроаналоговая следящая система | 1989 |

|

SU1783473A1 |

| Цифровой генератор гармонических функций | 1981 |

|

SU1001069A1 |

| Цифровой синтезатор частот | 1983 |

|

SU1190457A1 |

| Устройство для вычисления функций синуса и косинуса | 1986 |

|

SU1322272A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1042013A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифроаналоговых вычислительных устройствах, например в навигационных вычислительных устройствах, работающих с датчиками, в которых углы вьщаются в цифровом коде с преобразователей любого типа. Цель изобп te 00 00 со ел ел ел

-

-

Фиг.2

Фиг.З

Фиг.

Составит.ель З.Шершнева

Редактор Е.Папп Техред М.Дидык

Заказ 4223/39 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д-. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

22

Корректор М.Демчик

| Синусно-косинусный преобразователь | 1981 |

|

SU1005040A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1042013A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-23—Публикация

1986-04-03—Подача