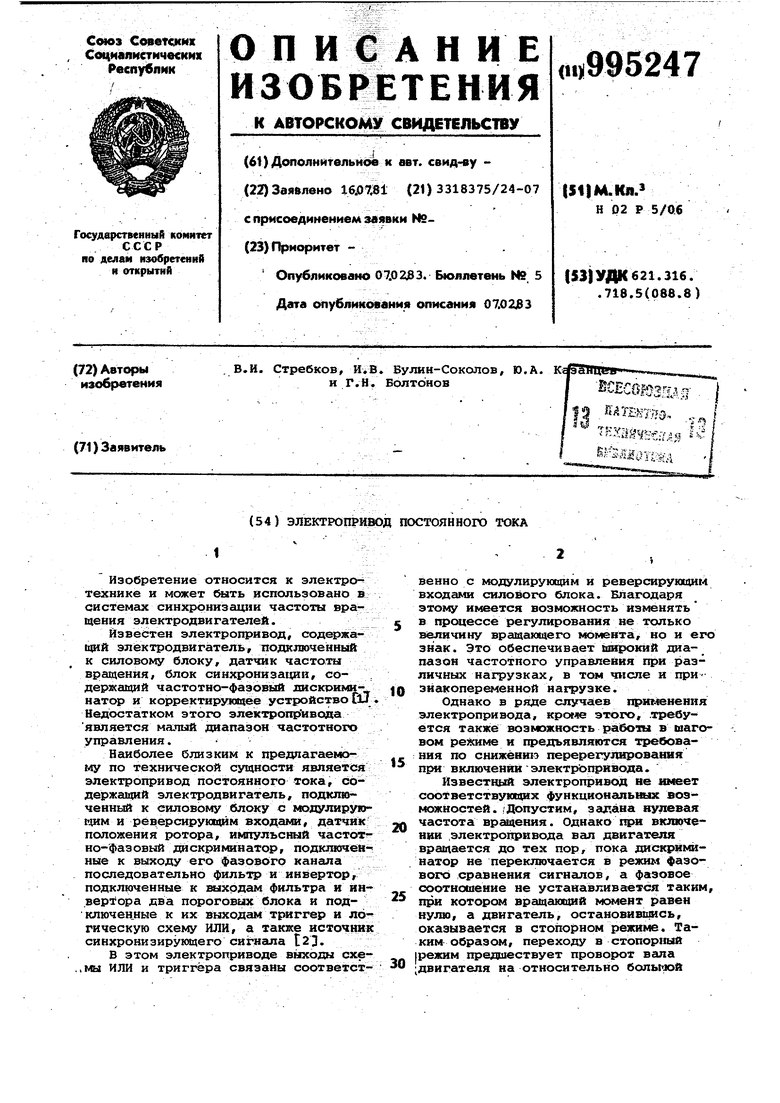

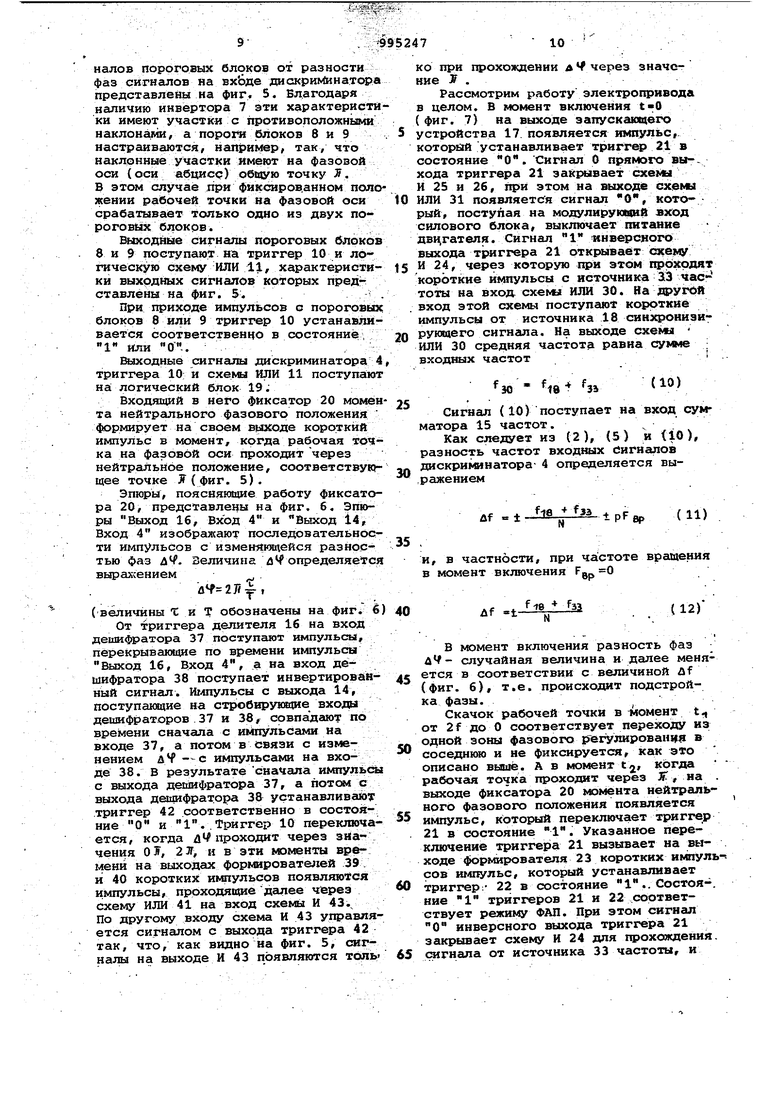

угол и первоначальное положение вала не сохраняется. -Для шагового режима необходимо, чтобы при задании нулевой частоты вращения и включении электропривода вал двигателя не врацался и фиксировалось его первоначальное положение (с точностью до иага ) . Указанный выме проворот вала при включении электропривода приводит также к большому перерегулированию при задании малой частоты вращения. Таким образом, недостатком извест ного электропривода является отсутствие возможности работн в шаговом режиме и низкое качество переходных процессов при включении на малых частотах вращения, что ограничивает функциональные возможности электропривода. Цель изобретения - расширение функциональных возможностей путем получения шагового режима и повышение качества переходных процессов. Поставленная цель достигается тем, что электропривод введены генератор тактовых иглпульсов, первый делитель частоты, вход KOTOpotS подключен к выходу генератора . вых импульсов, а выход - к входу.да чика положения ротора, формировател сигналов датчика положения ротора, включенный между его выходом и одним из входов импульсного частотно-фазо вого дискриминатора, последовательно соединенные сумматор частот и второй делитель частоты, причем один иЗ:. входов сумматора подключен к генератора тактовых импульсов, а пер вый выход второго делителяР 1астоты соединен с вторым входом тимпулясного частотно-фазового дискриминатора, запускающий блок и логический блок, содержащий фиксатор момента нейтраль ного фазового положения, второй и третий триггеры с раздельными входами, формирователь коротких импульjCOB, шесть логических схем И, вторую третью и четвертую логические схе1ЛЕЛ ИЛИ, источник частоты, при этом первый из входов второй схемл ИЛИ подключен к источнику синхронизирующего сигнала, а выход подключен к второму входу сумматора частот, выходы третьей и четвертой схемы ИЛИ подключены соответственно к модулирующему и реверсирующему входам силового блока, выход первой схемы И соединен с вторым входог второй cxei ИЛИ, а ее входы - с источником ча;стоты и с инверсным выходом второго триггера выход второй схеглл И по ключен к первому входу третьей схега ИЛИ, а входы - к выходу первой схем ИЛИ и к прямом выходам второго и третьего триггеров, выход третьей схемы И подключен к второму входу третьей схема ИЛИ, а ее входы - к прямому выходу второго триггера и к инверсному выходу третьего триггера, выход четвертой схемы И подключен к пepвo лy входу четвертой схемы ИЛИ, а входы подключены к прямым выходам первого) и третьего триггеров, выход пятой схемы И подключен к второму входу четвертой схемы ИЛИ, а входы подключены к инверсному выходу третьего триггера и выходу частотного канала импульсного частотно-фазового дискриминатора, выход шестой схемы И подключен к второму входу второго триггера, а входы подключены к инверсному выходу третьего триггера и дополнительному выходу импульсного частотно-фазоворо дискриминатора, фиксирующему момент равенства частот, первый вход второго триггера подключен к- выходу фиксатора момента нейтрального фазового положения, а вход установки в ноль второго триггера подключен к запускающему блоку, первый вход третьего триггера связан через фор1мнроватвль коротких импульсов с выхЬдом второго триггера, второй вход .Tsef bsi: триггера подключен к другому дополнительному выходу импульсного частотно-фазового дискриминатсдаа,...фиксирующему момент срыва синхронизации. При этом фиксатор момента нейтрального фазового положения содержит подключённые к второму и третьему выходам частот второго делителя частоты, два дешифратора, стробирующие входы которых связаны с формирователем сигнала датчика положения ротора, соединенные с выходами первого триггера, два формирователя коротких импульсов, к выходам которых подключена логическая схема ИЛИ, связанный с выходаб щ дешифраторов триггер с раздельными входа яи и подключенную к выходам этого триггера и схемы ИЛИ выходную схему И. На фиг. 1 представлена схема электропривода; на фиг. 2 - схема фиксатора момента нейтрального фазового положения; на Фиг. 3 - иглпульсный частотно-Фазовый дискриминатор, вариант построения; на фиг. 4-7 - эпюры, поясняющие работу электропривода. Электропривод содержит эле стродвигатель 1, подключенный к силовому блоку 2, связанный с валом двигателя датчик 3 положения ротора, импульсный частотно-фазовый дискриминатор 4. К выходу фазового канала 5 дискриминатора 4 подключены последовательно фильтр 6 и инвертор 7, а к их выходам - пороговые блоки 8 и 9. К выходам пороговых блоков подключены входы первого триггера 10 и первой схемы ИЛИ 11. Вход генератора 12 тактовых им- пульсов через первый делитель 13 частоты связан с входом датчика 3 полоисения ротора, выход которого через формирователь 14 сигналов датчика соединен с первым входом дискриминатора 4. К выходу генератора 12 подсоединен также один из входов сумматора 15, последовательно с которым включен второй делитель 16 , первый выход которого соединен с вторым входом дискриминатора 4. Электропривод содержит также -запускающий блок 17, источник 18 синхронизируюi ero сигнала и логический блок 19, в состав которого входят фиксатор 20 момента нейтрального фазового полджения, второй 21 и третий 22 триггеры с раздельными входами, формирователь 23 коротких импульсов, первая 24, вторая 25, третья 26, четвертая ; 27, пятая 28 и шестая 29 логические схе1иы И, вторая 30, третья 31, четвер тая : 32 логические схемы ИЛИ и источнйк 33 частоты.

При этом первый вход схемы ИЛИ 30 подключен к источнику 18 синхронизирующего сигнала, а выход подключен к второму сумматора 15, выходы третьей 31 и четвертой 32 схем ИЛИ подключены соответственно к модулирующему и реверсирующеког входам силового блока 2, выход первой схемы И 24 подключен к второму входу второй схемы ИЛИ 30, а входы подключены к источнику 33 частоты и инверсному выходу второго триггера 21, выход второй схеки И 25 подключен к первому входу третьей схемы ИЛИ 31, а входы подключены к выходу первой схемы ИЛИ 11 и прямвш выходам второго 21 и третьего 22 триггеров, выход третьей схемы И 26 подключен к второму входу третьей схемы ИЛИ 31, а входы подключены к прямому выходу второго триггера 21 и инверсному выходу третьего триггера 22, выход четвертой схекы И 27 подключен к первому входу четвертой схема ИЛИ 32, а входы подключены к прямым выходам первого 10 и третьего 22 триггерор, выход пятой cxeNu И 28 подключен к второму вхотог четвертой ИЛИ 32 а входы подключены к инверснсялу выходу третьего триггера 22 и выходу частотного канала 34 дискриминатора 4, выход шестой схемы И 29. подключен к второму входу второго триггера 21, а входы подключены к инверсному выхо третьего триггера 22 и допопнительному выходу 35 дискриминатора 4, фиксирующегду момент равенства частот первый вход второго триггера 21 подключен к выходу фиксатора 20 мсмента нейтрального фазового положения, а вход установки в ноль второго 21 подключен к запускающему блоку 17, первый вход третьего триггера 22 связан через формирователь 23 коротких импульсов с выходом второго триггера 21, а второй вход третьего

триггера 22 подключен к другому дополнительному выходу 36 дискриминатора 4 фиксирующему момент срыва синхронизации.

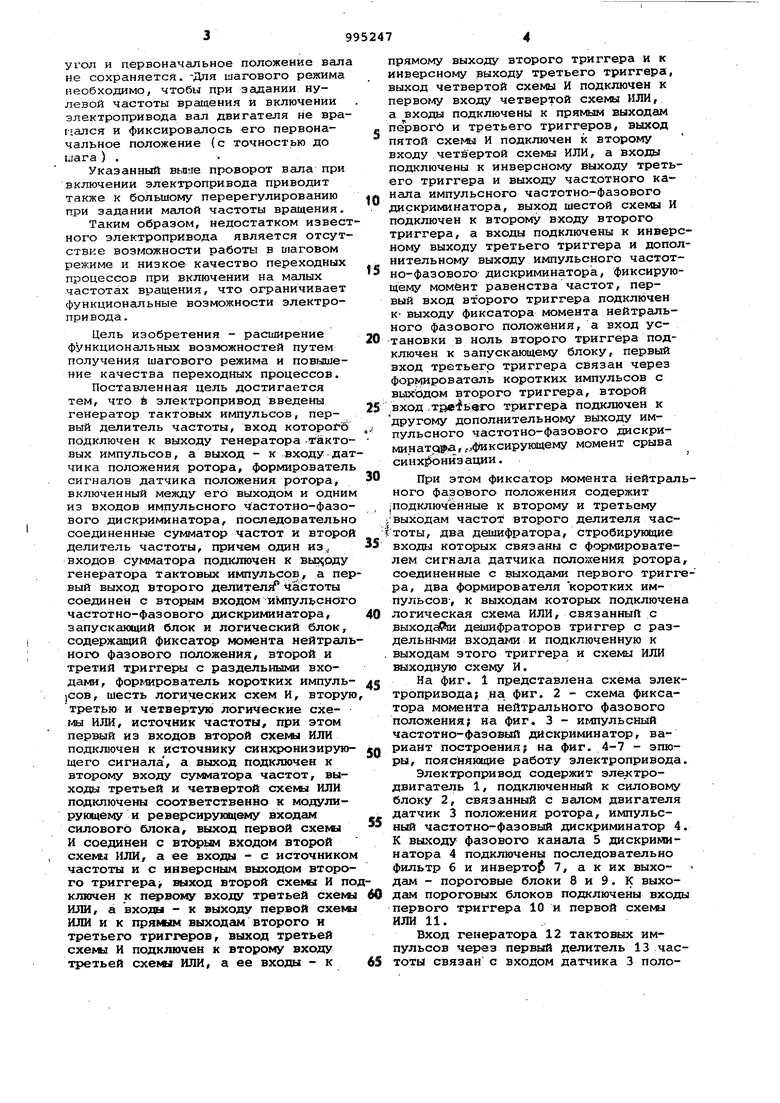

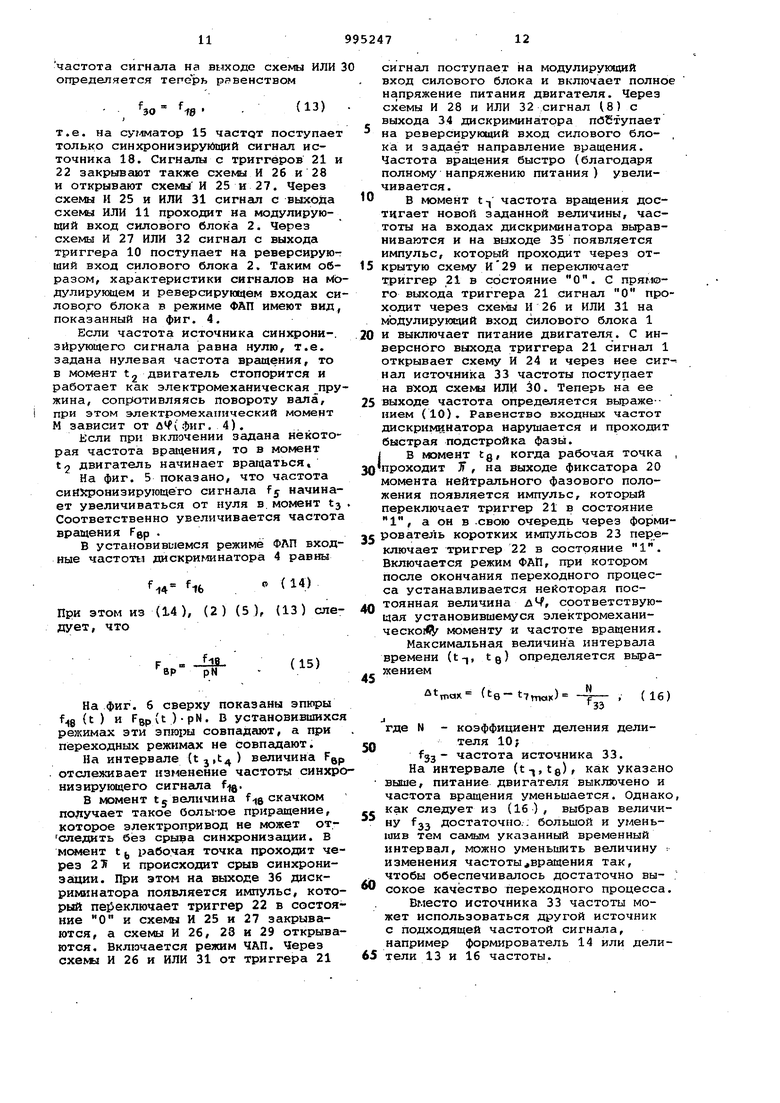

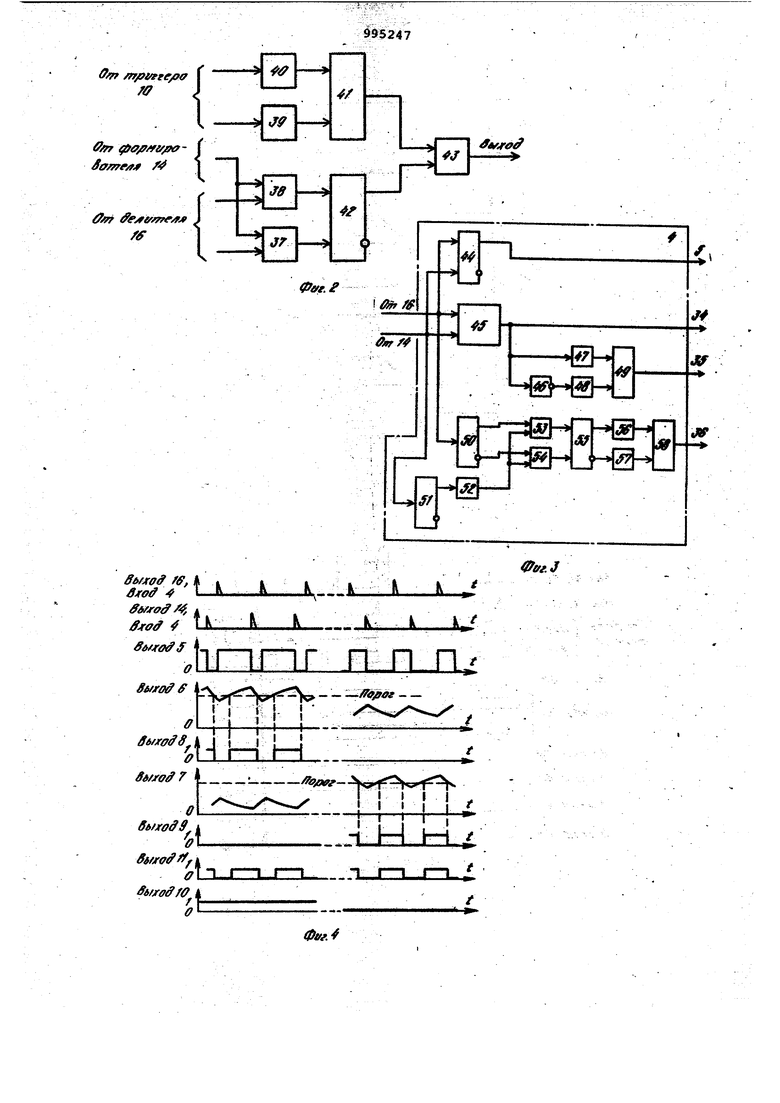

Фиксатор момента нейтрально|хэ фазового положения {фиг. 2 ) содержит подключенные к второму делителю два дешифратсфа 37 и 38, стробирупцие входы которых подключены к фop aIpoвaтелю 14 сигнала датчика лоложенця ротора, подключеишае к выходам первого триггера 10 два формфоватепя 39 и 40 коротких импульсов, подкпоченную к их выходам логическую схему ИЛИ 41 подключенный к аыходам дешифраторов триггер 42 с раздельными входами и подключенную к выходам триггера и схекы ИЛИ выходную логическую схему И 43.

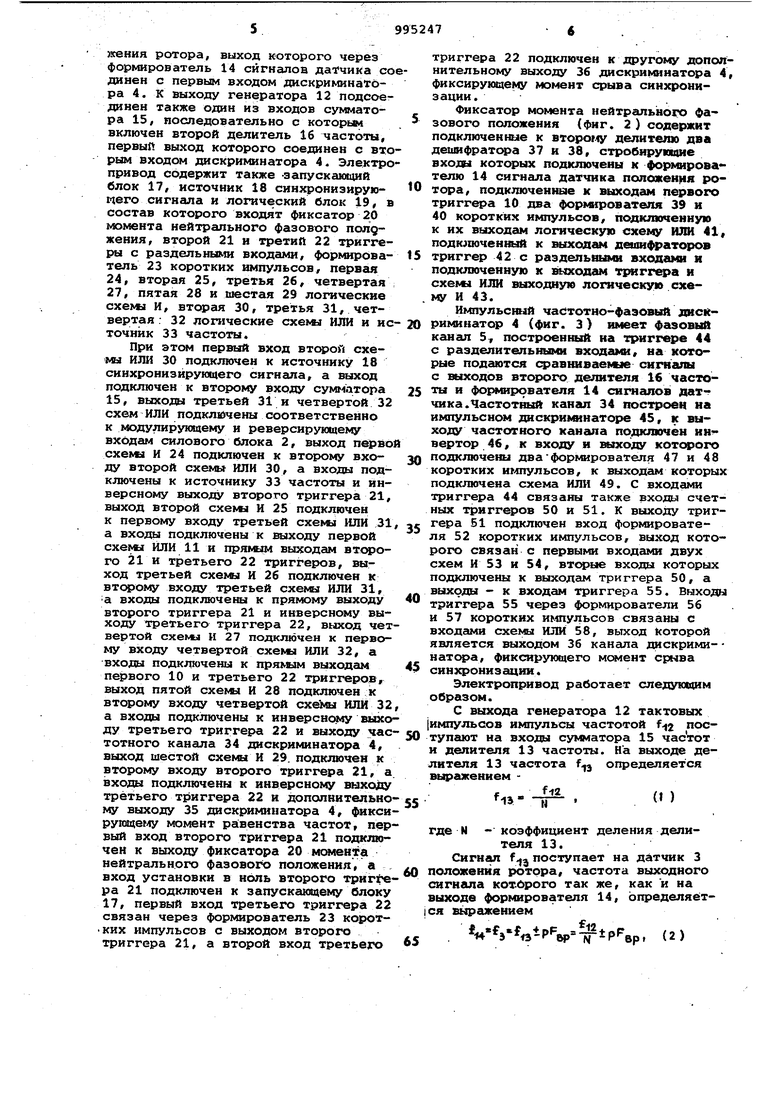

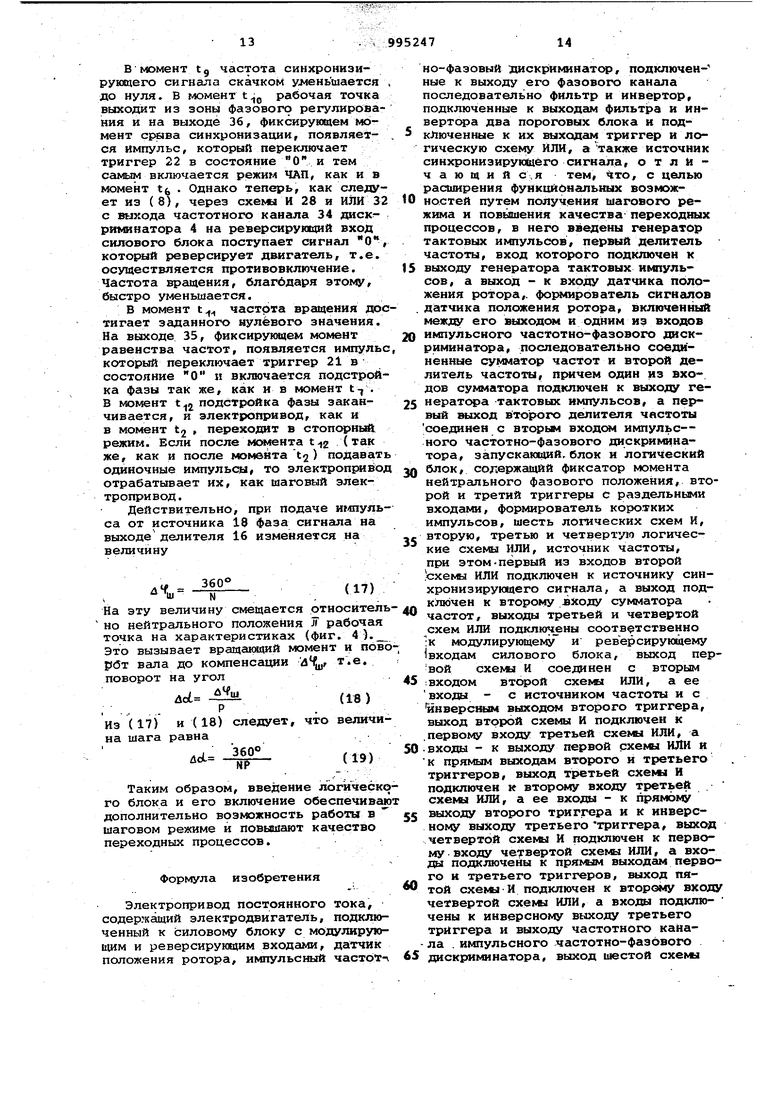

Импульсный частотно-фазовый дискриминатор 4 (фиг. 3) имеет фазовый кёшал 5, построенный на триггере 44 с разделительными входанш, на кото рые подаются сравниваемые сигналы с выходов второго делителя 16 частоты и формирователя 14 сигналов датчика.Частотный канал 34 построен на импульсном дискриитнаторе 45, к выходу частотного канала подключён ин вертор 46, к входу и выходу котсфого подключены два-форкмрователя 47 и 48 коротких нглпульсов/ к выходам которы подключена схема ИЛИ 49. С входами триггера 44 связаны также входм счетных триггеров 50 и 51. К выходу триггера 51 подключен вход формирователя 52 коротких импульсов, выход которого связан с первыми входами двух схем И 53 н 54, вторые входы которых подключены к выходам триггера 50, а выходы - к входам триггера 55. Выход триггера 55 через формирователи 56 и 57 коротких импульсов связаны с входами схемы ЮМ 58, выход Которой является выходом 36 канала дискриминатека, фиксирующего мсмент срыва синхронизации.

Электропривод работает следующим образом.

С выхода генератора 12 тактовых |импульсов импульсы частотой поступают на входы сумматора 15 частот и делителя 13 частоты. На выходе делителя 13 частота выражением «где N - коэффициент деления делителя 13.

Сигнал поступает на датчик 3 положения ротора, частота выходного сигнала котброго так же, как и на выходе формирователя 14, определяёт|ся выражением

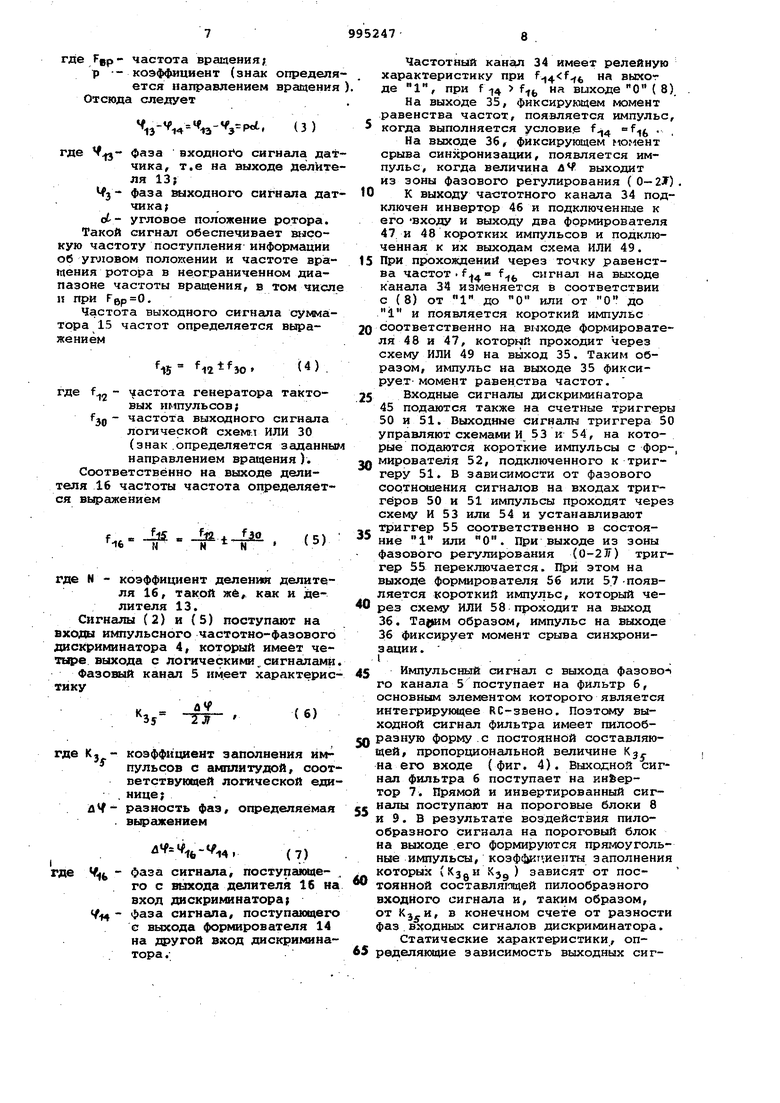

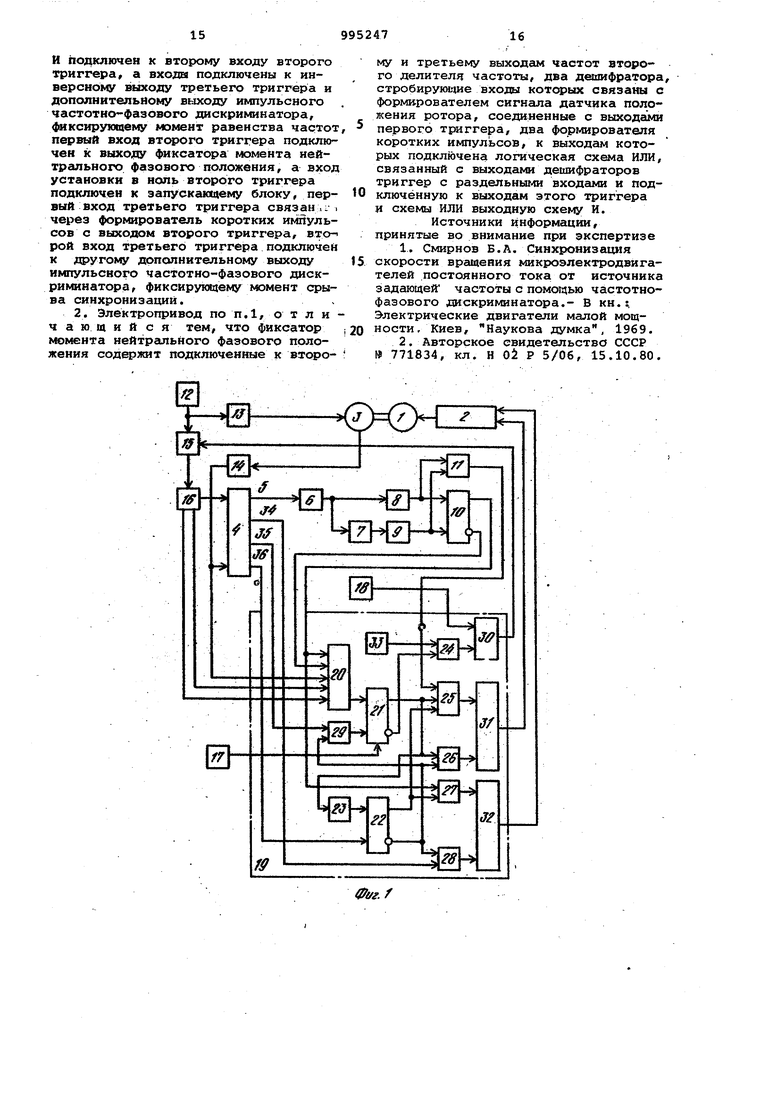

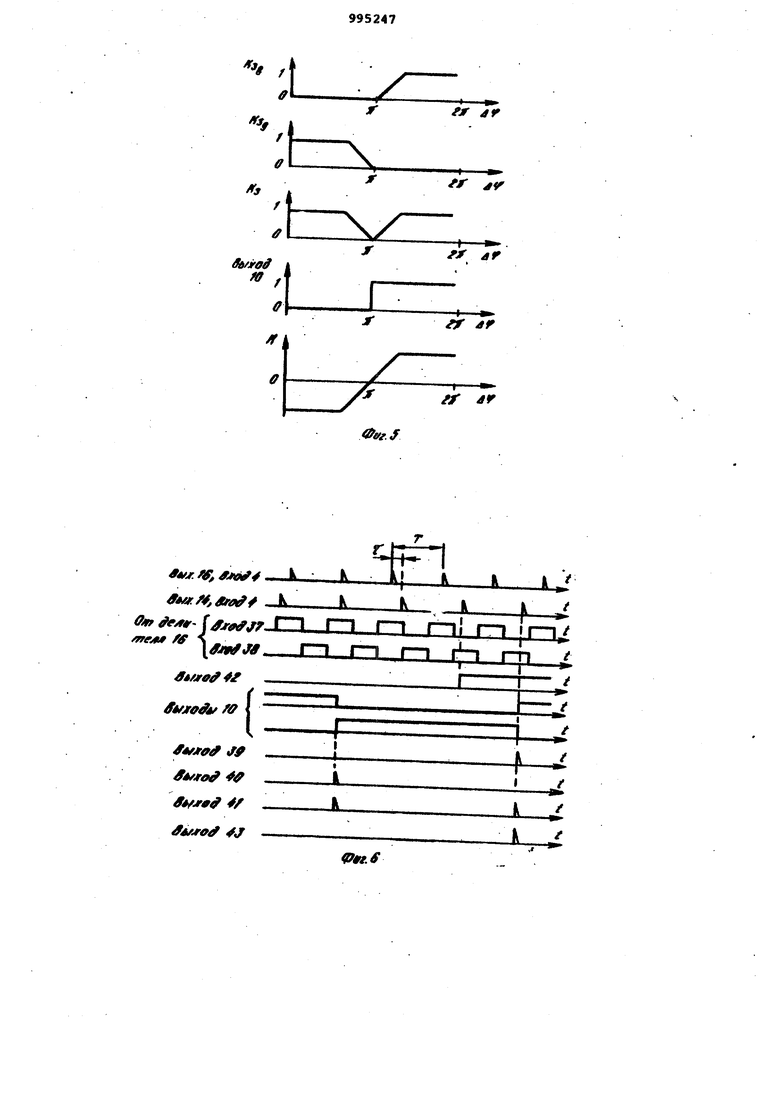

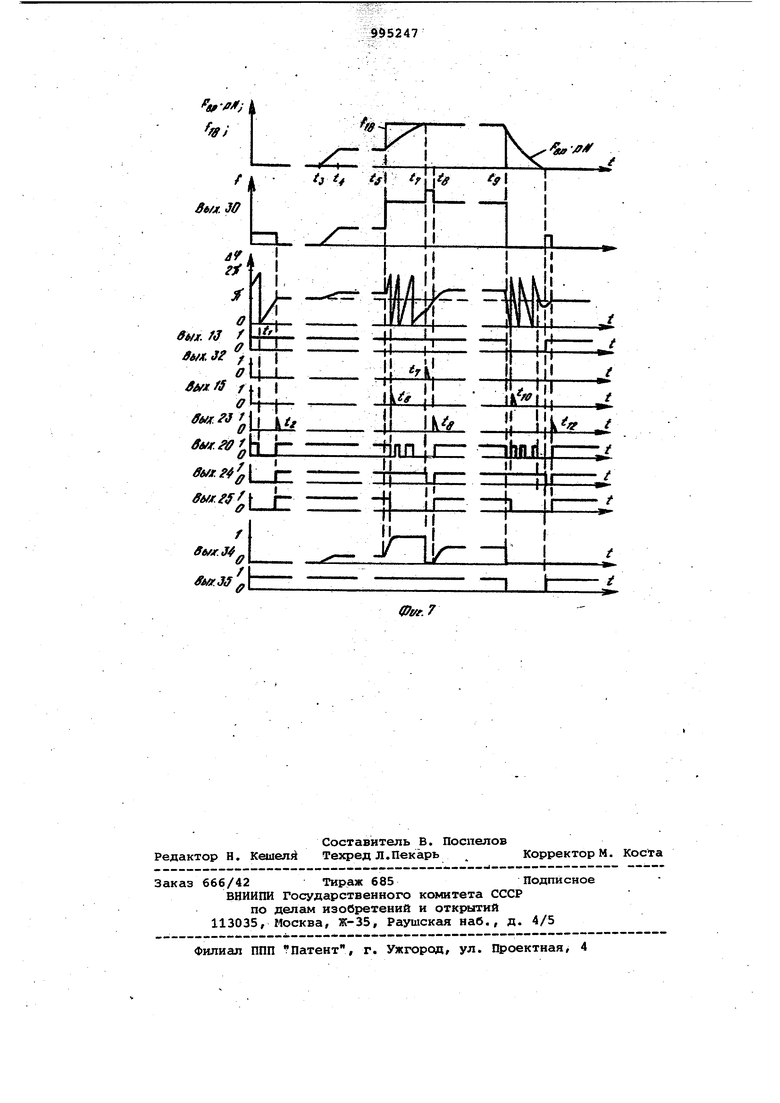

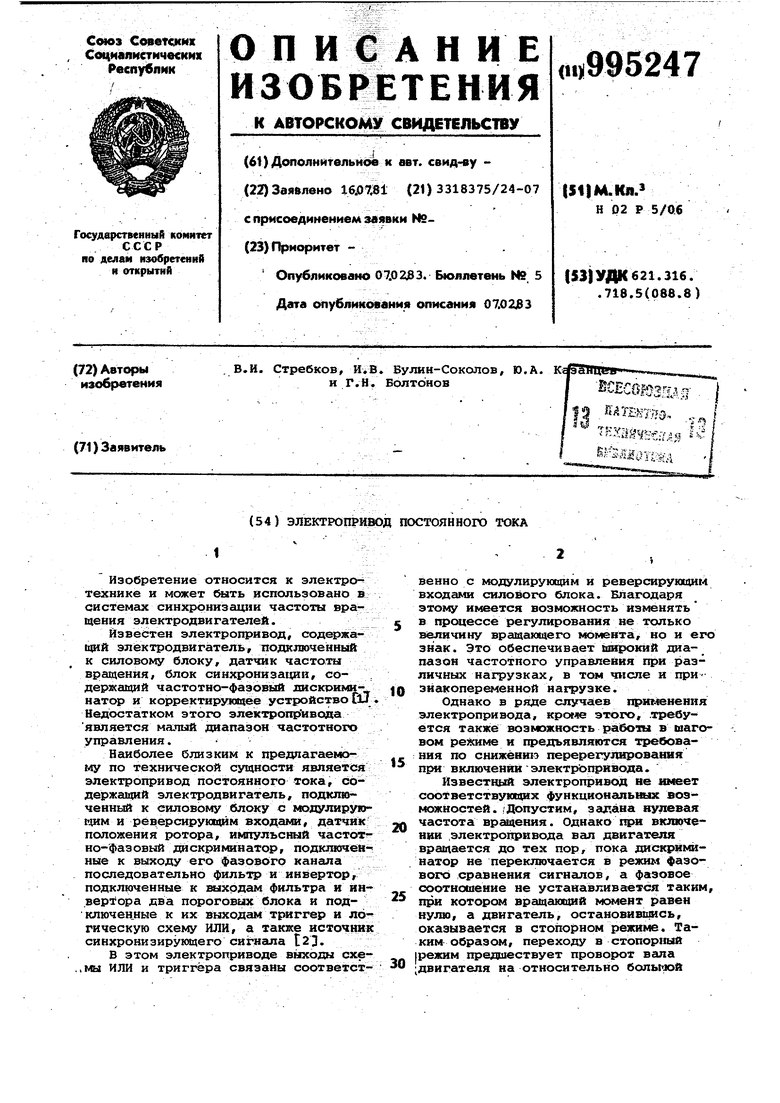

. VW-PV iP pt (2) где Fgp- частота вращения; р --коэффициент (знак определ ется направлением вращени Отсюда следует %3-V i3-Vp 3) где - фаза входгюх о сигнала да чика, т.е на выходе делИт ля 13; фаза выходного сигнала да чика; ot- угловое положение ротора. Такой сигнал обеспечивает високую частоту поступления информации об угловом положении и частоте вра мения ротора в неограниченном диапазоне частоты вращения, в том числ п при . Частота выходного сигнала сумма тора 15 частот определяется выражениемгде - частота генератора тактовых импульсов; - частота выходного сигнала логической схеми ИЛИ 30 (знак .определяется заданны направлением вращения}. Соответственно на выходе делителя 16 частоты частота определяется выражением L1 m+. М N где N - коэффициент деленифг делителя 16, такой ж6, как и Целителя 13. Сигналы (2) и (5) поступают на входы импульсного частотно-фазового дискриминатора 4, который имеет четщ е выхода с логическими сигналами Фазовый канал 5 имеет характерис тику где Kj - коэффициент заполнения им пульсов с амплитудой, соот ветствующей логической еди . нице J . Л - разность фаз, определяемая . выргикением , где Ч)(, - фаза сигнала, поступаюцего с выхода делителя 16 н вход дискриминатора У - фаза сигнала, поступающег с выхода формирователя 14 на другой вход дискримина тора. Частотный канал 34 имеет релейную характеристику при выхог да 1, при f-,4 , на выходе О ( 8) На выходе 35, фиксирующем момент равенства частот, появляется импульс, когда выполняется условие f ife На выходе 36, фиксирующем срыва синхронизации, появляется импульс, когда величина ЛЧ выходит из зоны фазового регулирования (О-2У). к выходу ча-стотного канала 34 подключен инвертор 46 и подключенные к его ВХОДУ и выходу два формирователя 47 и 48 коротких импульсов и подключенная к их выходам схема ИЛИ 49. При прохождений через точку равенства частот f 14 -tfc сигнал на выходе канала 34 изменяется в соответствии с (8) от 1 до О или от О до 1 и появляется короткий импульс соответственно на выходе формирователя 48 и 47, который проходит через схему ИЛИ 49 на выход 35. Таким образом, импульс на выходе 35 фиксирует момент равенства частот. Входные сигналы дискриминатора 45 подаются также на счетные триггеры 50 и 51. Выходные сигналы триггера 50 управляют схемами И 53 к 54, на которые подаются короткие импульсы с фор-, мирователя 52, подключенного к триггеру 51. В зависимости от фазового соотношения сигналов на входах триггеров 50 и 51 импульсы проходят через схему И 53 или 54 и устанавливают триггер 55 соответственно в состояние 1 или О. При выходе из зоны фазового регулирования (0-2Ж) триггер 55 переключается. При этом на выходе формирователя 56 или 57-появляется короткий импульс, который через схему ИЛИ 58 проходит на выход 36. образом, импульс на выходе 36 фиксирует момент срыва синхронизации. . .. , Импульсный сигнал с выхода фазового канала 5 поступает на фильтр 6, основным элементом которого является интегрирующее RC-звено. Поэтому выходной сигнал фильтра имеет пилообразную форму с постоянной составляющей, пропорциональной величине К,. на его входе (фиг. 4). Выходной сигнал фильтра 6 поступает на инйертор 7. Прямой и инвертированный сигналы поступают на пороговые блоки 8 и 9. В результате воздействия пилообразного сигнала на пороговый блок на выходе его формируются пряг юугольные импульсы, коэф тиепты заполнения которых (зоИ зависят от постоянной составлягтацей пилообразного входного сигнала и, таким образом, от , в конечном счете от разности фаз входных сигналов дискриминатора. Статические характеристики, определяющие зависимость выходных сигналов пороговых блоков от разности фаз сигналов на входе дискрил инатеф представлены на фиг. 5. Благодаря наличию инвертора 7 эти характерист ки имеют участки с противоположными наклонами, а порога блоков 8 и 9 настраиваются, например, так, что наклонные участки имеют на фазовой оси (оси абциср) общую точку Л. В этом случае при фиксиров.анном пол жении рабочей точки на фазовой оси срабатывает только одно из двух пороговых блоков. Выходные сигналы пороговых блоко 8 и 9 пос:тупают на триггер 10 и логическую схему ИЛИ 11, характеристи ки выходных сигналов которых представлены на фиг. 5.i При приходе импульсов с пороговы блоков 8 или 9 триггер 10 устанавли вается соответственно в состояние или О.. Выходные сигнсшы дискриминатора триггера 10; и схемы ИЛИ 11 поступаю на: логический бЛок 19; Входяпщй в него фиксатор 20 моме та нейтрального фазового положения формирует на своем виходе короткий импульс в момент, когда рабочая точ ка на фазовой оси проходит через нейтральное положение, соответствуй щее точке У (фиг. 5). Эпюры, поясняющие работу фиксато ра 20, представлены на фиг. 6, Эпюры Выход 16, Вход 4 и Выход 14, Вход 4 изображают последовательнос ти импульсов с изменлкяцейся разностью фаз Д. Величина л Ч определяетс вырахсением . (величины t и Т обозначены на фиг. 6 От триггера делителя 16 на вход дешифратора 37 поступают импульсы, перекрывающие по времени импульсы Выход 16, Вход 4, а на вход дешифратора 38 поступает инвертированный сигнгш. Игдпульсы с выхода 14, поступающие на стробнруншше входы дешифраторов.37 и 38, совпадают по времени сначала с ийпульсами на входе 37, а потом в связи с изменением дЧ -с импульсами на входе 38. В результате импульо с клхода дешифратора 37, а потом с выхода дешифратора 38 устанавливают триггер 42 соответственно в состояние О и 1..Триггер 10 переключается, когда л Чпроходит через значения 01, 21, и в эти моменты времени на выходах формирователей 39 и 40 коротких импульсов появляются импульсы, проходящие далее через схему ИЛИ 41 на вход схемы И 43. По другому входу схема И 43 управляется сигналом с выхода триггера 42 так, что, как видно на фиг. 5, сигналы на выходе И 43 появляются толь ко при прохождении А через значение JF . Рас смотрим работу эле ктропривода в целом. В момент включения t-0 (фиг. 7) на выходе запускающего устройства 17. появляется импульс, который устанавливает триггер 21 в состояние О. Сигнал О прямого вы-хода триггера 21 закрывает схемы И 25 26, этом на вьисод е схемы ИЛИ 31 появляется сигнал О, кото-рый, поступая на модулирукхций зход силового блока, выключает питание двцгателя. Сигнал 1 инверсного выхода т| иггера 21 открывает чзхему И 24, через которую при этом проходят короткие импульсы с источника S3 часТ01%1 на вход схемы ИЛИ 30. На ДФугОй вход этой схемы поступают короткие импульсы от источника 18 синхронизирующего сигнала. На выходе схемы ИЛИ 30 средняя частота равна cytme : входных частотi 8 за Сигнал (10) поступает на вход сумматора 15 частот. Как следует из (2), (5) и (10), разность частот входных Сигналов дискри инатора- 4 определяется вы,ражением t . pF и, в частности, при 4aicTOTe вращения в момент включения 0 f-ie - f33 N В момент включения разность фаз й - случайная величина и далее меняется в соответствии с величиной uf (фиг. 6), т.е. происходшт подстройка фазы. Скачок раерчеА точки в момент t от 2f до О соответствует переходу из одной зоны фазового регулирования в соседнкно и не фиксируется, как это описано выше. А в момент t когда рабочая точка проходит через ЛГ, на . выходе фиксатора 20 момента нейтрального фазового положения появляется импульс, который переключает три ггер 21 в состояние 1. Указанное переключеиие триггера 21 вызывает на выходе форьшрователя 23 коротких импульсов иг4пульс, который устанавливает триггер/ 22 в состояние 1.. Состоя-, ниа 1 триггеров 21 и 22 соответствует режиму ФАЛ. При этом сигнал О инверсного выхода триггера 21 закрывает схему И 24 для прохождения, сигнала от источника 33 частоты, и частота сигнала на выходе схемы ИЛИ определяется тегерь рявенством т.е. на сумматор 15 частот поступае только синхронизирующий сигнал источника 18. Сигналы с триггеров 21 и 22 закрывают также схемы И 26 и 28 и открывают схемы И 25 и 27. Через схемы И 25 и ИЛИ 31 сигнал с выхода схекы ИЛИ 11 проходит на модулирующий вход силового блока 2. Через схемы И 27 ИЛИ 32 сигнал с выхода триггера 10 поступает на реверсирующий вход силового блока 2. Таким образом, характеристики сигналов на Мо дулирукяцем и реверсирующем входах си лово.го блока в режиме ФАП имеют вид показанный на фиг. 4. Если частота источника синхрони-. зйрующего сигнала равна нулю, т.е. задана нулевая частота вращения, то в момент 12 двигатель стопорится и работает как электромеханическая пру жина, сопротивляясь повороту вала, при этом электромеханический момент М зависит от (.t)Hr. 4). Если при включении задана некото рая частота вращения, то в момент t двигатель начинает вращаться, На фиг. 5 показано, что частота сий$фонизйрующего сигнала fj начина ет увеличиваться от нуля в. момент t Соответственно увеличивается частот вращения Fgp . В установившемся режиме ФЛП вход ные частоты дискриминатора 4 равны « { 14) При этом из (14 ), (2) (5), (13) сле дует, что На фиг. 6 сверху показаны эпюры (t ) и FBp(t )-pN. В установившихс режимах эти эпюры совпадают, а при переходных режимах не совпадают. На интервале (tj.t4 ) величина F отслеягивает изменение частоты синхр низирующего сигнала f. В момент 15 величина скачком получает такое больное приращение, которое электропривод не может отследить без срыва синхронизации. В момент t J, рабочая точка проходит че рез 2 и происходит срыв синхрониэгоши. При этом на выходе 36 дискриминатора появляется импульс, кото рый пе еключает триггер 22 в состоя ние О и схемы И 25 и 27 закрываются, а схемы И 26, 28 и 29 открыва ются. Включается режим ЧАП. Через cxeNEJ И 26 и ИЛИ 31 от триггера 21 сигнал поступает на модулирующий вход силового блока и включает полное напряжение питания двигателя. Через схемы И 28 и ИЛИ 32 сигнал (8) с выхода 34 дискриминатора netSfynaeT на реверсирующий вход силового бло- , ка и задаёт направление вращения. Частота вращения быстро (благодаря полному напряжению питания) увеличивается. В момент t -, частота вращения достигает новой заданной величины, частоты на входах дискриминатора выравниваются и на выходе 35 появляется импульс, который проходит через открытую схему и переключает триггер 21 в состояние О. С прямого выхода триггера 21 сигнал О проходит через схемы И 26 и ИЛИ 31 на модулирующий вход силового блока 1 и выключает питание двигателя. С инверсного выхода триггера 21 сигнал 1 открывает схему И 24 и через нее сиг нал источника 33 частоты поступает на вход cxeNw ИЛИ 30. Теперь на ее выходе частота определяется выраже-нием (10). Равенство входных частот дискриминатора нарушается н проходит быстрая подстройка фазы. В момент t0, когда рабочая точка , проходит J, на выходе фиксатора 20 момента нейтрального фазового положения появляется импульс, который переключает триггер 21 в состояние 1, а он в .свою очередь через формирователь коротких импульсов 23 переключает триггер 22 в состояние 1. Включается режим ФАП, при котором после окончания переходного процесса устанавливается некоторая постоянная величина дЧ, соответствующая установившемуся электромеханической моменту и частоте вращения. Максимальная величина интервала времени (t-,, tg) определяется вьфажением (tg-t7). где N - коэффициент деления делителя 10; f33 - частота источника 33. На интервале (t-i.tg), как указано вьвие, питание двигателя выключено и частота вращения уменьшается. Однако, как следует из (16-) , выбрав величину fjj достаточно.: большой и уменьшив тем саглым указанный временный интервал, можно уменьшить величину . изменения частоты,вращения так, чтобы обеспечивалось достаточно вы- , сокое качество переходного процесса. Вместо источника 33 частоты может использоваться другой источник с подходящей частотой сигнаша, например формирователь 14 или делители 13 и 16 частоты. В момент tg частота синхронизирующего сигнала скачком уменьшается до нуля. В момент рабочая точка выходит из зоны фазового регулирова ния и на выходе 36, фиксирувяцем момент срыва синхронизации, появляется импульс, который перекл10чает триггер 22 в состояние О и тем самым включается режим ЧАП, как ив момент tfe . Однако теперь, как следу ет из (8), через схемы И 28 и ИЛИ 3 с выхода частотного канала 34 диск ртиинатора 4 на реверсирунхфий вход силового блока поступает сигнал О который реверсирует двигатель, т.е. осуществляется противовключение, частота вращения, благодаря этому, быстро уменьшается, В момент t частота вращения до тигает заданного нулевого значения. На выходе 35, фиксирующем момент равенства частот, появляется импуль который переключает триггер 21 в состояние О и включается подстрсЛ ка фазы так же, как и в момент t-| . В момент подстройка фазы заканчивается, и электропривод, как и в момент t2 , переходит в стопс ньй режим. Если после мотлента (так же, как и после момента 42) подават одиночные импульсы, то элвктроп1 1во отрабатывает их, как шаговый электропривод. Действительно, при подаче са от источника 18 фаза сигнала на выходе делителя 16 изменяется на величину Ш- -N На эту величину смещается ртносител но нейтрального положения л рабочая точка на характеристиках (фиг. 4). Это вызывает вращанвдий момент и пов вала до компенсации л%,, т.е. поворот на угол Из (17) и (18) следует, что величи на шага равна ,.-. Таким образом, введение логическ го блока и его включение обеспечива дополнительно возможность работы в шаговом режиме и повышают качество переходных процессов. Формула изобретения Электропривод постоянного тока, содержащий электродвигатель, подключенный к силовому блоку с модулирующим и реверсирующим входами, дастчик положения ротора, имтульсный частотно-фазовый ;ш1скриминат(ч, подключенные к выходу его фазового канала последовательно фильтр и инвертор, подключенные к выходёш фильтра и инвертора два пороговых блока и подкАюченные к их выходам триггер и логическую схему Или, атакже источник синхронизирующего сигнала, отличающий с я тем, 4то, с целью расширения функциональных возможностей путем получения шагового режима и повь шения качества переходных процессов, в него введены генератор тактовых импульсов, первый делитель частоты, вход которого подключен к выходу генератора тактовых импульсов, а выход - к входу датчика положения ротора,. фор 4ирователь сигналов датчика положения ротора, включенный между его выходсяк и одним из входов импульсного частотно-фазового дискриминатора, последовательно соединенные сумматор частот и второй делитель частоты, причем один из входов сумматора подключен к выходу генерат ч а тактовых импульсов, а первый выход второго делителя частоты соединен с вторьм входом импульс- ного частотно-фазового дискриминатора, запускаквдий, блок и логический блок, содержащий фиксатор момента нейтрального фазового положения, второй и третий триггеры с раздельными входами, формирователь коротких импульсов, шесть логических схем И, вторую, третью и четвертую логические схемы ИЛИ, источник частоты, при этом-первый из входов второй схемы ИЛИ подключен к источнику синхронизирующего сигнала, а выход подключен к второму входу сумматора частот, выходы третьей и четвертой схем ИШ1 подключены соответственно IK модулирукицему и реверсирующему (входам силового блока, выход первой cxei«i И соединен с вторым :входом второй схемы ИЛИ, а ее входы - с источником частоты и с нверсжзМ выходом второго триггера, выход второй схемы И подключен к . первому входу третьей схемы ИЛИ, а входы - к выходу первой схемы ИЛИ и к прямым выходам второго и третьего триггеров, выход третьей схемы И подключен к второму входу третьей схеки ИЛИ, а ее входы - к прямому выходу второго триггера и к инверсному выходу третьеготриггера, выход четвертой схемы И подключен к первому входу четвертой схемы ИЛИ, а входы подключены к прямым выходам первого и третьего триггеров, выход пятой схекы И подключен к входу четвертой схема ИЛИ, а входы подключены к инверсному выходу третьего триггера и выходу частотного канала . импульсного частотно-фазового дискриминатора, выход шестой схемл

И подключен к второму входу второго триггера, а входЕа подключены к инверсному выходу третьего триггера и дополнительному выходу импульсного частотно-фазового дискриминатора, фиксирующему момент равенства частот первый вход триггера подключен к выходу фиксатора момента нейтрального фазового положения, а вход установки в ноль второго триггера подключен к запускающему блоку, первый вход третьего триггера связан.:i через формирователь коротких импульсов с выходом второго триггера, второй вход третьего триггера подключен к другому дополнительному выходу импульсного частотно-Фазового дискриминатора, фиксирующему момент срыва синхронизации.

2. Электропривод по п,1, о т л и чающийся тем, что Фиксатор момента нейтрального фазового положения содержит подключенные к второму и третьему выходам частот второго делителя частоты, два дешифратора стробируюьдие входы которых связаны с формирователем сигнала датчика положения ротора, соединенные с выходами первого триггера, два формирователя коротких импульсов, к выходам которых подключена логическая схема ИЛИ, связанный с выходами дешифраторов триггер с раздельныгф входами и подключённую к выходам этого триггера и схемы ИЛИ выходную схему И. Источники информации, принятые во внимание при экспертизе

1.Смирнов Б.А, Синхронизация скорости вращения микроэлектродвигателей постоянного тока от источника задающей частоты с помощью частотнофазового дискриминатора.- В кн.; Электрические двигатели малой мощности, Киев, Наукова думка, 1969.

2.Авторское свидетельство СССР

№ 771834, кл. Н Oi Р 5/06, 15.10.80.

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Позиционный электропривод | 1984 |

|

SU1270859A1 |

| Электропривод постоянного тока | 1980 |

|

SU928575A1 |

| Электропривод постоянного тока | 1991 |

|

SU1786630A1 |

| Электропривод постоянного тока | 1991 |

|

SU1775833A1 |

| ЭЛЕКТРОПРИВОД | 1997 |

|

RU2130688C1 |

| Электропривод постоянного тока | 1978 |

|

SU771834A1 |

| СТАБИЛИЗИРОВАННЫЙ ЭЛЕКТРОПРИВОД | 2011 |

|

RU2462809C1 |

| Электропривод постоянного тока | 1986 |

|

SU1661951A1 |

| Синхронизируемый вентильный электродвигатель | 1985 |

|

SU1317581A1 |

| СИНХРОННО-СИНФАЗНЫЙ ЭЛЕКТРОПРИВОД | 2011 |

|

RU2485665C1 |

Авторы

Даты

1983-02-07—Публикация

1981-07-16—Подача