01

со со 1

г оэ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения отношения частот последовательностей импульсов | 1988 |

|

SU1596266A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для числового программного управления | 1985 |

|

SU1352459A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Устройство для управления трехфазным мостовым инвертором | 1984 |

|

SU1297194A1 |

| Система программного управления электроприводом | 1987 |

|

SU1481708A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Преобразователь унитарного кода в сдвиг фазы импульсного сигнала | 1984 |

|

SU1229962A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники для измерения величины отношения частот импульсных последовательностей, приведенной к ее номинальному значению. Целью изобретения является расширение диапазона измеряемых частот и функциональных возможностей. Устройство для измерения отношения частот последовательностей импульсов содержит входные шины 1 и 2, реверсивный счетчик 5, формирователь 6 разностной частоты, элемент 7 блокировки, выходную информационную шину 8 и кодоуправляемый делитель 10 частоты. Введение входных шин 3 и 4, выходной информационной шины 9, кодоуправляемых делителей частоты 11 и 12, мультиплексора 13, блока 14 памяти, формирователя 15 серии импульсов, тактового генератора 16, демультиплексора 17, делителя 18 частоты и управляющего блока 19 позволяет производить измерение величины отношения частот к одному из ряда номинальных значений в режимах "Настройка" и "Работа". 10 ил.

Фи9.1

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники для измерения величины отношения частот импульсных последовательностей, приведенной к ее номинальному значению

Цель изобретения - расширение пазона измеряемых частот и функциональных возможностей

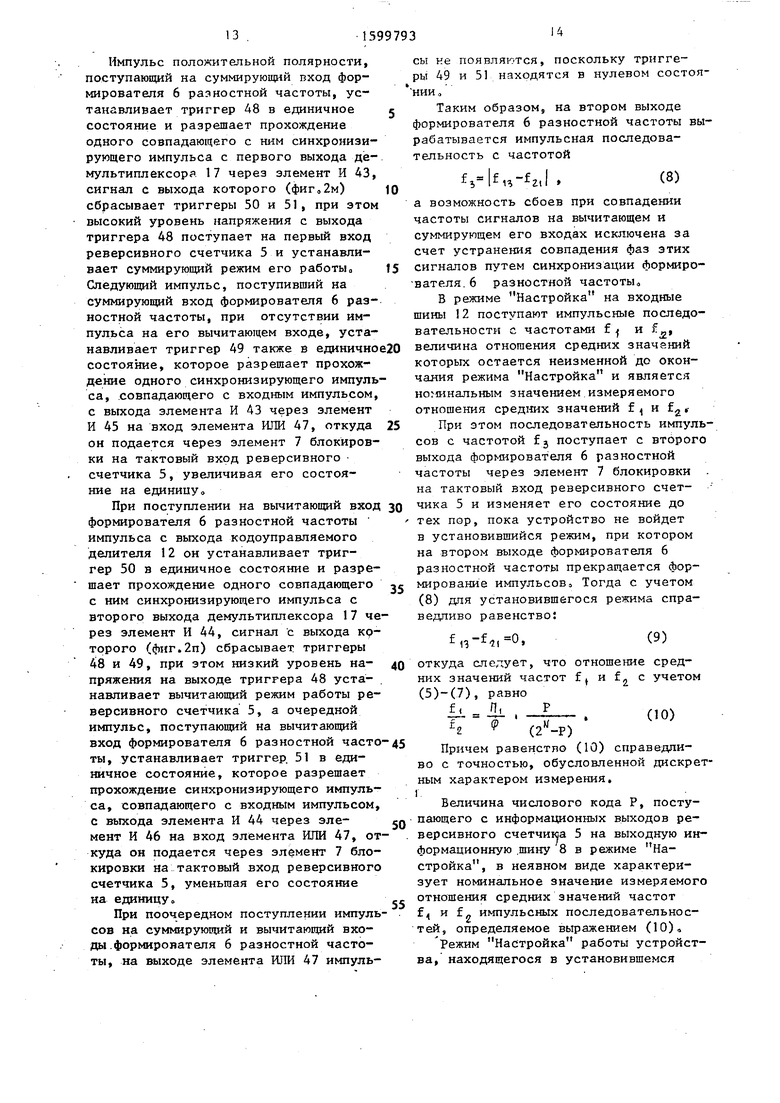

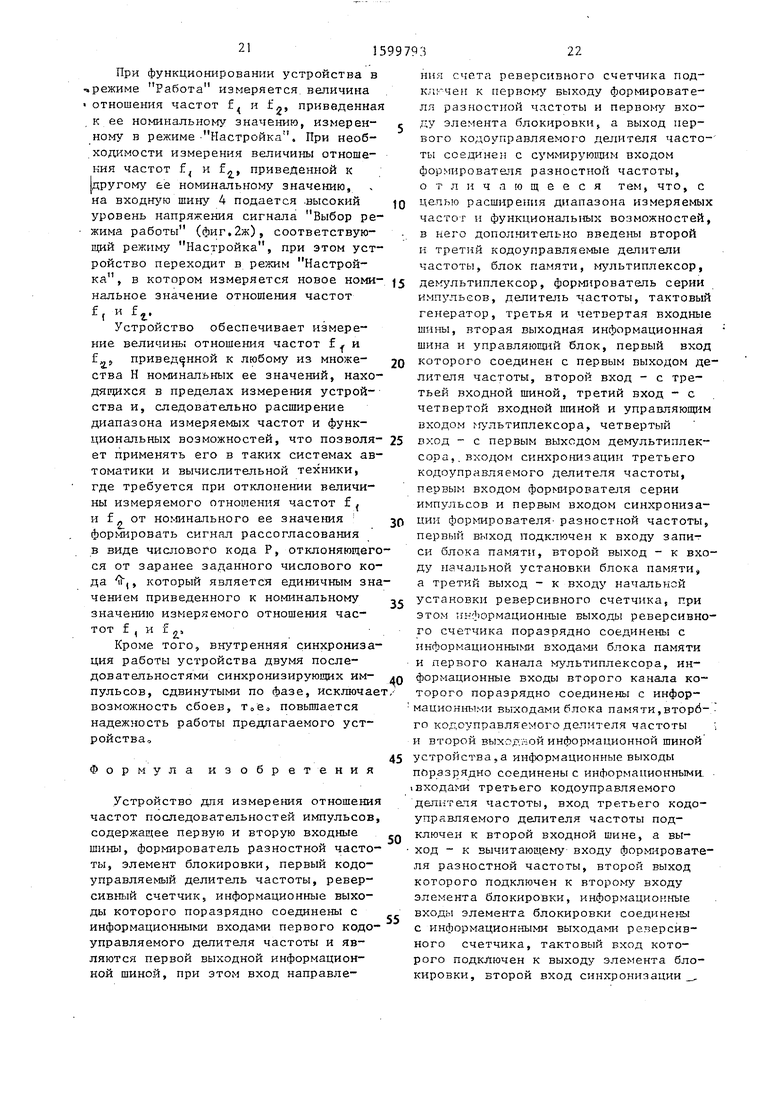

На фиГс1 представлена структурная схема устройства; на - временные диаграммы; на фиг, 3-8 - схемы отдельных блоков устройства; на фиг,9 и 10 - временнь е диаграммы,поясняющие его работу

Устройство для измерения отношения частот последовательностей .импульсов содержит входные шины 1-4, реверсивный счетчик 5, формирователь 6 разностной частоты, элемент 7 блокировки, выходные информационные шины 8 и 9, кодоуправляемые делители 10-12 частоты, мультиплексор 135 блок А памяти, формирователь 15 серии импуль- сов, тактовый генератор 16, демульти- плексор 17, делитель 18 частоты и уп- , равля1опд1й блок 19, первый вход которого соединен с первым выходом делителя 18 частоты, второй вход - с входной шиной 3, третий вход - с входной шиной 4 и управляющим входом мультиплексора 13, первый выход - с входом записи блока 14 памяти, второй выход - с входом начальной установки блока 14 памяти, четвертый вход объединен с входом синхронизации кодоуп- рдвляемого делителя 12 частоты, первым . формирователя 15 серии импульсов, с первым выходом демульти- плексора 17 и первым входом синхронизации формирователя 6 разностной частоты, а третий выход соединен с входом начальной установки реверсивного счетчика 5, информационные выходы которого поразрядно соединены с информационными входами, кодоуправ- ляемого делителя 10 частоты, выходной информационной шиной 8, информационными входами блока 14 памяти и информационными входами первого канала мультиплексора 13оНнформационные входы второго канала мультиплексора 13 поразрядно соединены с информа ционными входами кодоуправляемого делителя 11 частоты, с информационными выходами блока 14 памяти и выход- ной информационной шиной 9, а информационные выходы поразрядно соединены с информационными входами кодоуправляемого делителя 12 частоты, второй

вход которого соединен с входной шиной 2, а выход подключен к вычитающему входу формирователя 6 разностной

частоты, при этом его суммирующий вход соединен с выходом кодоуправляемого делителя 10 частоты, а первый выход подключен к входу направления счета реверсивного счетчика 5 и первому входу элемента 7 блокировки Выход элемента 7 соединен с тактовым

входом реверсивного счетчика 5, информационные входы - с информационными вьжодами реверсивного счетчика 5, а второй вход подключен к второму выходу формирователя 6 разностной частоты, второй вход синхронизации которого, объединен с входами синхронизации кодоуправляемых делителей частоты 10 и 11, вторым выходом демульти- плексора 17, первый вход которого

соединен с вторым выходом делителя 18 частоты, а второй вход подключен к входу делителя 18 частоты и выходу тактового генератора 16, причем входная шина 1 соединена с вторым входом

формирователя 15 серии импульсов, Вы- .ход формирователя 15 подключен к входу кодоуправляемого делителя 11 частоты, выход которого соединен с входом кодоуправляемого делителя 10

частоты

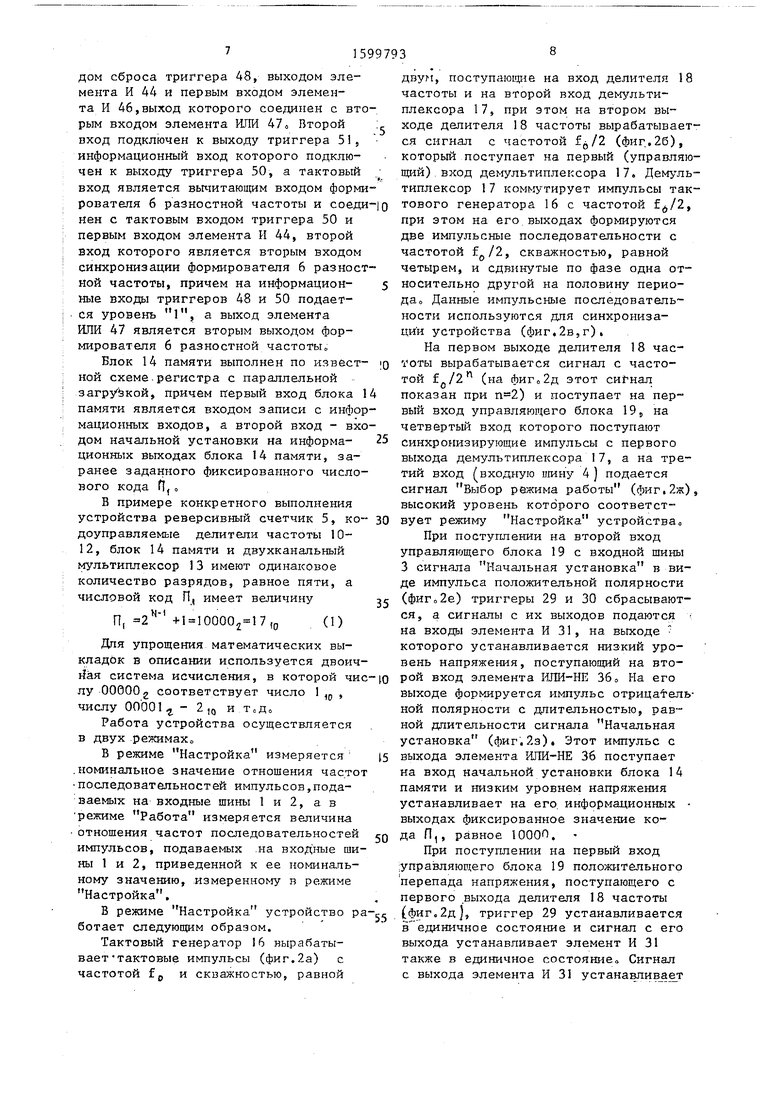

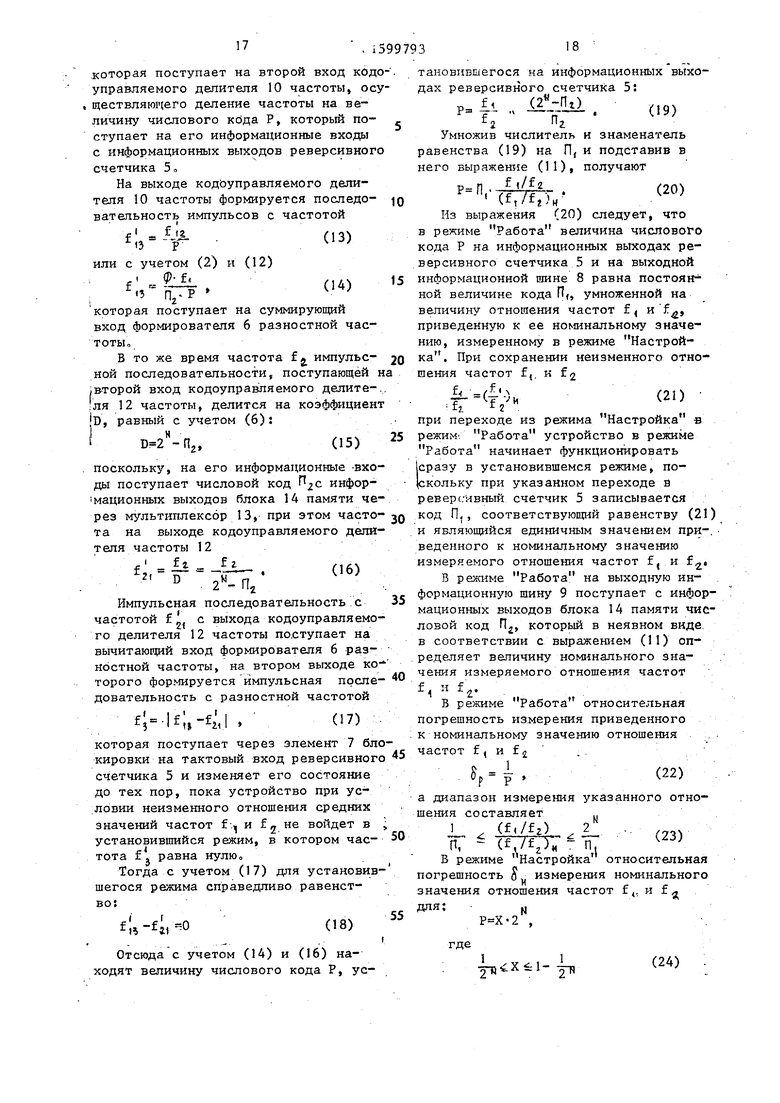

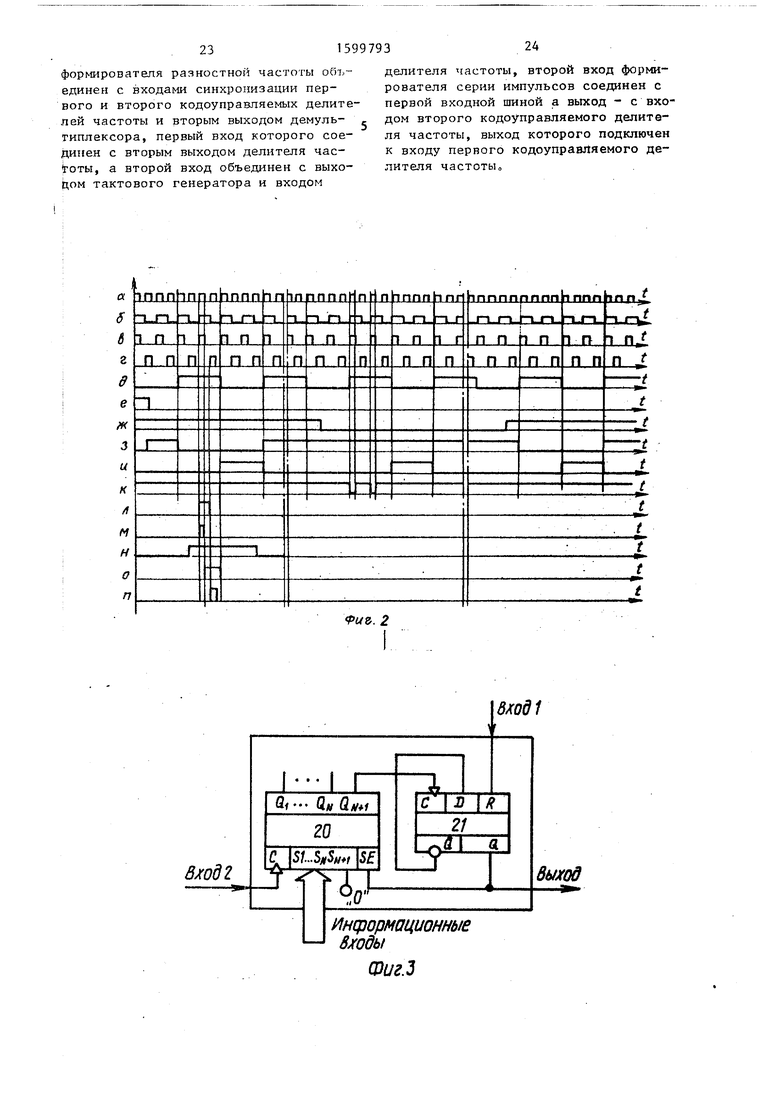

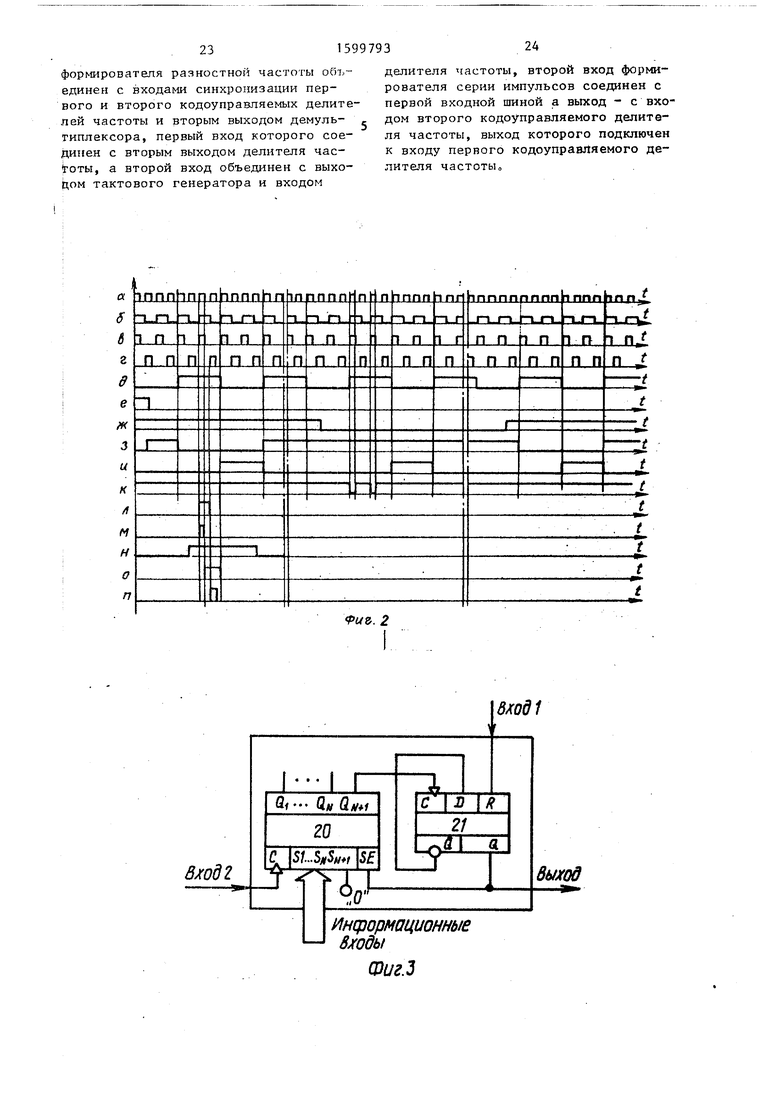

Кодоуправляемый делитель 10 (11) частоты (фиг.З) содержит вычитающий счетчик 20 и триггер 21, информационный вход которого соединен с его инверсным выходом, вход сброса подключен к входу кодоуправляемого делителя частоты, прямой выход подключен к выходу кодоуправляемого делителя частоты и к входу записи вычитающего счетчика 20, выход (N+l)-ro разряда которого, используемый в качестве выхода обратного переполнения, подключен к тактовому входу триггера 21 Тактовый вход и информационные входы N младших разрядов являются соответственно вторым входом и информационными входами кодоуправляемого делителя частоты, причем на информационный вход (N+l)ro разряда вычитающего счетчика 20 подается уровень О,

Кодоуправляемый делитель 12 частоты (фиг„4) содержит суммирующий счетчик 22 и триггеры 23 и 24 Инверсный тактовый вход триггера 24 соединен

10

с тактовым входом триггера 23 и входом третьего кодоуправляемого делителя 12 частоты, информационный вход соединен с входом синхронизации кодоуправляемого делителя 12 частоты, а выход подключен к тактовому входу суммирующего счетчика 22, выход ()-ro разряда которого, используемый в качестве выхода прямого переполнения, соеданен с входом установки триггера 23. Вход записи, соединенный с выходом триггера 23, и информационные входы N младших разрядов являются соответственно выходом и информацией- 5 ными входами кодоуправляемого делителя 12 частоты, причем на информационный вход триггера 23 и на информационный вход (N+l)-ro разряда суммирующего счетчика 22 подается уровень .

Формирователь 15 серии импульсов (фиго5) содержит триггеры 25 и 26, счетчик 27 и элемент И 28, выход которого является выходом формирователя 15 серии импульсов, инверсный вход соединен с тактовым входом и выходом (М+1)-го разряда счетчика 27 и инверсным входом сброса триггера 26, а прямой вход подключен к тактовому входу триггера 25, к входу разрешения счета счетчика 27 и является первым входом формирователя 15 серии импульсов. Выход триггера 26 соединён с входом обнуления счетчика 27, а тактовый вход соединен с выходом триггера 25, информационный вход которого является вторым входом формирователя 15 серии импульсов, причем на информационный вход триггера 26 подается уровень l

Управляющий блок 19 (фиг„6) содержит триггеры 29 и 30, элемент И 31, элемент И-НЕ 32 и четыре элемента ИЛИ-НЕ 33-36, причем тактовый вход триггера 29 является первым входом управляющего блока 19 и соединен с тактовым входом триггера 30, первым входом элемента И-НЕ 32 и первым входом третьего элемента ИЛИ-НЕ 35 Вход 50 сброса является вторьм входом уп- ;равляющего блока 19 и соединен с входом сброса триггера 30 и первым входом четвертого элемента ИЛИ-НЕ 36, информационный вход является третьим 55 входом управляющего блока 19, а прямой выход подключен к информационному входу триггера 30 и первым входам элемента И 31 и первого элемента ИЛИ20

25

30

Q

45

35

НЕ 33, вторые входы которых соединены между собой и подключены к инверсному выходу второго триггера 30. Выход элемента И 3 соединен с первым входом второго элемента ИЛИ-НЕ 34 ,и вторым входом четвертого элемента РШИ-НЕ 36, выход которого является вторым в(1- ходом управляющего блока 19. Выход первого элемента 1-ШИ-НЕ 33 соединен с вторыми входами элемента И-НЕ 32 и второго элемента 1ШИ-НЕ 34, причем третий вход элемента И-НЕ 32 является четвертым входом управляющего блока 19, а выход - первым выходом управляющего блока 19 о Выход второго элемента ИЛИ-НЕ 34 соединен с вторым входом третьего элемента ИЛИ-НЕ 35, выход которого является третьим выходом управляющего блока 19,

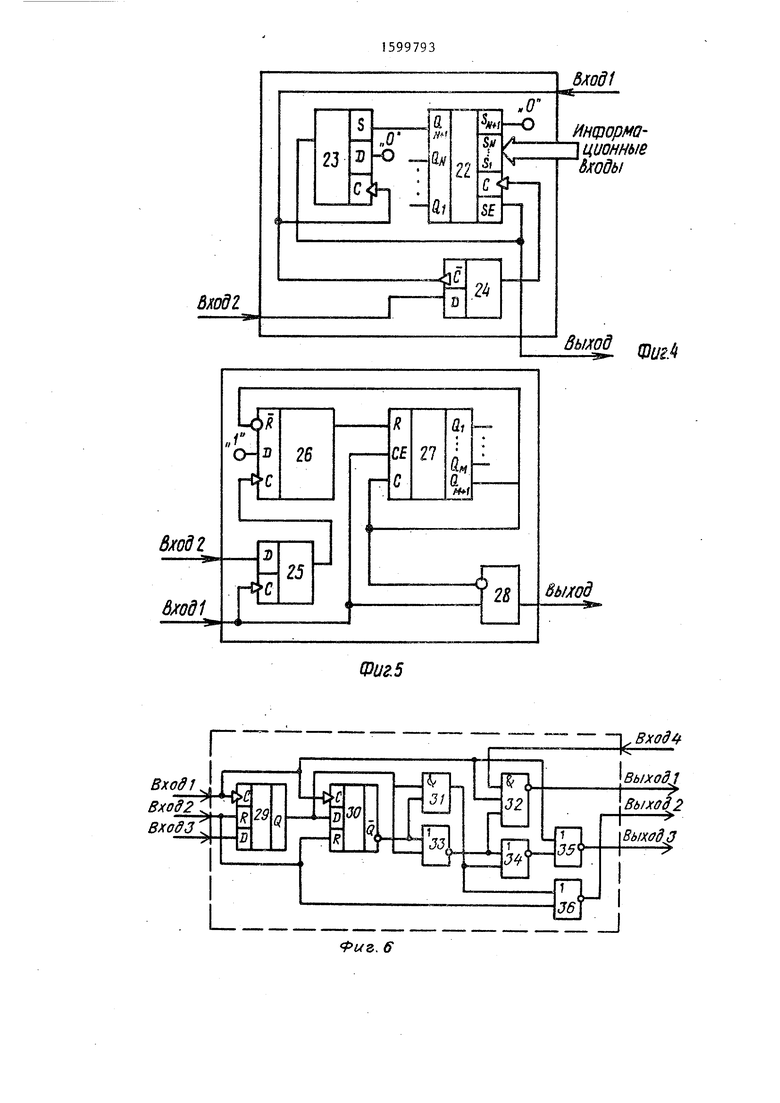

Элемент 7 блокировки (фиг.7) содержит два элемента И-НЕ 37,38, элемент ИЛИ 39, три элемента ИЛИ-НЕ 40-42, причем входы элемента И-НЕ 37

попарно соединены с входами элемента ИЛИ 39 и являются информационными входам элемента блокировки 7а Выход элемента И-НЕ 37 соединен с первым входом элемента ИЛИ-НЕ 40, а выход

элемента ИЛИ 39 соединен, с первьм вхо- дом элемента ИЛИ-НЕ 42, второй вход которого соединен с вторым (инверсным) входом элемента ШШ-НЕ 40 и является первым входом элемента 7 блокировки, а выход подключен к первому входу элемента ИЛИ-НЕ 41, второй вход которого соединен с выходом элемента ИЛИ-НЕ 40, а выход подключен к первому входу элемента И-НЕ 38, вто-

рой вход которого является вторым входом элемента 7 блокировки.

Формирователь 6 разностной частоты ;фиг.8) содержит четыре элемента И 43-46, элемент ИЛИ 47 и четыре триг-.

гера 48-51, причем первый вход элемен- та И 43, является первым входом синхронизации, а второй - суммирующий вход формирователя 6 разностной частоты - подключен к тактовым входам триггеров 48 и 49, выход соединен с входами сброса триггеров 50 и 51 и первым входом элемента И 45, выход... которого соединен с первым входом элемента ИЛИ 47о Второй вход подключен к выходу триггера 49, информационный вход которого соединен с выходом триггера 48 и является первым выходом формирователя 6 разностной частоты, а вход сброса соединен с вхо

дом сброса триггера 48, выходом элемента И А4 и первым входом элемента И 46,выход которого соединен с вто рым входом элемента РШИ 47, Второй вход подключен к выходу триггера 51, информационный вход которого подключен к выходу триггера 50, а тактовый вход является вычитающим входом форми рователя 6 разностной частоты и соеди нен с тактовым входом триггера 50 и первым входом элемента И 44, второй вход которого является вторым входом синхронизации формирователя 6 разност ной частоты, причем на информационные входы триггеров 48 и 50 подается уровень 1, а выход элемента ИЛИ 47 является вторым выходом формирователя 6 разностной частоты

Блок 14 памяти выполнен по известной схеме.регистра с параллельной загрузкой, причем первый вход блока 1 памяти является входом записи с инфор мационных входов, а второй вход - вхо дом начальной установки на информационных выходах блока 14 памяти, заранее заданного фиксированного числового кода П,о

В примере конкретного выполнения устройства реверсивный счетчик 5, ко- доуправляемые делители частоты 10- 12, блок 14 памяти и двухканальный мультиплексор 13 имеют одинаковое количество разрядов, равное пяти, а числовой код П, имеет величину

П,

, Н-1

+ 1 100002 17,0

1{ - 1-lW4J w W2 I/,

Для упрощения математических выкладок в описании используется двоич- 11ая система исчисления, в которой чис лу 00600 2 соответствует число 1 ,р , числу 00001 - 2,0 и т«д.

Работа устройства осуществляется в двух режимах

В режиме Настройка измеряется .номинальное значение отношения частот по.следовательностей импульсов,подаваемых на входные шины 1 и 2, а в режиме Работа измеряется величина отношения частот последовательностей импульсов, подаваемых .на вход ные шины 1 и 2, приведенной к ее номинальному значению, измеренному в режиме Настройка.

В режиме Настройка устройство ра ботает следующим образом.

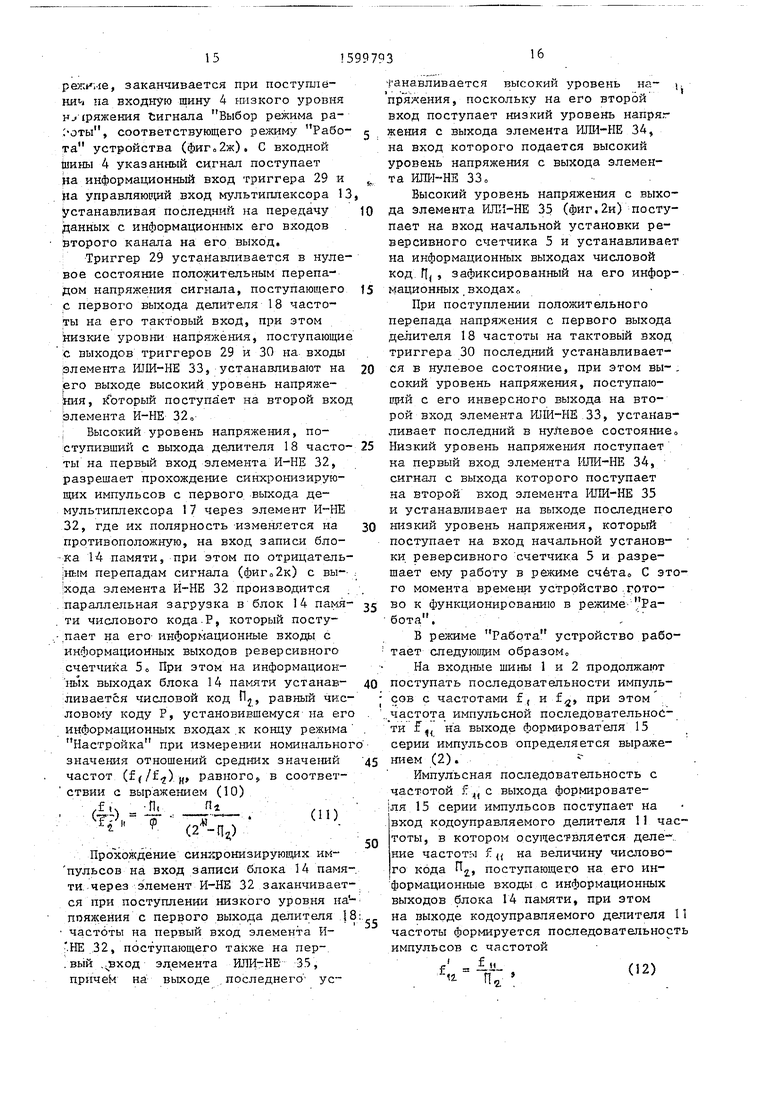

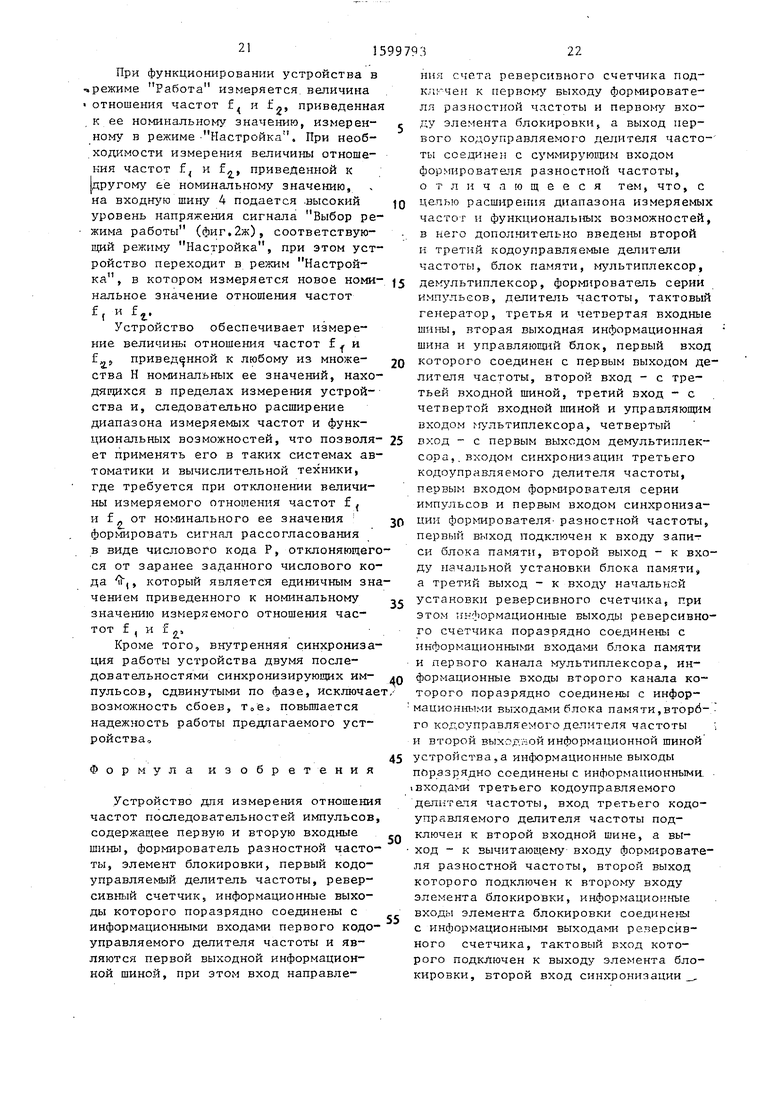

Тактовый генератор 16 нырабаты- вает-тактовые импульсы (фиг.2а) с частотой fp и скважностью, равной

10

25

двум, поступающие на вход делителя 18 частоты и на второй вход демульти- плексора 17, при этом на втором выходе делителя 18 частоты вырабатывается сигнал с частотой /2 (фиг.. 26), который поступает на первый (управляющий) . вход демультиплексора 17. Демуль- типлексор 17 комментирует импульсы так- |0 тового генератора 16 с частотой f./2 при этом на его выходах формируются две импульсные последовательности с частотой fjj/2, скважностью, равной четырем, и сдвинутые по фазе одна относительно другой на половину периода Данные импульсные последовательности используются для синхрониза- ци и устройства (фиг,2в,г).

На первом выходе делителя 18 час- готы вырабатывается сигнал с частотой д/2 (на фиго2д этот си1 нал показан при ) и поступает на первый вход управляющего блока 195 на четвертый вход которого поступают синхронизирующие импульсы с первого выхода демультиплексора I7, а на третий вход (входную имну 4 ) подается сигнал Выбор режима работы (фиг,2ж), высокий уровень которого соответст- 30 вует режиму Настройка устройства

При поступлении на второй вход управляющего блока 19 с входной шины 3 сигнала Начальная установка в виде импульса положительной полярности (фиго2е) триггеры 29 и 30 сбрасываются, а сигналы с их выходов подаются на входы элемента И 31 , на выходе - которого устанавливается низкий уровень напряжения, поступаюпщй на вто- О рой вход элемента ИЛИ-НЕ 36 На его выходе формируется импульс отрица гель- ной полярности с длительностью, равной длительности сигнала Начальная установка (фиг.2з). Этот импульс с 15 выхода элемента ИЛИ-НЕ 36 поступает на вход начальной установки блока 14 памяти и низким уровнем напряжения устанавливает на его. информационных выходах фиксированное значение ко- 50 да П,, равное 10000.

При поступлении на первый вход управляющего блока 19 положительного перепада напряжения, поступающего с первого выхода делителя 18 частоты 55 (, триггер 29 устанавливается в единичное состояние и сигнал с его выхода устанавливает элемент И 31 также в единичное состояние Сигнал с выхода элемента И 31 устанавливает

35

на выходе элемента ИЛИ-1№ 36 напряжение низкого уровня, при этом на информационных выходах блока 14 памя- ти сохраняется числовой код П рав- ный 10000.

В то же время высокие уровни напряжения с выходов триггеров 29 и 30 поступают на входы элемента ИПИ-НЕ 33 и устанавливают на его выходе низкий уровень напряжения, который поступает на второй вход элемента ШШ-НЕ 34, на первый вход .которого поступает высокий уровень напряжения с выхода элемента И 31. На.выходе элемента 1ШИ-НЕ 34 устанавливается напряжение низкого уровня, которое поступает на второй вход элемента РШИ-НЕ 35, при этом при поступлении на первый вход управляющего блока 19 импульса отрицательной полярности (фиго.д), он поступает на первый вход элемента ИЛН-НЕ 35 и передается на его выход в инвертированном виде. Импульс положительной полярности (фиго2и) с выхода элемен- та ИЛИ-НЕ 35 поступает на вход начальной установки реверсивного счетчика 5 и высоким уровнем напряжения устанавливает на его информационнь1х выходах числовой код П, , равный 10000, зафиксированный на его информационных входах о При поступлении очердного положительного перепада напряжения на первый вход управляющего блока 19 (фиго 2д), триггер 20 устанавливается в единичное состояние при этом на его инверсном выходе устанавливается низкий уровень напряжения, на втором выходе управляющего блока 19 устанавливается высокий уро- вень напряжения (фиго2з). а на третьем выходе - низкий уровень напряжения (фиг.2и). С этого момента времени устройство готово к работе в режиме. Настройка.

На входную шину 1 поступает последовательность импульсов с частотой f, откуда она подается на информационный вход триггера 25, который устанавливается в единичное состояние при наличии высокого уровня напряжения на его информационном входе по переднему Фронту синхронизирующего импульса (фиг.2в), поступающего с первого выхода демультиплексора 17 на его тактовы.й вход. Положительный перепад напряжения, поступающий с выхода триггера 25 на тактовый вход триггера 26, устанавливает последний

в единичное состояние. Высокий уровень напряжения, поступаю ий с выхода триггера 26 на вход сброса счетчика 27, устанавливает информационные выходы последнего в нулевые состояния, при этом напряжение низкого уровня, поступающее с выхода (М+1)-го разряда счетчика 27 на инверсный вход элемента И 28 и инверсный вход сброса триггера 26, устанавливает по- |Следний в нулевое состояние и разрешает прохождение через элемент И 28 синхронизирующих импульсов на вход кодоуправляемого делителя 11 частоты. Напряжение низкого уровня, поступающее с выхода триггера 26 на вход сброса счетчика 27, и напряжение низкого уровня,поступающее с выхода (М+1)-го разряда счетчика 27 на его тактовый вход, разрешает последнему счет синхронизирующих импульсов, поступающих на его вход разрешения счета, осуществляемый при поступлении задних фронтов указанных синхроимпульсов на его вход разрешения счета. При появлении на выходе (М+1)-го разряда счетчика 27 напряжения высокого уровня, оно блокирует дальнейший счет по тактовому входу счетчика 27 и запрещает прохождение синхронизирующих импульсов с первого выхода демультиплексора 17 на вход кодоуправляемого делителя 11 частоты через элемент И 28, при этом с момента обнуления счетчика 27 до момента его блокирования на выходе элемента И 28 формируется пачка из (R 2 импульсов, Тэв, средняя частота f. импульсной последовательности на выходе формирователя 15 серии импульсов

. „ -ф., 2 ,.(2)

При поступлении импульсной последовательности с частотой f на второй вход кодоуправляемого делителя 11 частоты, вычитающий счетчик 20 уменьшает свое содержимое до появления на его выходе обратного переполнения высокого уровня напряжения, при этом .положительный перепад устанавливает триггер 21 в единичное состояние (), находившийся ранее в нулевом состоянии за счет поступления на его вход сброса синхронизирующих импульсов с второго выхода демульти- Ьлексора 17. Появившийся на прямом рыходе триггера 21 высокий уровень напряжения записывает в счетчик 20

числовой код П,, 10000, поступающий на его информацион1-1ые входы . с информационных выходов блока 14 па мяти, а блгокайший синхронизирующий импульсJ поступающий на вход сброса триггера 21, устанавливает его в нуле вое состояние, разрешающее счет счет- чику 20 о

: Таким образом, кодоуправляемый де|1итель 11 частоты делит частоту f, SB П, раз, при ЭТОМ; на его выходе формируются импульсы положительной по- 1ярности (фиго 2л), следующие с часто- той

,(3)

f г

П,

Передний фронт которых совпадает с Передним фронтом синхронизирующих Импульсов с -первого выхода дe гyльти- Ьлексора 17, а задний фронт - с передним фронтом синхронизирующих импульсов с второго выхода демулультиплек- сора 17о

Импульсы с выхода кодоуправляемого делителя 1 частоты поступают на вход кодоуправляемого делителя 10 частоты, работающего аналогично„ Коэффициент деления кодоуправляемого делителя 10 частоты равен числовому коду Р на информационных выходах реверсивного счетчика 5, а частота на его выходе

llJ(4) 35

40

45

3 р

причем передуши фронт его выходных myльcoв (фиго 2л) также совпадает с Передним фронтом синхронизирующих ьйтульсов с первого выхода демульти- плексора 17, а задний фронт - с передним фронтом синхронизирующих импульсов с второго выхода демульти- плексора 17о

Импульсы с выхода кодоуправляемого делителя 10 частоты поступают на суммирующий вход формирователя 6 разностной частоты, при этом частота их следования с учетом (2)-(4) равна .

.fc -|:f- (5) 50

в то же время на входную шину 2 поступает импульсная последовательность с частотой ,,, откуда она подается на информационный вход триггера 24, который устанавливается в еди- ничное состояние при одновременном

поступлении высокого уровня напряже- Н11я на его информационный вход

с

0

0

5

0

5

0

5

0

(фиго2н) и заднего фронта сингфоии- зр рующего импульса, поступающего с первого выхода демультиплексора 17 на его тактовый входр Положительный, перепад напряжения, поступагош;1й с выхода триггера 24 на тактовый вход суммирующего счетчика 22, увеличивает состояние последнего на единицу, причем процесс подсчета входтшх импульсов с частотой f продолжается до появления на выходе прямого переполнения суммирующего счетчика 22 высокого уровня напряжения, поступаю- рдего на S-вход установки тригге- .ра 23. Триггер 23 устанавливается в единичное состояние (фиг,2о), высокий уровень напряжения с его выхода поступает на вход записи суммирующего счетчика 22 и производит запись в него числового кода Р с информационных входов последнего, которые подключены через мультиплексор 13 к информационным выходам реверсивного рчетчика 5, при этом мультиплексор 13 за счет подачи на его управляющий вход высокого уровня напряжения с входной щины 4 включен на передачу данных с его информационных входов первого канала на его выходо На выходе прямого переполнения суммирующего счетчика 22 устанавливается низкий уровень напряжения, при этом триггер 23 устанавливается в нулевое состояние (фиг.2о) при поступлеюти на его тактовый вход переднего фронта ближайшего синхронизируюрдего импульса с первого выхода демультиплексора 17,

Таким образом, кодоуправляемый делитель 12 частоты имеет коэффициент деления

, (б)

где N - количество разрядов информационных входов кодоуправляемого делителя 12 частоты, частота импульсной последовательности, поступающей с выхода кодоуправляемого делителя частоты 12 на вычитающий вход формирователя 6 разностной частоты

f.

(7)

причем для представления коэффициента D в десятичной системе исчисления, необходимо выполнить вычитание (2 -Г) в двоичной системе а его результат представить в десятичной системе исчисления о

Импульс положительной полярности, поступающий на суммирующий вход формирователя 6 разностной частоты, ус танавливает триггер А8 в единичное состояние и разрешает прохождение одного совпадающего с ним синхронизирующего импульса с первого выхода де- мультиплексора 17 через элемент И 43, сигнал с выхода которого (фиг,2м) сбрасывает триггеры 50 и 51, при этом высокий уровень напряжения с выхода триггера 48 поступает на первый вход реверсивного счетчика 5 и устанавливает суммирующий режим его работы Следующий импульс, поступивший на суммирующий вход формирователя 6 разностной частоты, при отсутствии импульса на его вычитающем входе, устанавливает триггер 49 также в единично состояние, которое разрешает прохождение одного синхронизирующего импульса, .совпадающего с входным импульсом, с выхода элемента И 43 через элемент И 45 на вход элемента ИЛИ 47, откуда он подается через элемент 7 блокировки на тактовый вход реверсивного счетчика 5, увеличивая его состояние на единицу

При поступлении на вычитающий вход формирователя 6 разностной частоты импульса с выхода кодоуправляемого делителя 12 он устанавливает триггер 50 в единичное состояние и разрешает прохождение одного совпадающего с ним синхронизирующего импульса с второго выхода демультиплексора 17 через элемент И 44, сигнал с выхода кр- торого (фиг.2п) сбрасывает триггеры 48 и 49, при этом низкий уровень на- пряжения на выходе триггера 48 уста- навливает вычитающий режим работы реверсивного счетчика 5, а очередной импульс, поступающий на вычитающий вход формирователя 6 разностной часто ты, устанавливает триггер. 51 в единичное состояние, которое разрешает прохождение синхронизирующего импульса, совпадающего с входным импульсом, с выхода элемента И 44 через эле- мент И 46 на вход элемента ИЛИ 47, откуда он подается через элемент 7 блокировки на тактовый вход реверсивного счетчика 5, уменьшая его состояние на единицу

При поочередном поступлении импульсов на суммирующий и вычитающий входы .формирователя 6 разностной частоты, на выходе элемента ИЛИ 47 импульсы не появляются, поскольку триггеры 49 и 51 находятся в нулевом состоя НИИо

Таким образом, на втором выходе формирователя 6 разностной частоты вырабатывается импульсная последовательность с частотой

lf,.-fz,l

(8)

а возможность сбоев при совпадении частоты сигналов на вычитающем и суммирующем его входах исключена за счет устранения совпадения фаз этих сигналов путем синхронизации формиро вателя.6 разностной частоты

В режиме Настройка на входные шины 12 поступают импульсные последовательности с частотами f .j и f, величина отношения средних значений которых остается неизменной до окончания режима Настройка и является но шнальным значением измеряемого отношения средних значений f и f.При этом последовательность импулсов с частотой fj поступает с второг выхода фop шpoвaтeля 6 разностной частоты через элемент 7 блокировки на тактовый вход реверсивного счетчика 5 и изменяет его состояние до тех пор, пока устройство не войдет в установившийся режим, при котором на втором выходе формирователя 6 разностной частоты прекращается формирование импульсов 3 Тогда с учетом (8) дпя установившегося режима спра- ведпиво равенство:

f,3-f,0.

(9)

откуда следует, что отношение средних значений частот fj и f с учетом (5)-(7), равно

fj Л1

f; (f

()

(10)

Причем равенство (10) справедливо с точностью, обусловленной дискретным характером измерения.

Величина числового кода Р, поступающего с информационных выходов реверсивного счетчика 5 на выходную информационную .шину 8 в режиме Настройка, в неявном виде характеризует номинальное значение измеряемого отношения средних значений частот f, и f. импульсных последовательностей, определяемое выражением (10),

Режим Настройка работы устройства, находящегося в установившемся

режиме, заканчивается при поступле- HHt-i па входг-гую шину 4 низкого уровня Hj-фяжения Ъигнала Выбор режима работы, соответствующего режиму Рабо- та устройства (фиго2ж). С входной шны 4 указанный сигнал поступает на информационный вход триггера 29 и на управляюпщй вход мультиплексора 13 устанавливая последний на передачу данных с информационных его входов второго канала на его выход,

Триггер 29 устанавливается в нулевое состояние положительным перепадом напряжения сигнала, поступающего с первого выхода делителя 18 частоты на его тактовьй вход, при этом Низкие уровни напряжения, поступающие с выходов триггеров 29 и 30 на. входы элемента ШШ-НЕ 33, устанавливают на (ЕГО выходе высокий уровень напряже- йия, Который поступает на второй вход Ьлемента И-НЕ 32,,; Высокий уровень напряжения, по- ступивший с выхода делителя 18 часто- ты на дервьй вход элемента И-НЕ 32, разрешает прохождение синхронизирующих импульсов с первого, выхода де- мультиплексора 17 через элемент И-НЕ 32, где их полярность -изменяется на противоположную, на вход записи блока 14 памяти, при этом по отрицатель- ;Ным перепадам сигнала (фиго2к) с вы-- |хода элемента Й-НЕ 32 производится .

.параллельная загРузка в блок 14 памя- ти числового кода.Р, который посту- ,пает на его- информационные входы с информационных выходов реверсивного счетчика 5 о При этом на информацион- ных выходах блока 14 памяти устанав- ливается числовой код П, равный чис- ловому коду Р, установившемуся на ег информационных входах .к концу режима Настройка при измерении номинально значения отношений средних значений частот () (,, равного в соответствии с выражением (10)

(ll) f - 1,

П,

Ji

()

(П)

Прохождение сиш-фонизирующих им- пульсов на вход записи блока 14 памяти..через элемент И-НЕ 32 заканчивает-. ся при поступлении низкого уровня на - ппяжения с первого выхода делителя ,18; частоты на первый вход элемента И- НЕ 32, поступающего также на пер- . вый ,вход элемента ИЛИ-НЕ- 35, причей на выходе .последнего ус ...

5 0

5 О

5

0 . - 5

0

5

ганавливается высокий уровень на- ,

пряжения, поскольку на его второй вход поступает низкий уровень напряг жения с выхода элемента ИЛИ-НЕ 34, на вход которого подается высокий уровень напряжения с выхода элемента ИЛИ-НЕ 33 оВысокий уровень напряжения с выхода элемента ИШ -НЕ 35 (фиг,2и) поступает на вход начальной установки реверсивного счетчика 5 и устанавливает на информационных выходах числовой код П(5 зафиксированный на его информационных . входах о

При поступлении положительного перепада напряжения с первого выхода делителя 18 частоты на тактовый вход триггера 30 последний устанавливается в нулевое состояние, при этом вы- . сокий уровень напряжения, поступающий с его инверсного выхода на второй вход элемента ШШ-НЕ.33, устанавливает последний в нулевое состояниео Низкий уровень напряжения поступает на первый вход элемента 1-1ПИ-НЕ 34, - сигнал с выхода которого поступает на второй вход элемента ЮТИ-НЕ 35 и устанавливает на выходе последнего низкий уровень напряжения, который поступает на вход начальной установ- ки реверсивного счетчика 5 и разрешает ему работу в режиме счёта С этого момента времещ- устройство .готово к функционированию в режиме- Ра бота.,

В режиме Работа устройство рабо тает следуюидам образоМо

На входные шины 1 и 2 продолжают поступать последовательности импульсов с частотами f, и f,, при этом

„частота импульсной последовательности н а выходе формирователя 15 серии имщшьсов определяется выражением (2).

Импульсная последовательность с частотой f .|, с выхода формировате- |ля 15 серии импульсов поступает на вход кодоуправляемого делителя 11 частоты, в котором осуществляется деле-, ние частоты f. (j на величину числового кода П, поступающего на его информационные входы с информационных выходов блока 14 памяти, при этом на выходе кодоуправляемого дарителя 11 частоты формируется последовательность импульсов с частотой

/ 4-i,t ,

которая поступает на второй вход кодо управляемого делителя 10 частоты, осу 1цествляю1чего деление частоты на величину числового кода Р, который по- ступает на его информационные входы с информационных выходов реверсивного счетчика 5

На выходе код&управляемого делителя 10 частоты формируется последо- вательность импульсов с частотой

з . (13)

или с учетом (2) и (12) Ф-f V

(14)

f --: Пг Р

которая поступает на суммирующий вход формирователя 6 разностной частоты,

В то же время частота f. импульс- ной последовательности, поступающей н

;в-торой вход кодоуправляемого делите-..

ля 12 частоты, делится на коэффициент

ID, равный с учетом (6):

2

(15)

поскольку, на его информационные -входы поступает числовой код инфор- мационных выходов блока 14 памяти через мультиплексор 13, при этом часто- та на выходе кодоуправляемого делителя частоты 12

- |i ,.

-2f

D

(16)

35

Импульсная последовательность.с частотой fg, с выхода кодоуправляемого делителя 12 частоты по.ступает на вычитающий вход формирователя 6 раз- ностной частоты, на втором выходе ко торого формируется импульсная после- довательность с разностной частотой

F -f t 21

(17)

которая поступает через элемент 7 блокировки на тактовый вход реверсивного 5 счетчика 5 и изменяет его состояние до тех пор, пока устройство при условии неизменного отношения средних значений частот f. и fj не войдет в , установившийся режим, в котором час- 50 тота fj равна нулю.

Тогда с учетом (17) для установив- шегося режима справедливо равенство;

f -f -n f 1% 41 (18)

Отсюда с учетом (14) и (16) находят величину числового кода Р, установившегося на информационных выхдах реверсивного счетчика 5:

Р fi . (:. (,9)

Ij П

Умножив числитель и знаменатель равенства (19) на П, и подставив в него выражение (II), получают fi/fg

-ТТГ717

Из выражения

(20)

н , (20) следует, что

в режиме Работа величина числового кода Р на информационных выходах реверсивного счетчика 5 и на выходной информационной шине 8 равна постоян ной величине кода П, умноженной на величину отновгения частот f и f, приведенную к ее номинальному значению, измеренному в режиме Настройка. При сохранении неизменного отношения частот , и f

5

Q

5

50

f4 Д«;

f.

)и

(21)

fl J-2

при переходе из режима Настройка в режим: Работа устройство в режиме Работа начинает функционировать jcpasy в установившемся режиме, по- 1скольку при указанном переходе в реверсивный счетчик 5 записывается код П,, соответствующий равенству (21) и являющийся единичным значением при-. веденного к номинальному значению измеряемого отношения частот f, и f,

В режиме Работа на выходную информационную шину 9 поступает с информационных выходов блока 14 памяти числовой код П, который в неявном виде, в соответствии с выражением (11) определяет величину номинального значения измеряемого отношения частот f, и f.

в режиме Работа относительная погрешность измерения приведенного к номинальному значению отношения частот f, и fо

1

р Р .

(22)

а диапазон измерения указанного отношения составляет

(f./fz).

м

(23)

п, - (, - п,

в режиме Настройка относительная погрешность о. измерения номинального значения отношения частот , и f для; « ,

где

У

(24)

19 учетом выражения (Ю)

8 - ) °к x-(i-x)

1599793

(25)

р кр н г и и и н н л

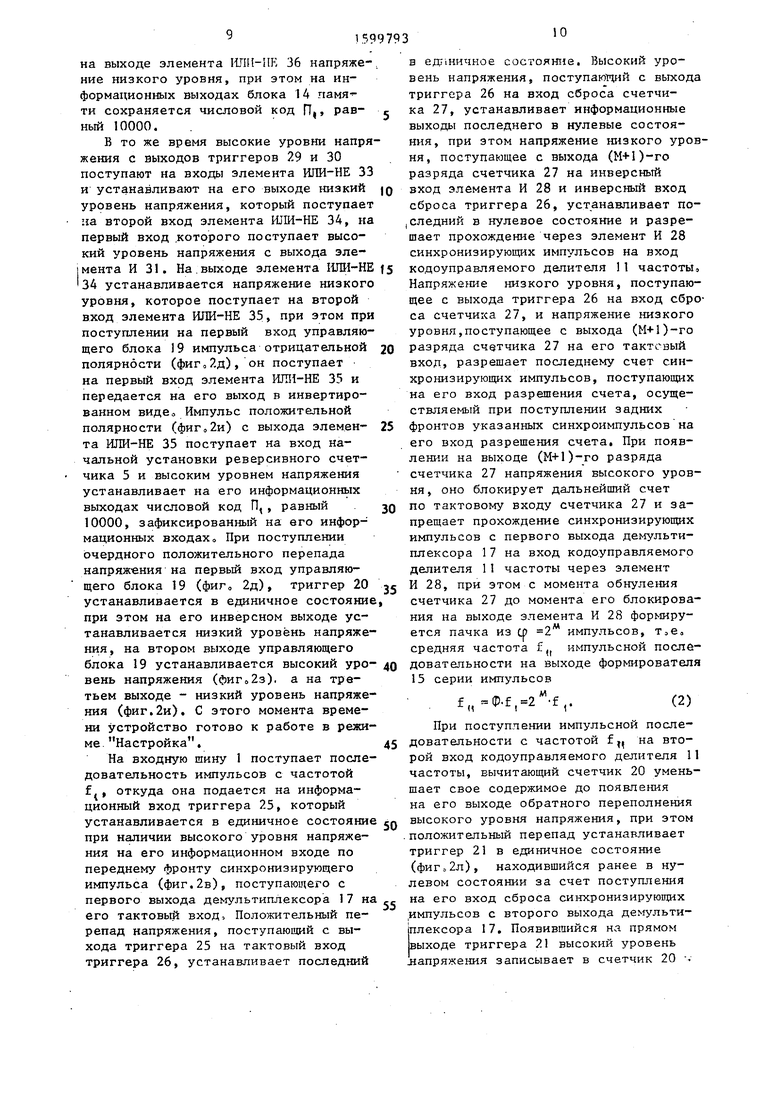

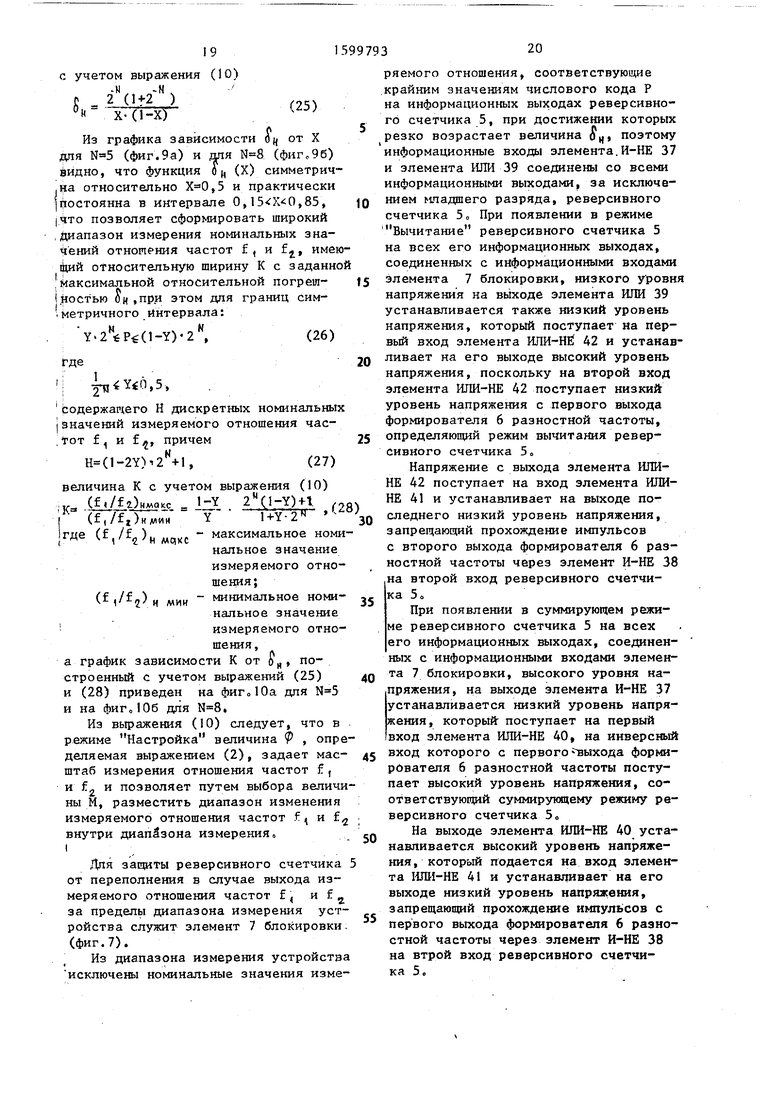

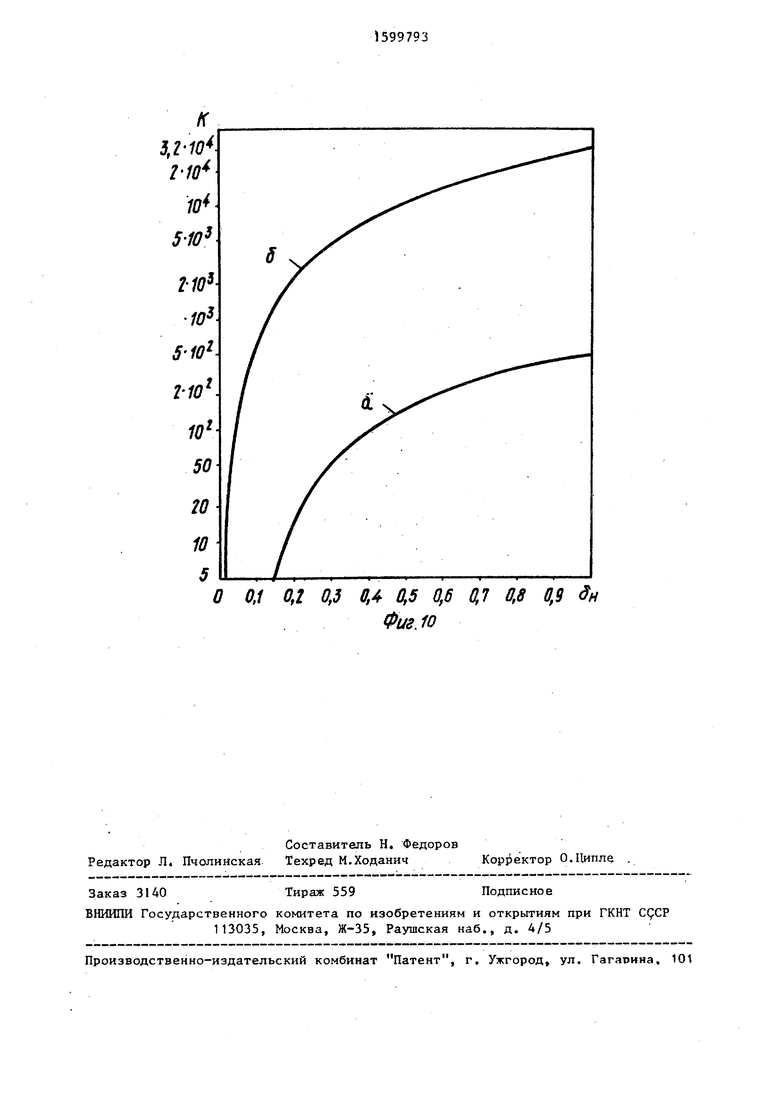

Из графика зависимости о от X дня (фиг.9а) и для (фиг.9б) йидно, что функция 0(, (Х) симметрич- ijia относительно и практически постоянна в интервале 0,,85, что позволяет сформировать широкий

.диапазон измерения номинальных значений отнотекия частот f , и fj,, имею- 1|щй относительную ширину К с заданной

максимальной относительной погреш-

(.ностью S M ,пр.и этом для границ сим метричного интервала:

(1-Y)2

(26)

Г Де

1

,5.

coдepжap ero Н дискретных номинальных j значений измеряемого отношения час- Тот f и fл, причем

H(1-2Y),(27)

величина К с учетом выражения (10)

.. (fi/fa)HMQ.c 1-Y 24l-y)n (2а

(f7/f xWH7 Y i+Y-2-

где () максимальное номинальное значение измеряемого отношения;(f ,) „„J, - минимальное номи-

нальное значение

измеряемого отношения,

а график зависимости К от fr, построенный с учетом выражений (25) и (28) приведен на фигоЮа для и на фиГоЮб для ,

Из выражения (10) следует, что в режиме Настройка величина Р , определяемая выражением (2), задает мае- штаб измерения отношения частот f, тл f., и позволяет путем выбора величины М, разместить диапазон изменения

измеряемого отношения частот внутри диапазона измерения

и f.

Для защиты реверсивного счетчика 5 от переполнения в случае выхода измеряемого отношения частот f и f за пределы диапазона измерения устройства служит элемент 7 блокировки- (фиг.7).

Из диапазона измерения устройства исключены номинальные значения изме20

5

0

5

зо

дО

45

50

55

ряемого отношения соответствующие крайним значениям числового кода Р на информационных выходах реверсивного счетчика 5, при достижении которых резко возрастает величина Оц поэтому информационные входы элемента.И-НЕ 37 и элемента ИЛИ 39 соединены со всеми информационными выходами, за исключением младшего разряда, реверсивного счетчика 5 о При появлении в режиме Вычитание реверсивного счетчика 5 на всех его информационных выходах, соединенных с информационными входами элемента 7 блокировки, низкого уровня напряжения на выходе элемента ИЛИ 39 устанавливается также низкий уровень напряжения, который поступает на первый вход элемента ИЛИ-НЁ 42 и устанавливает на его выходе высокий уровень напряжения, поскольку на второй вход элемента ИЛИ-НЕ 42 поступает низкий уровень напряжения с первого выхода формирователя 6 разностной частоты, определяющий режим вычитания реверсивного счетчика 5

Напряжение с выхода элемента ШШ- НЕ 42 поступает на вход элемента ИЛИ- НЕ 41 и устанавлива ет на выходе последнего низкий уровень напряжения, запрещающий прохождение импульсов с второго выхода формирователя 6 разностной частоты через элемент И-НЕ 38 на второй вход реверсивного счетчика 5

При появлении в суммирующем режиме реверсивного счетчика 5 на всех его информационных выходах, соединенных с информационными входами элемента 7 блокировки, высокого уровня напряжения, на выходе элемента И-НЕ 37 устанавливается низкий уровень напряжения, который поступает на первый вход элемента ИЛИ-НЕ 40, на инверсный вход которого с первого выхода формирователя 6 разностной частоты поступает высокий уровень напряжения, соответствующий суммирующему режиму реверсивного счетчика 5.

На выходе элемента ИЛИ-НЕ 40 устанавливается высокий уровень напряжения, который подается на вход элемента ИЛИ-НЕ 41 и устанав:щвает на его выходе низкий уровень напряжения, запрещающий прохождение импульсов с первого выхода формирователя 6 разностной частоты через элемент И-НЕ 38 на втрой вход реверсивного счетчика 5,

При функционировании устройства в режиме Работа измеряется величина отношения частот f и fл, приведенная к ее номинальному значению, измеренному в режиме- Настройка. При необходимости измерения величины отношения частот f. и fл, приведенной к

h

to

15

ругом ее номинальному значению, на входную шину 4 подается .высокий уровень напряжения сигнала Выбор режима работы (фиг,2ж), соответствующий режиму Настройка, при этом устройство переходит в режим Настройка, в котором измеряется новое номинальное значение отношения частот f, и f.

Устройство обеспечивает измерение величины отношения частот f , и f ,, приведенной к любому из множества Н номинальных ее значений, находящихся в пределах измерения устройства и, следовательно расширение диапазона измеряемых частот и функциональных возможностей, что позволя- 25 ет применять его в таких системах автоматики и вычислительной техники, где требуется при отклонении величины измеряемого отношения частот f и f„ от номинального ее значения

20

30

35

f от

формировать сигнал рассогласования в виде числового кода Р, отклоняющегося от заранее заданного числового кода i,, который является единичным значением приведенного к номинальному значению измеряемого отношения частот f , и f 2. . Кроме того, внутренняя синхронизация работы устройства двумя последовательностями синхронизирующих им- 0 пульсов, сдвинутыми по фазе, исключает,- возможность сбоев, Тое, повышается надежность работы предлагаемого уст- ройствао

Формула изобретения

Устройство для измерения отношения частот последовательностей импульсов, содержащее первую и вторую входные шины, формирователь разностной частоты, элемент блокировки, первый кодо- управляемый делитель частоты, реверсивный счетчик, информационные выходы которого поразрядно соединены с информационнь ш входами первого кодо- управляемого делителя частоты и являются первой выходной информационной шиной, при этом вход направлея to

15

2520

30

35

. 0т,-

45

50

55

ния счета реверсивного счетчика под- клгчеп к первом выходу формирователя разностной частоты и первоьту входу элемента блокировки, а выход первого кодоуправляемого делителя часто- ты соединен с суммирующим входом формирователя разностной частоты, отличающееся тем, что, с целью расширения диапазона измеряемых частот и функциональных возможностей, в него дополнительно введены второй и третий кодоуправляемые делители частоты, блок памяти, мультиплексор, демультиплексор, формирователь серии импульсов, делитель частоты, тактовый генератор, третья и четвертая входные шины, вторая выходная информационная шина и управляющий блок, первый вход которого соединен с первым выходом делителя частоты, второй вход - с третьей входной шиной, третий вход - с четвертой входной шиной и управляющим входом м льтиплексора, четвертый вход - с первым выходом демультиплек- сора., входом синхронизации третьего кодоуправляемого делителя частоты, первым входом формирователя серии импульсов и первым входом синхронизации формирователя- разностной частоты, первый выход подключен к входу записи блока памяти, второй выход - к входу начальной установки блока памяти, а третий выход - к входу начальной установки реверсивного счетчика, при этом ь нформационные выходы реверсивного счетчика поразрядно соединены с информационными входам.и блока памяти и первого канала мз льтиплексора, информационные входы второго канала которого поразрядно соединены с инфор- мацион1г ыми выходами блока памяти,вторб-- го кодоуправляемого делителя частоты и второй вых-од;-5ой информационной шиной устройства,а информационные выходы поразрядно соединены с информационными - 1 входами третьего кодоуправляемого делитетя частоты, вход третьего кодоуправляемого делителя частоты подключен к второй входной шине, а выход - к вычитающему входу фopмзipoвaтe- ля разностной частоты, второй выход которого подключен к второму входу элемента блокировки, информационные входы элемента блокировки соединер&1 с информационными выходами реверсивного счетчика, тактовый вход которого подключен к выходу элемента блокировки, второй вход синхронизации ,

формирователя разностной частоты об)- единен с входами синхронизации первого и второго кодоуправляемых делителей частоты и вторым выходом демуль- гиплексора, первый вход которого соединен с вторым выходом делителя частоты, а второй вход объединен с выходом тактового генератора и входом

sPi/. 2

BJCOd2

V

инсрормоционные Входы

Фиг.

делителя частоты, второй вход формирователя серии импульсов соединен с первой входной шиной а выход - с входом второго кодоуправляемого делителя частоты, выход которого подключен к входу первого кодоуправляемого делителя частоты.

вход1

с I д 1/

L±

1

Выход

Риг. 6

Фиг.5

1599793

Фиг. 7

Фиг,. 8

0,1 0,1 0,S 0,4 0.5 0,1 0.8 0,9 X Фи.9

Bxodz

)(Од1

/Г

,2-10 2-10

10 5 W

2-W

10

S 10

2 W

10 50

20 10

0 0,1 0,2 0,3 0,4 0,5 0,6 0,7 0.8 0,9 //

0U2,fO

Составитель H. Федоров Редактор Л. Пчолияская. Техред М.Ходанич Корректор О.Ципле .

Заказ 3140

Тираж 559

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ CQCP 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Устройство для измерения отношения частот последовательностей импульсов | 1985 |

|

SU1262405A1 |

Авторы

Даты

1990-10-15—Публикация

1988-08-16—Подача