(5) УСТРОЙСТВО для ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ОШИБОК

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство защиты от ошибок | 1987 |

|

SU1478362A2 |

| Устройство для настройки и контроля параметров регенератора цифровых систем связи | 1982 |

|

SU1042195A1 |

| Декодирующее устройство | 1985 |

|

SU1339894A1 |

| УСТРОЙСТВО АВТОВЫБОРА ДИСКРЕТНОГО КАНАЛА | 2011 |

|

RU2488222C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТ ПОВРЕЖДЕНИЯ НАПОРНОГО ТРУБОПРОВОДА | 1992 |

|

RU2046251C1 |

| Устройство для приема и передачи избыточных сигналов | 1981 |

|

SU976466A1 |

| Двухступенчатый параллельно-последовательный регенератор | 1985 |

|

SU1246394A1 |

| АКУСТООПТИЧЕСКИЙ АНАЛИЗАТОР СПЕКТРА | 1992 |

|

RU2024026C1 |

| Устройство для диагностики и прогнозирования отказов | 1989 |

|

SU1629898A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

I

Изобретение относится к электросвязи и может использоваться для определения коэффициента ошибок дискретных каналов связи.

Известно устройство для измерения коэффициента ошибок, содержащее последовательно соединенные анализатор ошибок и счетчик ошибок, счетчик числа, первый и второй индикаторы числа и последовательно соединенные счетчик степени и индикатор степени 1 .

Однако точность измерений известным устройством невысока.

Цель изобретения - повышение точности измерений.

Для достижения этой цели в известное устройство для измерения коэффициента ошибок введены первый триггер, счетчик циклов, последовательно соединенные блок считывания, счеУчик обратного счета,-второй триггер, клйэч, делитель и блок сравнения, первый и второй буферные регистры, элемент задержки последовательно соединенные первый элемент И, третий триггер, второй элемент И и первый элемент ИЛИ и последовательно соединенные третий элемент И и второй элемент ИЛИ, при этом выход анализатора ошибок через первый триггер соединен со вторым входом второго триггера, третий вход которого соединен с управляющими входами

10 счетчика числа, первого и второго буферных регистров и блока считывания, с первым входом первого элемента И, со входом элемента задержки и со входом счетчика циклов, на ко15торый подан сигнал цикловой синхронизации, первый и второй выходы счетчика ошибок соединены соответственно с сигнальным входом блока считывания и со вторым входом первого эле20мента ИЛИ, выход которого соединен с первым входом счетчика степени, второй вход которого соединен с выходом второго элемента ИЛИ, второй

вход которого соединен с первым выходом счетчика циклов, второй выход которого соединен со вторым входом блока сравнения, выход которого соединен со вторым.входом делителя и с сигнальным входом сметчика числа, вход установки которого соединен с третьим входом делителя и с выходом элемента задержки, первый и второй выходы сметчика числа соединены со вторыми -входами соответСтвенно первого и второго элементов И, первый и второй входы и второй выход третьего триггера соединены соответственно с первым входом третьего элемента И,. со вторым входом второго элемента И и со вторым входом третьего элемента И, соответствующие сигнальные выходы счетчика числа соответственно через первый и второй буферный регистры соединены со входами соответственно первого и второго индикаторов числа, выход ключа, на второй вход которого поданы тактовые импульсы, соединен с тактовым входом счетчика обратного счета, а на объединенные второй вход первого триггера, третий вход третьего триггера и управляющий вход счетчика степени подан сигнал сбросй

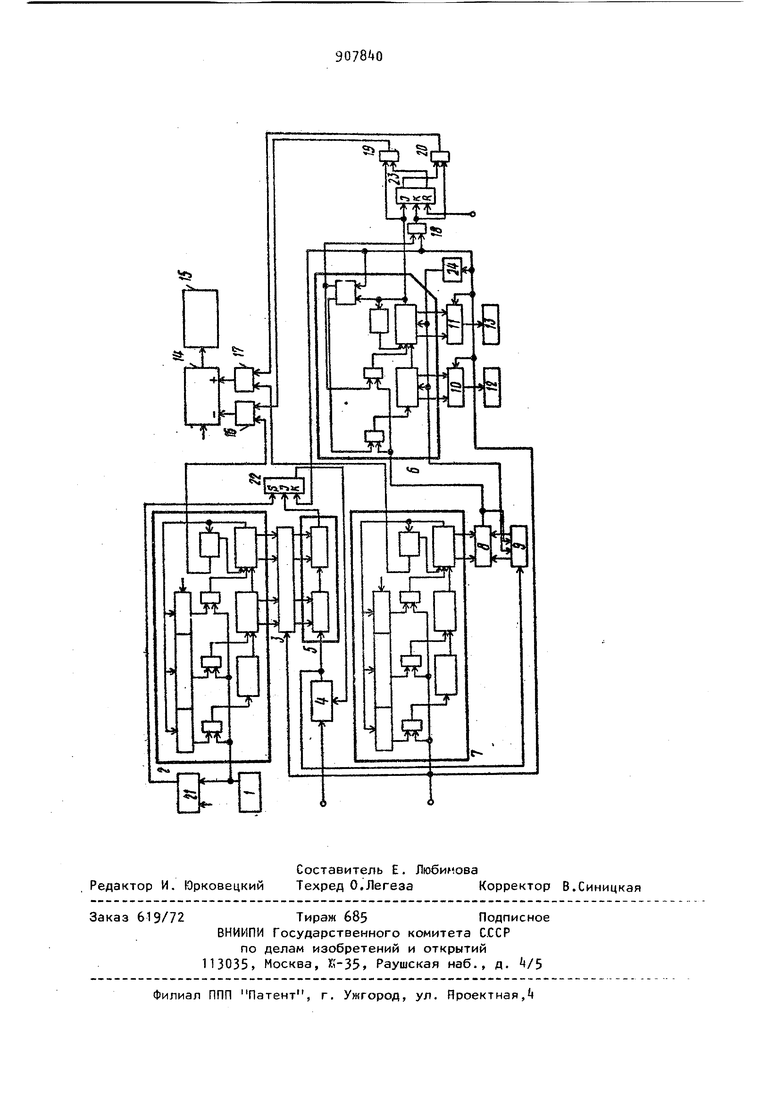

На чертеже представлена.структурная электрическая схема предлагаемого устройства.

Устройство для измерения коэффициента ошибок содержит анализатор 1 ошибок, счетчик Z ошибок, блок 3 считывания, ключ , счетчик 5 обратного счета, счетчик 6 числа, счетчик 7 циклов, блок 8 сравнения, делитель 9 первый и второй буферные регистоы 10 и 11, первый и второй индикаторы 12 и 13 числа, счетчик 1А степени, индикатор 15 степени, первый 16 и второй 17 элементы ИЛИ, первый 18, второй 19 и третий 20 элементы И, первый 21, второй 22 и третий 23 триггеры и элемент 2 задержки .

Устройство работает следующим образом.

Пусть длительность .цикла сброса равна N 100 тактов,отображение числа - двухразрядное (А,В),

При сбрюсе, привязанном во времени к циклу 1Ц, счетчик 1 устанавливается на - (1+IgN), т.е. на 10 , первый триггер 21 устанавливается в состояние, при котором на входе установки второго триггера

Li будет низкий уровень, и сигнал с его выхода закрывает ключ ,

Пусть в течение цикла с анализатора 1 поступило две ошибки. Одновременно с поступлением первой ошибки перебрасывается первый триггер 21, который снимает блокировку второго триггера 22, который в свою очередь блокировал ключ при отсутствии ошибок.

Через N тактов после сброса поступает сигнал первого цикла 1Ц,которым в буферные-регистры 10 и 11 переносится из сметчика 6 записанная информация. Третий триггер 23 не изменяет своего состояния. Этим же сигналом цикла Ш, поступающим в блок 3 осуществляется перенос накопленного количества ошибок из счетчика 2 в счетчик 5 а также пербрасывается второй триггер 22, открывая ключ 4, мерез который тактовая частота Т1-1 со входа устройства поступает на счетмик 5. вычитая из него имеющееся в нем количество ошибок. Сигналом цикла 1Ц через элемент 24 задержки сбрасывается десятичный счетчик счетчика 6 и делитель 9. Таким образом, при происходит умножение ошибок на десять, что компенсируется тем, что степень при сбросе устанавливается на 1 больше, чем Ig N.

Перенесенные две ошибки в счетчике 5 представляет двадцать ошибок, которые через ключ 4 поступают на делитель 9 представляющий собой десятичный счетчик, сбрасываемый выходным сигналом блока В. В счетчике 7 к этому моменту записан один цикл, т.е. на выходе блока 8 будет сформировано двадцать импульсов, которые поступают на вход декадного счетчика счетчика 6.Импульс заполнения декадного счетчика счетчика 6 постпает через первый элемент 18, который открыт.сброшенным третьим триггером 23 на вход вычитания счетчика 14 через первый элемент ИЛИ 16; задним фронтом импульса переводится в состояние 1 третий триггер 23,закрывая первый элемент И 18. В счетчике 6 будет записано число двадцать, которое с учетом фиксированной запятой будет представлено в дальнейшем (при поступлении следующего цикла), как число 2, В этот же период времени в счет чик 2 поступают очередные ошибки и анализатора 1. Пусть в этот период поступило еще три ошибки, т.е. суммарное количество ошибок составило пять. Импульс второго цикла поступает в счетчик 7, переносит число 2,0 в буферные регистры 10 и 11, число отображается индикаторами 12 и 13.О новременно вторым сигналом цикла 1Ц из счетчика 2 в счетчик 5 переносится пять ошибок, при этом через первый элемент И 18 импульс 1Ц не пройдет, так как он открывается задним фронтом цикла 1Ц. Вторым импульсом цикла 1Ц перебрасывается вновь второй триггер 22 открывая ключ k, через который из счетчика 5 вычитается пятьдесят импульсов. Вторым импульсом цикла 1Ц, задержанным элементом 2 задержки, сбрасывается делитель 9. После сравнения с содержимым счетчика 7, которое равно двум, на выходе блока 8 формируется двадцать пять импульсов, поступающих на счетчик 6. Аналогично, после поступления десяти импульсов на выходе счетчика 6 буде сформирован импульс, который не пройдет через второй элемент И 19 так как третий триггер 23 находится в единичном состоянии и второй элемент И 19 закрыт. Таким образом, после второго импульса цикла 1Ц в счетчике 6 буде записано двадцать пять импульсов. В промежутке между вторым и третьим сигналами цикла 1Ц ошибок не поступило и в счетчике 2 сохранилось прежнее число ошибок. В момент поступления третьего цикла 1Ц содержи мое счетчика 6 переносится в буферные регистры 10 и 11 для отображения аналогично предыдущим случаям. После десятого цикла на входе счетчика Т формируется импульс добавления и вычитания. Импульс добав ления формируется и сдвигается на цикл при заполнении счетчика 7, импульс вычитания - в результате срав нения переменных ошибок с числом, записаннь1м в старший разряд счетчика 7 циклов. Формируемые импульсы, поступающие в счетчик 6, вызывают переполнение декады А, и появляется первый в данной серии Импульс переполнения , который компенсируется задержанным импульсом переполнения счетчика 7. Технике экономический эффект от использования предложенного устройства состоит в возможности сокращения при необходимости времени измерений, а также управления интервалом измере ий в процессе измерений. Формула изобретения Устройство для измерения коэ(фициента ошибок, содержащее последовательно соединенные анализатор ошибок и счетчик ошибок, счетчик числа,первый и второй индикаторы числа и последовательно соединенные счетчик степени и индикатор степени, о тличающееся тем, что, с целью повышения точности измерений, введены первый триггер, счетчик циклов, последовательно соединенные блок считывания, счетчик обратного счета, второй триггер, ключ, делитель и блок сравнения, первый и второй буферные регистры, элемент задержки , последовательно соединеннь е первый элемент И, третий триггер, второй элемент И и первый элемент ИЛИ и последовательно соединенные третий элемент И и второй элемент ИЛИ, при этом выход анализатора ошибок через первый триггер соединен со вторым входом второго триггера, третий вход которого соединен с управляющими входами счетчика числа, первого и второго буферных регистров и блока считывания, с первым входом первого элемента И, со входом элемента задерис ки и со входом счетчика циклов, на который подан сигнал цикловой синхронизации, первый и второй выходы счетчика ошибок соединены соответственно с сигнальным входом блока считывания и со вторым входом первого элемента ИЛИ, выход которого соединен с первым входом счетчика степени, второй вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с первым выходом счетчика циклов, второй выход которого соединен со вторым входом блока сравнения, выход которого соединен со вторым входом делителя и с сигнальным входом счетчика числа, вход установки которого соединен с третьим входом делителя и с выходок элемента задержки,первый и второй выходы сметчика числа соединены со вторыми входами соответственно -первого и второго элементов И, первый и второй входы и второй выход третьего триггера соединены соответственно с первым входом третьего элемента И, со вторым входом второго элемента И и со вторым входом третьего элемента И, соответствующие сигнальные выходы счетчика числа соответственно через первый и второй буферный регистры соединены со входами соответственно первого и второго ин078i 08

дикаторов. числа выход ключа, на второй вход которого поданы taKTOBue импульсы, соединен с тактовым входом счетчика обратного счета,, а на обге5 диненные второй вход первого триггера, третий вход третьего триггера и управляющий вход счетчика степени подан сигнал сброса.

10 Источники информации,

принятые во внимание при экспертизе

Авторы

Даты

1982-02-23—Публикация

1980-04-11—Подача