Изобретение относится к запоминающим устройствам, в частности к запоминающим устройствам динамического типа, и может быть использовано в системах сбора, регистрации и обработки многоканальной измерительной информации.

Целью изобретения является повышение быстродействия устройства.

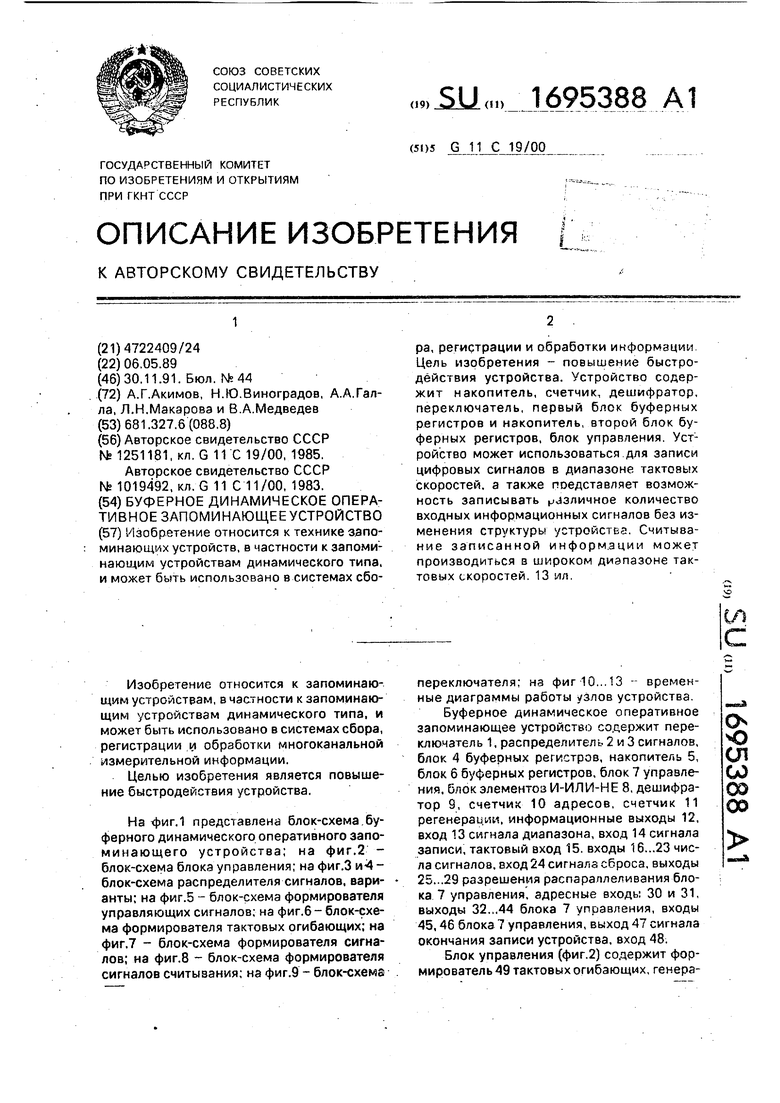

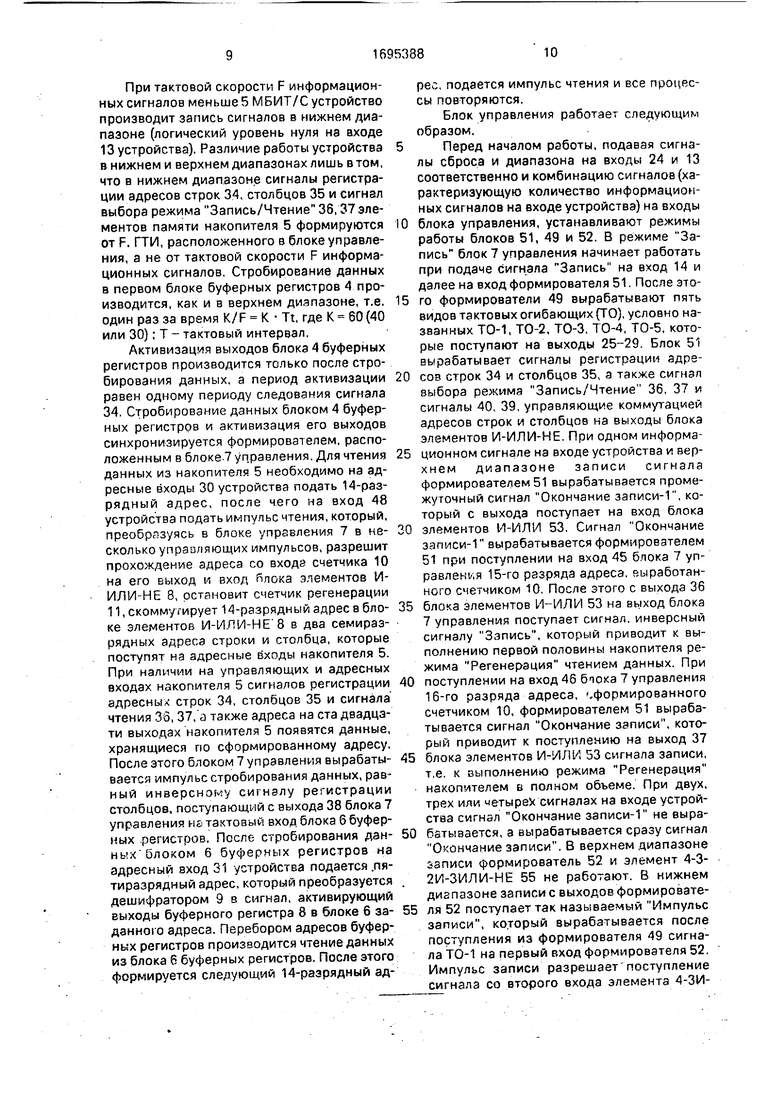

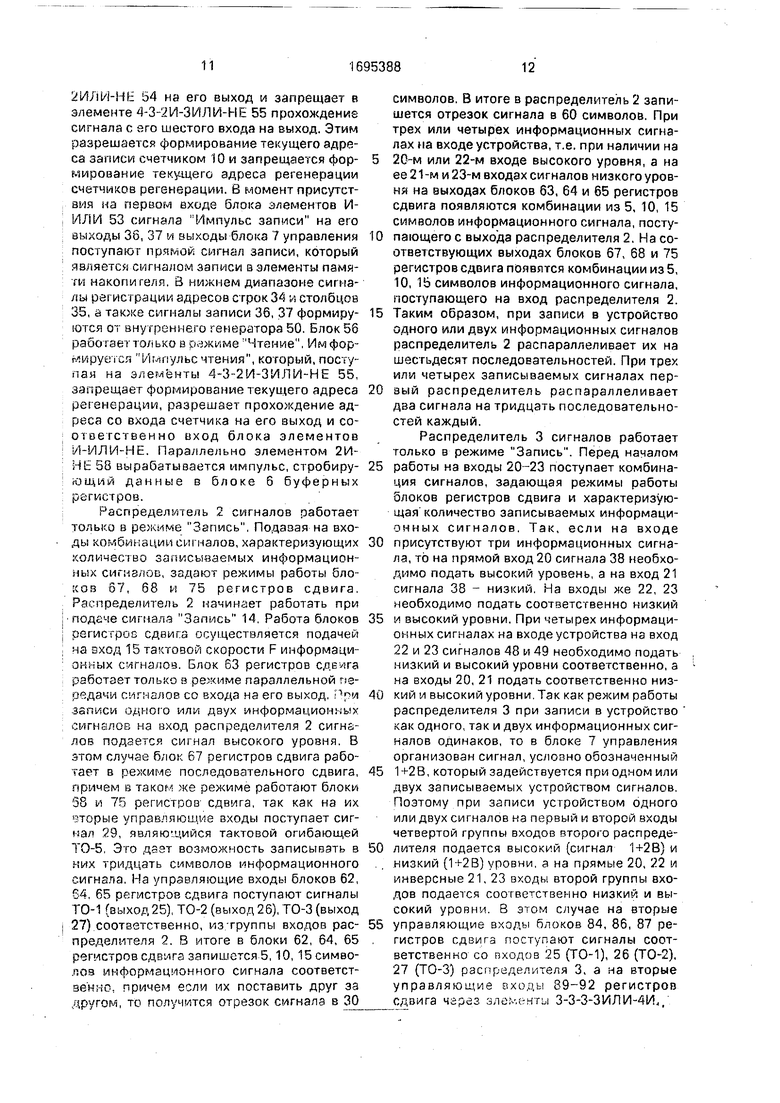

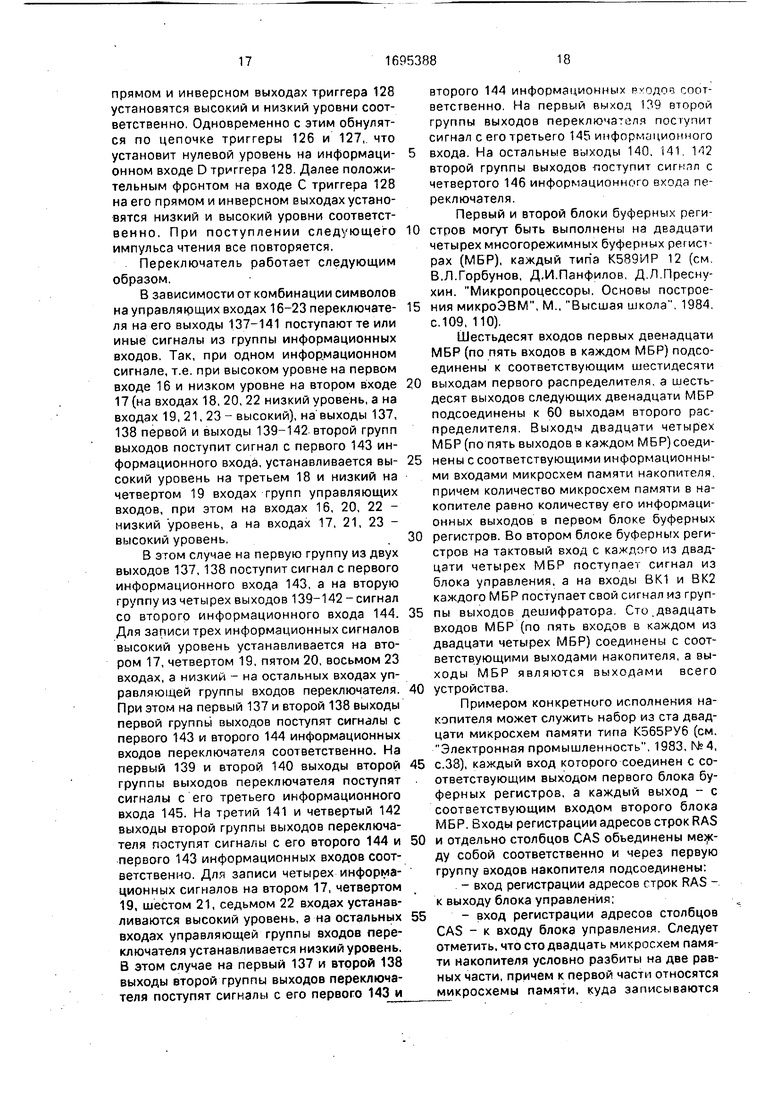

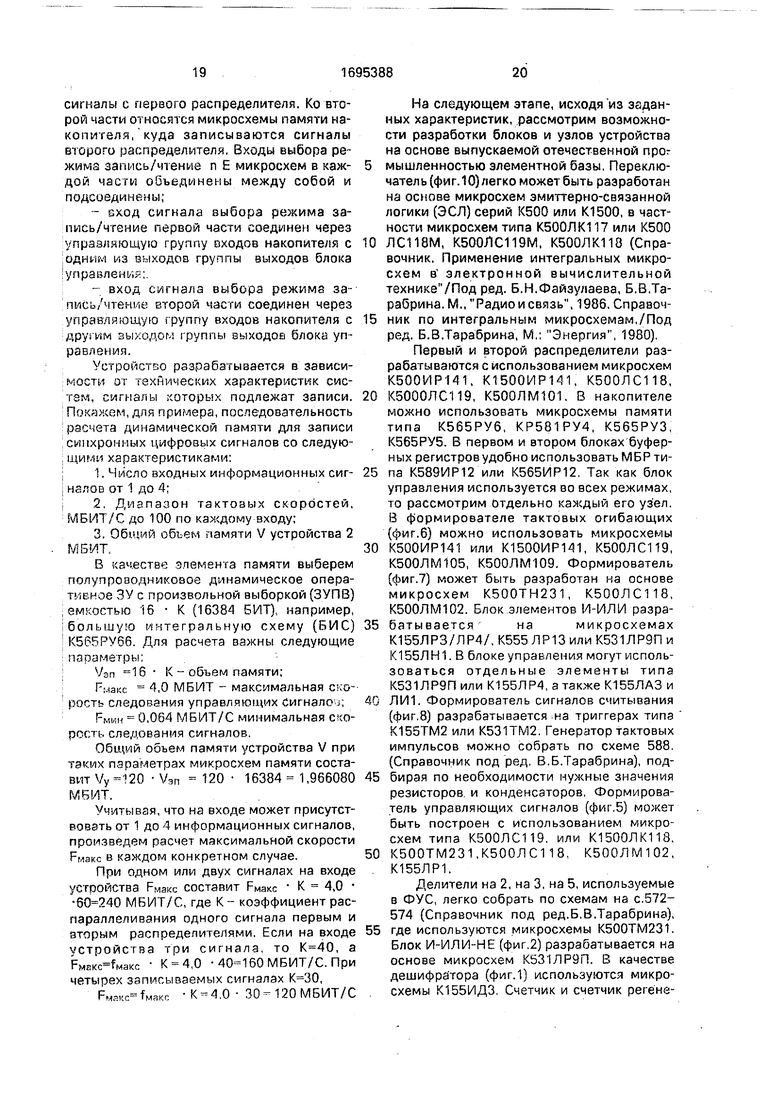

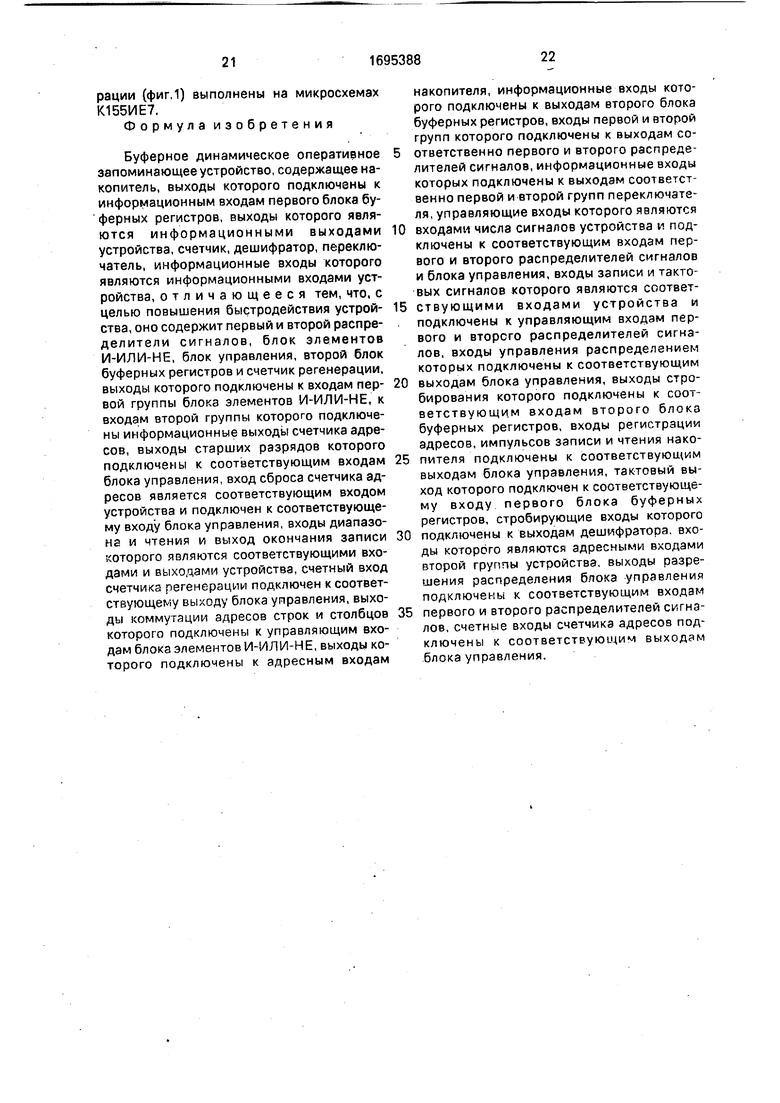

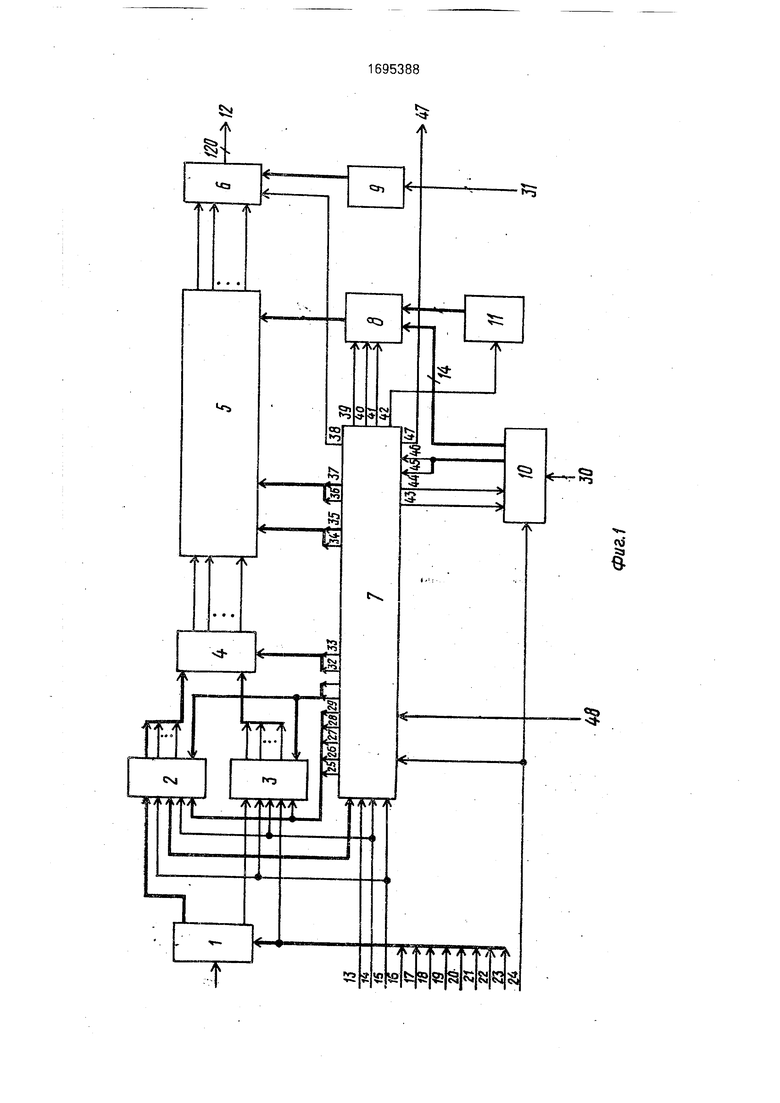

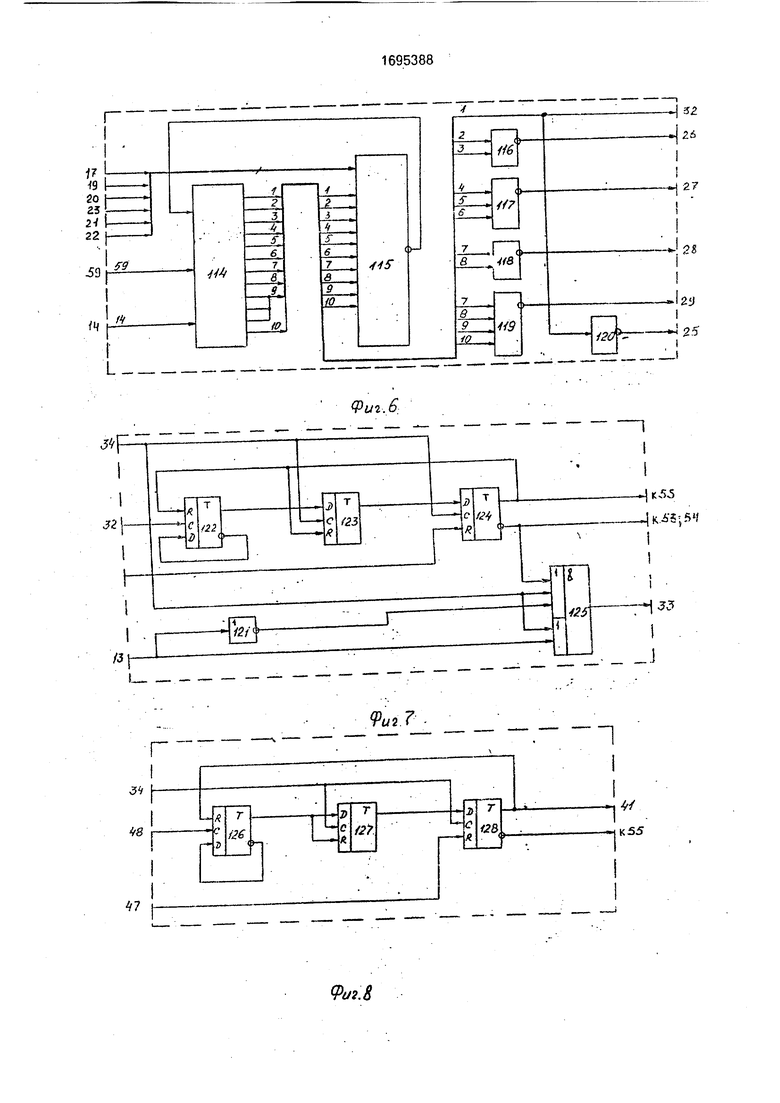

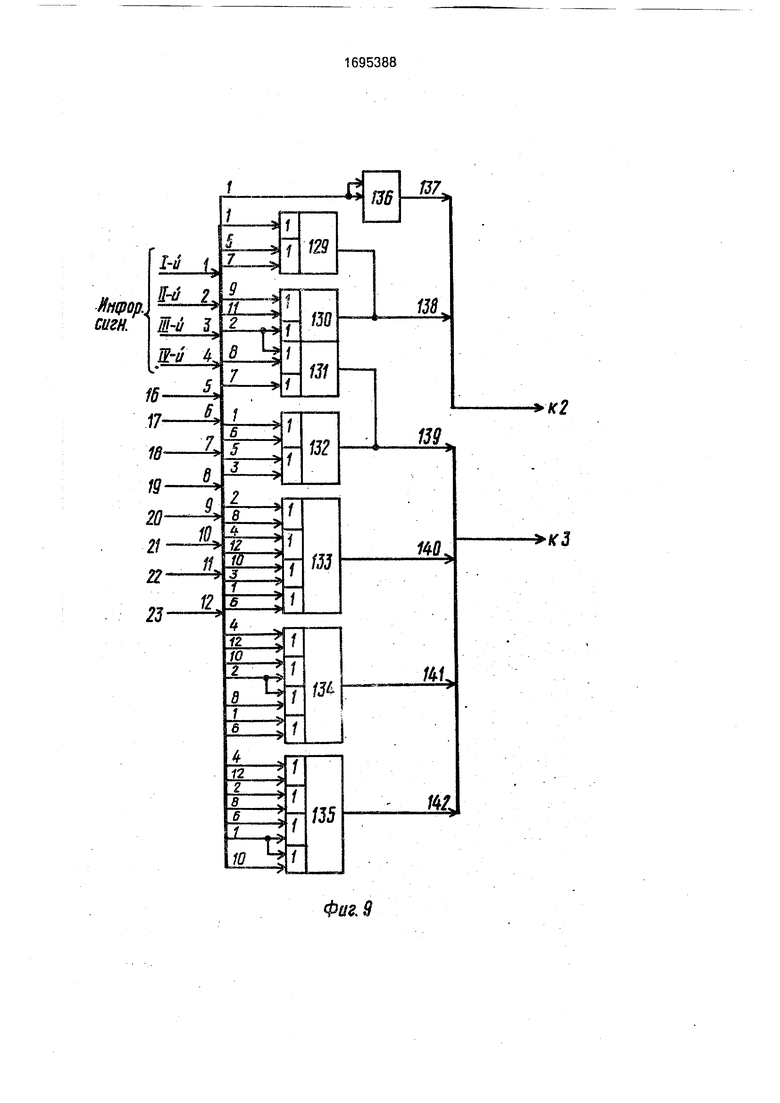

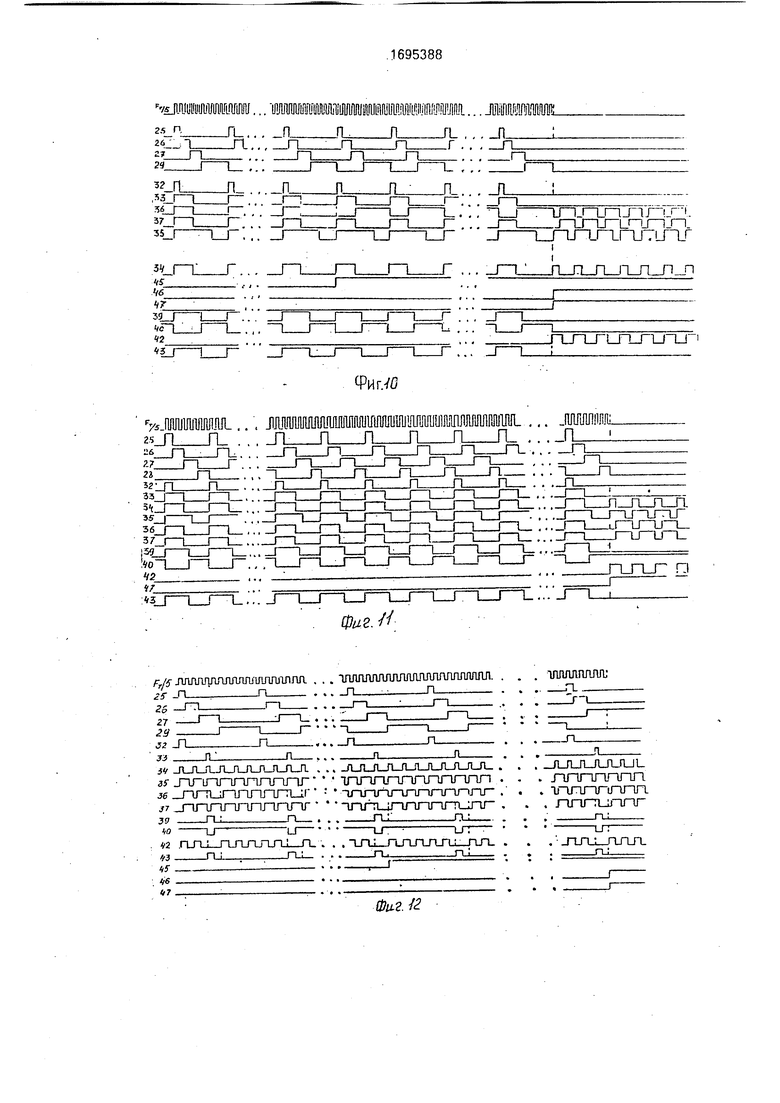

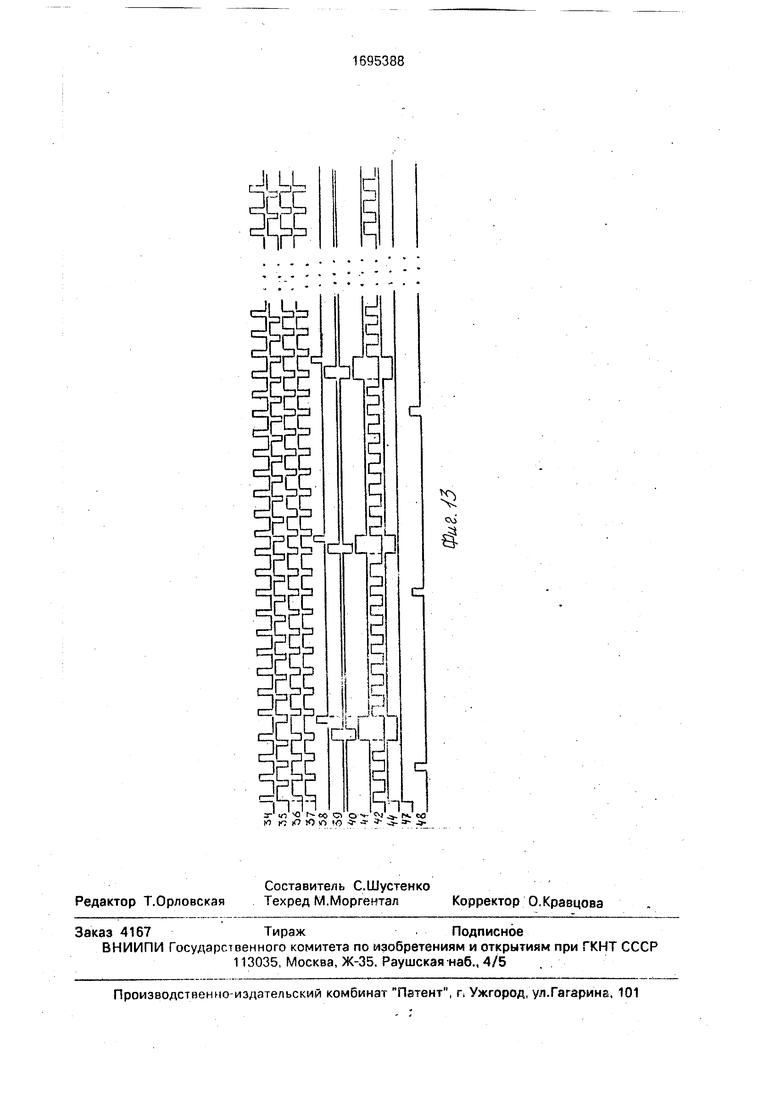

На фиг.1 представлена блок-схема буферного динамического оперативного запоминающего устройства; на фиг.2 - блок-схема блока управления; на фиг.З и-4 - блок-схема распределителя сигналов, варианты; на фиг.5 - блок-схема формирователя управляющих сигналов; на фиг.6-блок-схема формирователя тактовых огибающих; на фиг.7 - блок-схема формирователя сигналов; на фиг.8 - блок-схема формирователя сигналов считывания; на фиг.9 - блок-схема

переключателя; нз фиг 10...13 - временные диаграммы работы узлов устройства.

Буферное динамическое оперативное запоминающее устройство содержит переключатель 1,распределитель 2 и 3 сигналов, блок 4 буферных регистров, накопитель 5, блок 6 буферных регистров, блок 7 управления, блок элементов И-ИЛИ-НЕ 8, дешифратор 9, счетчик 10 адресов, счетчик 11 регенерации, информационные выходы 12, вход 13 сигнала диапазона, вход 14 сигнала записи, тактовый вход 15. входы 16...23 числа сигналов, вход 24 сигнала сброса, выходы 25...29 разрешения распараплеливания блока 7 управления, адресные входы 30 и 31, выходы 32.,.44 блока 7 управления, входы 45,46 блока7 управления, выход 47 сигнала окончания записи устройства, вход 48.

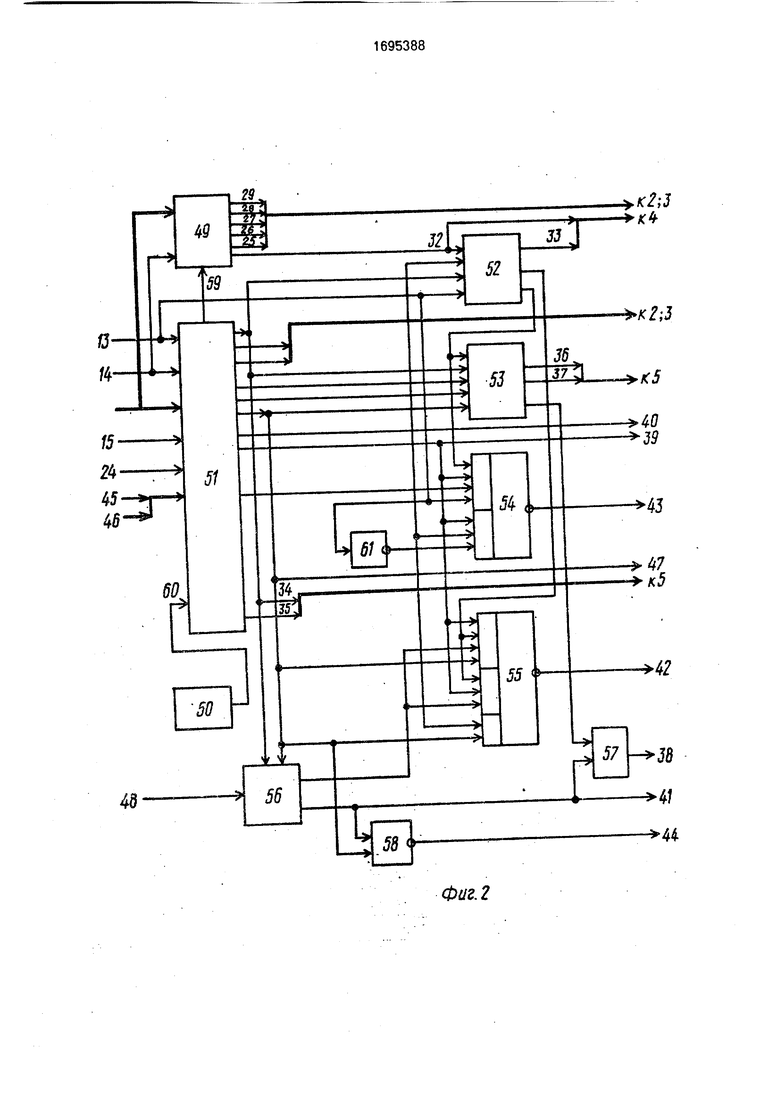

Блок управления (фиг.2) содержит формирователь 49 тактовых огибающих, генера(

О

ел

OJ 00 00

тор 50 тактовых импульсов, формирователь

51управляющих сигналов, формирователь

52сигналов, блок элементов И-ИЛИ 53, элемент 4-ЗИ-2ИЛИ-НЕ 54, элемент 4-3-2И- ЗИЛИ-НЕ 55, формирователь 56 сигналов считывания, элемент 2И 57, элемент 2И-НЕ 58, выход 59 формирователя 51 управляющих сигналов, выход 60 генератора 50 тактовых импульсов и элемент НЕ 61.

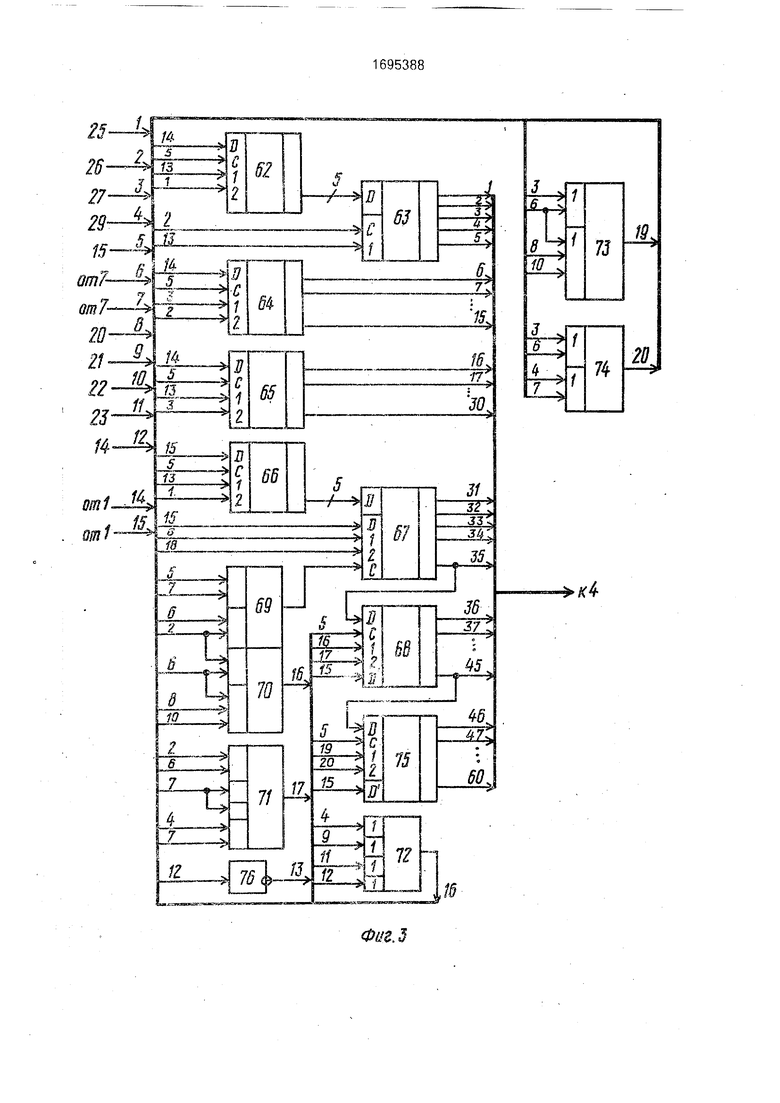

Распределитель сигналов (фиг.З) содер- жмт бпоки 62...68 регистров сдвига, первый 69 и еторой 70 элементы 3-ЗИЛИ-2И, 2-2-2- 2ИЛИ-ЛЦ 71 и 72, элементы 3-ЗИЛИ-2И 73 и 74, блок 75 регистров сдвига и элемент НЕ 76.

Второй распределитель сигналов (фиг.4) содержит элементы 3-3-3-ЗИЛИ-4И 77...80, элементы 3-3-ИЛИ-2И 81...83. блоки 84...92 регистров сдвига.

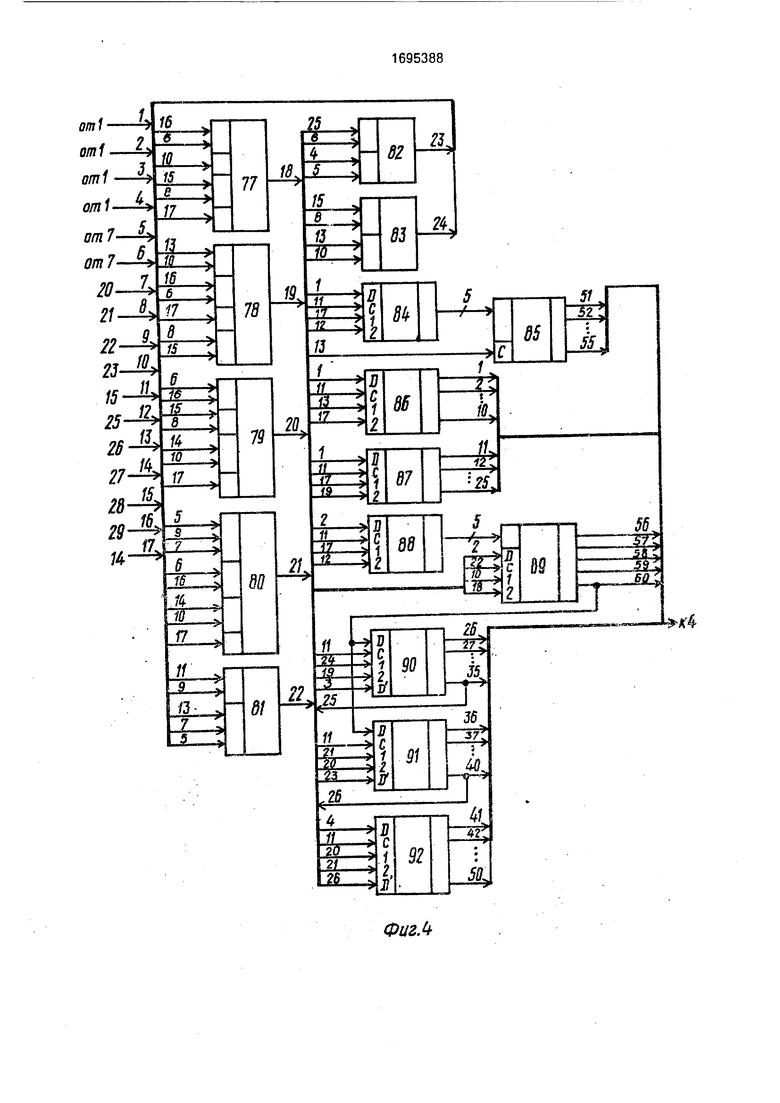

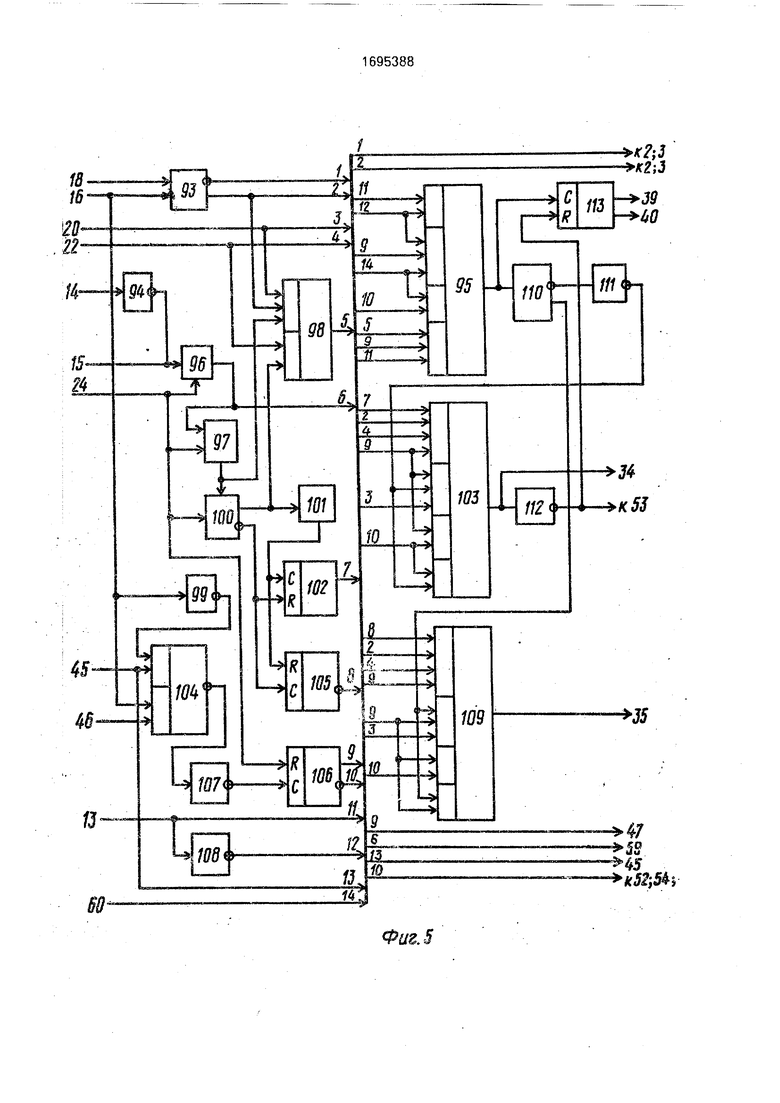

Формирователь управляющих сигналов (фиг.5)содержит элементы 2ИЛИ/2ИЛИ-НЕ 93 и 94, 4-3-2-2ИЛИ-4И 95, делители 96, 97, элемент 3-2ИЛИ-2И 98, элемент НЕ 99, делители 100 и 101, триггер 102, элемент 4-3- 2-2ИЛИ-4И 103, элемент 2-2И-2ИЛИ-НЕ 104, триггеры 105 и 106, элементы НЕ 107 и 108, элемент 4-3-2-2ИЛИ-4И 109, делитель 110, элементы НЕ 111, 112, триггер 113.

Формирователь 49 тактовых огибающих (фиг.6} содержит блок 114 регистров сдвига, элемент ЮИЛИ-НЕ 115, элемент 2ИЛИ-НЕ ПО, элемент ЗИЛИ-НЕ 117, элемент 2ИЛИ-ИЕ 118, элемент 4ИЛИ-НЕ 119, и элемент НЕ 120.

Формирователь 52 сигналов (фиг.7) со- держит элемент НЕ 121, триггеры 122...124 и элемент 3-2ИЛИ-2И 125.

Формирователь 56 сигналов (фиг.8) считывания содержит триггеры 126...128.

Переключатель 1 (фиг.9) содержит эле- менты 2-2ИЛИ-2И 129...132, элементы 2-2-2- 2ИЛИ-4И 133...135 и эпемент 2ИЛИ 136. .

Устройство работает и трех режимах: Запись, Регенерация, Чтение. В режиме Завись в начальный момент времени на четвертый вход устройства подается импульс определенного уровня, что приведет к установке в исходное состояние триггеров, счетчиков и других элементов, расположенных в счетчике и блоке управления. Далее на группу управляющих входов устройства подается комбинация из восьми сигналов, задающая количество поданных на информационные входы переключателя сигналов, подлежащих записи, на третий вход устройства подается тактовая скорость F записываемых информационных сигналов. Установкой определенного (низкого или высокого) уровня сигнала Диапазон на первом входе устройства задается диа-

пазон (нижний или верхний) записи информационных сигналов. Если скорость F информационных сигналов меньше F 5 МБИТ/С, то запись необходимо производить в нижнем диапазоне - уровень логического нуля сигнала Диапазон транзисторно-транзисторной логики (ТТЛ), в противном случае - в верхнем диапазоне - уровень логической единицы ТТЛ-сигнала Диапазон.

Рассмотрим работу устройства в верхнем диапазоне, т.е. при наличии на входах переключателя сигналов с F 5 МБИТ/С, и при высоком уровне ТТЛ на первом входе устройства. Режим Запись инициируется подачей на второй вход устройства сигнала определенного уровня. В результате переключатель, первый и второй распределители и блок управления установятся в нужный режим работы. В переключателе произойдет подключение информационных сигналов к выходам первой и второй групп выходов. В блоке управления с первой группы выходов на третьи группы входов первого и второго распределителей подаются сигналы, разрешающие распараллеливание входных информационных сигналов на определенное количество последовательностей. Так, если записывается устройством один или два информационных сигнала, то последние распараллеливаются как первыми, так и вторым распределителями на шестьдесят последовательностей. При трех или четырех информационных сигналах на входах устройства происходит их распараллеливание на сорок или тридцать последовательностей каждый сигнал соответственно, параллельно этому блоку управления формируются из тактовой скорости F управляющие сигналы регистрации адресов строк RAS, столбцов СА S и выбор режима Запись/Чтение (WE) элементов памяти, которые через четвертую и пятую группы выходов подаются на управляющие входы накопителя. Следует отметить, что длительность сигналов RAS, CAS, WE равна:

К К „ . т

1 ti

к

Ft 1/ТГ где К - количество последовательностей, полученных в результате распараллеливания одного информационного сигнала, т.е. К может быть равен 6$ 4$ Зф. Одновременно с третьей группы выходов блока управления подаются два сигнала, которые:

- стробируют в первом блоке буферных регистров символы, присутствующие на его информационных входах, т.е. запоминаются одновременно каждые 6ф 3{рсим- волов в зависимости от количества сигналов на входе устройства, В результате в первом блоке хранится в общем сто двадцать символов до прихода следующего строба;

- активизируют выходы первого блока буферных регистров, в результате чего на ста двадцати входах накопителя появятся сто двадцать хранящихся в блоке символов. Период активизации выходов первого блока буферных регистров равен периоду следования сигнала RAS регистрации адресов строк элементов памяти накопителя. Счетчик формирует 14-разрядные адреса, которые коммутируются блоком элементов И-ИЛИ-НЕ в две комбинации по семь символов и подаются на адресный вход накопителя. Период формирования нового адреса равен периоду управляющих сигналов RAS, CAS, WE.

Следует отметить, что при одном информационном сигнале на входе устройства производится регистрация данных сначала в первой половине накопителя, затем во второй. В момент заполнения второй половины объема накопителя в первой половине произвбдится регенерация информации чтения данных из элементов памяти. Это достигается тем, что счетчиком 10 вырабатывается при одном информационном сигнале на входе устройства промежуточный сигнал Окончание записи - 1, который поступает из второй группы выходов на один из входов 45 второй группы входов блока управления. В результате сигнал выбора режима Запись/Чтение WE, относящийся к первой половине накопителя, инвертируется и с пятой группы выходов блока управления поступает на один из входов второй группы управляющих входов накопителя. При заполнении всех ячеек памяти устройство переходит в режим Регенерация, который осуществляется чтением данных из накопителя. Режим Регенерация инициируется поступлением сигнала из второй группы выходов счетчика на вторую группу входов блока управления, который является последним адресом счетчика. После этого с шестого выхода блока управления на выход устройства поступает сигнал Окончание записи. В момент поступления сигнала Окончание записи управляющие сигналы RAS, CAS WE начнут формироваться от генератора тактовых импульсов (ГТИ), расположенного в блоке управления. Одновременно вырабатываются счетчиком регенерации адреса строк, которые через блок элементов И-ИЛИ-НЕ поступают на адресные входы накопителя.

При тактовой скорости F информационных сигналов меньше 5 МБИТ/С устройство производит запись сигналов в нижнем диапазоне. Для этого на первый вход устройства необходимо подать нулевой уровень ТТЛ, Различия работы устройства в нижнем и верхнем диапазонах лишь в том, что в нижнем диапазоне сигналы управления RAS, CAS, WE режимами работы накопителя формируются от ГТИ, расположенного в блоке управления, а не от тактовой скорости F информационного сигнала. Стробировэние данных в первом блоке буферных регистров производится так же, как и в верхнем диапазоне, т.е. один раз за время Tt, где , или 3. Активизация выходов первого блока буферных регистров производится только после стробирования данных, а период активизации равен одному

периоду следования сигнала RAS. Строби- рование данных первым блоком буферных регистров и активизация его выходов синхронизируются формирователем, расположенным в блоке управления устройства.

Для чтения данных из накопителя необходимо на первую группу адресных входов устройства подать 14-разрядный адрес, после чего на пятый вход устройства подать импульс чтения, который, преобразуясь в

блокеуправления в несколько управляющих импульсов, разрешит прохождение адреса со входа счетчика на его выход и вход блока элементов И-ИЛИ-НЕ, остановит счетчик регенерации и скоммутирует 14-разрядный

адрес в блоке элементов И-ИЛИ-НЕ в два семиразрядных адреса строки и столбца, которые поступают на адресные входы накопителя. При наличии на управляющих входах накопителя сигналов регистрации строк

RAS и столбцов CAS и сигнала чтения WE, а также адреса на ста двадцати выходах накопителя, появятся данные, хранящиеся по сформированному адресу. После этого блоком управления вырабатывается импульс стробирования данных, который поступает на тактовый вход второго блока буферных регистров. После стробирования данных вторым блоком буферных регистров на второй адресный вход устройства подается пятиразрядный адрес, который преобразуется дешифратором в сигнал, активизирующий выходы буферного регистра заданного адреса. Перебором адресов буферных регистров производится чтение

данных из второго блока буферных регистров. После этого формируется следующий 14-разрядный адрес, подается импульс чтения и порядок поступления сигналов повторяется.

Следу-ег отметить, что граница между верхнем и нижним диапазонами оп- , лначением тактовой скорости - ь Мtj /П/С информационных сигнале с /-unoN; требований на минимальный пьрнод ооращения к любой строке полупроводниковых динамических оперативны; запоминающих устройств

В sjex iMCi Записи в начальный момент времен / па аход 24 устройства подается iv.rsa/i сор jCds что пои ведет к установке в исходное состояние 10 и блока 7 управления. Далее на входы 16...23 устрой- ствь подаечсг комбинация из восьми сигналов, зздяющая количество поданных на мьгоормяцио: иык входы сигналов, подлежа- . uU ix загмс Н тактовый вход 15 подается сигнал с. чястогой f1- записываемых инфор- vir: ионных сигналов. Установкой опреде- (iii-. iKoro или высокого) уровня сигнале HD входе i3 устройства задается /jyianfUOH (нижний или нерхний) записи информационных сигналов. Если скорость F хнфо р;1., а ц i-i с ни ы;ч сигналов меньше - : Б /С, ю запись необходимо произ- Л дип. в нижнем диапазоне (уровень логического нуль сигнала диапазона), в гфотмзном случае - в верхнем диапазоне.

HECCMC PI- M р гбогу устройства в верх- Httiv, д ргт зг не Б г епеключатепе 1 произой- дат п.., цхмемоние информационных иигпатор к персой и второй группе выходов, Li блоке 7 управления выходов 25...29 на распредел Т -элм ., 3 подаются сигналы, раз- эошз ош/iL лспараллеливание входных ин- фе мачиомчух сигналов на определенное .иличэс г г: последовательностей, Так, если заг с нэгсг устройством один млн дйа ин .-popf tauiiJH iLiix сигнала, TO последние р;:с- ,(вливаюicf, распределителями 2, 3 -ic последовательностей. При трех i j;w «етырох информационных сигна- на -ia входах устройства происходит их рас- тар3 гтс 1ива.-|и ха сорок или тридцать мослидовзгсльнос.тей каждый сигнал соот- зе гственно. Пасзплел ьно этому блоком 7 уп- рэвпр гип формируются из тактовой лгоросш управляющие сигналы регистрации адресов строк 34 и столбцов 35 и выбор ч ре ж и iv ь запись/чтение 36, 37 ЭЛР.ЙНТОЕ пальчги, которые с выходов бло- п упп.ч лепия подаются на соответстау- ащие схсл.ы накопителя 5, Следует ;л..)гъ. что (ПЯ /тельность сигналов 34- 21 рлв-пй К/Г- К - Tt, где К - количество -юследсеате. ьносгей, полученных в ре- з;ль зп; ;,-;«; араллеливзния одного ин- ормац/гонисго сигнала, г.е. К может быть аве;- 60 (10 --Л . :Ю). Опнспргменно с аы- иол1.; 3V I - 1 блока 7 упидпле ия на блок

4 буферных регистров подаются сигналы, которые выполняют следующие функции: стробируют в блоке 4 буферных регистров символы, присутствующие на его информационных входах, т.е. запоминаются одновременно каждые 60 (40 или 30) символов в зависимости от количества сигналов на входе устройства. В результате в блоке 4 хранятся в общем сто двадцать символов до

0 прихода следующего строба. Кроме того, активизируют выходы блока 4, в результате чего на ста двадцати входах накопителя появятся сто двадцать символов данных.

Период активизации выходов блока 4

5 буферных регистров равеч периоду следованья сигнала 34 регистрации адресов строк элементов памяти накопителя 5. Счетчик 10 формирует 14-разрядные адреса, которые коммутируются блоком 8 элементов

0 И-ИЛИ-НЕ в две комбинации по семь символов и подаются на адресный вход накопителя 5. Период формирования нового адреса равен периоду следования управляющих сигналов 34-37. Следует от метить, что

5 при одном информационном сигнале на входе устройства производится регистрация данных сначала в первой половине накопителя 5, затем во второй. Во время заполнения второй половины объема нако0 пителя 5 в его первой половине производится регенерация информации чтением данных из элементов памяти, Это достигается тем, что счетчиком 10 вырабатывается при одном информационном сигнале на

5 входе устройства промежуточный сигнал Окончание записи-1, который поступает с выхода на один из входов 45, 46 блока управления 7. В результате сигнал 36 выбора режима Запись/Чтение, относящийся к

0 первой половине объема накопителя 5, инвертируется-и с выхода 36 блока 7 управления поступает на соответствующий вход накопителя 5.

При заполнении всех ячеек памяти уст5 ройство переходит в режим Регенерация, который осуществляется чтением данных из накопителя 5. Режим Регенерация инициируется поступлением сигнала с выхода счетчика 10 на вход 46 блока 7

0 управления, который на аыход устройства поступит сигналом Окончание записи. В момент поступления сигнала Окончание записи управляющие сигналы 34-37 начнут формироваться от генератора гаклэ5 вых импульсов (Г.ТИ), расположенного в блоке 7 управления. Одновременно вырабатываются счетчиком регенерации 11 ад- рэса строк, которые через блок элементов И-ИЛИ-НЕ 8 поступают на адресные входы накопителя 5.

При тактовой скорости F информационных сигналов меньше 5 МБИТ/С устройство производит запись сигналов в нижнем диапазоне (логический уровень нуля на входе 13 устройства). Различие работы устройства в нижнем и верхнем диапазонах лишь в том, что в нижнем диапазоне сигналы регистрации адресов строк 34, столбцов 35 и сигнал выбора режима Запись/Чтение 36,37 элементов памяти накопителя 5 формируются от F. ГТИ, расположенного в блоке управления, а не от тактовой скорости F информационных сигналов. Стробирование данных в первом блоке буферных регистров 4 производится, как и в верхнем диапазоне, т.е. один раз за время K/F К Tt, где К 60 (40 или 30); Т - тактовый интервал.

Активизация выходов блока 4 буферных регистров производится только после стро- бирования данных, а период активизации равен одному периоду следования сигнала 34. Стробирование данных блоком 4 буферных регистров и активизация его выходов синхронизируется формирователем, расположенным в блоке 7 управления. Для чтения данных из накопителя 5 необходимо на адресные входы 30 устройства подать 14-разрядный адрес, после чего на вход 48 устройства подать импульс чтения, который, преобразуясь в блоке управления 7 в несколько управляющих импульсов, разрешит прохождение адреса со входа счетчика 10 на его выход и вход лока элементов И- ИЛИ-НЕ 8, остановит счетчик регенерации 11, скоммугирует 14-разрядный адрес в блоке элементов И-ИЛИ-НЕ 8 в два семиразрядных адреса строки и столбца, которые поступят на адресные входы накопителя 5. При наличии на управляющих и адресных входах накопителя 5 сигналов регистрации адресных строк 34, столбцов 35 и сигнала чтения 35, 37, о также адреса на ста двадцати выходах накопителя 5 появятся данные, хранящиеся по сформированному адресу. После этого блоком 7 управления вырабатывается импульс стробирования данных, равный инверсному сигналу регистрации столбцов, поступающий с выхода 38 блока 7 управления на тактовый вход блока б буферных регистров. После стробирования данных Олоком 6 буферных регистров на адресный вход 31 устройства подается .пятиразрядный адрес, который преобразуется дешифратором 9 в сигнал, активирующий выходы буферного регистра 8 в блоке б заданною адреса. Перебором адресов буферных регистров производится чтение данных из блока 6 буферных регистров. После этого формируется следующий 14-разрядный адрес, подается импульс чтения и все процессы повторяются.

Блок управления работает следующим образом.

Перед началом работы, подавая сигналы сброса и диапазона на входы 24 и 13 соответственно и комбинацию сигналов (характеризующую количество информационных сигналов на входе устройства) на входы

блока управления, устанавливают режимы работы блоков 51, 49 и 52. В режиме Запись блок 7 управления начинает работать при подаче сигнала Запись на вход 14 и далее на вход формирователя 51. После это5 го формирователи 49 вырабатывают пять видов тактовых огибающих (ТО), условно названных ТО-1, ТО-2, ТО-3, ТО-4, ТО-5, которые поступают на выходы 25-29. Блок 51 вырабатывает сигналы регистрации адре0 сов строк 34 и столбцов 35, а также сигнал выбора режима Запись/Чтение 36, 37 и сигналы 40, 39, управляющие коммутацией адресов строк и столбцов на выходы блока элементов И-ИЛИ-НЕ. При одном информа5 ционном сигнале на входе устройства и верхнем диапазоне записи сигнала формирователем 51 вырабатывается промежуточный сигнал Окончание записи-1, который с выхода поступает на вход блока

0 элементов И-ИЛИ 53. Сигнал Окончание записи-1 вырабатывается формирователем 51 при поступлении на вход 45 бпока 7 управления 15-го разряда адреса, выработанного счетчиком 10. После этого с выхода 36

5 блока элементов И-ИЛИ 53 на выход блока 7 управления поступает сигнал, инверсный сигналу Запись, который приводит к выполнению первой половины накопителя режима Регенерация чтением данных. При

0 поступлении на вход 46 бпока 7 управления 16-го разряда адреса, сформированного счетчиком 10, формирователем 51 вырабатывается сигнал Окончание записи, который приводит к поступлению на выход 37

5 блока элементов И-ИЛИ 53 сигнала записи, т.е. к выполнению режима Регенерация накопителем в полном объеме. При двух, трех или четырех сигналах на входе устройства сигнал Окончание записи-1 не выра0 батывается, а вырабатывается сразу сигнал Окончание записи. В верхнем диапазоне записи формирователь 52 и элемент 4-3- 2И-ЗИЛИ-НЕ 55 не работают. В нижнем диапазоне записи с выходов формировате5 ля 52 поступает так называемый Импульс записи, который вырабатывается после поступления из формирователя 49 сигнала ТО-1 на первый вход формирователя 52, Импульс записи разрешает поступление сигнала со второго входа элемента 4-ЗИ2ИЛИ-НЕ b4 на его выход и запрещает в элементе 4-3-2И-ЗИЛИ-НЕ 55 прохождение сигнала с его шестого входа на выход. Этим разрешается формирование текущего адреса записи счетчиком 10 и запрещается формирование текущего адреса регенерации счетчиков регенерации. В момент присутствия на первом входе блока элементов И- ИЛИ 53 сигнала Импульс записи на его выходы 38, 37 и выходы блока 7 управления поступают прямой сигнал записи, который является сигналом записи в элементы памяти накопителя. В нижнем диапазоне сигналы per ис грации адресов строк 34 и столбцов 35, d также сигналы записи 36, 37 формируются от внутреннего генератора 50. Блок 56 paooiaei только в режиме Чтение, Им формируемся Импульс чтения, который, поступая на элементы 4-3-2И-ЗИЛИ-НЕ 55, запрещает формирование текущего адреса регенерации, разрешает прохождение адреса со входа счетчика на его выход и COOTS ве гственно вход блока элементов i/1-ИЛИ-НЕ. Параллельно элементом 2И- НЕ 58 вырабатывается импульс, стробиру- ю щ и и данные в блоке б буферных регистров.

Распределитель 2 сигналов работает только в режиме Запись, Подавая на входы комбинации сигналов, характеризующих количество записываемых информационных сигналов, задают режимы работы блоков 67, 68 и 75 регистров сдвига, Распределитель 2 начинает работать при подече сигнала Запись 14, Работа блоков регисгрос сдвига осуществляется подачей ча вход 15 тактовой скорости F информационных сигнаиоз. Блок 63 регистров сдвига работает только в режиме параллельной передачи сигналов со входа на его выход, Vй записи одного или двух информационных сигналов на вход распределителя 2 сигналов подается сигнал высокого уровня. В этом случае блок 67 регистров сдвига работает в режиме последовательного сдвига, причем в таком же режиме работают блоки 58 и 75 регистров сдвига, так как на их вторые управляющие входы поступает сигнал 29, являющийся тактовой огибающей ТО-5, Это дает возможность записывать в них тридцать символов информационного сигнала, На управляющие входы блоков 62, Ј4, 65 регистров сдвига поступают сигналы ТО-1 (выход 25), ТО-2 (выход 26), ТО-3 (выход 27) соответственно, из труппы входов распределителя 2. В итоге в блоки 62, 64, 65 регистров сдвмга запишется 5,10,15 символов информационного сигнала соответственно, причем если их поставить друг за другом, то получится отрезок сигнала в 30

символов. В итоге в распределитель 2 запишется отрезок сигнала в 60 символов. При трех или четырех информационных сигналах на входе устройства, т.е. при наличии на

20-м или 22-м входе высокого уровня, а на ее 21-м и 23-м входах сигналов низкого уровня на выходах блоков 63, 64 и 65 регистров сдвига появляются комбинации из 5, 10, 15 символов информационного сигнала, посту0 лающего с выхода распределителя 2. На соответствующих выходах блоков 67, 68 и 75 регистров сдвига появятся комбинации из 5, 10, 1Ь символов информационного сигнала, поступающего на вход распределителя 2.

5 Таким образом, при записи в устройство одного или двух информационных сигналов распределитель 2 распараллеливает их на шестьдесят последовательностей. При трех или четырех записываемых сигналах пер0 вый распределитель распараллеливает два сигнала на тридцать последовательностей каждый.

Распределитель 3 сигналов работает только в режиме Запись. Перед началом

5 работы на входы 20-23 поступает комбинация сигналов, задающая режимы работы блоков регистров сдвига и характеризующая количество записываемых информационных сигналов. Так, если на входе

0 присутствуют три информационных сигнала, то на прямой вход 20 сигнала 38 необходимо подать высокий уровень, а на вход 21 сигнала 38 - низкий, На входы же 22, 23 необходимо подать соответственно низкий

5 и высокий уровни. При четырех информационных сигналах на входе устройства на вход

22 и 23 сигналов 48 и 49 необходимо подать низкий и высокий уровни соответственно, а на входы 20, 21 подать соответственно низ0 кий и высокий уровни, Так как режим работы распределителя 3 при записи в устройство как одного, так и двух информационных сигналов одинаков, то в блоке 7 управления организован сигнал, условно обозначенный

5 1+2В, который задействуется при одном или двух записываемых устройством сигналов. Поэтому при записи устройством одного или двух сигналов на первый и второй входы четвертой группы входов второго распреде0 лителя подается высокий (сигнал 1+2В) и низкий (1+2В) уровни, а на прямые 20, 22 и инверсные 21, 23 входы второй группы входов подается соответственно низкий и высокий уровни. В этом случае на вторые

5 управляющие входы блоков 84, 86, 87 регистров сдвига поступают сигналы соответственно со входов 25 (ТО-1), 26 (ТО-2), 27 (ТО-3) распределителя 3, а на вторые управляющие входы 89-92 регистров сдвига чгрез злол-д-нгы 3-3-3-ЗИЛИ-4И,,

77-80 соответственно поступит сигнал ТО-5 со входа 29. Сигнал ТО-2 со входа 26 распределителя 3 поступает на блоки 86 и 85 регистров сдвига, переписывая в последний одновременно пять сигналов с выходов бло- ка 84 регистров сдвига. В результате в блоки 85, 86, 87, 89, 91 и 92 регистров сдвига запишется по 5, 10, 15, 5, 10, 5,10 символов информационного сигнала соответственно, что в итоге составляет отрезок сигнала в шестьдесят символов, Следует отметить, что режимы работы блоков 84-87 регистров сдвига не меняются при любом количестве записываемых устройством информационных сигналов. При трех информационных сигналах на входе устройства, т.е. при наличии высокого уровня на входе 20 и низкого на входе 21, на вторые управляющие входы блоков 89-92 регистров сдвига через элементы 3-3-3-ЗИЛИ-4И 77-80 поступит сиг- нал ТО-4 с входа 28. В результате в блоки 89 и 91 регистров сдвига запишется по пять символов третьего информационного сигнала в каждую со второго входа распределителя 3. В блок 90 регистров сдвига запишется десять символов второго информационного сигнала. -В блок 92 регистров сдвига запишется десять символов первого информационного сигнала с четвертого входа первой группы входов. В блоки 85, 86, 87 регистров сдвига запишется в общем тридцать символов третьего информационного сигнала, но поступающего с входа распределителя 3. Таким образом, при трех информационных сигналах на входе устройства в распредели- теле 3 зафиксируется, сорок символов третьего информационного сигнала; десять символов второго информационного сигнала и десять символов первого. Если учесть, что в первом распределителе фиксируется (см.фчг 3) в этот момент времени по тридцать символоб первого и второго информационных сигналов, то окажется, что при прохождении сигналов тактовых огибающих (ТО-1, ТО-2, ТО-3, ТО-4) и первым, и вторым распределителями фиксируется по сорок символов каждого информационного сигнала. При четырех сигналах на входе устройства, т .е. при наличии высокого уровня на входе 22 и низкого на входе 23, в блоки 85, 86,87 регистров сдвига запишется тридцать символов третьего информационного сигнала, а в блоки 89-92 регистров сдвига запишется тридцать символов четвертого информационного сигнала.

Следует отметить, что сигнал ТО-1 (инверсный сигналу ТО-1) подается на тактовый вход буферных регистров, расположенных в блоке 4 буферных регистров (см.сигнал 32 на фиг.1) для стробирования

последних символов, записанных в первом и втором распределителях. Поэтому, чтобы развязать во времени момент стробирования блоком 4 буферных регистров уже запи- санных в распределители символов с необходимостью записи в них следующих символов информационных сигналов, предложено первые пять символов перезагружать в регистр параллельного действия сразу же после их записи в регистр сдвига последовательного действия.

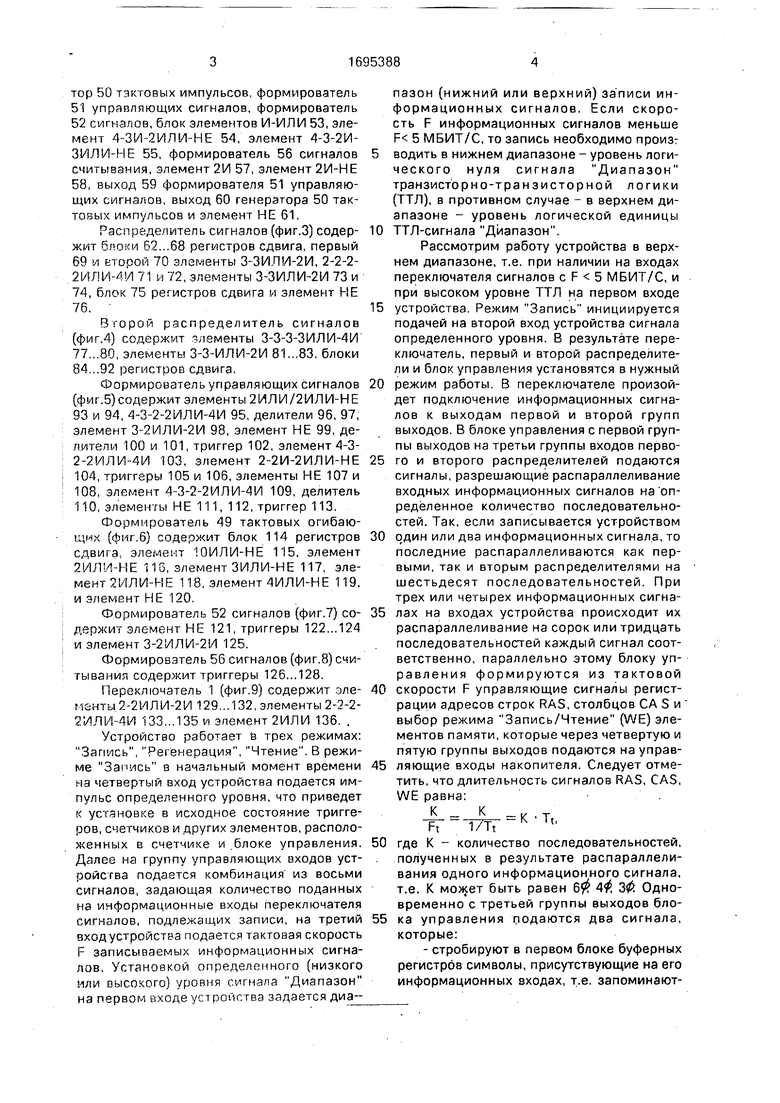

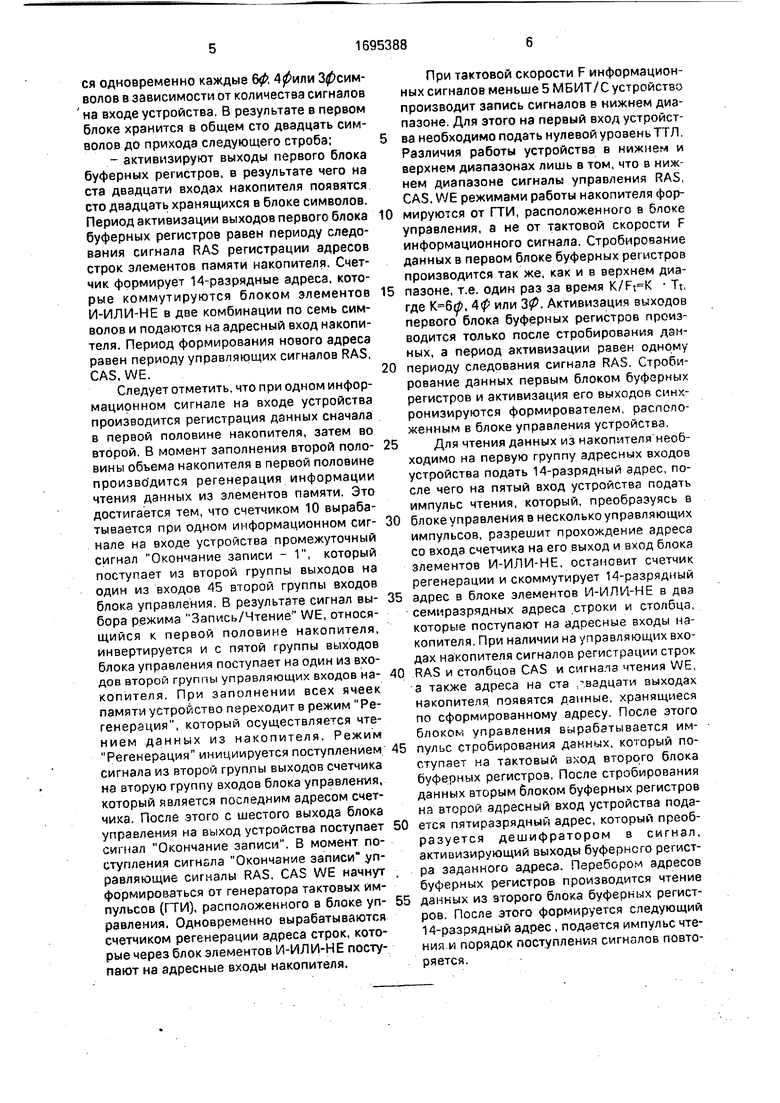

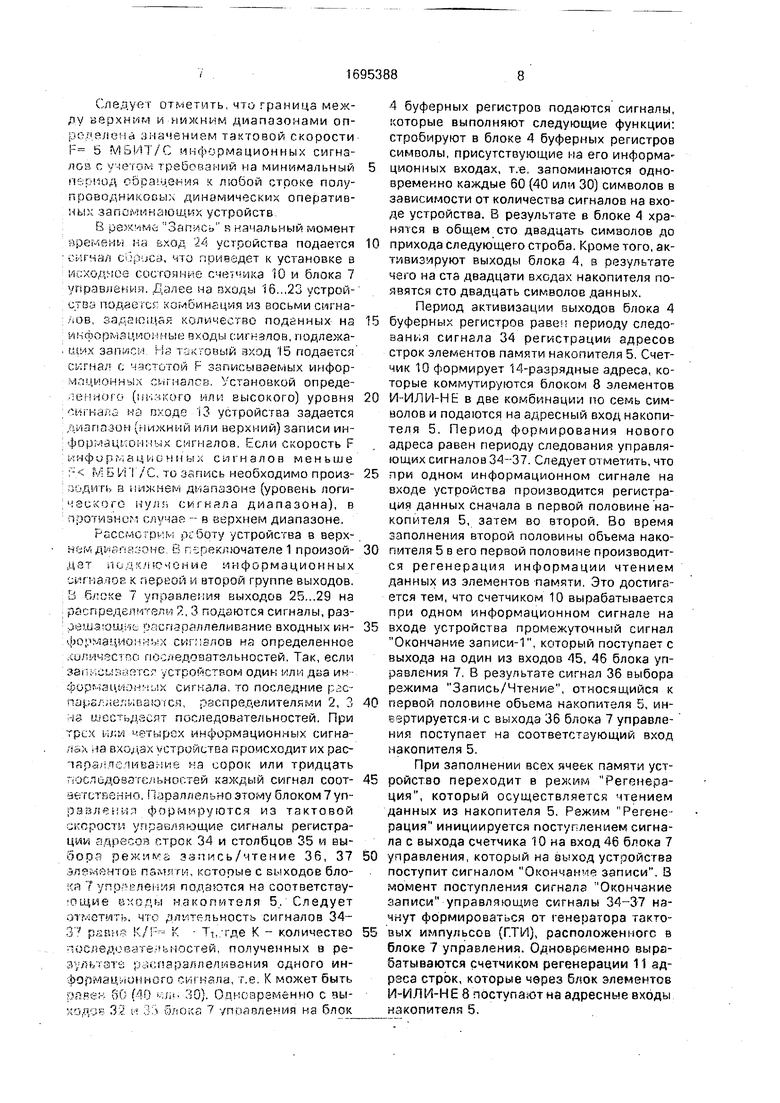

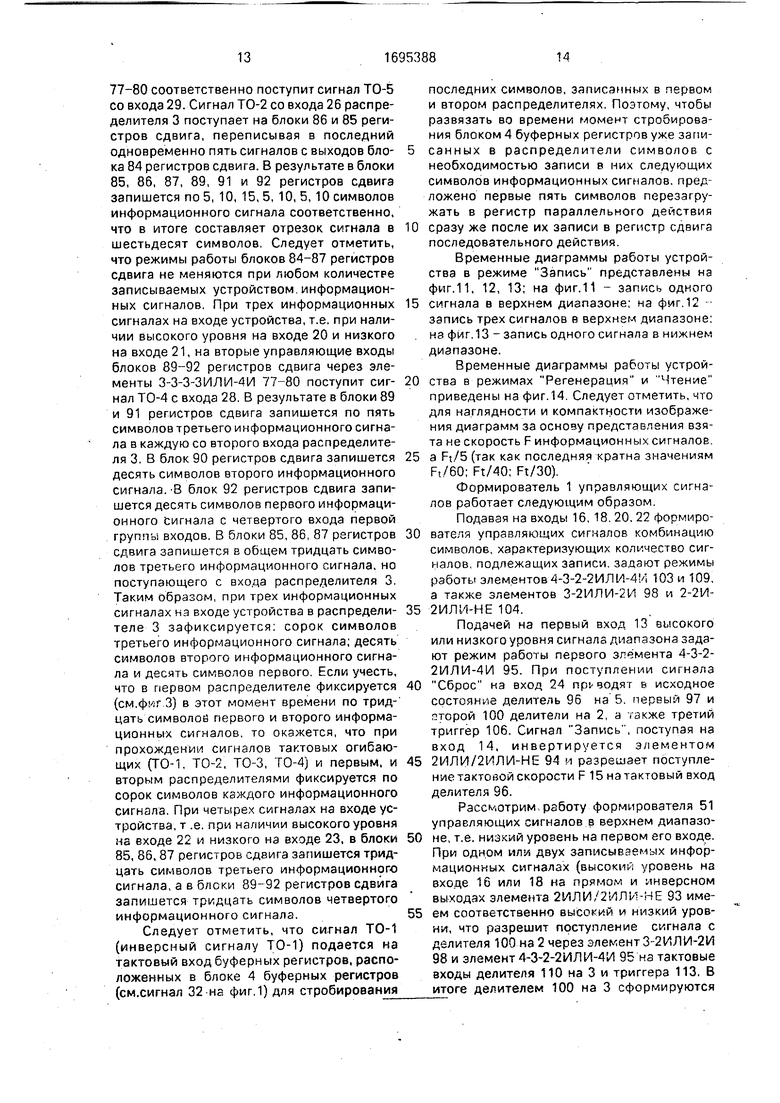

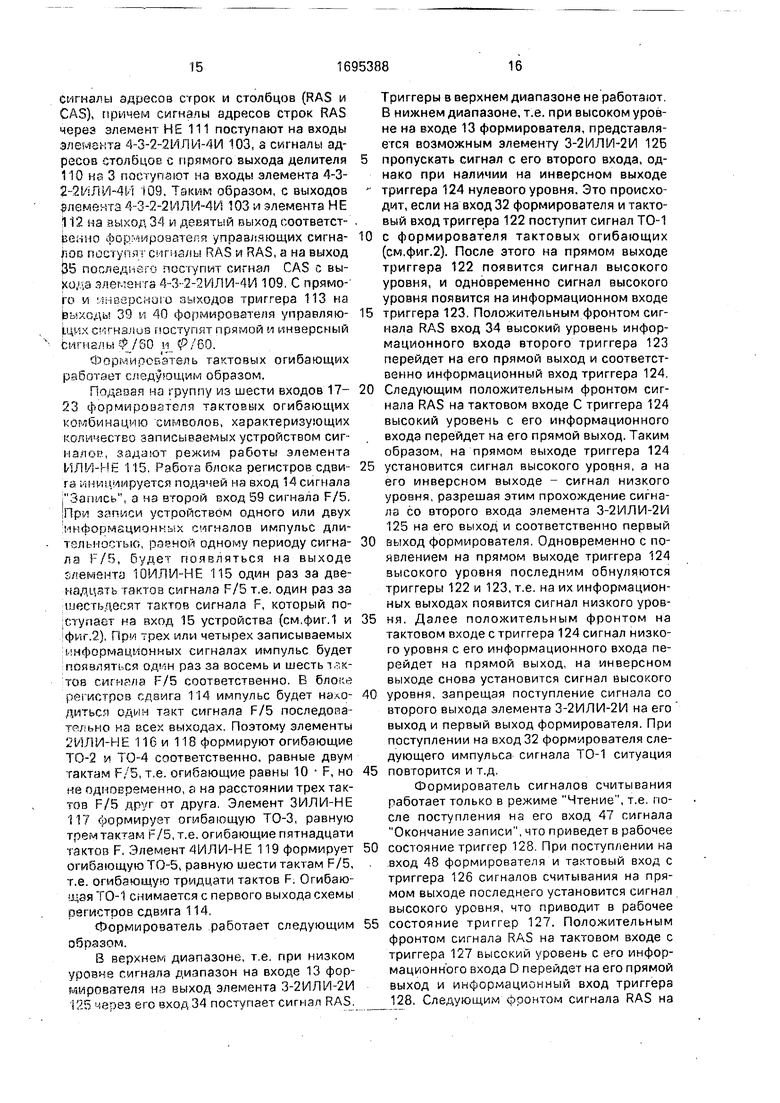

Временные диаграммы работы устройства в режиме Запись представлены на фиг.11, 12, 13; на фиг.11 - запись одного сигнала в верхнем диапазоне; на фиг. 12 запись трех сигналов в верхнем диапазоне: нз фиг.13 - запись одного сигнала в нижнем диапазоне.

Временные диаграммы работы устройства в режимах Регенерация и Чтение приведены на фиг.14. Следует отметить, что для наглядности и компактности изображения диаграмм за основу представления взята не скорость F информационных сигналов a Ft/5 (так как последняя кратна значениям Ft/60; Ft/40; Ft/30).

Формирователь 1 управляющих сигналов работает следующим образом.

Подавая на входы 16, 18, 20. 22 формирователя управляющих сигналов комбинацию символов, характеризующих количество сигналов, подлежащих записи, задают режимы работы элементов 4-3-2-2ИЛИ-4 /1 103 и 109. а также элементов 3-2ИЛИ-2И 98 и 2-2И- 2ИЛИ-НЕ 104.

Подачей на первый вход 13 высокого или низкого уровня сигнала диапазона задают режим работы первого элемента 4-3-2- 2ИЛИ-4И 95. При поступлении сигнала Сброс на вход 24 npi-водят в исходное состояние делитель 96 на 5. первый 97 и пторой 100 делители на 2, а «зкже третий триггер 106, Сигнал Запись, поступая на вход 14, инвертируется элементом 2ИЛИ/2ИЛИ-НЕ 94 и разрешает поступление тактовой скорости F 15 на тактовый вход делителя 96.

Рассмотрим работу формирователя 51 управляющих сигналов в верхнем диапазоне, т.е. низкий уровень на первом его входе. При одном или двух записываемых информационных сигналах (высокий уровень на входе 16 или 18 на прямом и инверсном выходах элемента 2ИЛИ/2ИЛИ-ЧЕ 93 имеем соответственно высокий и низкий уровни, что разрешит поступление сигнала с делителя 100 на 2 через элемент 3-2ИЛИ-2И 98 и элемент 4-3-2-2ИЛИ-4И 95 нз тактовые входы делителя 110 на 3 и триггера 113. В итоге делителем 100 на 3 сформируются

Сигналы адресов строк и столбцов (RAS и CAS), причем сигналы адресов строк RAS через элемент НЕ 111 поступают на входы элемента 4-3-2-2ИЛИ-4И 103, а сигналы адресов столбцов с прямого выхода делителя 110 на 3 поступают на входы элемента 4-3- 2-2ИЛИ-4И Ю9, Таким образом, с выходов элемента 4-3-2-2ИЛИ-4И 103 и элемента НЕ 112 на выход 34 и девятый выход соответственно формирователя управляющих сигналов поступи г сигналы RAS и RAS, а на выход 35 последнего поступит сигнал CAS с выхода элемента 4-3--2-2ИЛИ-4И 109, С прямого и hisepCHOiO зыходов триггера 113 на выходы 39 и 40 формирователя управляющих сигнзлиз поступят прямой и инверсный

Сип1глыФ/80 .

Формирователь тактовых огибающих работает следующим образом.

Подавая на группу из шести входов 17- 23 формирователя тактовых огибающих комбинацию символов, характеризующих количество записываемых устройством сиг- налое, задают режим работы элемента ИЛИ-НЕ 115. Работа блока регистров сдвига инициируется подачей на вход 14 сигнала Запись, а на второй вход 59 сигнала F/5. При записи устройством одного или двух информационных сигналов импульс длительностью, поеной одному периоду сигнала F/5, будет появляться на выходе элемента 10ИЛИ-НЕ 115 один раз за двенадцать тактов сигнала F/5 т.е. один раз за шестьдесят тактов сигнала F, который по- рступает на вход 15 устройства (см.фиг. 1 и фиг.2), Пр /i трех или четырех записываемых информационных сигналах импульс будет появляться один раз за восемь и шесть тлк- тоа сигнала F/5 соответственно. В блоке регистров сдвига 114 импульс будет нэло- диться один такт сигнала F/5 последовательно на всех выходах. Поэтому элементы 2НЛИ-МЕ 116 и 118 формируют огибающие ТО-2 и ТО-4 соответственно, равные двум тактам F/5, т.е. огибающие равны 10 F, но не одновременно, а на расстоянии трех тактов F/5 друг от друга. Элемент ЗИЛИ-НЕ 117 формирует огибающую ТО-3, равную трем тактам F/5, т.е. огибающие пятнадцати тактов F, Элемент 4ИЛИ-НЕ 119 формирует огибающую ТО-5, равную шести тактам F/5, т.е. огибающую тридцати тактов F. Огибающая ТО-1 снимается с первого выхода схемы регистров сдвига 114.

Формирователь работает следующим образом.

В верхнем диапазоне, т.е. при низком уровне сигнала диапазон на входе 13 формирователя на выход элемента 3-2ИЛИ-2И 125 через его вход 34 поступает сигнал RASJ

Триггеры в верхнем диапазоне не работают. В нижнем диапазоне, т.е. при высоком уровне на входе 13 формирователя, представляется возможным элементу 3-2ИЛИ-2И 125

пропускать сигнал с его второго входа, однако при наличии на инверсном выходе триггера 124 нулевого уровня. Это происходит, если на вход 32 формирователя и тактовый вход триггера 122 поступит сигнал ТО-1

0 с формирователя тактовых огибающих (см,фиг.2). После этого на прямом выходе триггера 122 появится сигнал высокого уровня, и одновременно сигнал высокого уровня появится на информационном входе

5 триггера 123. Положительным фронтом сигнала RAS вход 34 высокий уровень информационного входа второго триггера 123 перейдет на его прямой выход и соответственно информационный вход триггера 124.

0 Следующим положительным фронтом сигнала RAS на тактовом входе С триггера 124 высокий уровень с его информационного входа перейдет на его прямой выход. Таким образом, на прямом выходе триггера 124

5 установится сигнал высокого уровня, а на его инверсном выходе - сигнал низкого уровня, разрешая этим прохождение сигнала со второго входа элемента 3-2ИЛИ-2И 125 на его выход и соответственно первый

0 выход формирователя. Одновременно с появлением на прямом выходе триггера 124 высокого уровня последним обнуляются триггеры 122 и 123, т.е. на их информационных выходах появится сигнал низкого уров5 ня. Далее положительным фронтом на тактовом входе с триггера 124 сигнал низкого уровня с его информационного входа перейдет на прямой выход, на инверсном выходе снова установится сигнал высокого

0 уровня, запрещая поступление сигнала со второго выхода элемента 3-21/1ЛИ-2И на его выход и первый выход формирователя. При поступлении на вход 32 формирователя следующего импульса сигнала ТО-1 ситуация

5 повторится и т.д.

Формирователь сигналов считывания работает только в режиме Чтение, т.е. после поступления на его вход 47 сигнала Окончание записи, что приведет в рабочее

0 состояние триггер 128. При поступлении на вход 48 формирователя и тактовый вход с триггера 126 сигналов считывания на прямом выходе последнего установится сигнал высокого уровня, что приводит в рабочее

5 состояние триггер 127. Положительным фронтом сигнала RAS на тактовом входе с триггера 127 высокий уровень с его информационного входа D перейдет на его прямой выход и информационный вход триггера 128. Следующим фронтом сигнала RAS на

прямом и инверсном выходах триггера 128 установятся высокий и низкий уровни соответственно. Одновременно с этим обнулят- ся по цепочке триггеры 126 и 127, что установит нулевой уровень на информационном входе D триггера 128. Далее положительным фронтом на входе С триггера 128 на его прямом и инверсном выходах установятся низкий и высокий уровни соответственно. При поступлении следующего импульса чтения все повторяется.

Переключатель работает следующим образом.

В зависимости от комбинации символов на управляющих входах 16-23 переключателя на его выходы 137-141 поступают те или иные сигналы из группы информационных входов. Так, при одном информационном сигнале, т.е. при высоком уровне на первом входе 16 и низком уровне на втором входе 17 (на входах 18, 20, 22 низкий уровень, а на входах 19, 21, 23 - высокий), на выходы 137, 138 первой и выходы 139-142 второй групп выходов поступит сигнал с первого 143 информационного входа, устанавливается высокий уровень на третьем 18 и низкий на четвертом 19 входах групп управляющих входов, при этом на входах 16, 20, 22 - низкий уровень, а на входах 17, 21, 23 - высокий уровень.

В этом случае на первую группу из двух выходов 137, 138 поступит сигнал с первого информационного входа 143, а на вторую группу из четырех выходов 139-142 - сигнал со второго информационного входа 144. Для записи трех информационных сигналов высокий уровень устанавливается на втором 17, четвертом 19, пятом 20, восьмом 23 входах, а низкий - на остальных входах управляющей группы входов переключателя. При этом на первый 137 и второй 138 выходы первой группы выходов поступят сигналы с первого 143 и второго 144 информационных входов переключателя соответственно. На первый 139 и второй 140 выходы второй группы выходов переключателя поступят сигналы с его третьего информационного входа 145. На третий 141 и четвертый 142 выходы второй группы выходов переключателя поступят сигналы с его второго 144 и первого 143 информационных входов соответственно. Для записи четырех информационных сигналов на втором 17, четвертом 19, шестом 21, седьмом 22 входах устанавливаются высокий уровень, а на остальных входах управляющей группы входов переключателя устанавливается низкий уровень. В этом случае на первый 137 и второй 138 выходы второй группы выходов переключателя поступят сигналы с его первого 143 и

второго 144 информационных соответственно. На первый выход 139 еторой группы выходов переключателя nociynuT сигнал с его третьего 145 информационного входа. На остальные выходы 140, 141 142 второй группы выходов поступит сигнал с четвертого 146 информационного входа переключателя.

Первый и второй блоки буферных реги0 стров могут быть выполнены на двадцати четырех мнсогорежимных буферных регистрах (МБР), каждый типа К589ИР 12 (см В.Л.Горбунов, Д.И.Панфилов, Д.Л.Пресну- хин. Микропроцессоры, Основы построе5 ния микроЭВМ, М., Высшая школа. 1984. с.109, 110).

Шестьдесят входов первых двенадцати МБР (по пять входов в каждом МБР) подсоединены к соответствующим шестидесяти

0 выходам первого распределителя, а шестьдесят выходов следующих двенадцати МБР подсоединены к 60 выходам второго распределителя. Выходы двадцати четырех МБР (по пять выходов в каждом МБР)соеди5 нены с соответствующими информационными входами микросхем памяти накопителя, причем количество микросхем памяти в накопителе равно количеству его информационных выходов в первом блоке буферных

0 регистров. Во втором блоке буферных регистров на тактовый вход с каждого из двадцати четырех МБР поступает сигнал из блока управления, а на входы ВК1 и ВК2 каждого МБР поступает свой сигнал из груп5 пы выходов дешифратора. Сто.двадцать входов МБР (по пять входов в каждом из двадцати четырех МБР) соединены с соответствующими выходами накопителя, а выходы МБР являются выходами всего

0 устройства.

Примером конкретного исполнения накопителя может служить набор из ста двадцати микросхем памяти типа К565РУ6 (см. Электронная промышленность, 1983, №4,

5 с.38), каждый вход которого соединен с соответствующим выходом первого блока буферных регистров, а каждый выход - с соответствующим входом второго блока МБР. Входы регистрации адресов строк RAS

0 и отдельно столбцов CAS объединены между собой соответственно и через первую группу входов накопителя подсоединены:

- вход регистрации адресов строк RAS - к выходу блока управления;

5 - вход регистрации адресов столбцов CAS - к входу блока управления. Следует отметить, что сто двадцать микросхем памяти накопителя условно разбиты на две равных части, причем к первой части относятся микросхемы памяти, куда записываются

сигналы с первого распределителя. Ко второй части относятся микросхемы памяти накопителя, куда записываются сигналы второго распределителя. Входы выбора режима запись/чтение n E микросхем в каждой части объединены между собой и подсоединены;

-еход сигнала выбора режима запись/чтение первой части соединен через управляющую группу входов накопителя с одним из выходов группы выходов блока управления;

-вход сигнала выбора режима запись/чтение второй части соединен через управляющую группу входов накопителя с другим выходом группы выходов блока управления.

Устройство разрабатывается в зависимости от технических характеристик систем, сигналы которых подлежат записи. Покажем, для примера, последовательность расчета динамической памяти для записи синхронных цифровых сигналов со следующими характеристиками:

1.Число входных информационных сигналов от 1 до 4:

2.Диапазон тактовых скоростей, МБИТ/С до 100 по каждому входу;

3.Общий объем памяти V устройства 2 МБИТ,

В качестве элемента памяти выберем полупроводниковое динамическое оперативное ЗУ с произвольной выборкой (ЗУПВ) .емкостью 16 К (16384 БИТ), например, большую интегральную схему (БИС) К565РУ66. Для расчета важны следующие паоамегры;

УЭП 16 К - объем памяти;

Рнакс 4,0 МБИТ - максимальная скорость следования управляющих Сигнале j;

FMHH 0,064 МБИТ/С минимальная скорость следования сигналов.

Общий объем памяти устройства V при таких параметрах микросхем памяти составит Vy 120 -Van 120 16384 1,966080 МБИТ.

Учитывая, что на входе может присутствовать от 1 до 4 информационных сигналов, произведем расчет максимальной скорости Рмакс в каждом конкретном случае.

При одном или двух сигналах на входе устройства Рмакс составит FMaxc К 4,0 МБИТ/С, где К- коэффициент распараллеливания одного сигнала первым и вторым распределителями, Если на входе устройства три сигнала, то , а FMEKc Wc К 4,0 МБИТ/С. При четырех записываемых сигналах ,

РЧакс Тмакс -К 4.0 30-120 МБИТ/С

На следующем этапе, исходя из заданных характеристик, рассмотрим возможности разработки блоков и узлов устройства на основе выпускаемой отечественной прог

мышленностью элементной базы, Переключатель (фиг. 10) легко может быть разработан на основе микросхем эмиттерно-связанной логики (ЭСЛ) серий К500 или К1500, в частности микросхем типа К500ЛК117 или К500

ЛС118М, К500ЛС119М, К500ЛК118 (Справочник. Применение интегральных микросхем в электронной вычислительной технике /Под ред. Б.Н.Файзулаева, Б.В.Та- рабрина.М., Радио и связь, 1986.Справочник по интегральным микросхемам,/Под ред. Б.В.Тарабрина, М.; Энергия, 1980),

Первый и второй распределители разрабатываются с использованием микросхем К500ИР141, К1500ИР141, К500ЛС118,

К5000ЛС119, К500ЛМ101. В накопителе можно использовать микросхемы памяти типа К565РУ6, КР581РУ4, К565РУЗ, К565РУ5. В первом и втором блоках буферных регистров удобно использовать МБР типа К589ИР12 или К565ИР12, Так как блок управления используется во всех режимах, то рассмотрим Отдельно каждый его узел. В формирователе тактовых огибающих (фиг.6) можно использовать микросхемы

К500ИР141 или К1500ИР141, К500ЛС119, К500ЛМ105, К500ЛМ109. Формирователь (фиг.7) может быть разработан на основе микросхем К500ТН231, К500ЛС118, К500ЛМ102. Блок элементов И-ИЛИ разрабатываетсянамикросхемах

К155ЛРЗ/ЛР4/, К555 ЛР13 или К531ЛР9П и К155ЛН1. В блоке управления могут использоваться отдельные элементы типа К531ЛР9П или К155ЛР4, а также К155ЛАЗ и

ЛИ1. Формирователь сигналов считывания (фиг.8) разрабатывается на триггерах типа К155ТМ2 или К531ТМ2. Генератор тактовых импульсов можно собрать по схеме 588. (Справочник под ред. В.Б.Тарабрина), подбирая по необходимости нужные значения резисторов и конденсаторов, Формирователь управляющих сигналов (фиг,5) может быть построен с использованием микросхем типа К500ЛС119, или К1500ЛК118,

К500ТМ231 Д500ЛС118, К500ЛМ102, К155ЛР1.

Делители на 2, на 3, на 5, используемые в ФУС, легко собрать по схемам на с.572- 574 (Справочник под ред.Б.В.Тарабрина),

где используются микросхемы К500ТМ231. Блок И-ИЛИ-НЕ (фиг.2) разрабатывается на основе микросхем К531ЛР9П. В качестве дешифра тора (фиг.1) используются микросхемы К155ИДЗ. Счетчик и счетчик регенерации (фиг.1) выполнены на микросхемах К155ИЕ7.

Формула изобретения

Буферное динамическое оперативное запоминающее устройство, содержащее накопитель, выходы которого подключены к информационным входам первого блока буферных регистров, выходы которого являются информационными выходами устройства, счетчик, дешифратор, переключатель, информационные входы которого являются информационными входами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит первый и второй распре- делители сигналов, блок элементов И-ИЛИ-НЕ, блок управления, второй блок буферных регистров и счетчик регенерации, выходы которого подключены к входам первой группы блока элементов И-ИЛИ-НЕ, к входам второй группы которого подключены информационные выходы счетчика адресов, выходы старших разрядов которого подключены к соответствующим входам блока управления, вход сброса счетчика адресов является соответствующим входом устройства и подключен к соответствующему входу блока управления, входы диапазона и чтения и выход окончания записи которого являются соответствующими входами и выходами устройства, счетный вход счетчика регенерации подключен к соответствующему выходу блока управления, выходы коммутации адресов строк и столбцов которого подключены к управляющим входам блока элементов И-ИЛЙ-НЕ, выходы которого подключены к адресным входам

накопителя, информационные входы которого подключены к выходам второго блока буферных регистров, входы первой и второй групп которого подключены к выходам соответственно первого и второго распределителей сигналов, информационные входы которых подключены к выходам соответственно первой и второй групп переключателя, управляющие входы которого являются

входами числа сигналов устройства и подключены к соответствующим входам первого и второго распределителей сигналов и блока управления, входы записи и тактовых сигналов которого являются соответствующими входами устройства и подключены к управляющим входам первого и второго распределителей сигналов, входы управления распределением которых подключены к соответствующим

выходам блока управления, выходы стро- бирования которого подключены к соответствующим входам второго блока буферных регистров, входы регистрации адресов, импульсов записи и чтения накопителя подключены к соответствующим выходам блока управления, тактовый выход которого подключен к соответствующему входу первого блока буферных регистров, стробирующие входы которого

подключены к выходам дешифратора, входы которого являются адресными входами второй группы устройства, выходы разрешения распределения блока управления подключены к соответствующим входам

первого и второго распределителей сигналов, счетные входы счетчика адресов подключены к соответствующим выходам блока управления.

1Ј

U

9

№

J.

Of

Pi,

ТЯ

22 6Ј

8Ј

SE

№

к.

ЖушЩЩяГ

Јгж

и

VZ

9Г

51

ы

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для индикации | 1985 |

|

SU1261005A1 |

| Устройство для регистрации информации | 1989 |

|

SU1603412A1 |

| УСТРОЙСТВО ДИАГНОСТИЧЕСКОГО КОНТРОЛЯ КАНАЛА ВОСПРОИЗВЕДЕНИЯ АППАРАТУРЫ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ | 1991 |

|

RU2024968C1 |

Изобретение относится к технике запоминающих устройств, в частности к запоминающим устройствам динамического типа, и может быть использовано в системах сбора, регистрации и обработки информации Цель изобретения - повышение быстродействия устройства. Устройство содержит накопитель, счетчик, дешифратор, переключатель, первый блок буферных регистров и накопитель, второй блок буферных регистров, блок управления. Устройство может использоваться для записи цифровых сигналов в диапазоне тактовых скоростей, а также поедставляет возможность записывать различное количество входных информационных сигналов без изменения структуры устройства. Считывание записанной информации может производиться в широком диапазоне тактовых скоростей. 13 ил.

ZIт

Фиг. 2

Фиг. 3

Фиг А

Фиг. 5

Г

Фиг. 8

Ф иг. 6

PU2

п

Фиг. 9

JUT4LJl JLJLn r lLn n . . .JlJ-LJLJUJunJLJUAJLJU . ; UUIJULJULJLJULJUI . . ТППЛПППППГТПГ

LT

и

u-

Ц- JF7

u;ui i

шшгишлля 1гшляши ллпллпш1лллпш1п. шишшллмлллЛалллг srj

Ili TLTU

тшишппг иш111111Ш 1Ш1Ш11шгаш1ИШ1ттшшвж imiuiiuiiuuiiu

88C969L

.th

.. #

..s/f

. JLJLJl ri n fLJl rLJLJ H . jriLJLJUULjr-U n T 3f . -JLJLJLJULJLJLJl-JT-T se

-inrTTinnr-inr-inr «f

1J

u-

Ц- JF7

// 37

OW&

| Буферное запоминающее устройство | 1985 |

|

SU1251181A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1019492A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-11-30—Публикация

1989-05-06—Подача