Изобретение относится к вычислительной технике и технике связи и может быть использовано в цифровых системах передачи информации.

Цель изобретения повышение быстродействия устройства.

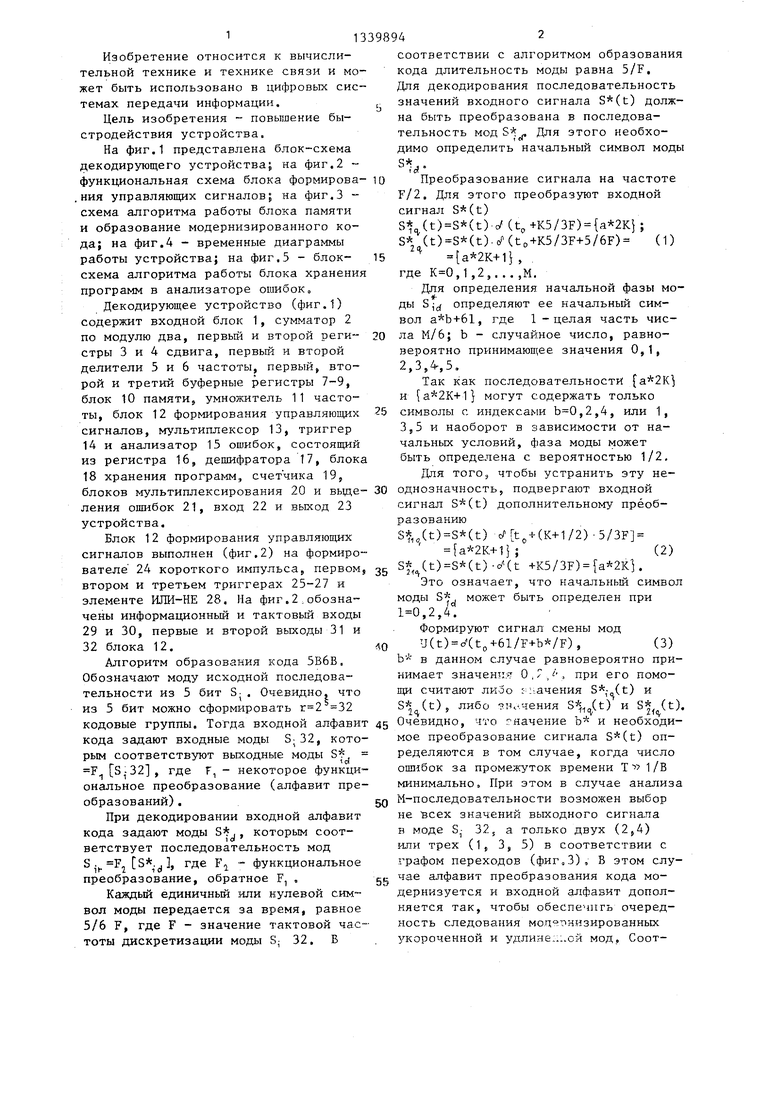

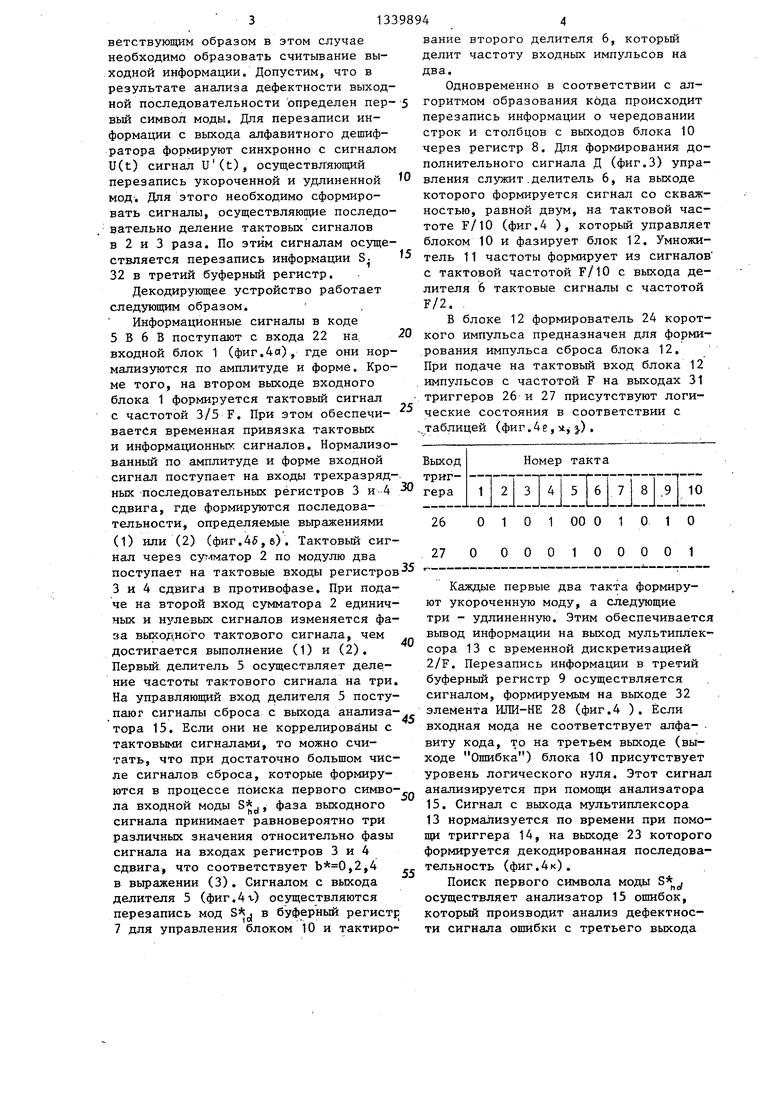

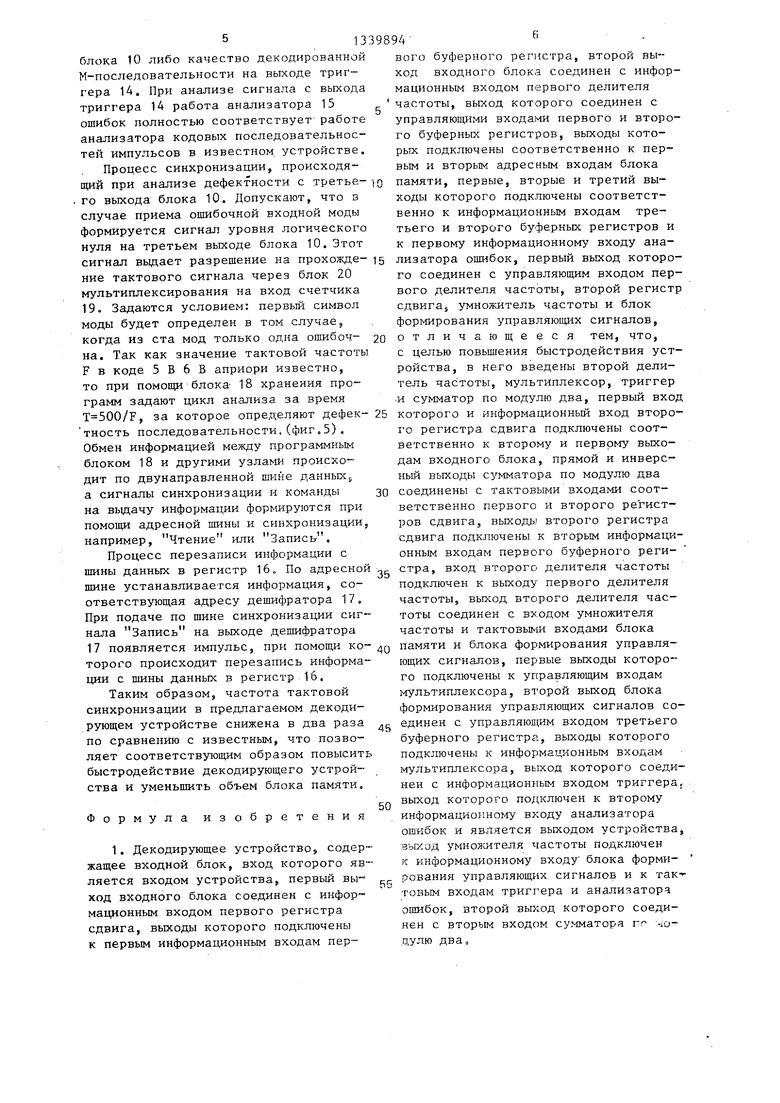

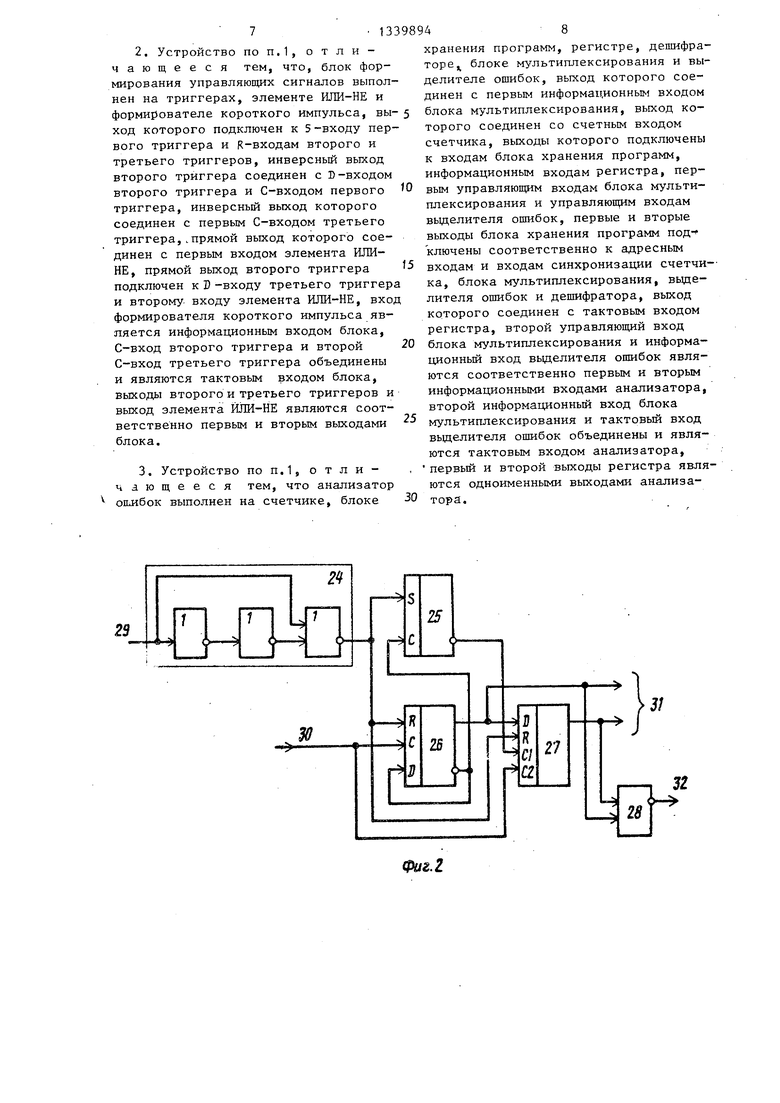

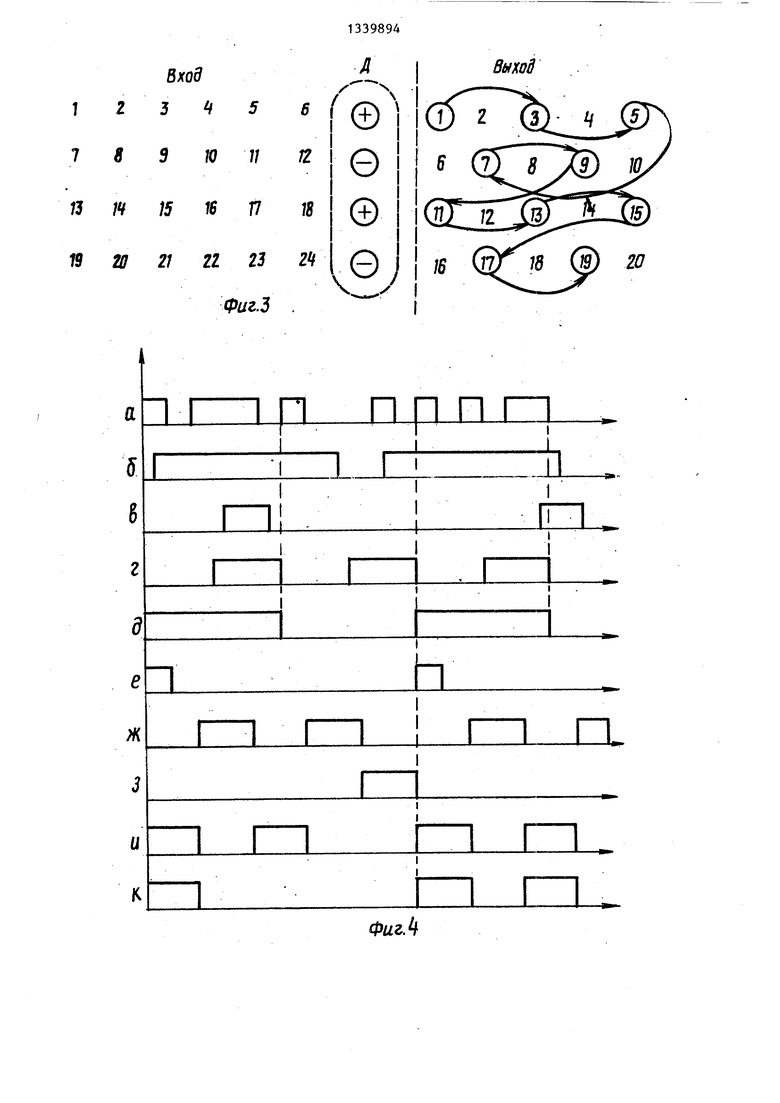

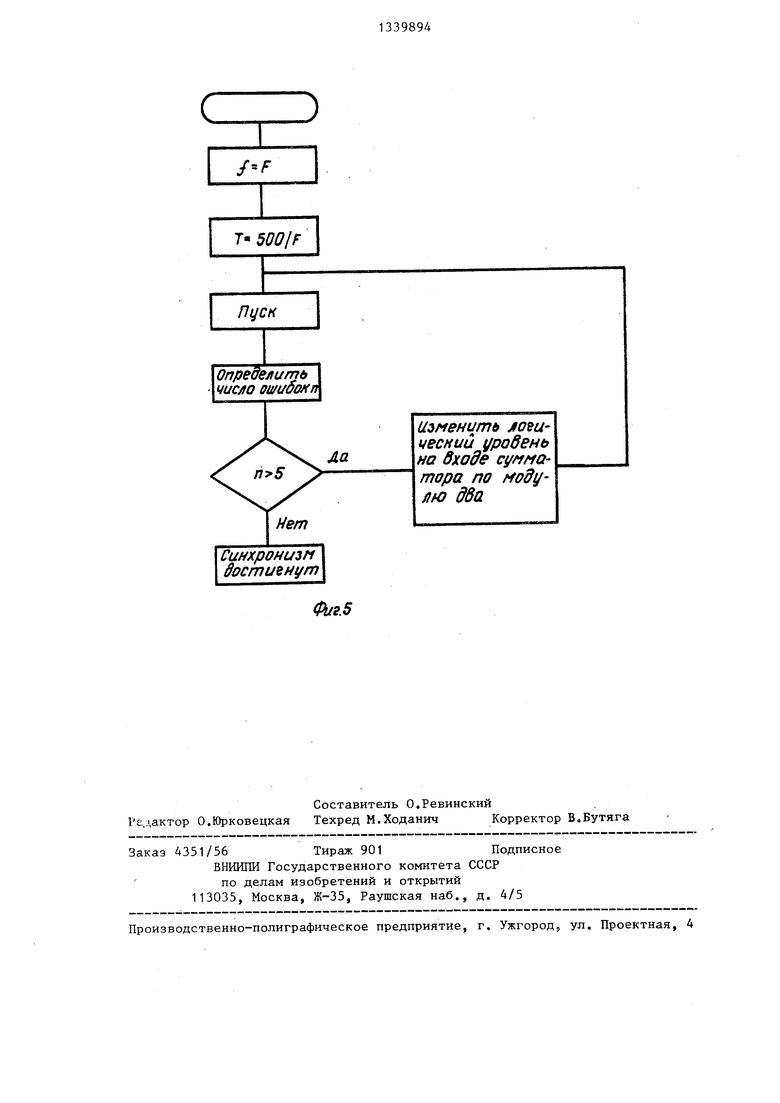

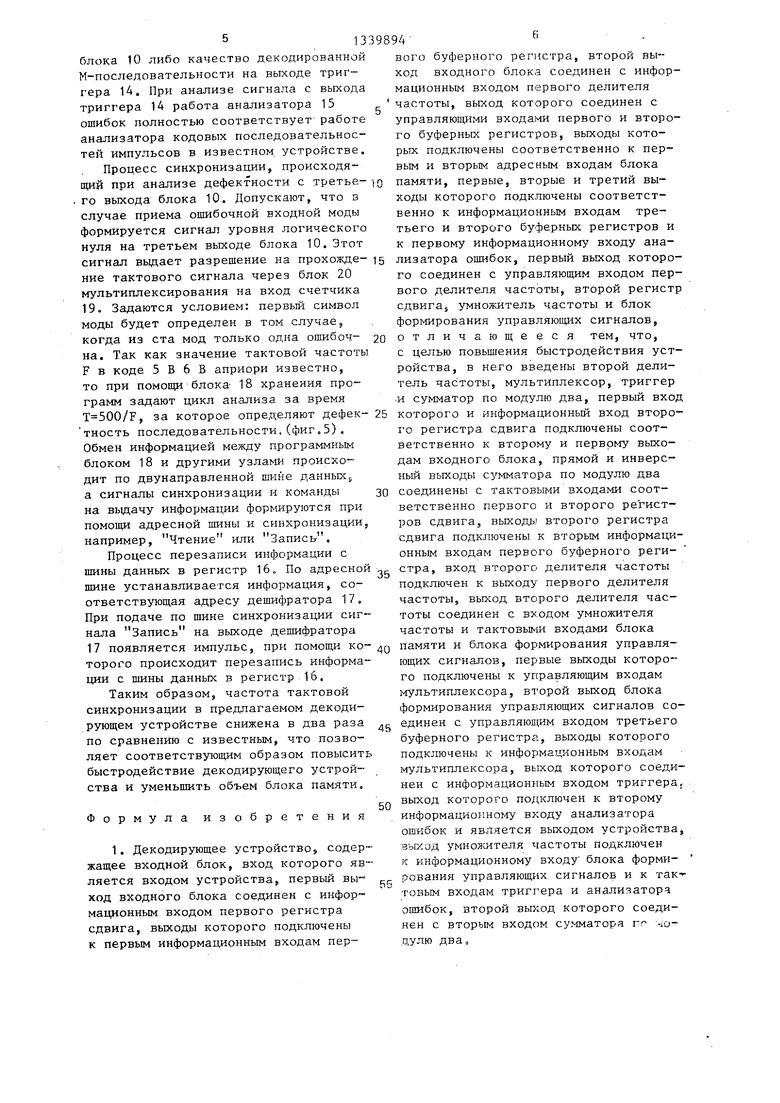

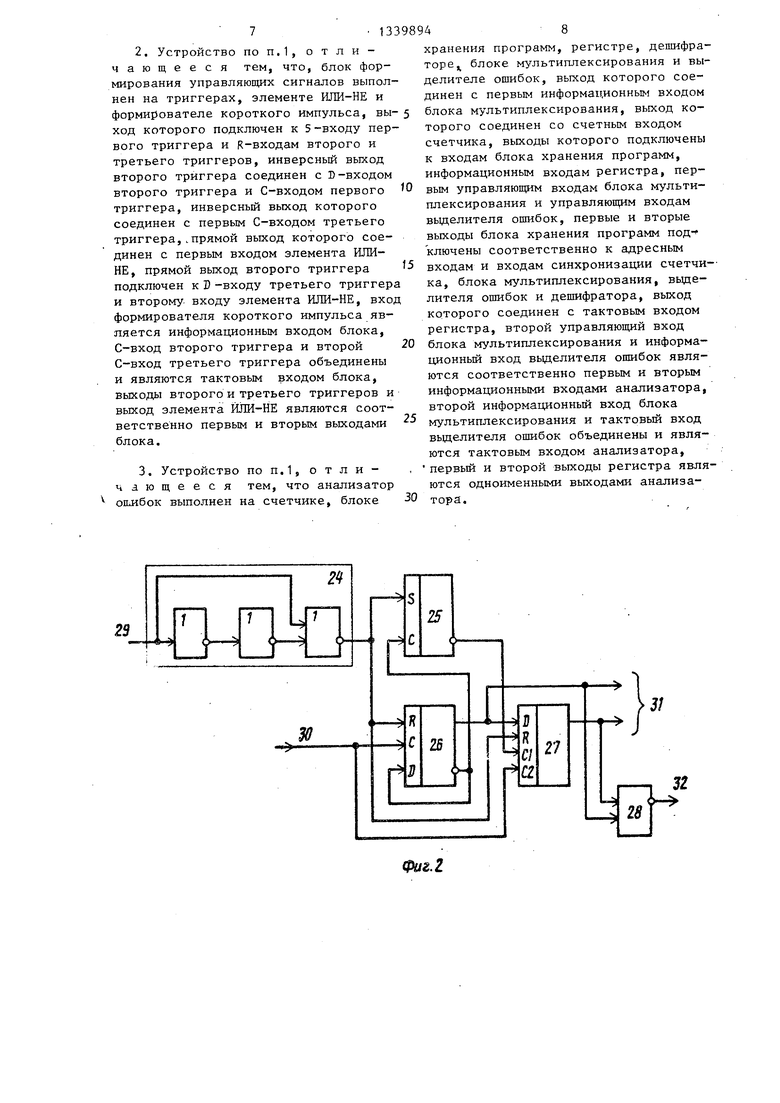

На фиг.1 представлена блок-схема декодирующего устройства; на фиг,2 - функциональная схема блока формирова .ния управляющих сигналов; на фиг.З - схема алгоритма работы блока памяти и образование модернизированного кода; на фиг.4 - временные диаграммы работы устройства; на фиг.З - блок- схема алгоритма работы блока хранени программ в анализаторе ошибок

Декодирующее устройство (фиг.1) содержит входной блок 1, сумматор 2 по модулю два, первый и второй регистры 3 и 4 сдвига, первый и второй делители 5 и 6 частоты, первый, второй и третий буферные регистры 7-9, блок 10 памяти умножитель 11 часто

ты, блок 12 формирования управляющих

Так как последовательности и ta 2K+1} могут содержать только 25 символы с индексами ,2,4, или 1, 3,5 и наоборот в зависимости от начальных условий, фаза моды может быть определена с вероятностью 1/2,

Для того, чтобы устранить эту несигналов, мультиплексор 13, триггер

14 и анализатор 15 ошибок, состоящий

из регистра 16, дешифратора 17, блока

18 хранения программ, счетчика 19j,

блоков мультиплексирования 20 и выде- 30 однозначность, подвергают входной

ления опшбок 21, вход 22 и выход 23 сигнал S(t) дополнительному прёобустройства.

Блок 12 формирования управляющих сигналов выполнен (фиг.2) на формиро

разованию

S (t)SA(t) + (K+1/2)-5/3F

U 2K+1} ;

(2

вателе 24 короткого импульса, первом, 35 S(t)S(t) c/ (t +K5/3F) .

втором и третьем триггерах 25-27 и элементе ИЛИ-НЕ 28. На фиг.2,обозначены информационный и тактовый входы 29 и 30, первые и второй выходы 31 и 32 блока 12.

Алгоритм образования кода 5В6В, Обозначают моду исходной последовательности из 5 бит S-. Очевидно, что из 5 бит можно сформировать 32

Это означает, что начальный симво моды S может быть определен при ,2,4.

Формируют сигнал смены мод 0 U(t) /(t +61/F+bA/F), (3) b в данном случае равновероятно при нимает значени 7 О,/, , при его помощи считают лиЗо :-:1ачения .(t) и S(t), либо ..чения S,(t) и S(t

Формируют сигнал смены мод 0 U(t) /(t +61/F+bA/F), (3) b в данном случае равновероятно принимает значени 7 О,/, , при его помощи считают лиЗо :-:1ачения .(t) и S(t), либо ..чения S,(t) и S(t).

кодовые группы. Тогда входной алфавит 45Очевидно, что гяачение Ъ и необходикода задают входные моды S- 32, кото-мое преобразование сигнала S(t) опрым соответствуют вьпсодные моды S ределяются в том случае, когда число

F S.32, где F, - некоторое функци-oimi6oK за промежуток времени Т 1/В

овальное преобразование (алфавит пре-минимально. При этом в случае анализа

образований).50 -последовательности возможен выбор

При декодировании входной алфавитне всех значений выходного сигнала

кода задают моды , которым соот-в моде S- 32, а только двух ()

или трех (1j 3, 5) в соответствии с графом переходов (фиг.З), В этом слу- gj- чае алфавит преобразования кода модернизуется и входной алфавит дополняется так, чтобы обеспечить очередность следования мод -Г низированных укороченной и удлине:.:.ой мод, Соответствует последовательность мод

S . F, S.j , где t - функциональное

преобразование, обратное F, ,

Каждый единичный или нулевой символ моды передается за время, равное 5/6 F, где F - значение тактовой частоты дискретизации моды S 32. В

соответствии с алгоритмом образования кода длительность моды равна 5/F, Для декодирования последовательность значений входного сигнала S(t) должна быть преобразована в последовательность мод S ,. Для этого необхоt f

димо определить начальный символ моды

Я

5

Преобразование сигнала на частоте 7/2, Для этого преобразуют входной сигнал S(t)

S(t)S(t) V (t +K5/3F) ; S (t)S(t).(to+K5/3F+5/6F) (1)

aA2K-H} , , где ,1,2,...,M.

Для определения начальной фазы моды Sjj определяют ее начальный символ , где 1 -целая часть числа М/6; b - случайное число, равновероятно принимающее значения 0,1, 2,3,4,5,

Так как последовательности и ta 2K+1} могут содержать только 5 символы с индексами ,2,4, или 1, 3,5 и наоборот в зависимости от начальных условий, фаза моды может быть определена с вероятностью 1/2,

Для того, чтобы устранить эту не0

разованию

S (t)SA(t) + (K+1/2)-5/3F

U 2K+1} ;

(2)

35 S(t)S(t) c/ (t +K5/3F) .

Это означает, что начальный символ моды S может быть определен при ,2,4.

Формируют сигнал смены мод 0 U(t) /(t +61/F+bA/F), (3) b в данном случае равновероятно принимает значени 7 О,/, , при его помощи считают лиЗо :-:1ачения .(t) и S(t), либо ..чения S,(t) и S(t).

45Очевидно, что гяачение Ъ и необходив моде S- 32, а только двух ()

или трех (1j 3, 5) в соответствии с графом переходов (фиг.З), В этом слу- чае алфавит преобразования кода модернизуется и входной алфавит дополняется так, чтобы обеспечить очередность следования мод -Г низированных укороченной и удлине:.:.ой мод, Соот

313

ветствующим образом в этом случае необходимо образовать считывание выходной информации/Допустим, что в результате анализа дефектности выходной последовательности определен пер- вьш символ моды. Для перезаписи информации с выхода алфавитного дешифратора формируют синхронно с сигналом U(t) сигнал U (t), осуществляющий перезапись укороченной и удлиненной мод. Для этого необходимо сформировать сигналы, осуществляющие последовательно деление тактовых сигналов в 2 и 3 раза. По этим сигналам осуществляется перезапись информации S 32 в третий буферный регистр.

Декодирующее устройство работает следующим образом.

Информационные сигналы в коде 5 В 6 В поступают с входа 22 на входной блок 1 (фиг.4с(), где они нормализуются по амплитуде и форме. Кроме того, на втором выходе входного блока 1 формируется тактовый сигнал с частотой 3/5 F. При этом обеспечивается временная привязка тактовых и информационных сигналов. Нормализованный по амплитуде и форме входной сигнал поступает на входы трехразрядных последовательных регистров 3 и 4 сдвига, где формируются последовательности, определяемые выражениями

(1) или (2) (фиг.45,в). Тактовый сигнал через сут-тматор 2 по модулю два поступает на тактовые входы регистров 3 и 4 сдвига в противофазе. При подаче на второй вход сумматора 2 единичных и нз левых сигналов изменяется фаза выходного тактового сигнала, чем достигается выполнение (1) и (2). Первый, делитель 5 осуществляет деление частоты тактового сигнала на три На управляющий вход делителя 5 поступают сигналы сброса с выхода анализатора 15. Если они не коррелированы с тактовыми сигналами, то можно считать, что при достаточно большом числе сигналов сброса, которые формируются в процессе поиска первого символа входной моды S, фаза выходного сигнала принимает равновероятно три различных значения относительно фазы сигнала на входах регистров 3 и 4 сдвига, что соответствует ,2,4 в выражении (3). Сигналом с вькода делителя 5 (фиг.4г) осуществляются

перезапись мод

7 для управления блоком

в буферный регист : 10 и тактиро0

5

5

0

ванне второго делителя 6, который делит частоту входных импульсов на два.

Одновременно в соответствии с алгоритмом образования кода происходит перезапись информации о чередовании строк и столбцов с выходов блока 10 через регистр 8, Для формирования дополнительного сигнала Д (фиг.З) управления служит.делитель 6, на выходе которого формируется сигнал со скважностью, равной двум, на тактовой частоте F/10 (фиг.4 ), который управляет блоком 10 и фазирует блок 12. Умножитель 11 частоты формирует из сигналов с тактовой частотой F/10 с выхода делителя 6 тактовые сигналы с частотой F/2.

В блоке 12 формирователь 24 короткого импульса предназначен для формирования импульса сброса блока 12, При подаче на тактовый вход блока 12 импульсов с частотой F на выходах 31 триггеров 26 и 27 присутствуют логические состояния в соответствии с .таблицей (фиг.4e,.).

Каждые первые два такта формируют укороченную моду, а следующие три - удлиненную. Этим обеспечивается вьшод информации на выход мультиплексора 13 с временной дискретизацией 2/F. Перезапись информации в третий буферный регистр 9 осуществляется сигналом, формируемым на выходе 32

элемента ИЛИ-НЕ 28 (фиг.4 ). Если входная мода не соответствует алфа- . виту кода, то на третьем выходе (выходе Ошибка) блока 10 присутствует уровень логического нуля. Этот сигнал анализируется при помощи анализатора 15. Сигнал с выхода мультиплексора 13 нормализуется по времени при помощи триггера 14, на выходе 23 которого формируется декодированная последовательность (фиг.4к).

Поиск первого символа моды осуществляет анализатор 15 ошибок, который производит анализ дефектности сигнала ошибки с третьего выхода

блока 10 либо качество декодированной М-последовательности на выходе триггера 14. При анализе сигнала с выхода триггера 14 работа анализатора 15 ошибок полностью соответствует работе анализатора кодовых последовательнос- тей импульсов в известном устройстве.

Процесс синхронизации, происходящий при анализе дефектности с третьего выхода блока 10. Допускают, что в случае приема ошибочной входной моды формируется сигнал уровня логического нуля на третьем выходе блока 10. Этот сигнал выдает разрешение на прохождение тактового сигнала через блок 20 мультиплексирования на вход счетчика 19. Задаются условием: первый символ моды будет определен в том случае, когда из ста мод только одна ошибочна. Так как значение тактовой частоты F в коде 5 В 6 В априори известно, то при помощи блока- 18 хранения программ задают цикл анализа, за время T 500/F, за которое определяют дефек- тность пocлeдoвaтeльнocтvI. (фиг.5) . Обмен информацией между программным блоком 18 и другими узлами происходит по двунаправленной шине данных а сигналы синхронизации и команды на вьщачу информации формируются при помощи адресной шины и синхронизацииj например, Чтение или Запись.

Процесс перезаписи информации с шины данных в регистр 16, По адресной шине устанавливается информация, соответствующая адресу дешифратора 17, При подаче по шине синхронизации сигнала Запись на выходе дешифратора 17 появляется импульс, при помощи которого происходит перезапись информации с шины данных в регистр 16.

Таким образом, частота тактовой синхронизации в предлагаемом декодирующем устройстве снижена в два раза по сравнению с известным, что позволяет соответствующим образом повысить быстродействие декодирующего устройства и уменьшить объем блока памяти.

Формула изобретения

1. Декодирующее устройство, содержащее входной блок, вход которого является входом устройства, первый вы ход входного блока соединен с информационным входом первого регистра сдвига, выходы которого подключены к первым информационным входам первого буферного регистра, второй выход входного блока соединен с информационным входом первого делителя частоты, выход которого соединен с управляющими входами первого и второго буферных регистров, выходы которых подключены соответственно к первым и вторым адресным входам блока

памяти, первые, вторые и третий выходы которого подключены соответственно к информационным входам третьего и второго буферных регистров и к первому информационному входу ана5 лизатора ошибок, первый выход которого соединен с управляющим входом первого делителя частоты, второй регистр сдвига5 умножитель частоты и блок формирования управляющих сигналов,

0 отличающееся тем, что, с целью повьшгения быстродействия устройства, в него введе ы второй делитель частоты, мультиплексор, триггер и сумматор по модулю два, первый вход

5 которого и информационный вход второго регистра сдвига подключены соответственно к второму и первому выходам входного блока, прямой и инверсный выходы сумматора по модулю два

0 соединены с тактовыми входами соответственно первого и второго рег ист- ров сдвига, выходы второго регистра сдвига подключены к вторым информационным входам первого буферного региf- стра, вход второго делителя частоты подключен к выходу первого делителя частоты, выход второго делителя частоты соединен с входом умножителя частоты и тактовыми входами блока

0 памяти и блока формирования управляющих сигналов, первые выходы которого подключены к управляющим входам 1 4ультиплексора, второй выход блока формирования управляющих сигналов сос единен с управляющим входом третьего буферного регистра, выходы которого подключены к информационным входам мультиплексора, выход которого соединен с информационным входом триггера, выход которого подключен к второму информационног-гу входу анализатора оиибок и является выходом устройства, выход умножителя частоты подключен к информационному входу блока форми- рования yпpaвляюш ix сигналов и к так- товым входам триггера и анализатора ошибок, второй вьпсод которого соединен с вторым входом сумматора гг- -io- ,цулю два с

0

5

2. Устройство ПОП.1, отличающееся тем, что, блок формирования управляющих сигналов выполнен на триггерах, элементе ИЛИ-НЕ и формирователе короткого импульса, выход которого подключен к 5-входу первого триггера и R-входам второго и третьего триггеров, инверсный выход второго триггера соединен с D-входом второго триггера и С-входом первого триггера, инверсный выход которого соединен с первым С-входом третьего триггера,.прямой выход которого соединен с первым входом элемента ИЛИ- НЕ, прямой выход второго триггера подключен к D-входу третьего триггера и второму- входу элемента ИЖ-НЕ, вход формирователя короткого импульса является информационным входом блока, С-вход второго триггера и второй С-вход третьего триггера объединены и являются тактовьм входом блока, выходы второго и третьего триггеров и выход элемента ШШ-НЕ являются соответственно первым и вторым выходами блока.

3. Устройство по n.l, о т л и - чающееся тем, что анализатор одлбок выполнен на счетчике, блоке 0

хранения программ, регистре, дешифраторе , блоке мультип-пексирования и выделителе ошибок, выход которого соединен с первым информационным входом блока мультиплексирования, выход которого соединен со счетным входом счетчика, выходы которого подключены к входам блока хранения программ, информационным входам регистра, первым управляющим входам блока мультиплексирования и управляющим входам вьщелителя ошибок, первые и вторые выходы блока хранения программ под- ключены соответственно к адресным входам и входам синхронизации счетчика, блока мультиплексирования, вьщелителя ошибок и дешифратора, выход которого соединен с тактовым входом регистра, второй управляющий вход блока мультиплексирования и информационный вход выделителя ошибок являются соответственно первым и вторым информационными входами анализатора, второй информационный вход блока мультиплексирования и тактовый вход вьщелителя ошибок объединены и являются тактовым входом анализатора, первый и второй выходы регистра являются одноименными выходами анализатора.

Фиг. 2.

Вход 3 Ч 5

1339894

Л

г::л

Ю 11 1Z

13 Щ 15 16 П

18

19 20 21 22 23 24

Фиг.З .

ч

Выход

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1987 |

|

SU1497745A1 |

| Анализатор кодовых последовательностей импульсов (его варианты) | 1984 |

|

SU1238243A1 |

| Кодирующее устройство | 1987 |

|

SU1510093A1 |

| Анализатор кодовых последовательностей импульсов | 1985 |

|

SU1305868A2 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Генератор кодовых последовательностей импульсов | 1987 |

|

SU1531080A1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| Дельта-кодер | 1987 |

|

SU1441482A1 |

| Преобразователь дельта-модулированного сигнала в импульсно-кодомодулированный сигнал | 1985 |

|

SU1282336A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в цифровых системах передачи информации позволяет повысить быстродействие устройства. Декодирующее устройство содержит входной блок 1, делитель 5 частоты, регистры 3,4 сдвига, буферные регистры 7-9, блок 10 памяти, умножитель 11 частоты и анализатор 15 ошибок. Благодаря введению сумматора 2 по модулю два, делителя 6 частоты, блока 12 формирования сигналов управления, мультиплексора 13 и триггера 14 декодирование кода 5В6В осуществляется с вдвое : меньшей тактовой частотой, чем в известном устройстве за счет попеременного анализа укороченной и удлиненной мод входного кода. 2 з.п. ф-лы, 5 ил., 1 табл. Q (Л 00 со Х) 00 () 4

ФигЛ

С

т- 500IF

Определить число 011/иоо/ п

изменить лоъи- чесний дробень на Входе ct/nмотора по ноду- лю два

Синхронизм достигнут

Составитель О.Ревинский l ,j,aKTop О.Юрковецкая Техред М.Ходанич Корректор В.Бутяга

Заказ 4351/56 Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Декодирующее устройство | 1980 |

|

SU917341A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для синхронизации @ -последовательности | 1984 |

|

SU1225002A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Анализатор кодовых последовательностей импульсов (его варианты) | 1984 |

|

SU1238243A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Fernemelde -technik, 1981, № 6, с.214-218, рис.3. | |||

Авторы

Даты

1987-09-23—Публикация

1985-12-04—Подача