(5) УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ЧАСТОТЫ ВРАЩЕНИЯ ЭЛЕКТРОДВИГАТЕЛЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для стабилизации частоты вращения электродвигателя | 1989 |

|

SU1686681A1 |

| СТАБИЛИЗИРОВАННЫЙ ЭЛЕКТРОПРИВОД | 2011 |

|

RU2462809C1 |

| Частотно-фазовый дискриминатор | 1988 |

|

SU1589373A1 |

| Устройство для управления ведущим шаговым двигателем | 1981 |

|

SU999022A1 |

| Электропривод постоянного тока | 1986 |

|

SU1661951A1 |

| Способ цифрового измерения отклонения скорости от заданной и устройство для его осуществления | 1988 |

|

SU1615620A1 |

| Частотно-фазовый дискриминатор | 1983 |

|

SU1356191A1 |

| Способ регулирования частоты вращения электродвигателя переменного тока | 1987 |

|

SU1471277A1 |

| Устройство для измерения временных параметров радиоимпульсов | 1977 |

|

SU687415A1 |

| Электропривод постоянного тока | 1991 |

|

SU1786630A1 |

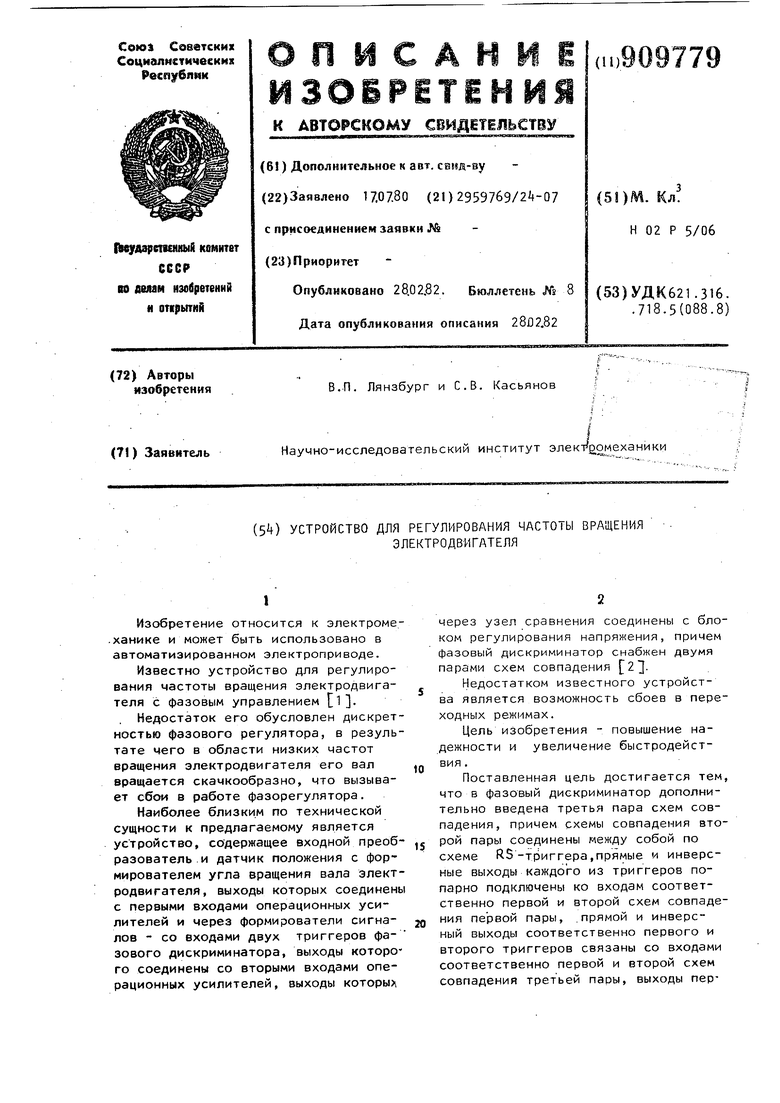

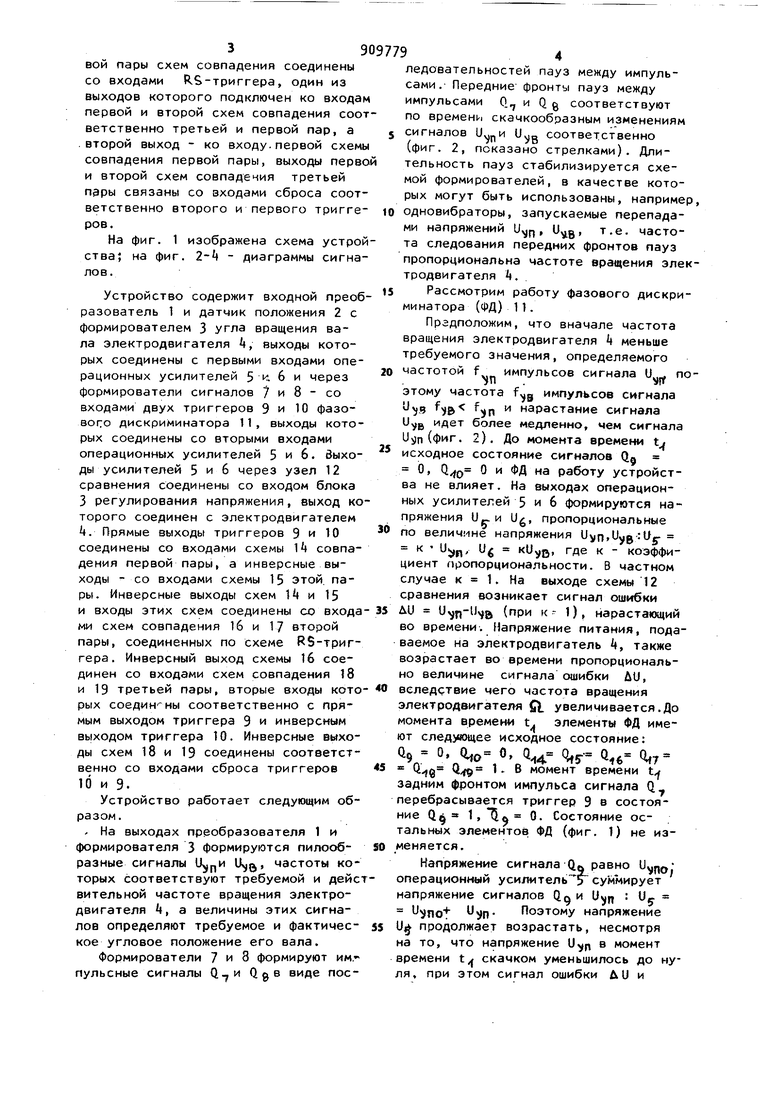

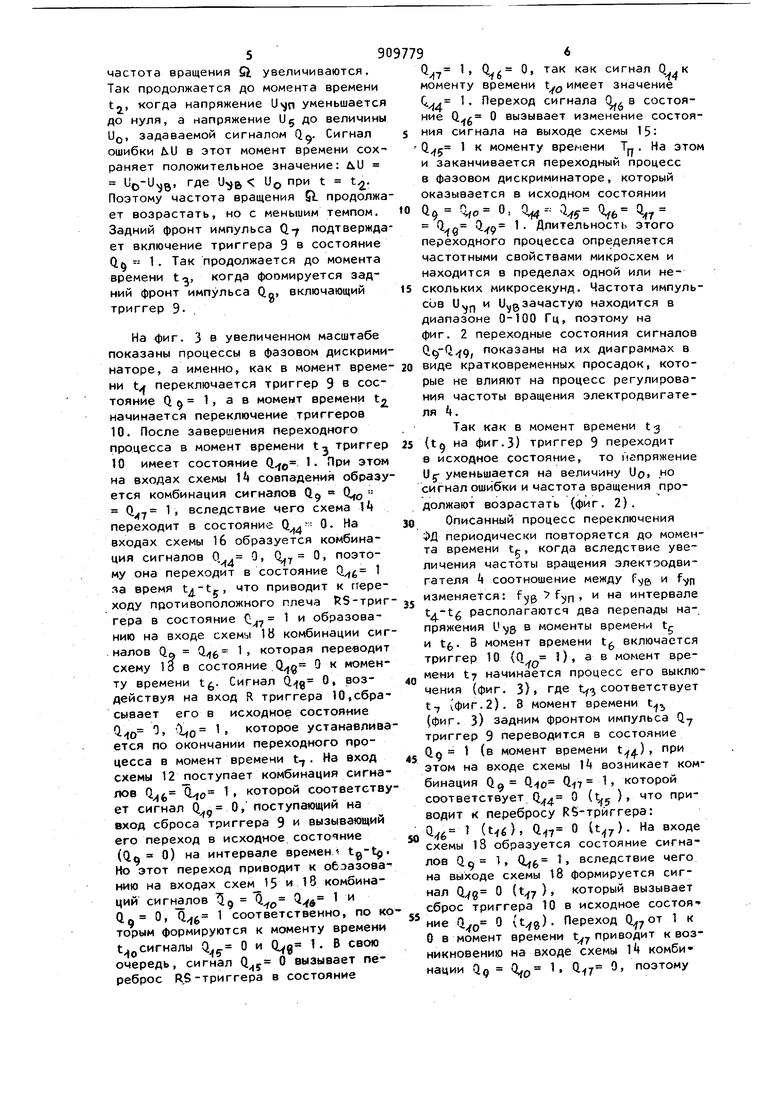

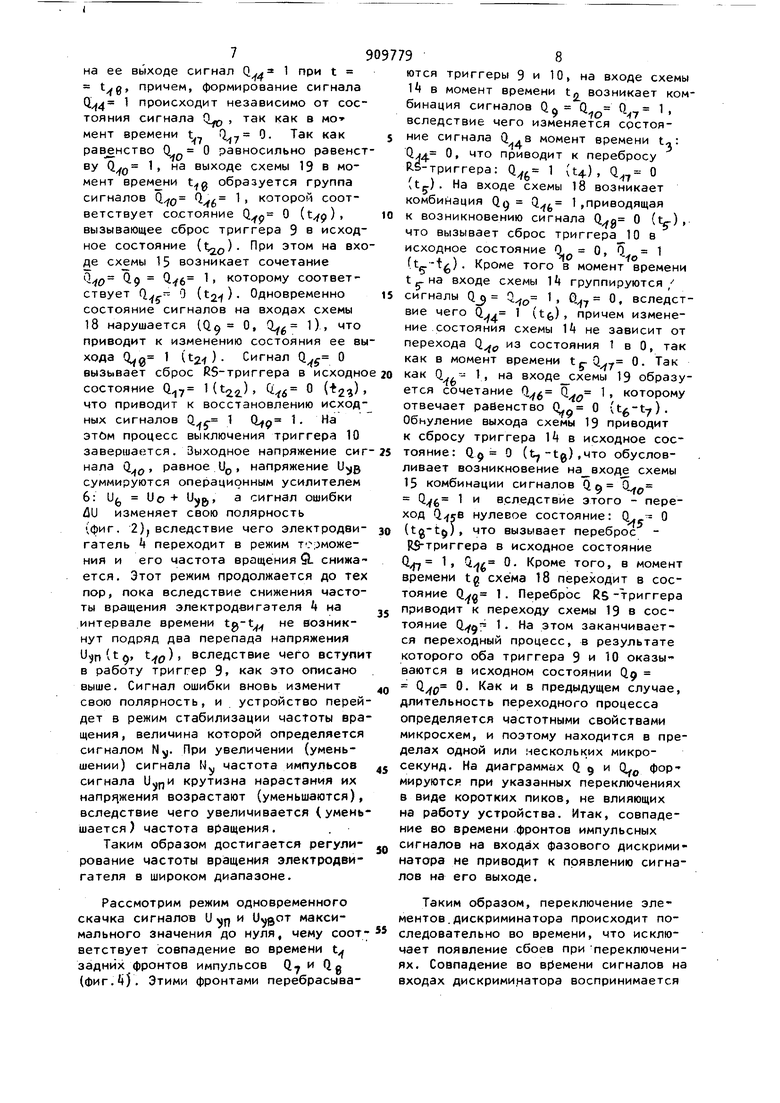

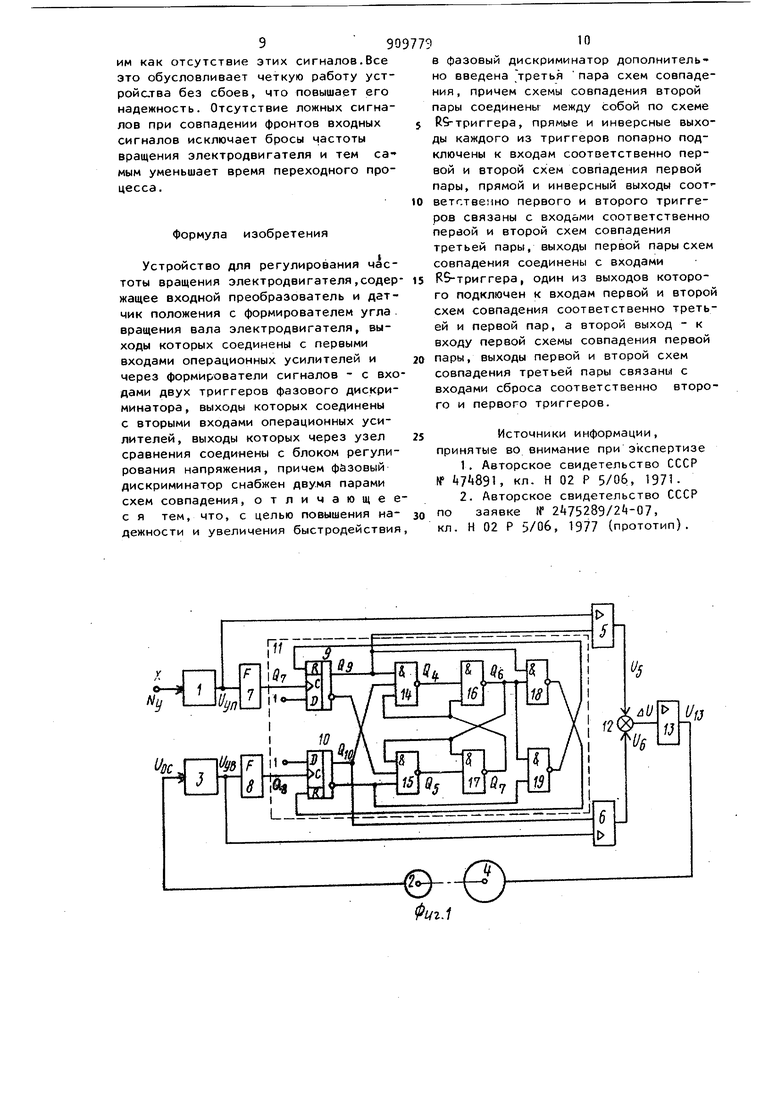

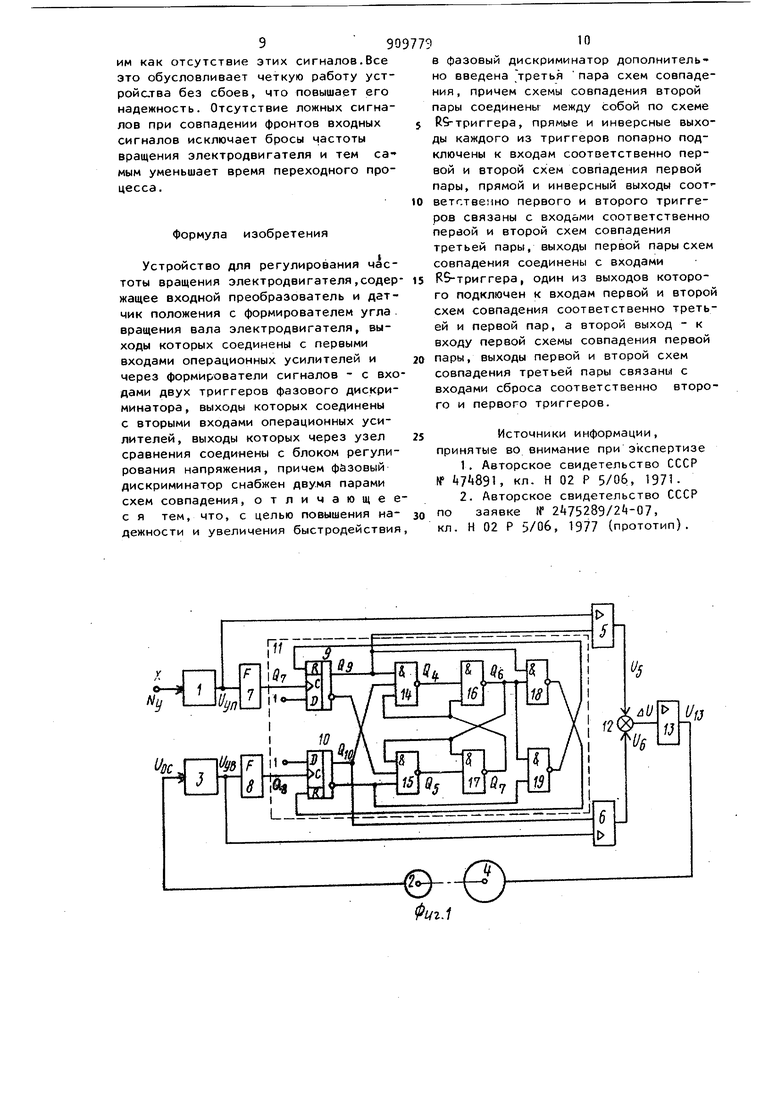

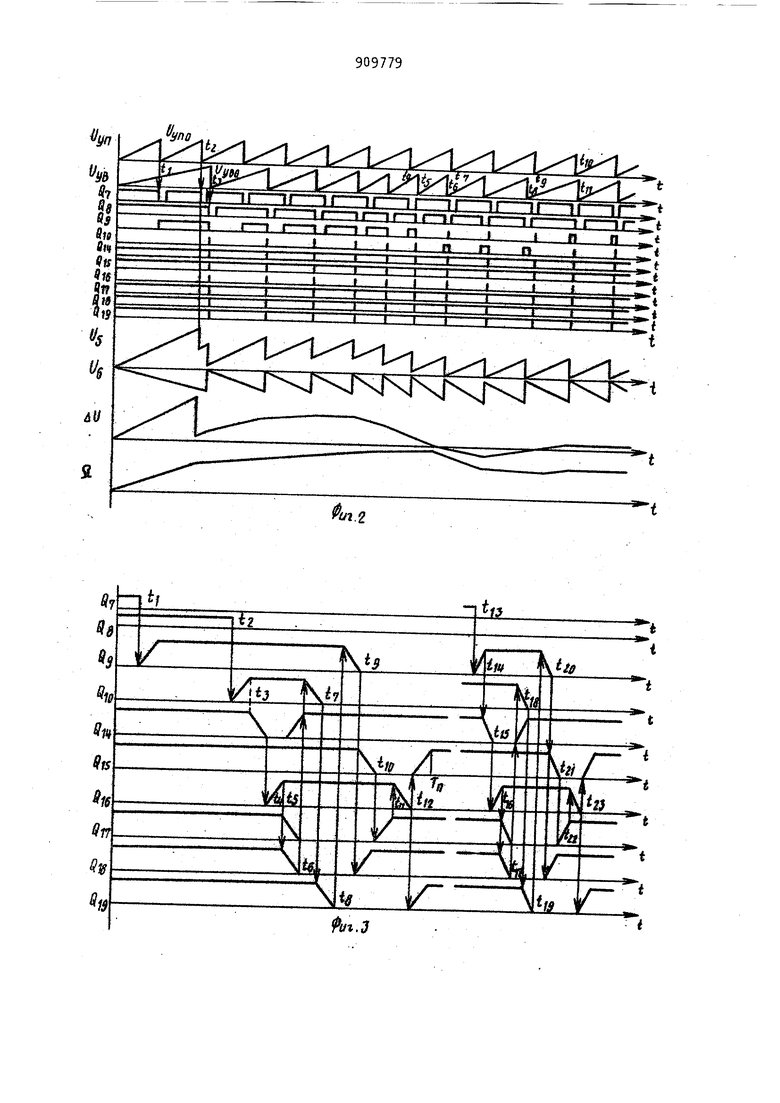

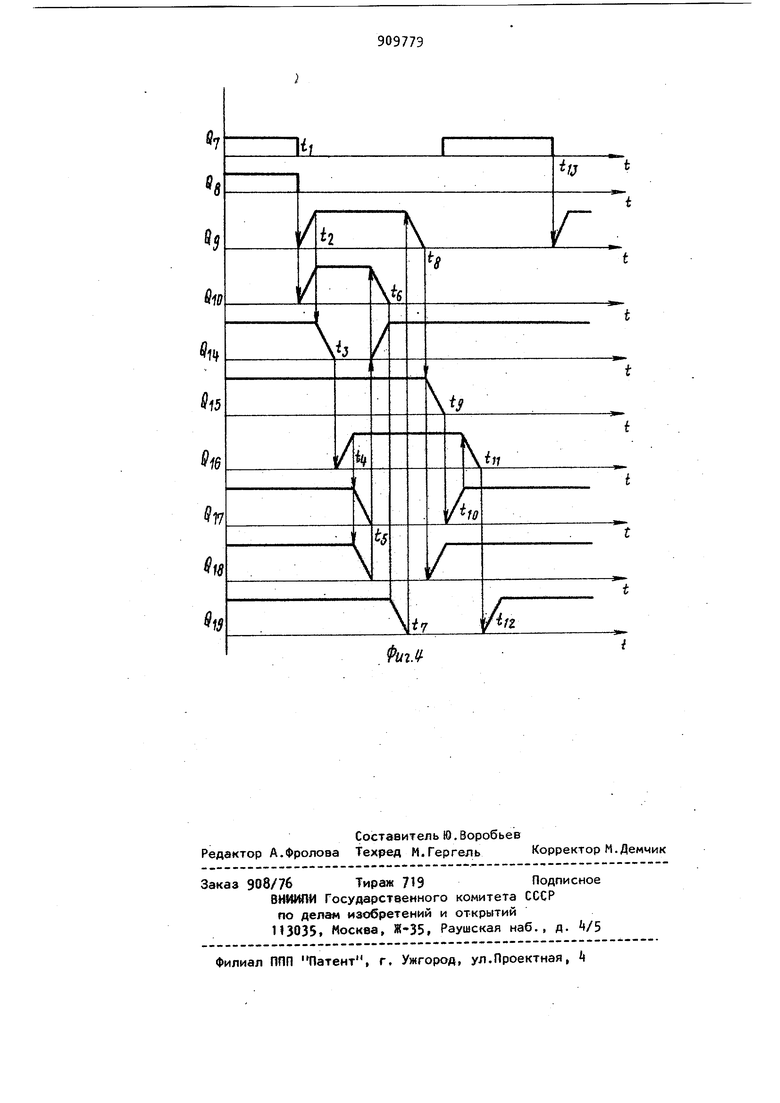

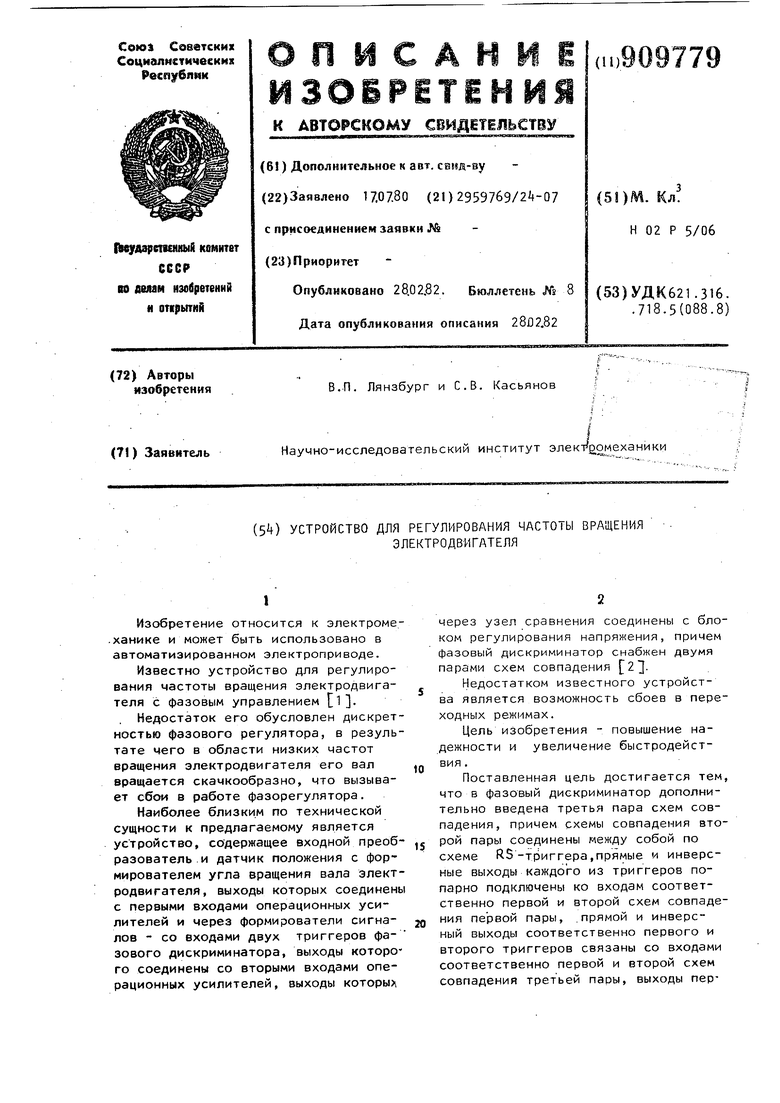

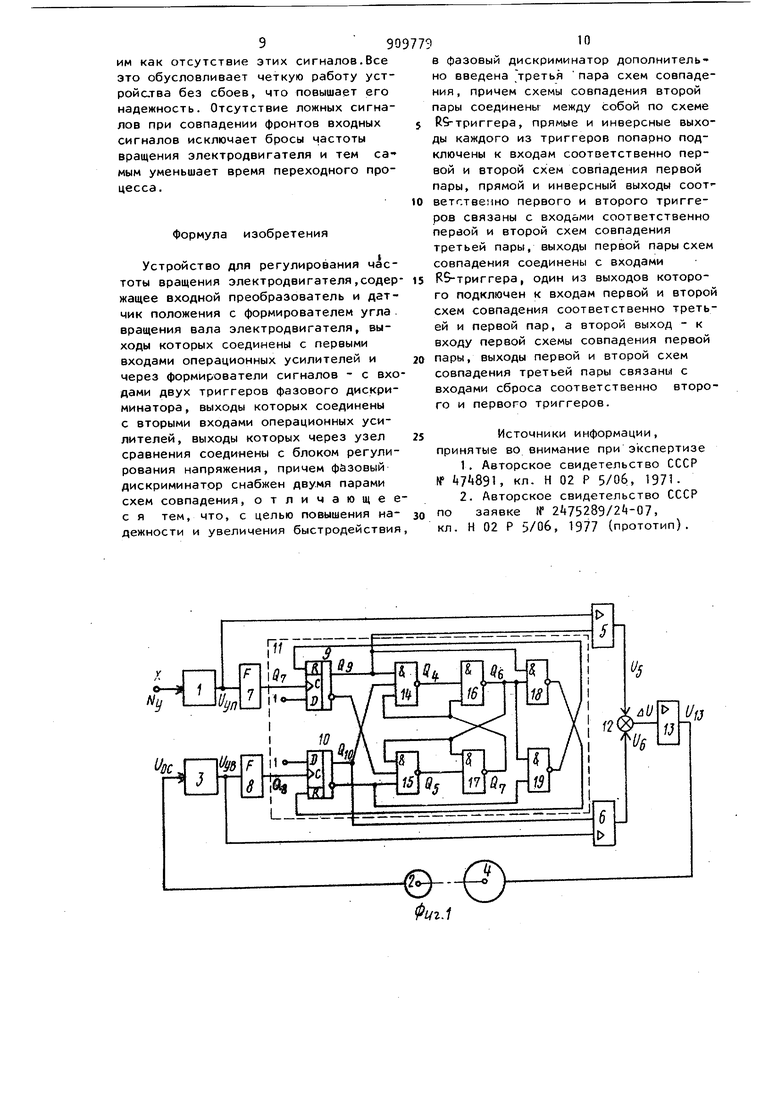

Изобретение относится к электроме .ханике и может быть использовано в автоматизированном электроприводе. Известно устройство для регулирования частоты вращения электродвигателя с фазовым управлением l. Недостаток его обусловлен дискрет ностью фазового регулятора, в резуль тате чего в области низких частот вращения электродвигателя его вал вращается скачкообразно, что вызывает сбои в работе фазорегулятора. Наиболее близким по технической сущности к предлагаемому является устройство, содержащее входной преоб разователь и датчик положения с формирователем угла вращения вала элект родвигателя, выходы которых соединен с первыми входами операционных усилителей и через формирователи сигналов - со входами двух триггеров фазового дискриминатора, выходы которо го соединены со вторыми входами операционных усилителей, выходы которых через узел сравнения соединены с блоком регулирования напряжения, причем фазовый дискриминатор снабжен двумя парами схем совпадения 23Недостатком известного устройства является возможность сбоев в переходных режимах. Цель изобретения - повышение надежности и увеличение быстродействия , Поставленная цель достигается тем, что в фазовый дискриминатор дополнительно введена третья пара схем совпадения, причем схемы совпадения второй пары соединены между собой по схеме RS-триггера,прямые и инверсные выходы каждого из триггеров попарно подключены ко входам соответственно первой и второй схем совпадения первой пары, .прямой и инверсный выходы соответственно первого и второго триггеров связаны со входами соответственно первой и второй схем совпадения третьей пары, выходы пер39вой пары схем совпадения соединены со входами RS-триггера, один из выходов которого подключен ко входам первой и второй схем совпадения соот ветственно третьей и первой пар, а .второй выход - ко входу.первой схемы совпадения первой пары, выходы перво и второй схем совпадения третьей пэры связаны со входами сброса соответственно второго и первого триггеров. На фиг. 1 изображена схема устрой ства; на фиг. 2- - диаграммы сигналов . Устройство содержит входной преоб разователь 1 и датчик положения 2 с формирователем 3 угла вращения вала электродвигателя Ц, выходы которых соединены с первыми входами операционных усилителей 5 К. 6 и через формирователи сигналов 7 и 8 - со входами двух триггеров 9 и 10 фазового дискриминатора 11, выходы которых соединены со вторыми входами операционных усилителей 5 и 6. выходы усилителей 5 и 6 через узел 12 сравнения соединены со входом блока 3 регулирования напряжения, выход ко торого соединен с электродвигателем 4. Прямые выходы триггеров 9 и 10 соединены со входами схемы 14 совпадения первой пары, а инверсные выходы - со входами схемы 15 этой, пары. Инверсные выходы схем 14 и 15 и входы этих схем соединены со входа ми схем совпадения 16 и 17 второй пары, соединенных по схеме RS-триггера. Инверсный выход схемы 16 соединен со входами схем совпадения 18 19 третьей пары, вторые входы кото и рых соедин-ны соответственно с прямым выходом триггера 9 и инверсным выходом триггера 10. Инверсные выходы схем 18 и 19 соединены соответственно со входами сброса триггеров 10 и 9. Устройство работает следующим образом. На выходах преобразователя 1 и формирователя 3 формируются пилообразные сигналы и, частоты которых соответствуют требуемой и дейс вительной частоте вращения электродвигателя 4, а величины этих сигналов определяют требуемое и фактическое угловое положение его вала. Формирователи 7 и 8 формируют имг пульсные сигналы О.и QgB виде последовательностей пауз между импульсами.- Передние фронты пауз между импульсами 0 и Q g соответствуют по BpeMeHki скачкообразным изменениям сигналов Uog соответственно (фиг. 2, показано стрелками). Длительность пауз стабилизируется схемой формирователей, в качестве которых могут быть использованы, например, одновибраторы, запускаемые перепадами напряжений U, , т.е. частота следования передних фронтов пауз пропорциональна частоте вращения электродвигателя 4. Рассмотрим работу фазового дискриминатора (ФД) 11. Предположим, что вначале частота вращения электродвигателя 4 меньше требуемого значения, определяемого частотой f импульсов сигнала 1) поэтому частота импульсов сигнала f и нарастание сигнала Uyg идет более медленно, чем сигнала и5)п(фиг. 2). До момента времени t исходное состояние сигналов Qg - О Q-tO О и ФД на работу устройства не влияет. На выходах операционных усилителей 5 и 6 формируются напряжения Uj и Ug, пропорциональные по величине напряжения Uyn,Uyg:Ug- к , и «UyQ, где к - коэффициент пропорциональности. В частном случае к 1. На выходе схемы 12 сравнения возникает сигнал ошибки AU U yj-lJyg (при к- 1), нарастающий во времени. Напряжение питания, подаваемое на электродвигатель 4, также возрастает во времени пропорционально величине сигнала ошибки Ли, вследствие чего частота вращения электродвигателя (Jt увеличивается.До момента времени t. элементы ФД имеют слбдзвощее исходное состояние: 9 О 0 « л4Г Я,7 -f в момент времени Ц задним фронтом импульса сигнала Q перебрасывается триггер 9 в состояние Q 1,liu 0. Состояние остальных элементов ФД (фиг. 1) не изменяется. Напряжение сигнала Q равно операционный усилмтель суммирует напряжение сигналов Qg и у л Поэтому напряжение и продолжает возрастать, несмотря на то, что напряжение в момент времени t скачком уменьшилось до ну ля. при этом сигнал ошибки ди и 590 частота вращения Q. увеличиваются. Так продолжается до момента времени когда напряжение уменьшается до нуля, а напряжение Ug до величины UQ, задаваемой сигналом Q. Сигнал ошибки U.U в этот момент времени сохраняет положительное значение: Л.и lJ0-Uv,Q, где UQ при t t. Поэтому частота вращения ffl. продолжа ет возрастать, но с меньшим темпом. Задний фронт импульса Q- подтверждает включение триггера 9 в состояние Qh 1. Так продолжается до момента времени to, когда фоомируется задний фронт импульса Qn, включающий триггер 9На фиг. 3 в увеличенном масштабе показаны процессы в фазовом дмскриминаторе, а именно, как в момент времени tx переключается триггер 9 в соетояиие Qu 1 а в момент времени tn начинается переключение триггеров 10. После завершения переходного процесса в момент времени t триггер 10 имеет состояние Q.fo 1. При этом на входах схемы И совпадения образуется комбинация сигналов Q, вследствие чего схема 1 переходит в состояние Q,- 0. На входах схемы 16 образуется комбинация сигналов 0., О, (L, О, поэтому она переходит в состояние Q.(, 1 яа время t.-t, что приводит к переходу противоположного плеча RS-триггера в состояние (1.7 образованию на входе схемы 18 комбинации сигналов Qc, 46 Ь которая переводит схему 13 в состояние Q.n О к моменту времени t... Сигнал Q.o О, воздействуя на вход R триггера Ю.сбрасывает его в исходное состояние а-,п О 1.п 1, которое устанайливается по окончании переходного процесса в момент времени Ц. На вход схемы 12 поступает комбинация сигнаяов Q, 1 . которой соответствует сигнал Q О,поступающий на вход сбросатриггера 9 и вызывакщий его переход в исходное состояние (Q., 0) на интервале времена t0-U. НоVoT переход приводит к ое.7а1ованию на входах схем 15 и 18 комбинаций сигналов . Q. Q 1 и Q О, Q..; 1 соотв1тствённо, по кото%м формируются к моменту времени 1,„сигналы Q,, О и Ь В свою оЙредь, сигн1л а,,Л%ызы8ает переброс RS-триггер в состояние 96 i6 сигнал 0, к моменту времени имеет значение 4 сигнала 0., в состояние О вызывает изменение состояиия сигнала на выходе схемы 15: моменту времени Т.,. На этом и заканчивается переходный процесс в фазовом дискриминаторе, который оказывается в исходном состоянии Q О, Q - t,- %9 -fP Длительность этого переходного процесса определяется частотными свойствами микросхем и находится в пределах одной или нескольких микросекунд. Частота импуль и зачастую находится в диапазоне 0-100 Гц, поэтому на фиг. 2 переходные состояния сигналов Q.), показаны на их диаграммах в виде кратковременных просадок, которые не влияют на процесс регулирования частоты вращения электродвигатепя . Так как в момент времени tg (t на фиг.З) триггер 9 переходит в исходное состояние, то нгпряжение Uf уменьшается на величину Uo, но сигнал ошибки и частота вращения продолжают возрастать (фиг. 2). Описанный процесс переключения ФД периодически повторяется до момен а времени t, когда вследствие увеличения частоты вращения элект-эодвигателя Ц соотношение между f и f изменяется: fye Ьп и на интервале 4( Располагаются два перепады напряжения в моменты времени tg и t. В момент времени t включается триггер 10 (0 I), а в момент вре начинается процесс его выклю ен ( 3). где t; соответствует Ь Фиг.2). 3 момент времени t (. 3) задним фронтом импульса Q триггер 9 переводится в состояние 9 времена этом на входе схемы 14 возникает комбинация Q 0.0 Ь которой соответствует Q, О (t, ). что приводит к перебросу RS-триггера: 7 « Ч/) 18 образуется состояние сигналов Q9 1, 0, Т, вследствие чего «а выходе схемы 18 формируется сиг«ал О (t который вызывает сброс триггера О в исходное состоя «ие О ). Переход 1 к О в момент времени t приводит к возникновению на входе схемы И комбинации Qg 0,о Ь 1о « на ее выходе сигнал Q 1 при t , причем, формирование сигнала Ч//4 происходит независимо от сос тояния сигнала (i-, , так как в мо мент времени t Q 0. Так как равенство О равносильно равенст ву 1, на выходе схемы 19 в момент времени образуется группа сигналов О.л 1 I которой соответствует состояние О (), вызывающее сброс триггера 9 в исходное состояние (Q) При этом на вхо де схемы 15 возникает сочетание 0 9 Y6 1 которому соответствует О (ta-f)- Одновременно состояние сигналов на входах схемы 18 нарушается (Q О, 0 1), что приводит к изменению состояния ее вы хода 1 (t2-f)- Сигнал вызывает сброс RS-триггера в исходно состояние 1{t22.) -f6 (2г что приводит к восстановлению исходных сигналов 1 д этом процесс выключения триггера 10 завершается. Выходное напряжение сиг нала , равное Up , напряжение суммируются операционным усилителем 6: U(j DO + Ujg, a сигнал ошибки йи изменяет свою полярность (фиг. 2), вследствие чего электродвигатель 4 переходит в режим то;оможения и его частота вращения 9. снижается. Этот режим продолжается до тех пор, пока вследствие снижения частоты вращения электродвигателя k на интервале времени tg-t не возникнут подряд два перепада напряжения UvinU ), вследствие чего вступи в работу триггер 9 как это описано выше. Сигнал ошибки вновь изменит устройство перей свою полярность, и дет в режим стабилизации частоты вра щения, величина которой определяется сигналом Ny, При увеличении (уменьшении) сигнала Н частота импульсов сигнала иорИ крутизна нарастания их напр 1жения возрастают (уменьшаются), вследствие чего увеличивается (умень шается ) частота вращения. Таким образом достигается регулирование частоты вращения электродвигателя в широком диапазоне. Рассмотрим режим одновременного скачка сигналов U и максимального значения до нуля, чему соответствует совпадение во времени t задних фронтов импульсов Q и Qg (фиг.Ч). Этими фронтами перебрасываются триггеры 9 и 10, на входе схемы 1 в момент времени t возникает комбинация сигналов Q Q Q 1 , вследствие чего изменяется состояние сигнала Q в момент времени Q о, что приводит к перебросу I S-триггера: Q., 1 (14), Q., О /чО л vt). На входе схемы 18 возникает комбинация QQ Q 1 ,приводящая к возникновению сигнала О (t,-) , что вызывает сброс триггера 10 в исходное состояние Я(о Кроме того в момент времени t на входе схемы Т группируются/ сигналы Q Q 1, 0. 0. вследствие чего Q 1 (tfe), причем изменение состояния схемы 1 не зависит от перехода Q из состояния 1 в О, так О- Так как в момент времени t, как Q -- 1, на входе схемы19 образу сочетание () Q. 1, которому отвечает равенство (л О (-м-,). Обнуление выхода схемы 19 приводит к сбросу триггера Ц в исходное состояние: QA О (t,-to),что обусловливает возникновение на входе схемы 15 комбинации сигналов Qл Q. Qy 1 и вследствие этого - переход нулевое состояние: Q О ( что вызывает переброс RS-триггера в исходное состояние Q 1, i/jg О- Кроме того, в момент времени tg схема 18 переходит в состояние 1. Переброс Rs -триггера приводит к переходу схемы 19 в состояние 1 . На этом заканчивается переходный процесс, в результате которого оба триггера 9 и 10 оказываются в исходном состоянии Q /fO - предыдущем случае, длительность переходного процесса определяется частотными свойствами микросхем, и поэтому находится в пределах одной или нескольких микросекунд. На диаграммах Q и (Ьд формируются при указанных переключениях в виде коротких пиков, не влияющих на работу устройства. Итак, совпадение во времени фронтов импульсных сигналов на входах фазового дискриминатора не приводит к появлению сигнаЛОВ на его выходе. Таким образом, переключение элементов, дискриминатора происходит последовательно во времени, что исключает появление сбоев при переключениях. Совпадение во в0емени сигналов на входах дискриминатора воспринимается им как отсутствие этих сигналов.Все это обусловливает четкую работу устройства без сбоев, что повышает его надежность. Отсутствие ложных сигналов при совпадении фронтов входных сигналов исключает бросы частоты вращения электродвигателя и тем самым уменьшает время переходного процесса. Формула изобретения Устройство для регулирования час т тоты вращения электродвигателя,содер жащее входной преобразователь и датчик положения с формирователем угла. вращения вала электродвигателя, выходы которых соединены с первыми входами операционных усилителей и через формирователи сигналов - с вхо дами двух триггеров фазового дискриминатора , выходы которых соединены с вторыми входами операционных усилителей , выходы которых через узел сравнения соединены с блоком регулирования напряжения, причем фазовый дискриминатор снабжен двумя парами схем совпадения, отличающее с я тем, что, с целью повышения надежности и увеличения быстродействия 9 в фазовый дискриминатор дополнительно введена третья пара схем совпадения, причем схемы совпадения второй пары соединены между собой по схеме к5-триггера, прямые и инверсные выходы каждого из триггеров попарно подключены к входам соответственно первой и второй схем совпадения первой пары, прямой и инверсный выходы соот ветстаемно первого и второго триггеров связаны с входами соответственно первой и второй схем совпадения третьей пары, выходы первой пары схем совпадения соединены с входами . ПСПЫ , О PS-триггера, один из выходов которого подключен к входам первой и второй схем совпадения соответственно третьей и первой пар, а второй выход - к входу первой схемы совпадения первой пары, выходы первой и второй схем совпадения третьей пары связаны с входами сброса соответственно второго и первого триггеров. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № , кл. Н 02 Р 5/06, 1971. 2.Авторское свидетельство СССР по заявке № 2 75289/2«-07, кл. Н 02 Р 5/06, 1977 (прототип).

i

1

n %

%

Qn

:4

IN

% /Г

ff

e

уГ

Щ 15

Авторы

Даты

1982-02-28—Публикация

1980-07-17—Подача