(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЕДУЩИМ ШАГОВЫМ ДВИГАТЕЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Цифровой частотный дискриминатор | 1975 |

|

SU542328A1 |

| Устройство для сопряжения микроЭВМ с кассетным магнитофоном | 1982 |

|

SU1345185A1 |

| Устройство для сопряжения микроЭВМ с кассетным магнитофоном | 1983 |

|

SU1396136A1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| Цифровой частотно-фазовый дискриминатор | 1983 |

|

SU1117824A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| Устройство для определения местоположения источника акустической эмиссии | 1987 |

|

SU1499224A1 |

| Цифровое фазосдвигающее устройство | 1988 |

|

SU1622835A1 |

| СТАБИЛИЗИРОВАННЫЙ ЭЛЕКТРОПРИВОД | 2011 |

|

RU2462809C1 |

Изобретение относится к управлению электроприводами и может быть использовано в устройствах автойатики и телемеханики с шаговыми двигателями, в частности в устройствах . синхронного воспроизведения цифровой магнитной записи с пилот-сигналом и ведущим ищ.

Известно устройство для синхронного воспроизведения записи на магнитном носителе, содер жацее блок сравнения, дискриминатор, интегратсф и выходной блок l .

Недостатком известного устройст ва является невысокая точность.

Наиболее близким к изобретению по технической сущности является устройство для управления ведущим шаговым двигателем, содержащее первый и второй реверсивные счетчики, формирователь импульсов и частотный дискриминатор 21 .

Недостаток .известного устройства невысокая точность.

Целью изобретения является повышение-точности устройства.

Указанная цель достигается тем, что в устройство введены первый, второй и третий таймеры, фазовый дискриминатор, первый и второй

RS-триггеры, деши4фатор, регцстр сдвига, первый, второй и третий Логические блоки, причем первые выходы дешифратора, частотного дискриминатора , первый и второй выходы фазового дисприминатора через первый логический блок подключены к суммирующему входу первого реверсивного счетчика, второй выход дешифратора,

10 выход второго RS-триггера, первые выходы первого и второго таймеров, второй выход частотного дискриминатора и первый вход устройства через второй логический блок подключены к

15 вычитающему входу первого реверсивного счетчика, а первый, второй и третий выходы второго таймера, обнуляющий вход устройства и выход второго RS-триггёра через третий ло20гический блок подключены к обнуляющему входу первого реверсивного счетчика, разрядные выходы которого соединены с соответствукяцими входами дешифратора, с первшл R-входом

25 второго RS-триггера и через регистр сдвига - с информационными входами второго реверсивного счетчика, первые суммирующий и вычитающий входы которого подключены к старшему раз30ряду регистра сдвига, вторые суммирующий и вычитающий входы - к- выходу второго реверсивного счетчика третьи суммирующий и вычитающий вхды - к первому входу устройства, чтвертые суммирующий и вычитающий входы, а также синхронизирующий вход - к первому выходу третьего тмера , а обнуляющий вход - к обнуля тему входу устройства, соединенному с первым входом первого таймера с первым и вторым входами второго таймера и с первым управляющим входом регистра рдвига, .второй управляющий вход которого подключен .к четвертому выходу второго таймера, пятый, шестой и седьмой выходы которого соединены соответственно с первым входом фа,зового дискриминатора, с первым и вторым входами частотного дискриминатора, а первый инверсный выход - с первым входом третьего таймера, второй выход которого подключен к третьему входу частотного дискриминатора, а второй вход - к четвертому входу частотного дискриминатора, к второму входу фазового дискриминатора и к первому входу устройства, первый, второй, третий, четвертый, пятый, шестой и седьмой входы формирователя импульсов подключены соответственно к выходу второго реверсивного счетчика, к выходу первого RS-триггера, к выходу вто.рогб -КЗ-триггера, к первому входу первого таймера, к старшему разряду Е5егистра сдвига, к первому входу устройства и .к второму выходу первого таймера, третий выход которого соединен с третьим входом фазового дискриминатора, четвертый вход которого соединен с первым рвыходом второго таймера и с вторым R-входом второго RS- триггера, а первый и второй выходы - соответственно с S-входом и R-входом первого RS-триггера, третий выход дешифратора прдключен к S-входу второго RS-триггера, а второй вход первого таймера и третий вход второго таймера - соответственно к певому и второму входам устройства.

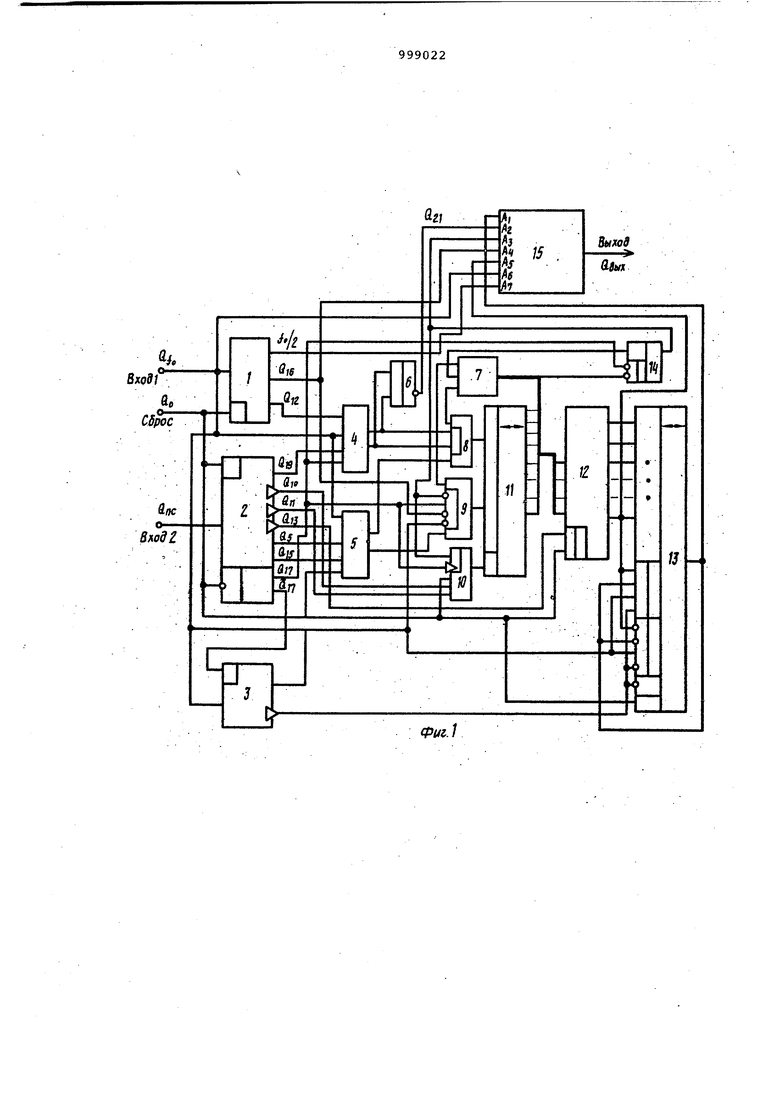

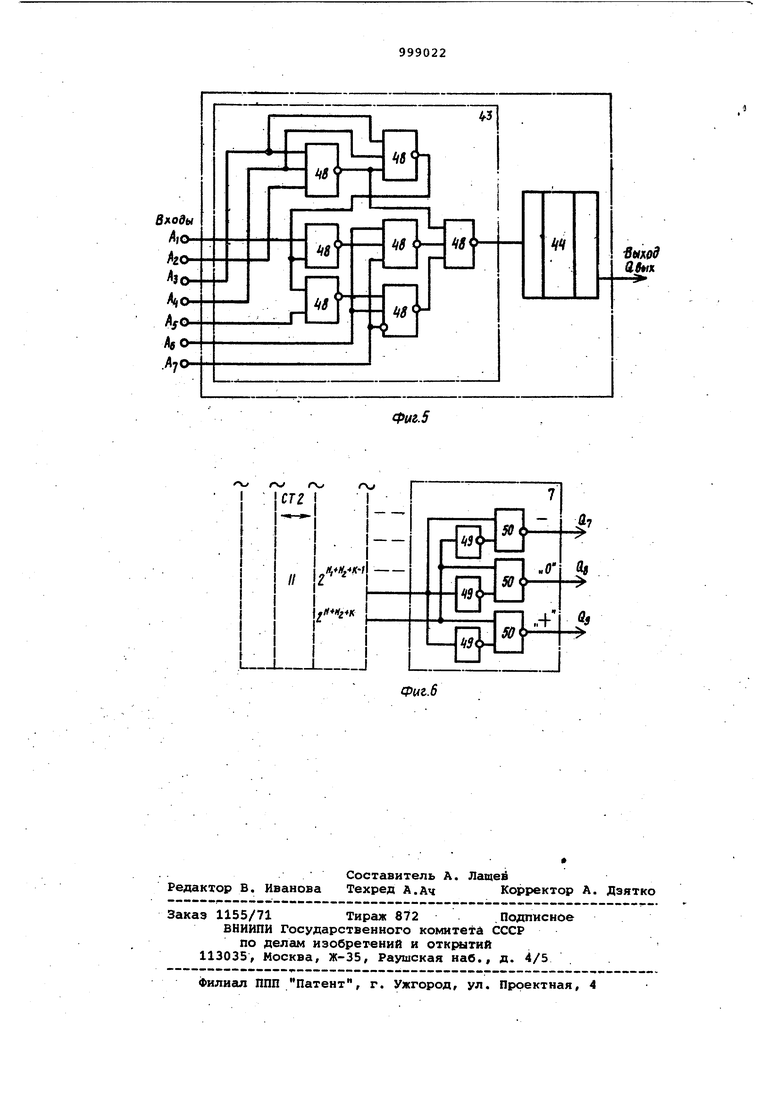

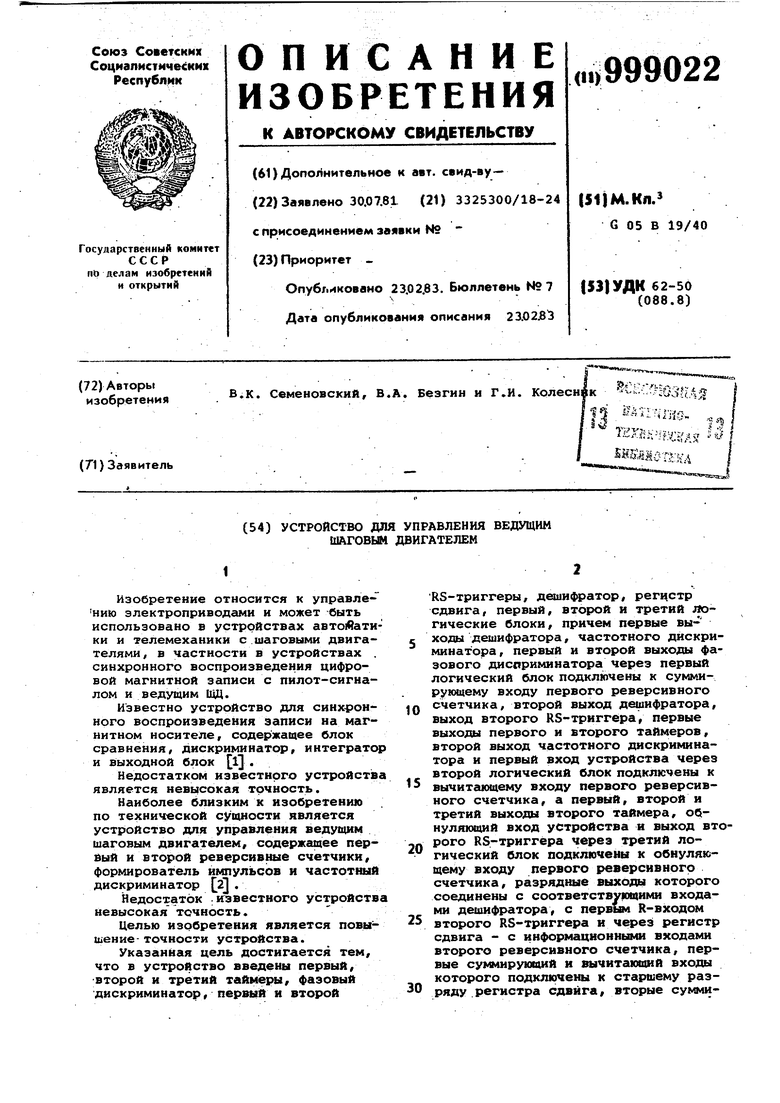

На фиг. 1 приведена блок-схема :устройства для управления ведущим шаговым двигателем; на фиг. 2 временные, диаграмли сигналов на вхдах устройства и выходах основных его элементов; на фиг. 3 - примерная реализация таймеров и логических блоков; на фиг. 4. - примерная реализация дискриминаторов;, на фиг. 5 - примерная реализация формрователя импульсов; на фиг. 6 примерная реализация дешифратора. .Устройство для управления содержит первый таймер 1, второй таймер 2, третий таймер-3, фазовый.

дискриминатор 4, частотный дискриминатор 5, первый RS-триггер б, дешифратбр 7, первый логический блок 8, второй логический блок 9, третий логический блок 10, первый реверсивный счетчик 11, регистр 12 сдвига, второй реверсивный счетчик 13, второйRS-триггер 14, формирователь 15 импульсов, счетчик 16 импульсов, элемент И 17, счетчик 18 импульсов, элементы И 19-21, формирователи 22-24 импульсов,, счетчик 25 импульсов, элемент И 26, формирователь 27 импульсов, элемент ИЛИ 28, элементы И 29-31, формирователь 32 импульсов, элемент ИЛИ 33, элемент И 34, регистр 35 сдвига, формировател.ь 36 импульсов, элементы И 37-39 реверсивный счетчик 40 импульсов, RS-триггер 41, элемент ИЛИ 42, переключатель. 43 частот и счетчик 44 импульсов, элементы ИЛИ 45, И 46, триппер 47 и элементы И 48, ИЛИ 49 и И 50.

Второй вход устройства является счетным входом второго таймера 2, подключаемым к внешнему источнику воспроизводимого пилот-сигнала 9пс

Обнуляющий вход Сброс подключается к внешнему источнику сигнала QQ установки в Q.

Первый вход является входом сигнала GH опорной частоты fQ,

Выходом устройства является выход формирователя 15 импульсов

(QebiJКоэффициент счета счетчика 18 втрого таймера 2

+ 1 Тз.ыо. Р„

счг

где F рабочая частота шагового

ы двигателя (ЕЦЦ) выбирается близкой к его частоте приемистости,

т время практически полноЗ.ШП го затухания колебаний ротора ЩЦ (в пределах шага) , возникающих при максимально возможном изменении ( д FIU ) частоты Рщ в. процессе автоматического регулирования/

N, число разрядов счетчика 18 таймера 2 без учета старшего (N2 1-го) раз ряда, реализованного в виде единичного триггера, имекице го отдельный вход (S) установки в 1 Коэффициент, счета счетчика 16 первого таймера 1

1„

.1

- счетчика 25 третьего таймера 3

К

счз

где N - число разрядов счетчика fo - опорная частота.

Величина f выбирается в зависимости от допустимой ошибки дискретности стабилизации частоты воспроизводимого пилот-сигнала.

Коэффициент счета второго ревер.сивного счетчика 13

Кр.сч13 первого реверсивного счетчика 11

к 9N.+ N, + 1

- Схемы фазового и частотного дис(Криминаторов 4 и 5 строятся так, что при. подаче на один из их входов частоты f5,, на другой - импульса воспроизводимого пилот-сигнала G(g , на третий - соответствующего ему импульса эталонного сигнала Qg и на четвертый - разрешающего потенциала QYI например Qу 1/ и при задержке одного из сигналов Quo 6)5 например Q ПС , относительно другого Qg на величину , сигналы на выходах + (Q Ч) и - I (Q -) дискриминатора должны быть: при . Q + - пачка импуль . . сов частотой (,и длительностью пачки

- } Q - . 1/ при Д t ц| о - наоборот. Формирователь 15 импульсов включает в себя переключатель частот 43 с .управляющими входами А1...А5, частотными входами А6, А7 и выходным сигналом Р/ а также выходной счетчик 44 с коэффициентом счета

вых тота fA6 fo 3 vioft. А7 . |3ависимость Частоты fp сигнала Р от ;управлякмцих сигналов А1.. .А4 опред еляется таблицей истинности г

10- О 11 О О 1 1001

- - - - 0011

00 0011111111

- - -. - о О 00 11 11

1 10 011 О О 0101

О 4г f- «

if

i

fo Т о

Р -г 0 2 - г

(Прочерки обозначают произвольные значения сигналов: О или 1). Дешифратор 7 предназначен для защиты пер вого реверсивного счетчика 11 от переполнения при счете по суммирующему или вычитающему входам, а также для выдачи сигнала ( Qg), соответствующего знаку числа п, эапиСс1лного в счетчике 11 (О f 1 при (П О и Qg О при п i 0) .

Работа устройства включает В себя коррекцию фазы ср и коррекцию частоты Fpc воспроизводимого сигнала Qnc

В момент пуска, Когда QQ 1или после -го шага текущего цикла устройство находится в состоянии, соответствующем 2 ™2 + 1-му шагу, когда сигнал Qi7 на выходе старшего

0 разряда таймера 2-0,7 - Этот сигнал:

а) разрешает фазовому дискрими- натору 4 заполнять интервал Д между ближайшими (передними) фронтами 5 очередных сигналов: + 1-ГО импульса Q 19 воспроизводимого сигнала Qno и эталонного Qg Q (с выхода старшего разряда первого таймвpa 1) импульсами с выхода + или

- (в зависимости от sign д) /

0 фаэрврго дискриминатора, которые:

-подаются соответственно на вход К или S первого RS-триггера; .

-поступают через первыйяогичес5 кий блок 8 на счетный вход первого

реверсивного счетчика 11, в результате чего в счетчике 11 запоминдеуСЯ ЧЦСЛО U п tf ,

6J запирает второй логический блок 9,: запрещая счет по вхоД/ -rl

0 счетчиком 11 импульсов частоты д.. Частотный дискриминатор в течение +1-ГО шага заперт сигналом вследствие чего сигналы ни обоих, выходах +. и - частотного диск5риминатора 5 будут (у + Q -

i;

в) отпирает элемент И на R-входе второго RS-триггера 14, paapeiiian воздействие на этот вход сигнала

0 Q2 О, где Q2 - сигнал с выхода одного из млС1ДШИХ разрядов NQ-ГО pe-j: версивного счетчика 11, если й. , где ДПзн fo-Тзн гдеГГ дширина зоны нечувствительности уст5 ройства. Если д п. i.arij , то в пределах + 1-го .шага 2 и на R-входе триггера 14 сохраняется уровень 1, а на выходе этого триггера - сигнал Qy 0, который:

0 - запирает второй логический блок 9, подтверждая запрет обратного отсчета в счетчике 11;

-отключает входы коррекции фазы A3, А4 формирователя импульсов 15, запрещая тем самым всякое воз5действие .на фазу выходного сигнала 8ых устройства;

-сохраняет разрешение на сброс. счетчика 11 сигналом, поступаюпшм на R-вход счетчика 11 с выхода тре0тьего логического блока 10 в момент окончания сигнала Q,y 1 (т.е. в конце N2 + 1-го шага, когда - 0).

Когда в конце 2 2 + 1-го шага 5 происходит сброс счетчика 11 в исходное состояние, на третьем выходе дешифратора 7 появляется сигнал Qg О, подтверждающий состояние первого RS-триггера Qn 0. Поскольку после 22 + 1-го шага прошедшего цикла Q| О вплоть до 22 + 1-г шага очередного цикла, а Q4 QS . О вплоть до. -го шага этого цикла, то счетчик 11 будет сохранят исходное состояние из-за отсутствия счетных импульсов на входах, по кра ней мере до начала 2/ -го шага, 1шрина зоны нечувствительности , определяемая номером разряда тай Мера 2, выбирается так, чтобы зна- чение Т-ги 2 0- превышало флюк туации фазы воспроизводимого сигнала Qnc f обусловленные неточностью отработки шага ЩЦ. Поскольку замер л tp производится при отсутствии колебаний ротора ЩЦ, то практически достаточно иметь Т2н(0 ,01i..O ,02) Т,

Если же Л n,, д Пд,,, то спустя время после начала 2 i + 1-го шага сигнал Q2 принимает значение Q4 V 1- Поскольку на протяжении + 1-го шага I, то на R-входе триггера 14 появляется уровень О, тогда как при д. п О Qg 1, вследствие чего триггер 14 переходит в состояние Qi4 Сигна

Q4 1

-Отпирает входы A3, А4 коррекции фазы формирователя импульсов 15

-снимает запрет на подачу счетных импульсов на вход -1 реверсивного счетчика 11;

-запрещает сброс реверсивного счетчика 11 в конце + l-ro шага сигналом Qj-j 1.°

Поскольку длительность импульсов сравниваемых сигналов Q i и G( i ест - -(ulir то д(|,4Тц,|2и число ДПц, будет полностью записано в реверсивный счетчик 11 в пределах дли тельности + 1-го шага.; Сразу после окончания 2 + 1-го шага на третьем входе логического блока 9 появляется разрешающий сигнал Qc;f О, но логический блок 9 остается закрытым почти до конца шага сигналом Qi6 О, тогда как дискриминаторы 4 и 5 остаются запертыми соответственно сигналами Q|7 О и Q|5 О , Поэтому реверсивный счетчик 11 сохраняет записанное в нем число U п ср вплрть до момента начала импульса Q|6 1 с длительностью

2 /fo (то есть в течение времени Т и - ЛТц,, от начал а шага). Величина ATjj,(p выбирается достаточно малой (практически дТщс/,4(0,010,02)Тц, ), Чтобы коррекция фазы не приводила к существенному увеличению амплитуды и времени затухания колебаний ротора ЩЦ.

В течение времени 4 Тццр , когда Q, 1, на вход -1 реверсивного счетчика 11 подаются импульсы с частотой (, (числом П(. -йТу(я-5 2 ), вследствие чего при каждом шаге число (записанное по +1 в течение + 1-го шага предыдущего цикла в реверсивном счётчике 11 уменьшается на величину дП(, а за 2 шагов цикла - на величину 2 2,,дп. Одновременно дозирующий сигнал Q|(, и сигнал Qg подаются на входы A3 и А4 формирователя 15 импульсов, что при 1 приводит к увеличению или уменьшению количества импульсов на входе счетчика 44 блока 15 в течение шага на величину ЬПср . Следствием этого является изменение, длительности очередного периода Тщ выходного сигнала Q gbu на величину , Д /f , про ивоположную по знаку измеренному сдвигу Atq,. Б итоге,, фазовый сдвиг между импульсами воспроизводимого сигнала Q ПС и эталонного Q|2 уменьшается, одновременно с уменьшением числа запнсднного в реверсивном счетчике 11..

Как только число ДПи, записанное в первом реверсивном счетчике 11, уменьшается до величины Прсц .1 ( + ) сигнал Qg на третьем выходе.дешифратора 7 станет равен Qg О, что приводит к возврату триггера 14 в исходное состояние 9(4 0.2. Коррекция частоты Коррекция частоты производится независимо от процесса коррекции фазы, в каждом из 2 + 1-го, шагов цикла, по результатам замера инт рвала времени uti между передними фронтами сигнала Qg- 1 на выходе второго таймера 2 и совпадающего с импульсом воспроизводимого входного сигнала CJnc с длительносТЬЮЬИУ ТЩ/ И соответствующего ему эталонного импульс.а Gd 1, формируемого третьим таймером 3. Для установки в О таймера 3, на R-вход подается синхронизирующий сигнал Q|7 , благодаря чему очередные циклы в элементе И 17 и в формирователе импульсов 23 начинаются в один и тот же момент. Это позволяет измерять величину независимо от разового сдвига сигнала Q,(.относительно onopt-iHx сигналов Qjjc выхода таймера 1. Поскольку величина по существу является суммой интервалов времени йС f ц, между, передними фронтами сигналов Q ПС ( частотой Р(с Рц) и эталонных импульсов с N -горазряда фopIv иpoвaтeля 23 для каждого из шагов, тй средняя величина ut за.цикл есть ut i/2 . Импульсы заполнения интервала il i (с частотой fo,- числом лn-f SltyfQ) При каждом шаге, в зависимости от sign ut t добавляются к числу импуль сов частоты о/2 заполнения шага на входе счетчика 44 в формировател 15 импульсов или вычита1 тся из это го Числа., что приводит к соответствующему изменению частоты F выходного сигнала Qgyx. При этом скорос вращения ведущего ЩЦ изменяется та что воспроизводимая частота стре мится сравняться с эталонной часто |тоЩ. . с этой целью в течение го шага каждого цикла с помощью тайме ра 2 ф9Рмируется сигнал Qi5 1, разрешающий схеме частотного дискриминатора 5 заполнение импульсами с частотой fо интервала д f между передними фронтами сигнала Q, фор мируемого таймером 2 и совпадающего с 2 1 -м импульсом воспроизводи мого сигнала Qn и соответствующего ему эталонного сигнала Q4, формируемого третьим таймером 3. Интервал заполняется импульсами с ча тотой frt , числом Hi nf где: и nf I/. Указанные импульсы заполнения снимаются с одного из выходов частотного детектора и подаются соответственно на вход блока (или на вход блока 9), на счетный вход счетчика 11. Установка в О реверсивного счетчика 11 производится в момент подачи сигнала Q,- 1 коротким импульсом Q,, О с третьего выхода таймера 2. Если чи ло йп, записываемое в счетчик 11 случайно превысит предполагаемую максимальную величину А nf max во избежание переполнения суетчика 11, блок 8 (или 9), пропускающий в данный момент счетные импульсы на вход счетчика 11, запирается сигналом с выхода дешифратора 7, что предотвращает случайные сбои устройства. При записи .числа йп в р еверсивный счетчик 11 счетные импульсы подаются на вход младшего разряда, тогда как выходы старших разрядов, начиная с N4 +1-го подключены к входам (N| +1)-разрядного регистра сдвига 12. При этом, указанные входы отключены (то есть информационные сигналы, поданные на эти входда не записываются в разряды регистра 12) потенциалом Q tg О, подаваемым с четвертого выхода второго таймера 2 на V-вход разрешения параллельной записи информации регист , ра 12. В момент окончания го шага (то есть в момент прихода заднего фронта сигнала Qij-, принимающего значение Q)5 0) второй таймер 2 формирует разрешающий сигнал .Qig 1 в виде короткого импульса, :в течение которого происходит перезапись информации с выходов. N(41 старших разрядов счетчика 11 в регистр 12 числа, равного дп U ni . Это число, фактически с погрешностью-не более +1, равно среднему за цикл числу импульсов заполнения и-нтервала между (передними) фронтами воспроизводимого сигнала Qnc сигнала 913 эталонной части Fg с инверсного выхода }i -го разряда счетчика третьего таймера.- . В момент окончания короткого импульса QIQ 1- (то есть при Л|3 . О на V-входе регистра 12 одноё 5ёменно с формиррванием заднего фров- та короткого импульса Q щ начинается формирование короткого импульса . 6, поступающего на четвертый вход третьего логического блока 10,; на одном выходе которого присутствуе сигнал Qj 1,а на других входах исходные уровни сигналов Оц и .Q с выходов второго таймера 2. При этом импульсный сигнал Qfg О через третий логический блок 10 подается на обнуляющий вход реверсивного с.четчика 11, который возвргодается. в исходное состояние. Поэтому к мо-г менту начала + 1-го шага устройство возвращается в исходное состояние, описанное ранее. Причем в регистре 12 будет записано среднее за 2 1 шагов число ( ni) импульсов заполнения разности периодов частоты Ffjc воспроизводимого входного сигнала 9,с и сигнала (,з эталонной частоты. В момент начала каждого из импульсов Q|-j (то есть, практически, . в начале каждого шага) на импульсном выходе Q третьего таймера 3 появляется короткий импульс Q О, который, поступая на синхронизирующий вход второго реверсивного счетчика 13, разрешает параллельную перезапись числа хранящегося в регистре 12 на протяжении 22- шагов текущего цикла, в счетчик 13. Одновременно, короткий импульс Q4 О, поступая на четвертые входы счетчика , предотвращает списывание числа д., записанного в счетчике 13, импульсами частоты f, по- . даваемыми на третьи входы счетчи - . ка 13. ЕСЛИ Atfu 0, то естьТп(-Тз и, следовательно, запись числа Д.п1щ в первый реверсивный счетчик 11 производилась по суммирующему входу, то на выходе старшего разряда счётчика 11 сохранится уровень-признак прямого счета (суммирования), Этот же уровень О будет записан в старшем разряде регистра 12. и соответственно счетчика 13, на старшем .разряде которого будет Q20 О В этом случае после окончания коротко го импульса Q О, то есть при fj; 1 на четвертых входах второго ревер сивного счетчика 13, сигнал опорной частоты fg, подаваемый на третьи входы счетчика 13, проходит на вход счетчика 13, Следовательно, начиная с момента окончания короткого импульса Q сигналы U5 2о совпадают по уровню Q G)2o 0) 3 время списывания в счетчике 13 числа равное Л1 ,|nim/ (с точностью до указанной выше ошибки дискретнос ти) . В момент перехода положительно го (в данном случае) числа, записан Ного в счетчике 13, через О уровень сигнала на выходе старшего раз ряда счетчика 13, то есть уровень Q20 изменится (с О на 1), что приведет к запиранию вычитающего входа счетчика 13 и счет импульсов на данном шаге прекратится. Вместе с тем, ак как в течение времени , было Q О, а QI-I 0 то, согласно таблице истинности формирователя 15 импульсов частота fp сигнала на входе счетчика 44 блока 15 при номинальной величине fp f(j/2, в начале каждого шага данного цикла (то есть, при 0) Б течение времени Д if будет равна fg. Это значит, что колиуество импульсов, подаваемых на вход выходного счетчика 44 формирователя 15, возрастает и период Тщ частоты Рц) на выходе этого счетчика уменьшается на величину . В результате, увеличится скорость вра щения ЩД, то есть скорость протяжки и соответственно частота воспроизводимого пилот-сигнала Р,спериод которой ТПР уменьшится на величину л1 ц,, то есть сравняется с периодом Тэ эталонной частоты Fg. Если , то есть Т„ : Т ) и/ следовательно, запись числа в счетчик 11 производилась по вычитающему входу, то на выходе старшего разряда этого счетчика сохраняется уровень-признак обратного счета, например 1. Этот же уровень- (Q 1) будет записан в старшем разряде регистра 12 и соответственно счетчика 13, на выходе старшего разряда которого , В этом случае после окончания ко роткого импульса Q 0, то есть при Q 1 и сигнале Q д 1 на чет вертых входах счетчика 13, сигнал опорной частоты fQ, подаваемый на третьи входы счетчика 13,, проходит на суммирующий вход счетчика 13. Следовательно, начиная с момента окончанил короткого импульса Q сигналы G и Q2ocoвпaдaют по уровню (Q 1) на время списывания в счетчике 13 числа равное /utiljj fo /uifuj (с точностью до указанной выше ошибки дискретности) В момент перехода отрицательного числа, записанного в счетчике 13, через О уровень сигнала на выходе старшего разряда счетчика 13 - ®2о изменится -(в данном случае - с 1 на 0), что приведет к запиранию суммирующего входа счетчика 13. Поскольку вычитающий вход остается запертым сигналом Q i, 1 (в течение шагов цикла), то счет импульсов на данном шаге прекращается. Вместе с тем, поскольку в течение Времени д1{ц,(3 G20 1, а 0 0 то, согласно таблице истинности для формирования выходных импульсов формирователя 15 частота fp сигнала на входе счетчика 44 формирователя 15 в начале каждого шага в течение вре мени&и щ будет равна: f р О. Это значит, что количество импульсов, подаваемых на вход указанного счётчика 44, уменьшится и период Тщ частоты Рщ на выходе счетчика 44 (то есть частоты выходного сигнала QgboO возрастет на- величину tiij . В результате уменьшится скорость вращения ротора 1цД, то есть скорость протяжки и, соответственно, частота воспроизводимохо пилот-сигнала Pfjc период которой уменьшится на величину Л1.11ц и сравняется с периодом эталонной частоты РЭ. Таким образом, в предлагаемом устройстве j отклонений фазы А ср и частоты Д сигнала датчика (в данном случае пилот-сигнала Qnc воспроизводимого с магнитного носителя) рт эталонных и соответствующая коррекция регулирования скорости вращения ведущего шагового двигателя производится н непрерывно, а циклически, в конце каждого из циклов, длительность которых Т ц постоянна и заведомо больше времени практически полного затухания колебаний ротора ЩЦ возникающих при внесении коррекции в начале цикла, -измеренные значения Аср и усредненной за время Тц (2 + ) Тц величины U Ff|2 фиксируются каждое в своем запоминающем устройстве, причем коррекция частоты пилот-сигнала в следующем цикле производится путем изменения длительности каждого из этого цикла Тц; йа величину, соответствующую измеренному значению ь f У , а коррекция фазы (если д превышает некоторое допустимое значение) путем изменения Тц, на постоянную малую величину f вводимую до тех пор, пока возникающий за счет нее фазовый сдвиг не скомпенсирует измеренную величину. При этом величинай7ш( выбирается достаточно малой, порядка 1% от Ту, чтобы введе ние ее (то есть коррекция фазы) не приводило к существенному увеличению амплитуды и времени затухания колебаний ротора ЩЦ и к связанной этим необходимости увеличения длительности цикла Тц. Зона нечувстви тельности должна превышать флю туации фазового сдвига, возникающи из-заприсущей ЩД неточности отработки шага (в общем случае - до 10-20%), которая при отсутствии вн них возмущений, -в частности, изменений рабочей частотьг, составляет 0,006 Тц,. Применение предлагаемого устрой ва позволяет повысить точность и расширить область устойчивой ста.билизации с 1 до 10-15%, что заведомо перекрывает область возможных отклонений дискриминируемой частоты от номинала. Это Обуславливает получение определенного технико-экономического эффекта от его внедрения в системы стабилизации скорости протяжки магнитного носителя. Формула изобретения Устройство для управления ведущим шаговым двигателем, содержащее первый и второй реверсивные счетчи ки, формирователь импульсов и частотный дискриминатор, отлича щ е е с я тем, что, с целью повышения точности устройства, в него .введены первый, второй и третий таймеры, фазовый дискриминатор, пе вый и второй RS-триггеры, дешифратор, регистр сдвига,, первый, второй и третий логические блоки, при чем первые выходы дешифратора, частотного дискриминатора, первый и второй выходы фазового дискриминатора через первый логический бло подключены к суммирующему входу первого реверсивного счетчика, вто рой выход дешифратора, выход второго RS-триггера, первые выходы первого и второго таймеров, второй выход частотного дискриминатора и -первый вход устройства через вто рой логический блок подключены к вычитающему входу первого реверсив ного счетчика, а первый, второй и третий выходы второго таймера, обн ляйщий вход устройства и .выход вто рого RS-триггера через третий логический блок подключены к обнуляю щему входу первого реверсивного счетчика/ разрядные выходы которог соединены с соответствующими входа ,ми дешифратора, с первым R-входом второго RS-триггера и через регистр сдвига - с информационными входами второго реверсивного счетчика, первые суммирующий и вычитающий входы которого подключены к старшему разряду регистра сдвига, вторые суммирующий и вычитающий входы - к выходу второго реверсивного счетчика, третьи суммирующий и вычитающий входы - к первому входу устройства, четвертые суммирующий и вычитающий входы, а также синхронизирующий вход - к первому выходу тре-тьего таймера, а обнуляющий вход к обнуляющему входу устройства, соединенному с первым входом первого таймера, с первым и вторым входами второго таймера и с перВЕли) управляющим входом регистра сдвига, второй управляющий вход которого . подключен к четвертому выходу второго таймера, пятый, шестой и седьмой выходы которого соединены соответственно с первым входом фазового дискриминатора, с первым и вторым входами частотного дискриминатора , а первый инверсный выход - с первым входом третьего таймера, второй выход которого подключен к треты ему входучастотного дискриминатора , а второй вход - к четвертому входу частотного дискриминатора, к второму входу фазового дискриминатора и к первому входу устройства, первый, второй, третий, четвертый, пятый, шестой и седьмой входы формирователя импульсов подключены соответственно к выходу второго реверсивного счетЧИка, к выходу первого RS-триггера, к выходу второго RS-TpHiгера, к первому входу первого тайме ра, к старшему разряду регистра сдвига, к первому входу устройства и к второму выходу первого таймера, третий выход которого соединен с третьим входом фазового- дискриминатора, четвертый вход которого соединен с первым выходом второго таймера и с вторым R-входом второго RS-триггера, а первый и второй выходы. - соответственно с З-входом и R-входом первого RS-триггера,третий выход дешифратора подключен к S-входу второго RS-триггера,а второй вход первого таймера и третий вход Btoporo таймера. - соответственно к первому и второму входам устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 649032, кл. G 11 В 27/32, 1976. 2.Патент ФРГ 2342224, кл. Н 02 Р 5/00, опублик. 1976 (прототип).

Авторы

Даты

1983-02-23—Публикация

1981-07-30—Подача